Financial tax control SOC chip logic checking system

A logic verification and financial tax technology, applied in the field of logic verification system, can solve the problems of complex verification and testing work, shorten the development cycle and improve the design performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

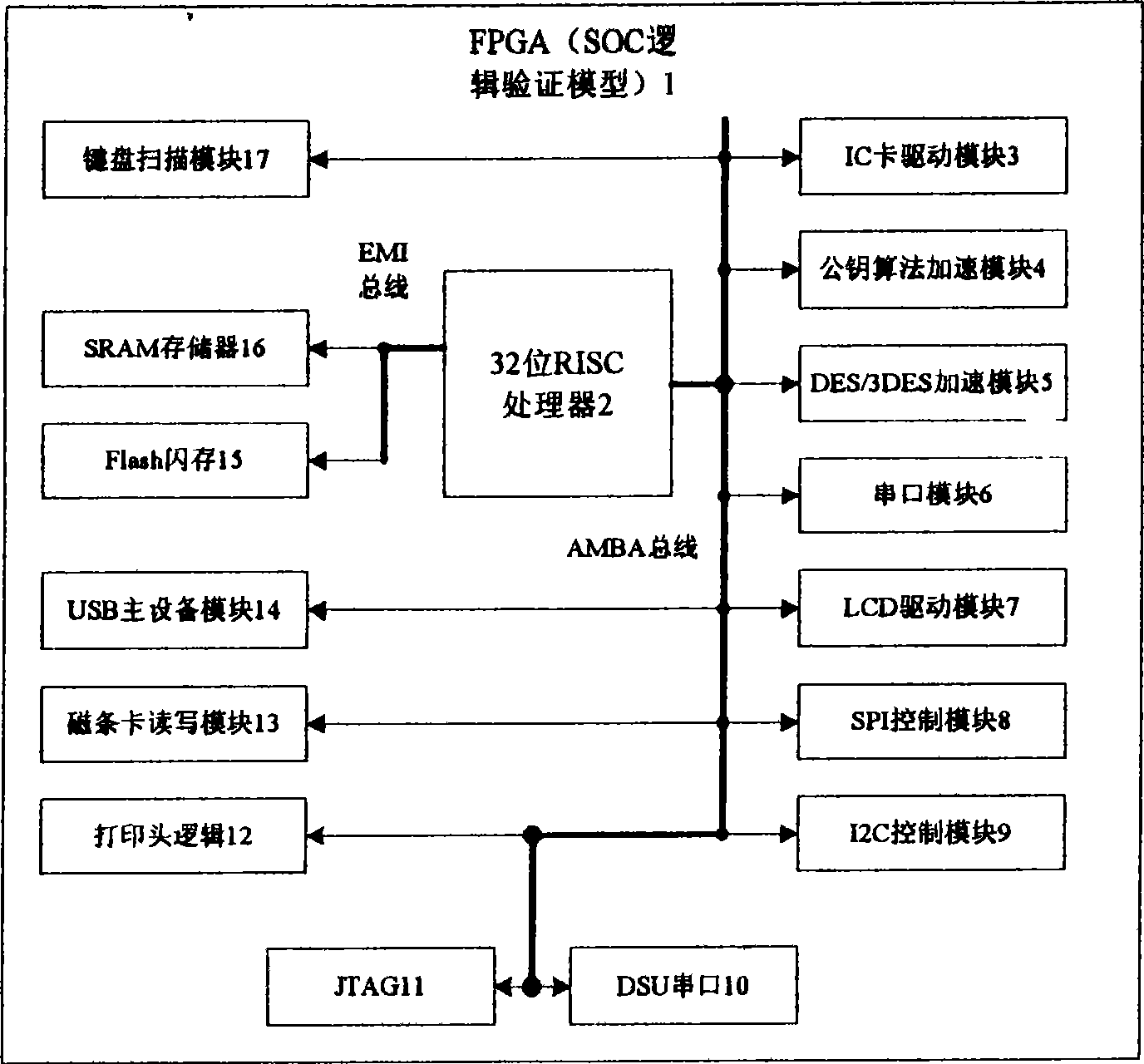

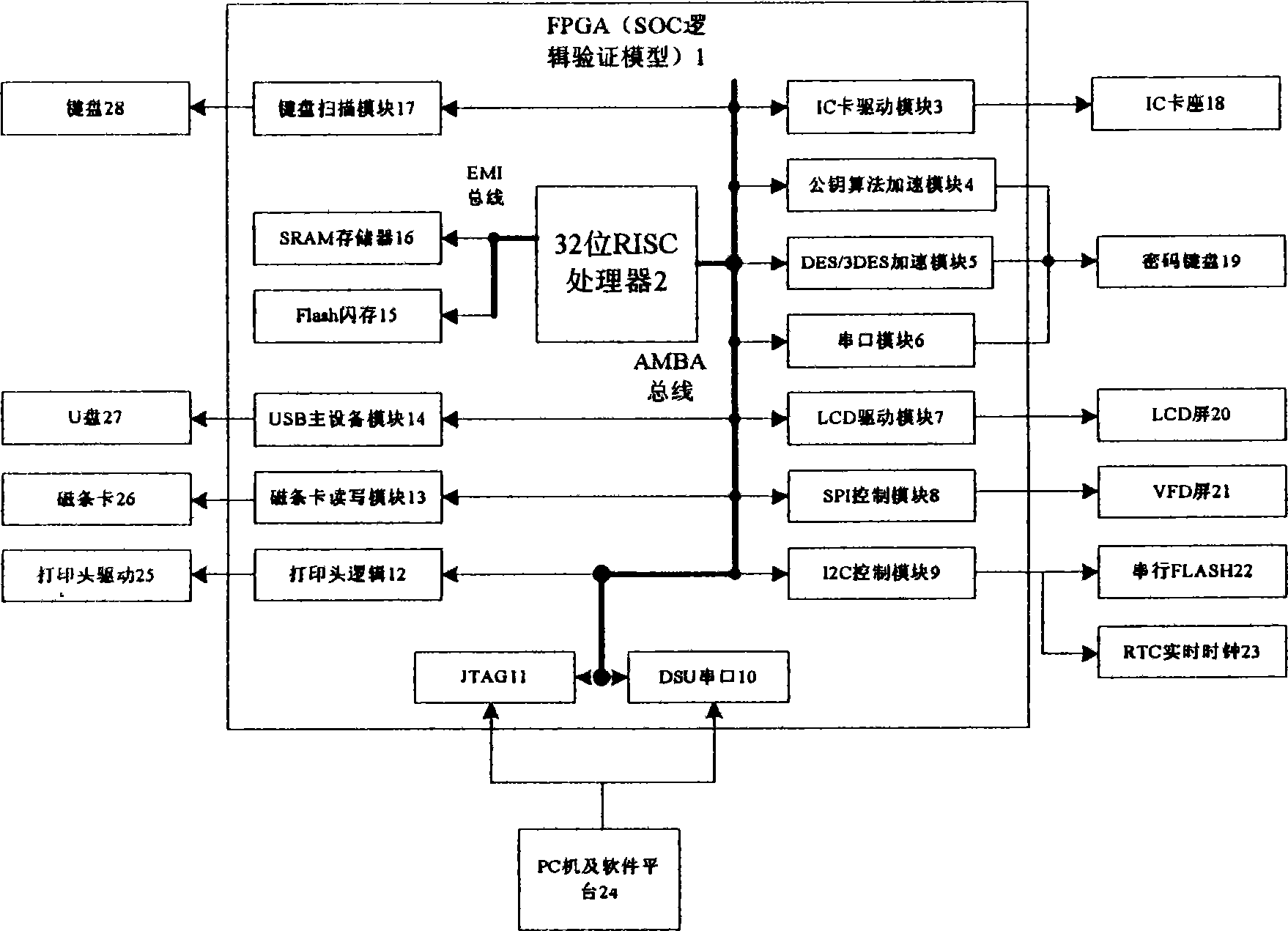

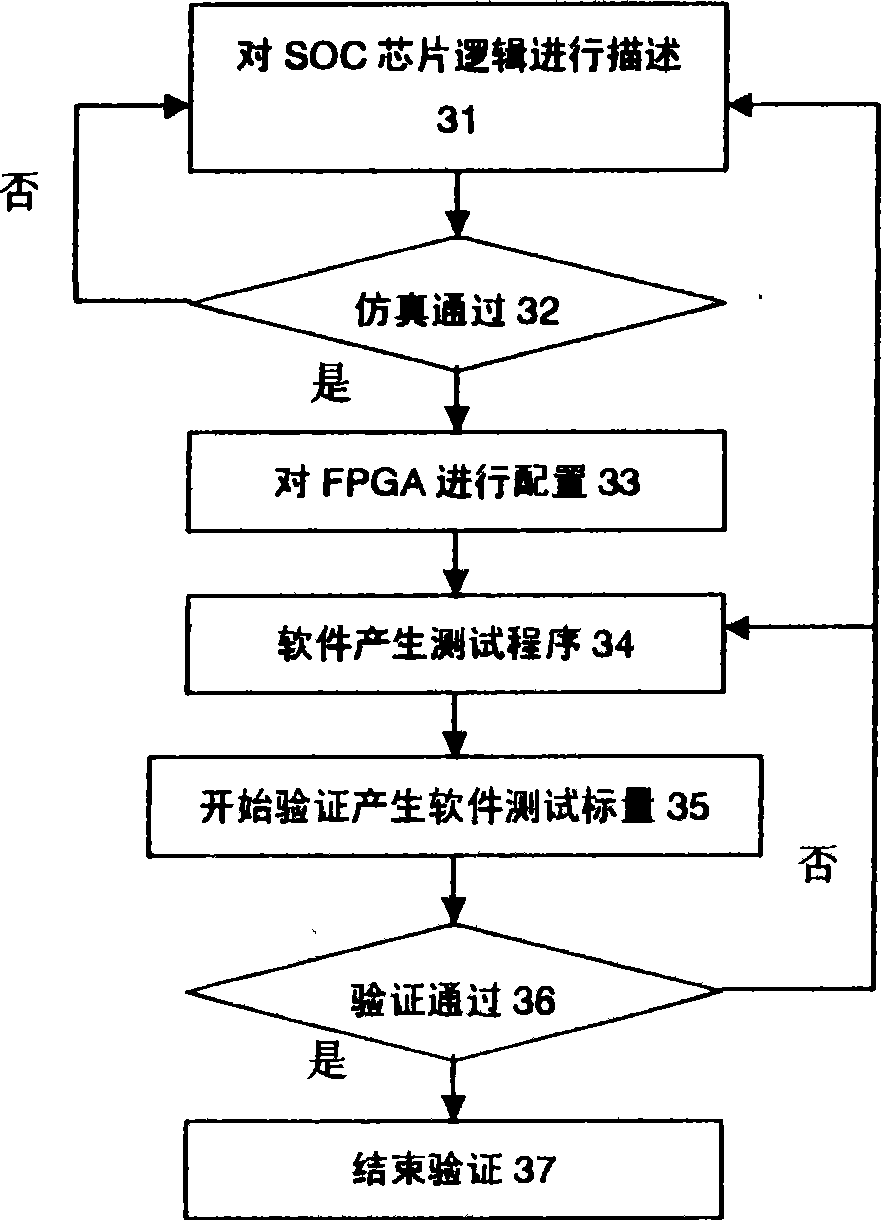

[0015] figure 1 It is a schematic diagram of the SOC logic verification model. Among them, the structure of the SOC logic verification model includes 32-bit RISC processor, IC card driver module 3, public key algorithm acceleration module 4, DES / 3DES acceleration module 5, serial port module 6, LCD driver module 7, SPI control module 8, I2C control module 9, DSU serial port 10, JTAG11, print head logic 12, magnetic stripe card read-write module 13, USB master module 14, Flash flash memory 15, SRAM memory 16 and keyboard scanning module 17, wherein, IC card driver module 3 , public key algorithm acceleration module 4, DES / 3DES acceleration module 5, serial port module 6, LCD driver module 7, SPI control module 8, I2C control module 9, DSU serial port 10, JTAG11, print head logic 12, magnetic stripe card reading and writing Module 13, USB master module 14 and keyboard scanning module 17 are connected to 32-bit RISC processor through AMBA bus, Flash flash memory 15 and SRAM memo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More