System and method for automatically generating constraint file of field programmable gate array (FPGA)

A constraint file, automatic generation technology, applied in the direction of instrumentation, computing, electrical digital data processing, etc., can solve problems such as error-prone, heavy workload, complex design of FPGA constraint files, etc., to achieve the effect of ensuring accuracy and improving design efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

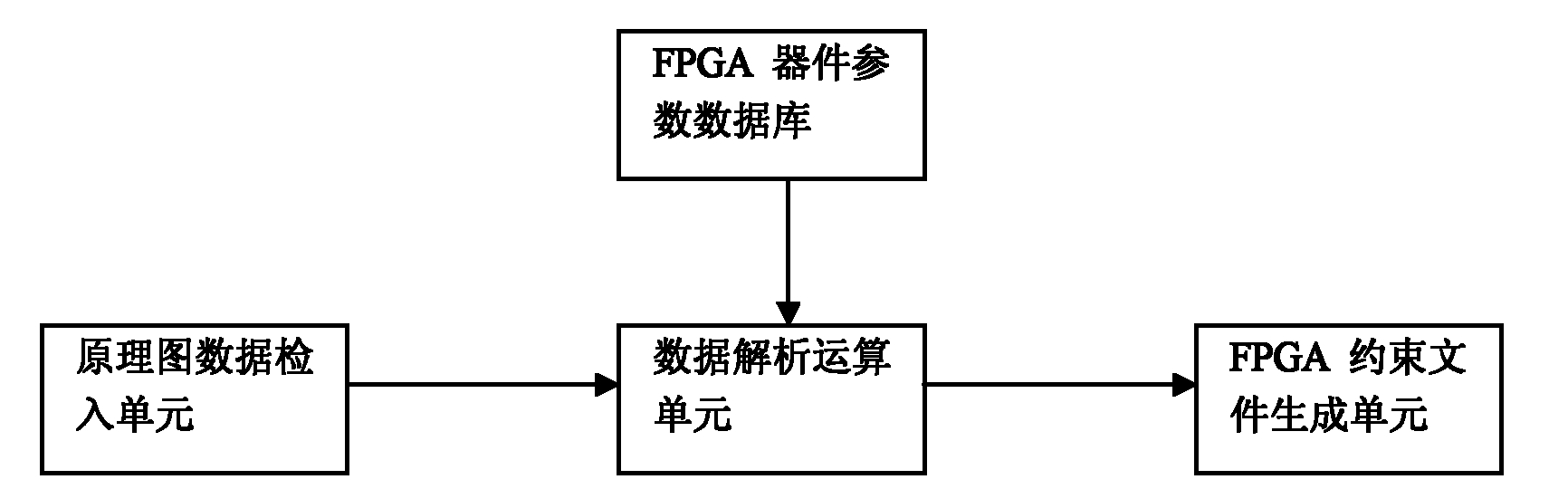

Method used

Image

Examples

Embodiment

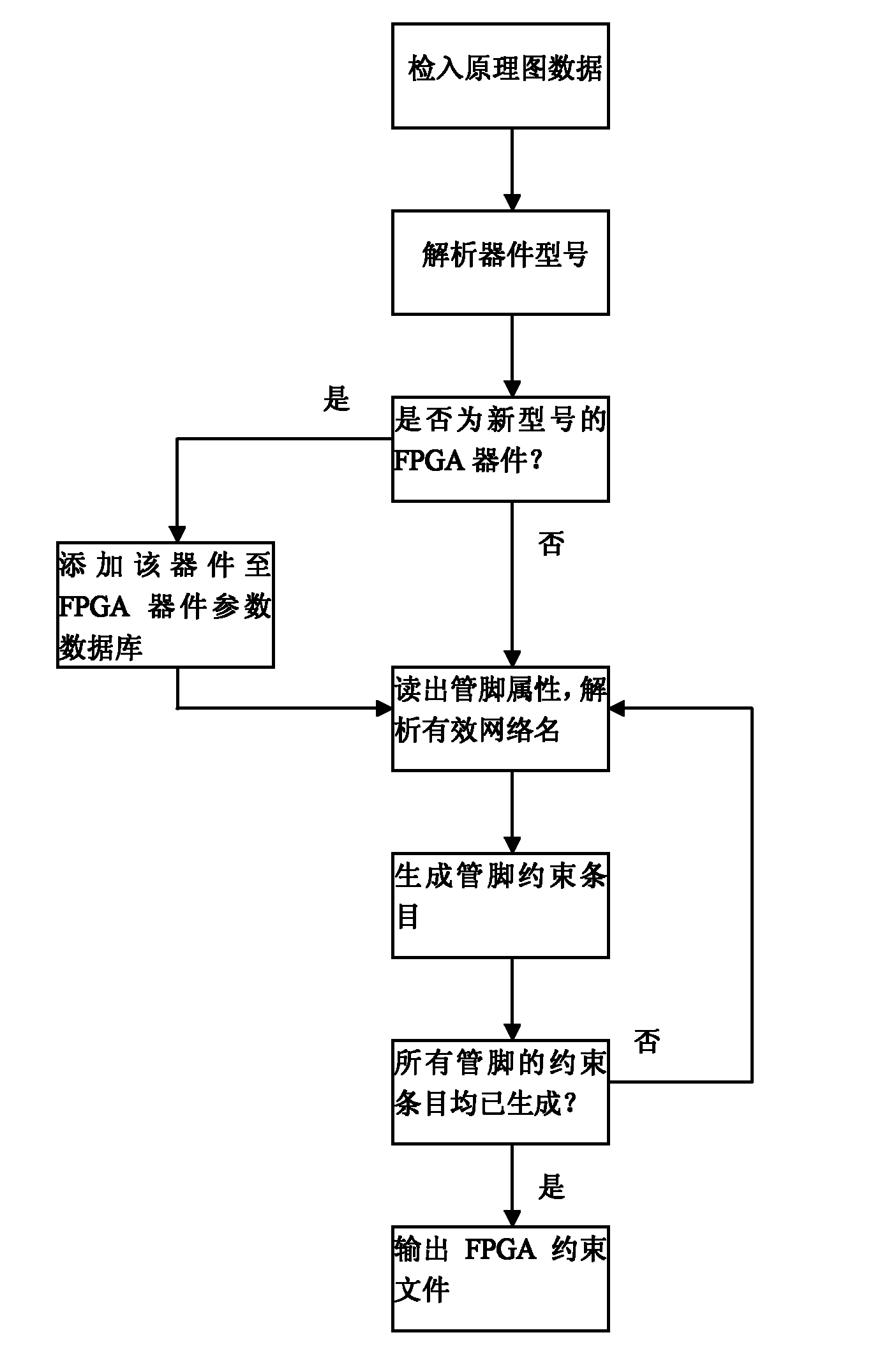

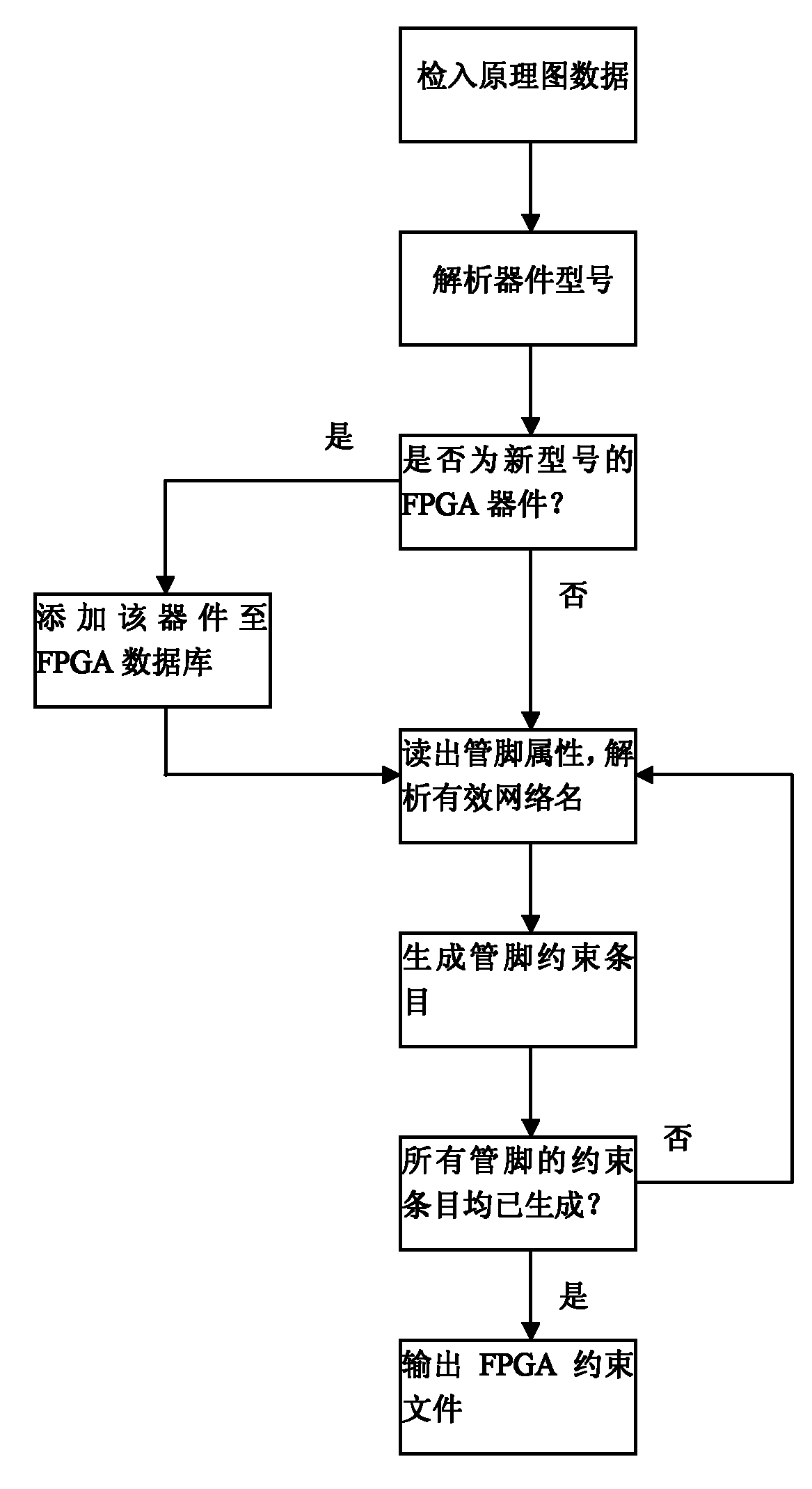

[0048] Take the generation of the FPGA constraint file on the main control board of the switch as an example,

[0049] First, check in the schematic topology data through the schematic data check-in unit:

[0050] Signal name: N1253354

[0051] Device pins connected by signal lines: R232.1, UF21.E2

[0052] (Note: R232 and UF21 are device bit numbers, and the following ".1" and ".E2" are pin numbers)

[0053] Device material number: R232(0012578)UF21(0011123)

[0054] Signal name: IN_LVTTL_ADDR13

[0055] Device pins connected by signal lines: R232.2

[0056] Then, according to the checked-in schematic topology data, enter the parsing process:

[0057] The first step is to find the FPGA device in the schematic diagram: According to the device tag naming convention, the device whose tag number starts with "R" is a resistor, and the device whose tag number starts with "UF" is an FPGA device.

[0058] In the second step, according to the searched FPGA device number, check w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More