Guidable FPGA (field programmable gate array) configuration circuit

A technology for configuring circuits and configuring information, applied in the direction of boot program, program control device, electrical digital data processing, etc., can solve the problems of small storage information capacity, power failure processing, troublesome use, etc., and achieve the effect of reducing the number of chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0009] In order to further understand the content, features and effects of the present invention, the following examples are given, and detailed descriptions are given below with reference to the accompanying drawings.

[0010] The structure of the present invention will be described in detail below in conjunction with the accompanying drawings.

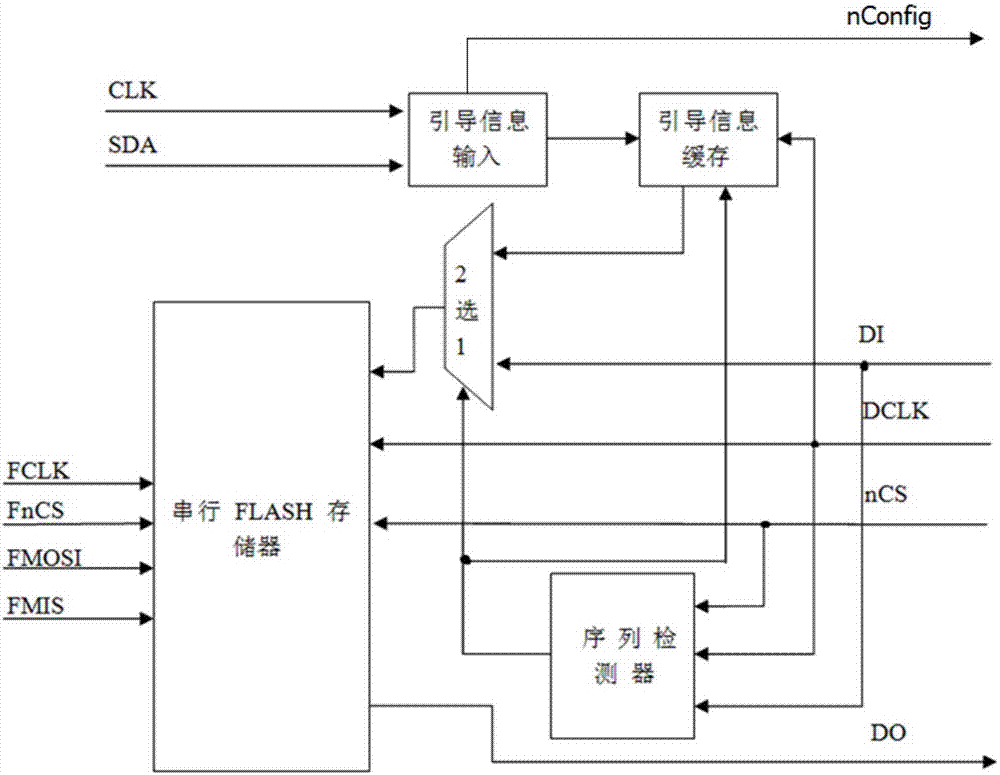

[0011] Such as figure 1 As shown, the bootable FPGA configuration circuit provided by the embodiment of the present invention includes a serial FLASH memory, and the FCLK, FnCS, FMOSI, and FMIS interfaces of the serial FLASH memory are connected to an external processor; the configuration information is written to the serial FLASH through the above-mentioned interface Memory; interface CLK, SDA to connect to external processor; set boot information through the above interface; nConfig, DI, DCLK, nCS, DO connect to FPGA through wires.

[0012] Further, the data writing of the serial FLASH memory: the external processor finishes writi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More