Patents

Literature

53 results about "Field-programmable object array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

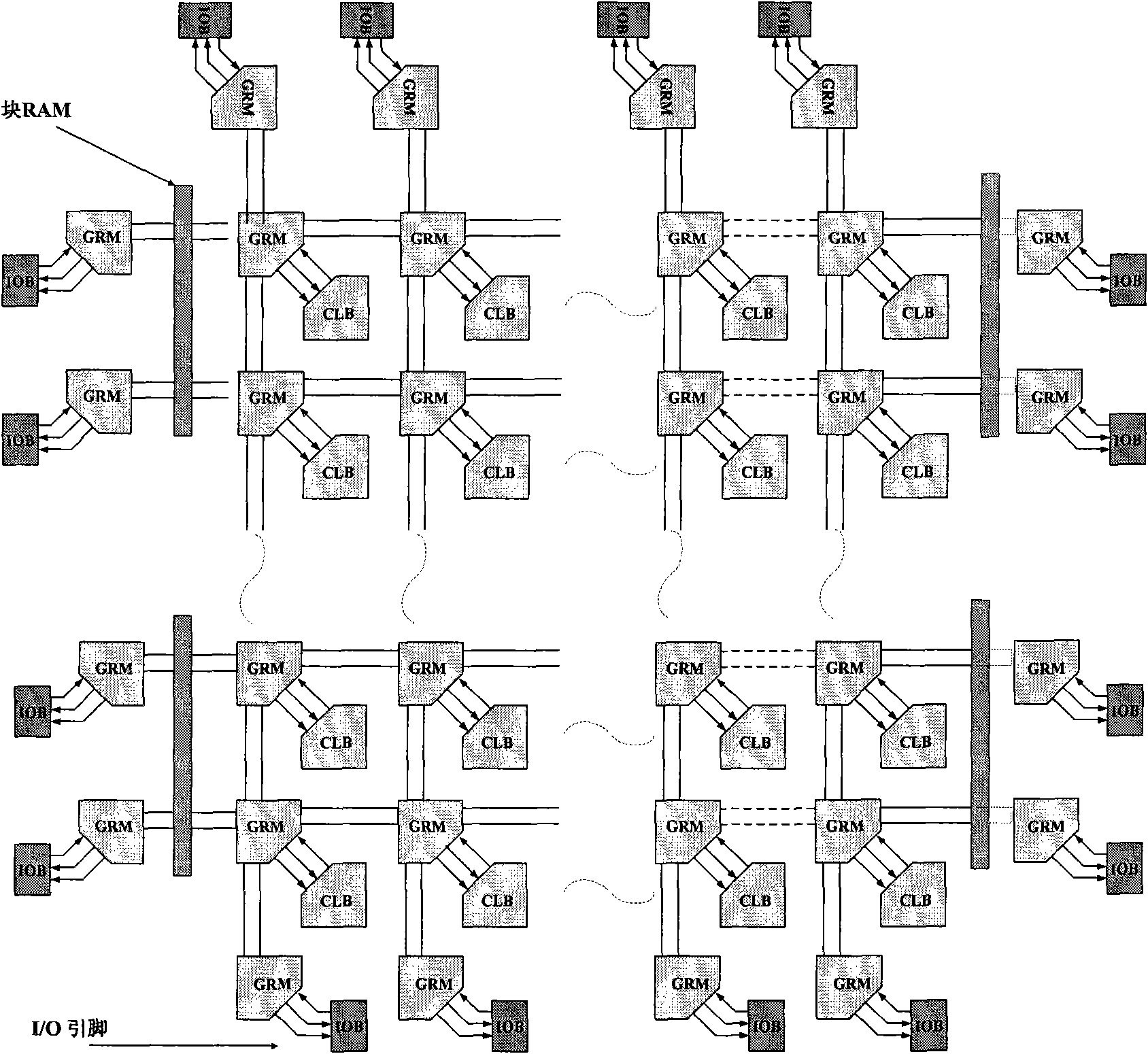

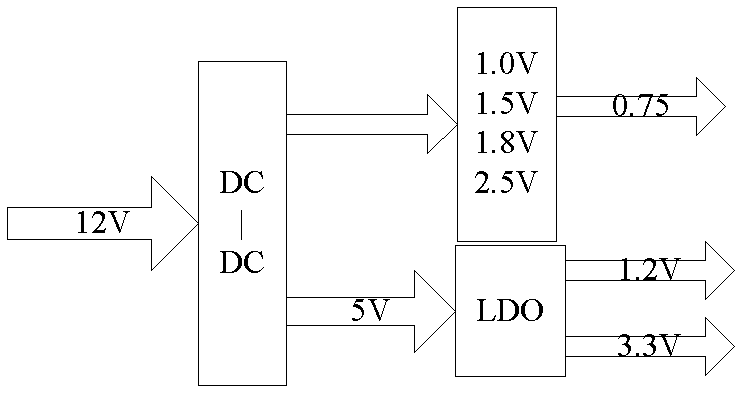

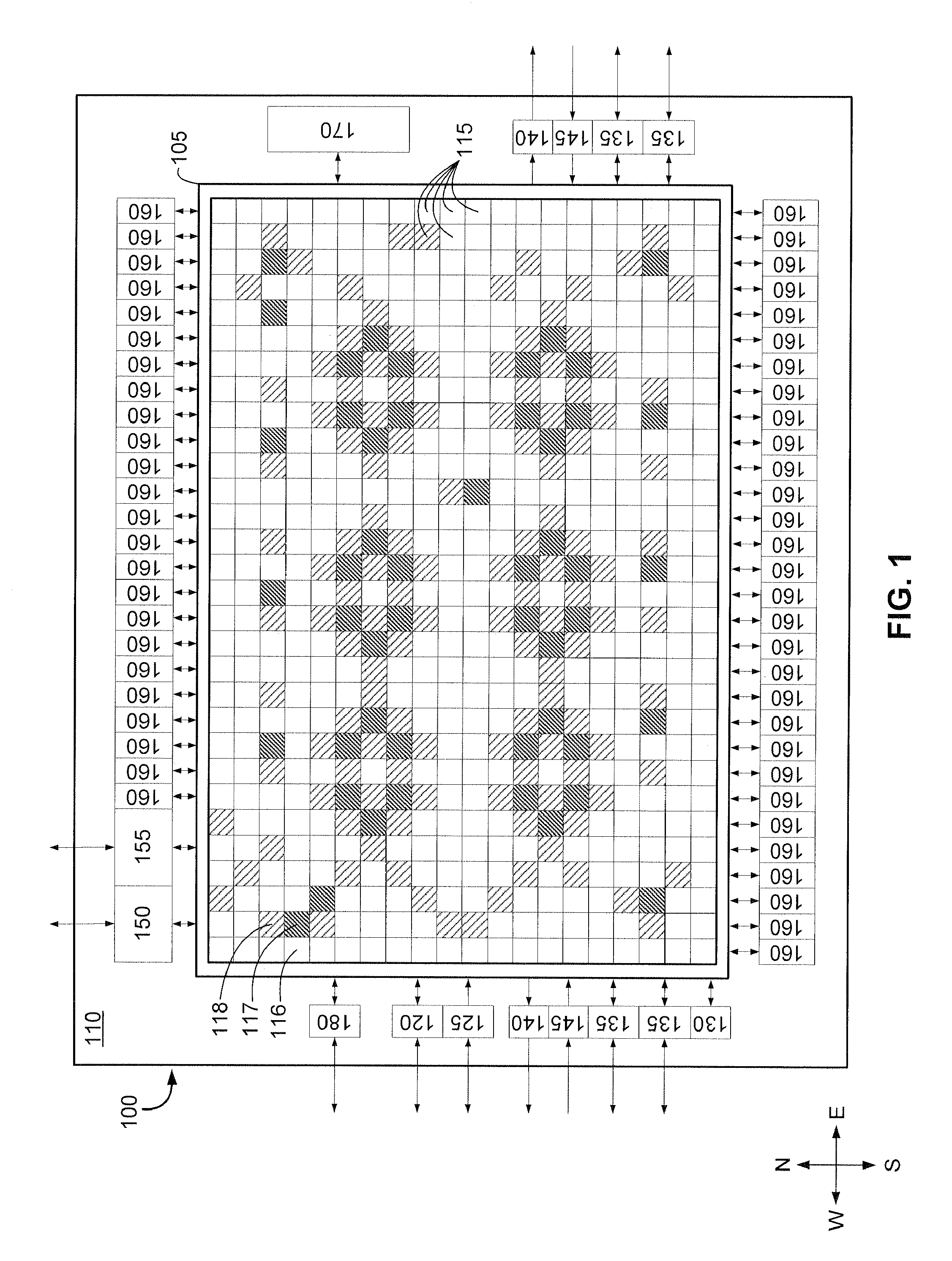

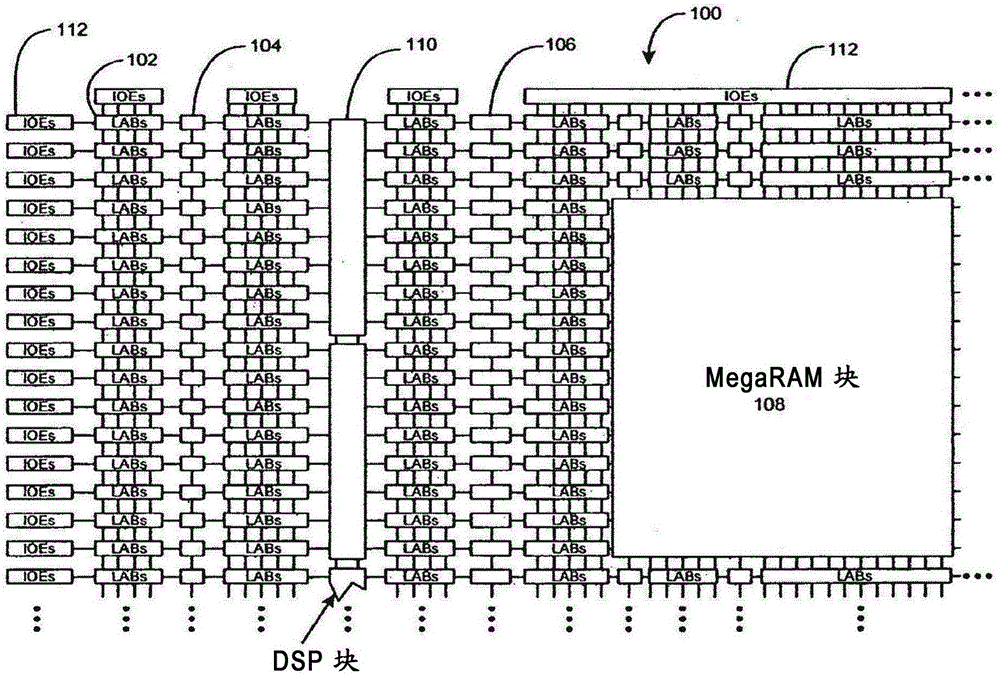

A field-programmable object array (FPOA) is a class of programmable logic device designed to be modified or programmed after manufacturing. They are designed to bridge the gap between ASIC and FPGA. They contain a grid of programmable silicon objects. Arrix range of FPOA contained three types of silicon objects arithmetic logic units (ALUs), register files (RFs) and multiply-and-accumulate units (MACs). Both the objects and interconnects are programmable.

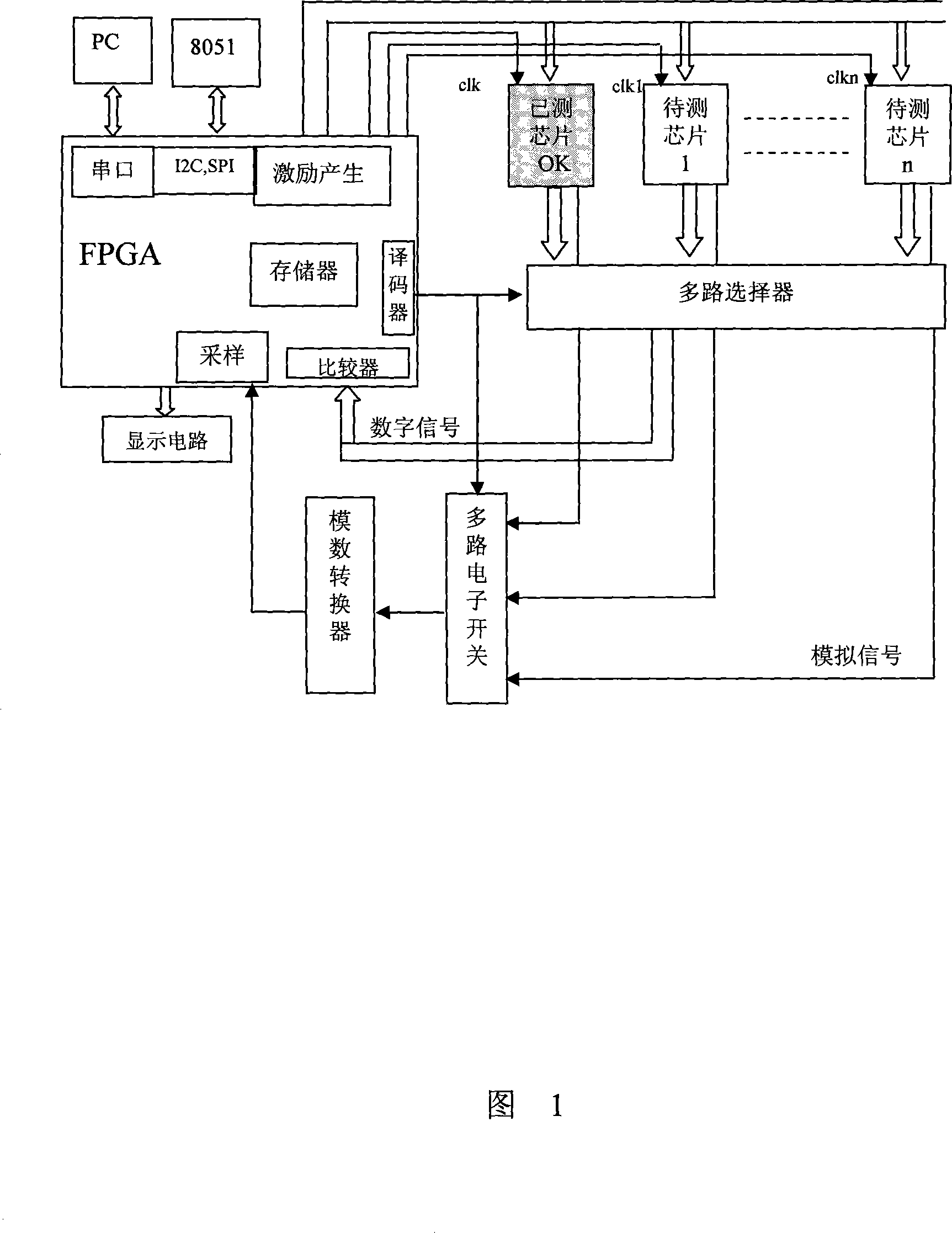

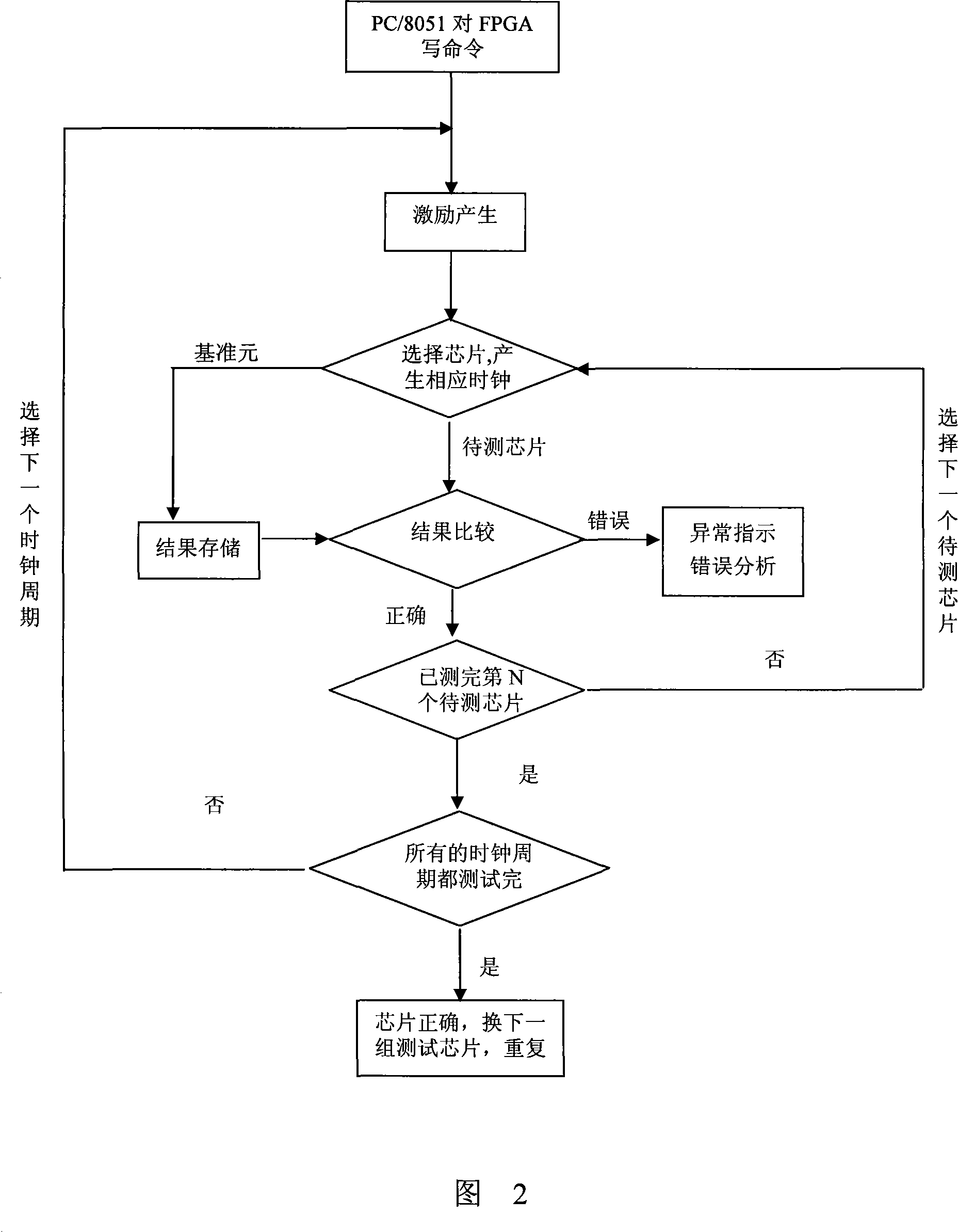

Multiple chips automatic test method based on programmable logic device

InactiveCN101158708AMeet the test requirementsImplement automated testingDigital circuit testingProgrammable logic deviceField-programmable object array

The invention relates to an automatic testing technology for molectron, in particular to an automatic testing method for multiple chips based on field programmable gate array (FPGA). According to the technical scheme provided by the invention, the field programmable gate array comprises the sample circuits that are connected to each other, a circuit of digital comparator, an encoder, and a pulse generating circuit. The technical scheme is characterized in that the input end of the circuit of digital comparator is connected with the output end of a multiplexer, the input end of the sample circuit is connected with a plurality of chips being tested; and the pulse generating circuit is connected with a plurality of chips being tested and a tested chip respectively; the output end of the encoder circuit is connected with the multiplexer. The invention uses the field programmable gate array (FPGA) to set up a simple automatic testing system, in which the automatic testing of a single or a plurality of chips can be implemented simultaneously on a testing board, The invention achieves automatic testing and has low input cost and rapid development, thus completely satisfying the requirement for the testing of small-lot products.

Owner:无锡汉柏信息技术有限公司

Field programmable object array having image processing circuitry

ActiveUS20100020880A1Improve performanceReduce Design ComplexityPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningData compressionImaging processing

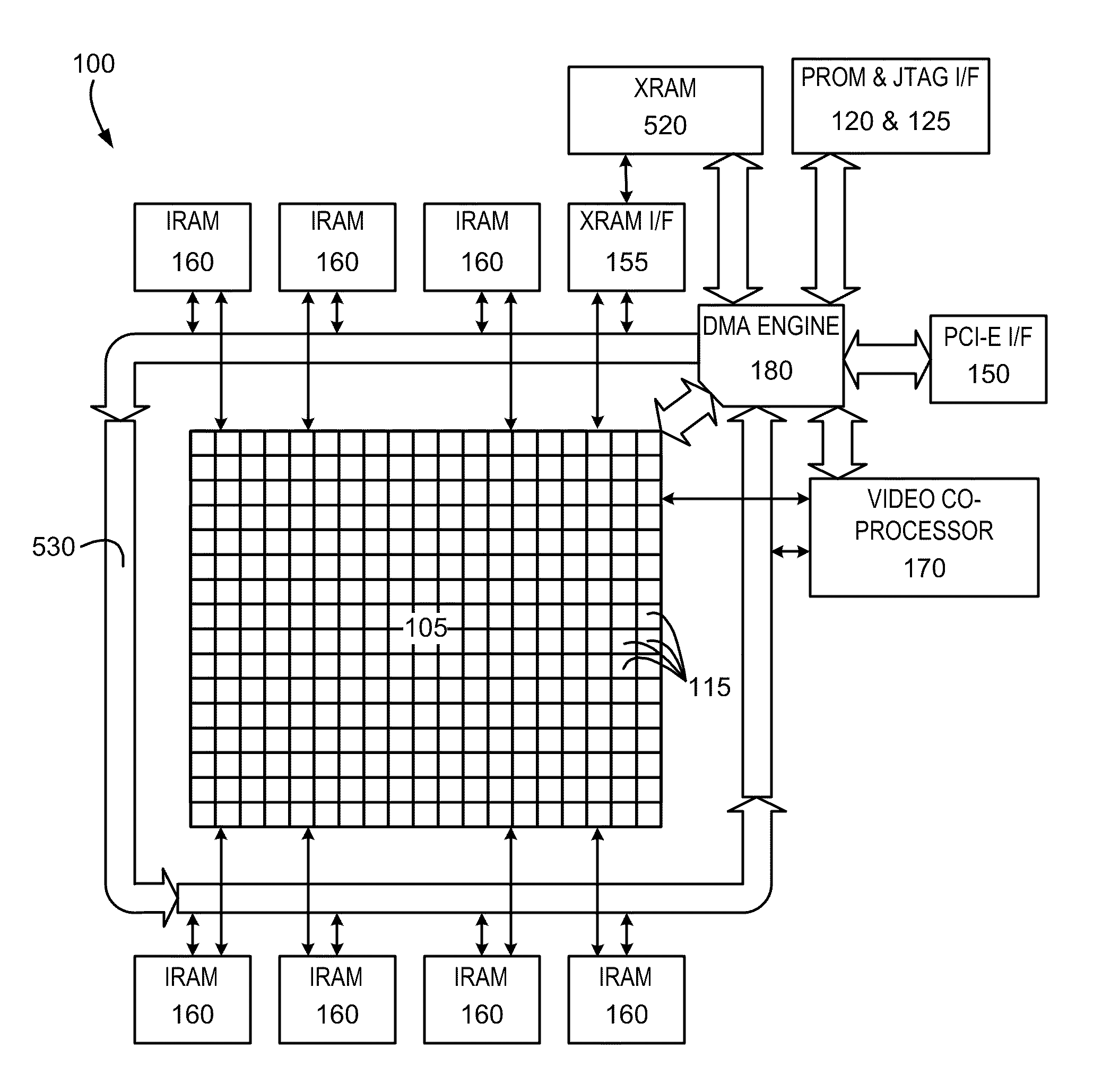

A field programmable object array integrated circuit has video data compression capability. The integrated circuit comprises an array of programmable objects and a video compression co-processor communicatively coupled to the array of objects. The video compression co-processor comprises a set of search engines and a subpixel engine. The subpixel engine can interpolate subpixels from integer pixels and shift the integer pixels by a predetermined number of subpixels. The search engines can perform a plurality of sum of absolute differences (SAD) computations between search window pixels and macroblock pixels to locate the best SAD value using either integer pixels and / or the interpolated subpixels.

Owner:NYTELL SOFTWARE LLC

Method, device and system for field programmable gate array test

InactiveCN101196557AAvoid length restrictionsImplement remote testingDigital circuit testingField-programmable object arrayTransformer

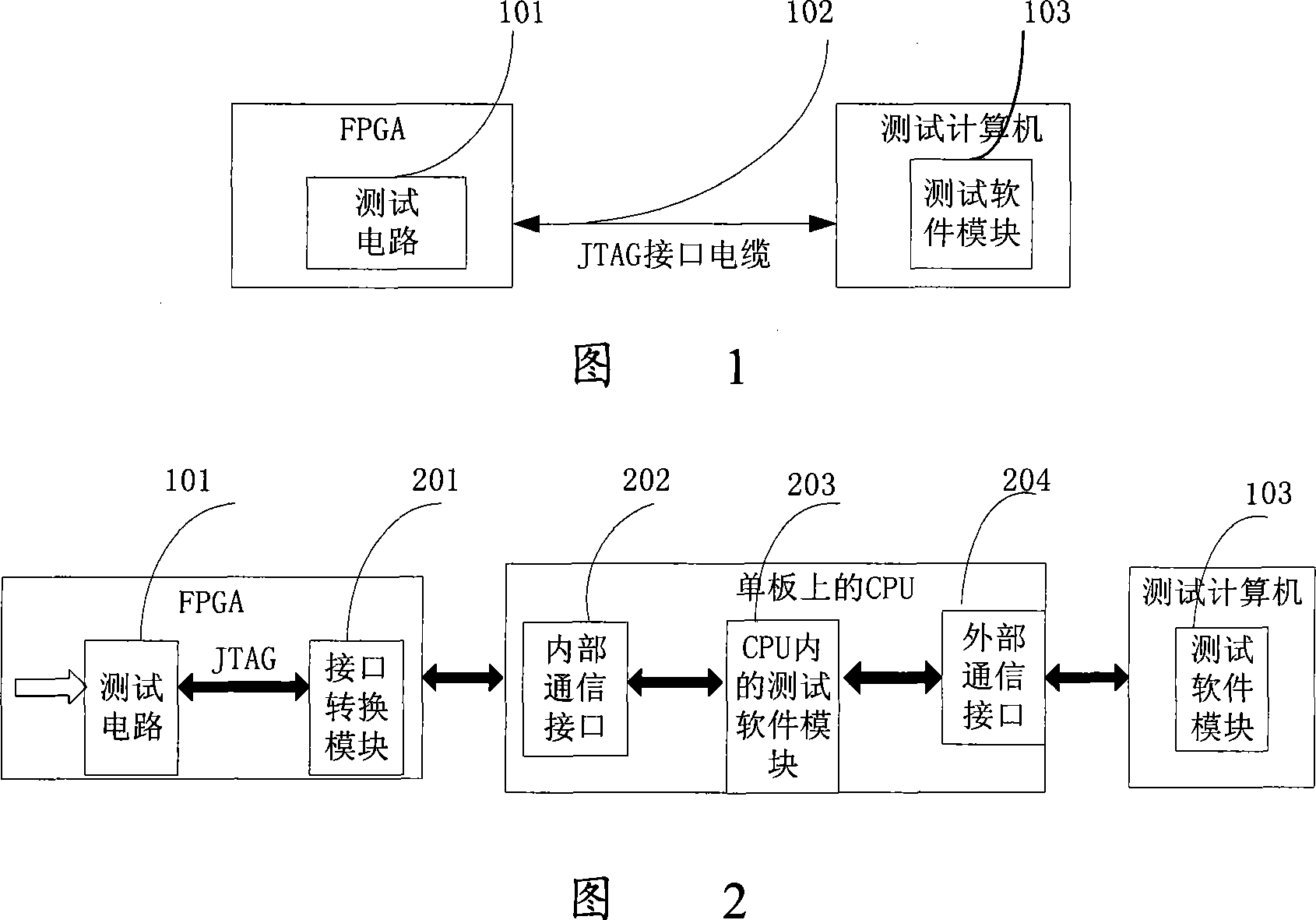

The embodiment of the invention provides a method, a device and a system for testing the field programmable gate array, the method of which comprises that: the control chip receives the FPGA (field programmable gate array) and test the data of interface format recognized by the control chip output after the transformer of the related information; the control chip sends the data of interface format which can be recognized to the test computer; the control chip receives the control information sent by the test computer; the control chip sends the control information to FPGA. The embodiment of the invention solves the problems that the online test and remote test can not be achieved due to the limit of JTAG interface and the JTAG cable in length in prior art by the control chip on the veneer and the external communication interface.

Owner:SHANGHAI HUAWEI TECH CO LTD

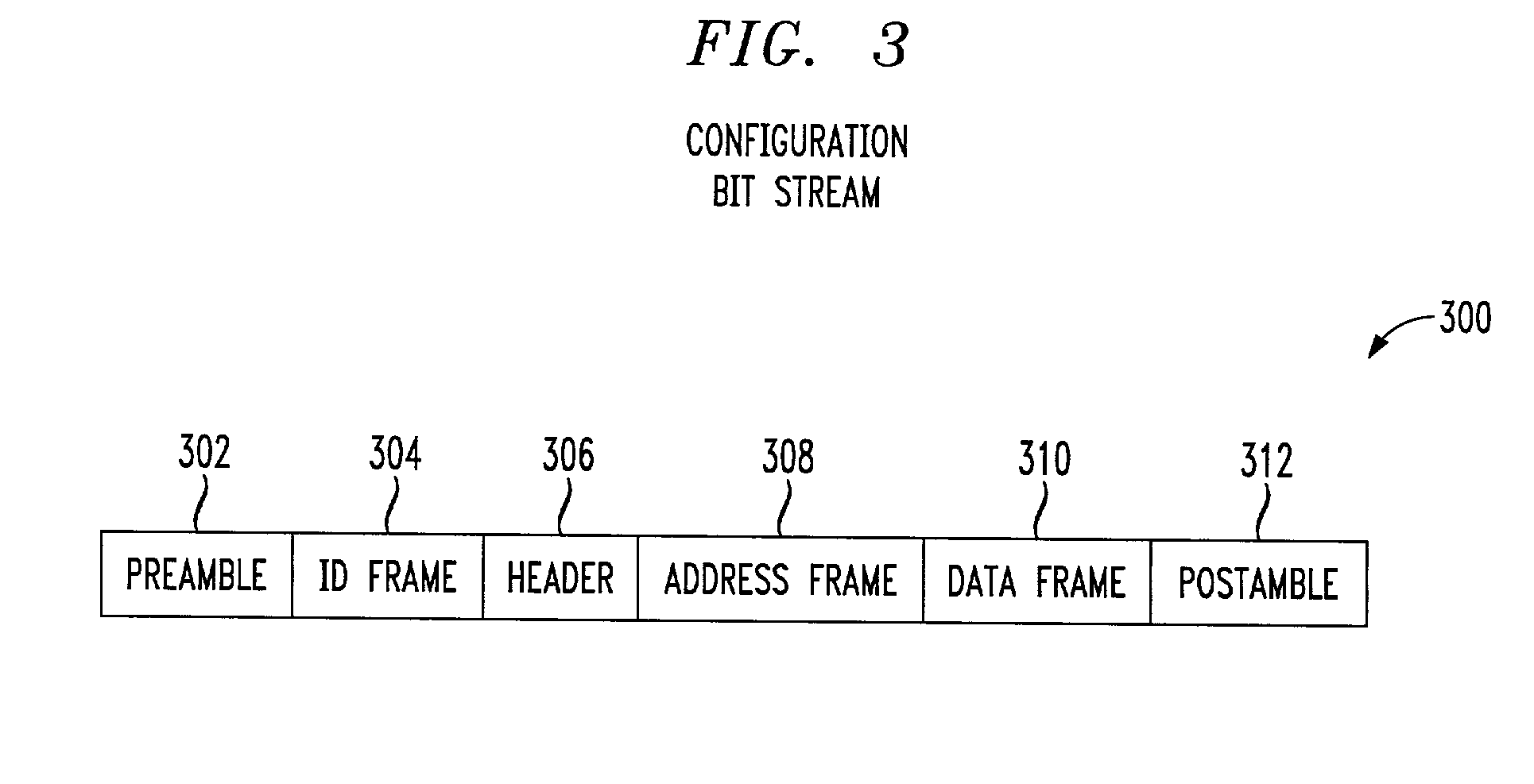

Field programmable gate array (FPGA) bit stream cormat

InactiveUS20020010902A1Programmable logic circuit arrangementsPulse automatic controlData streamField-programmable object array

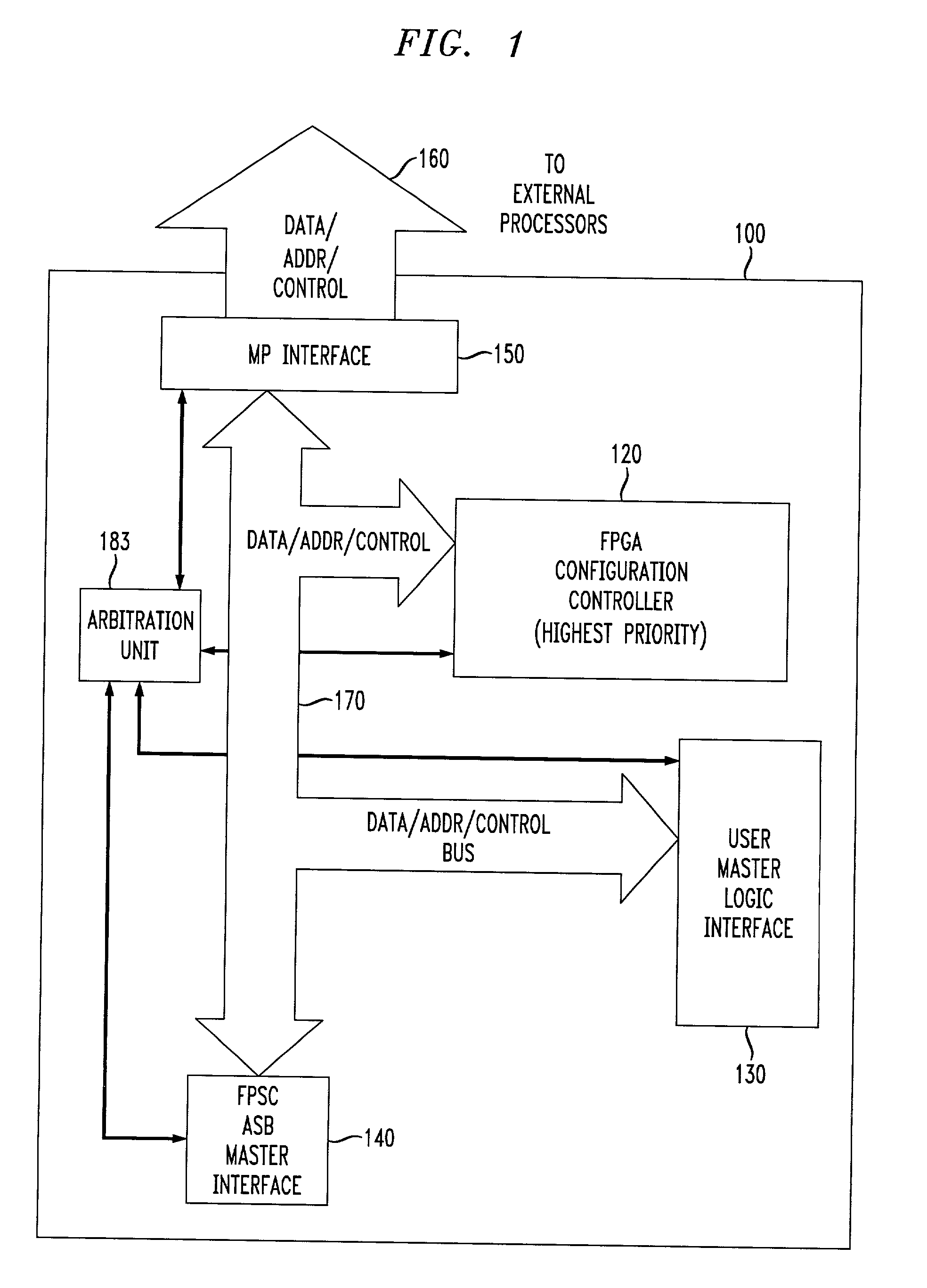

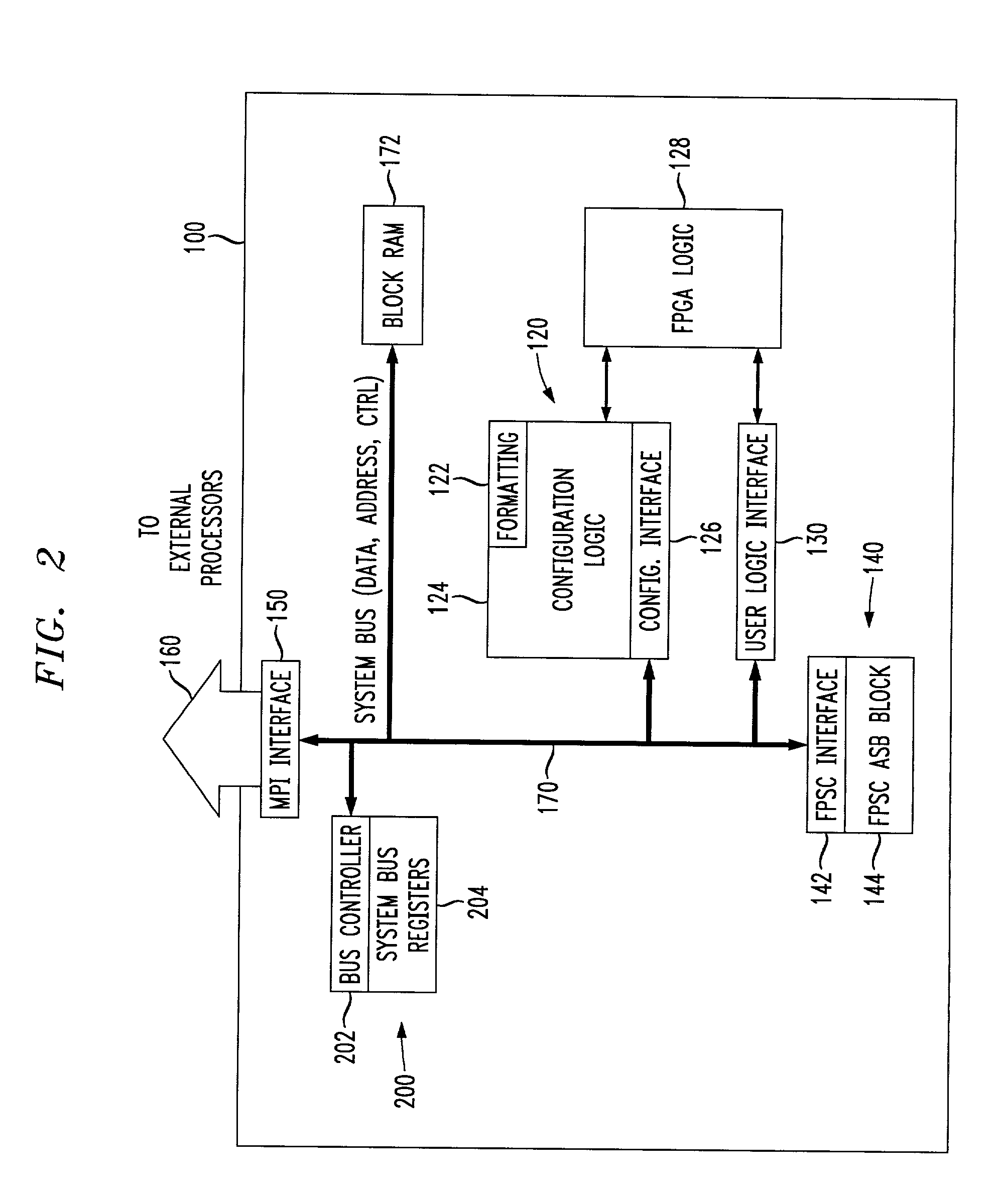

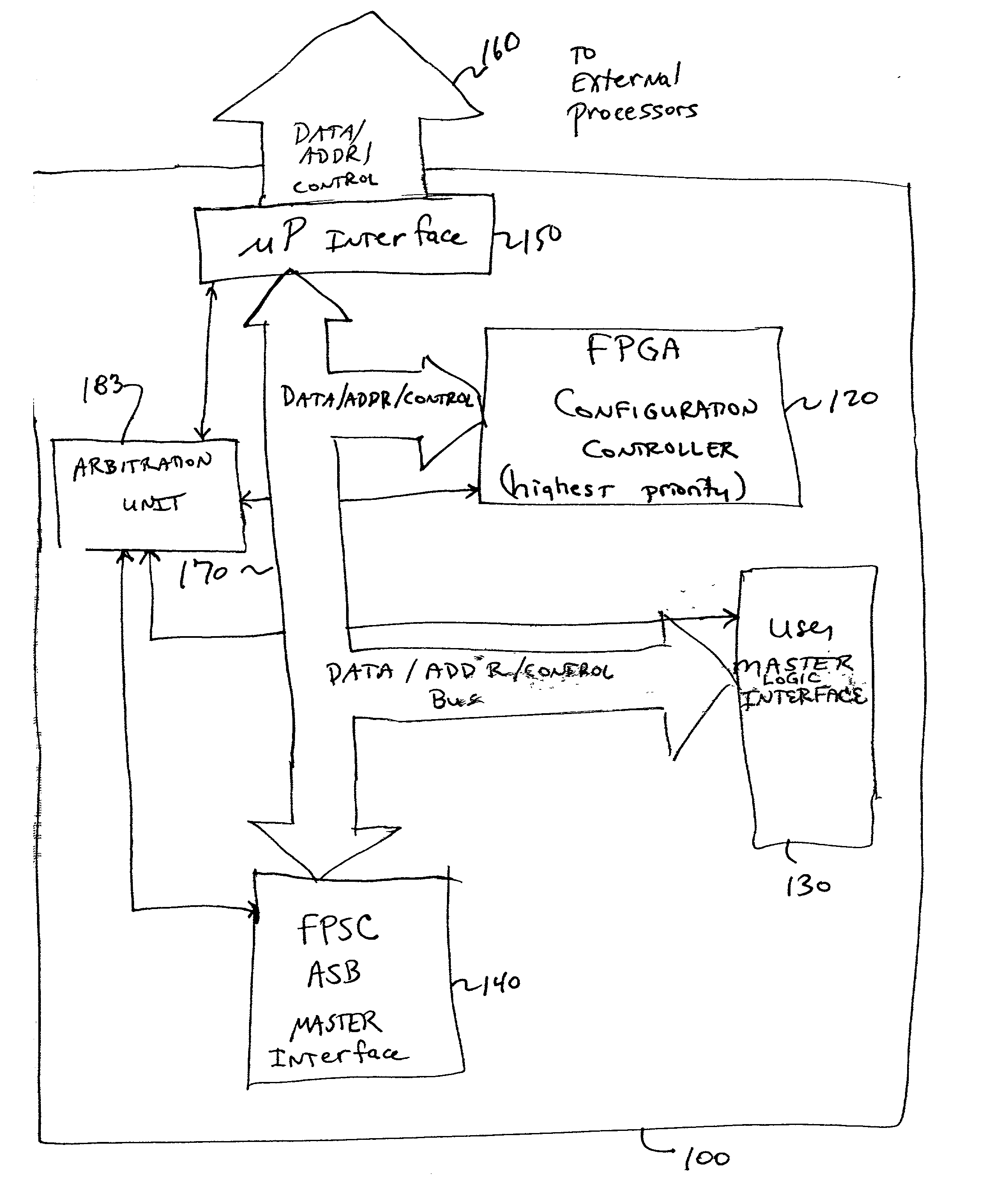

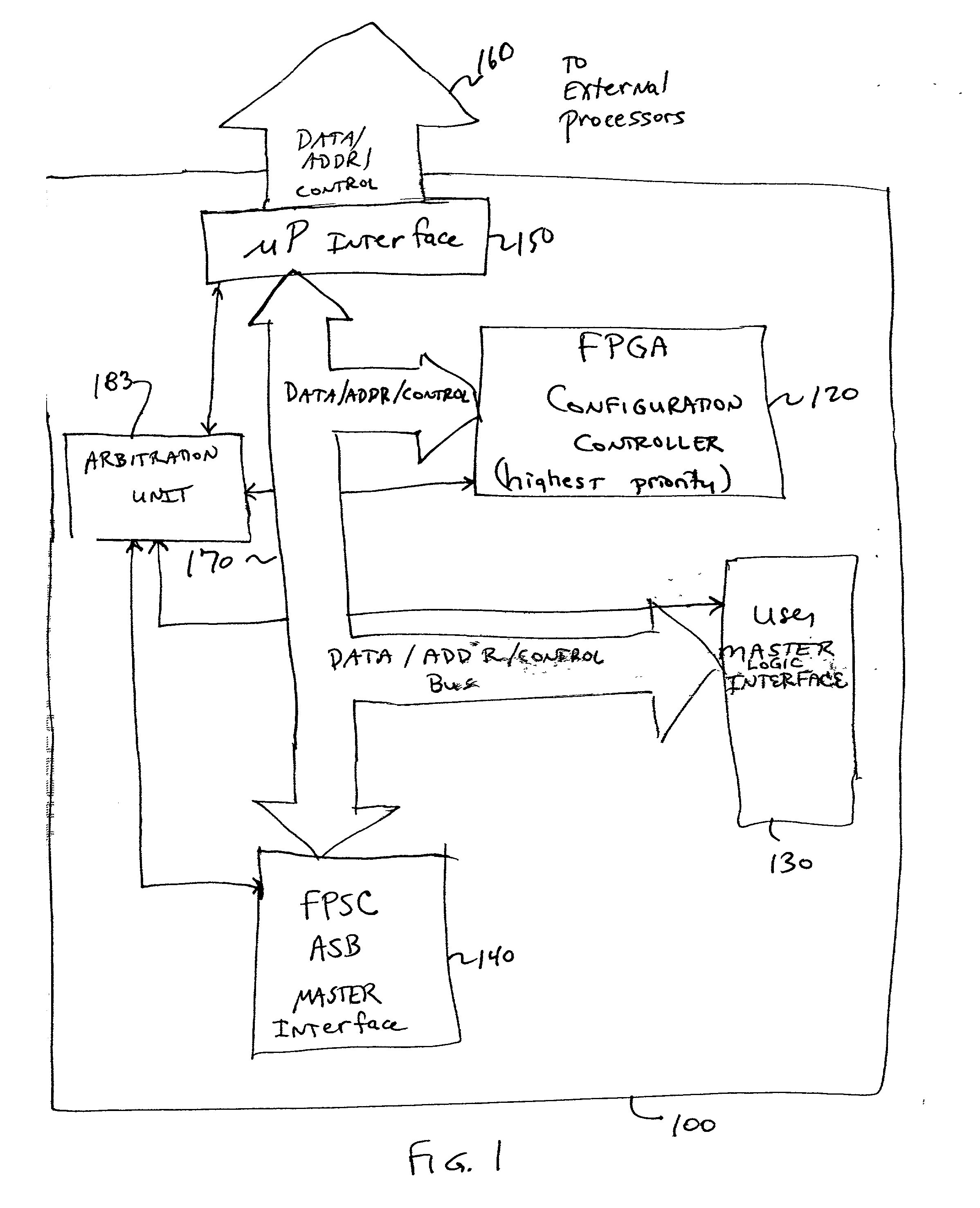

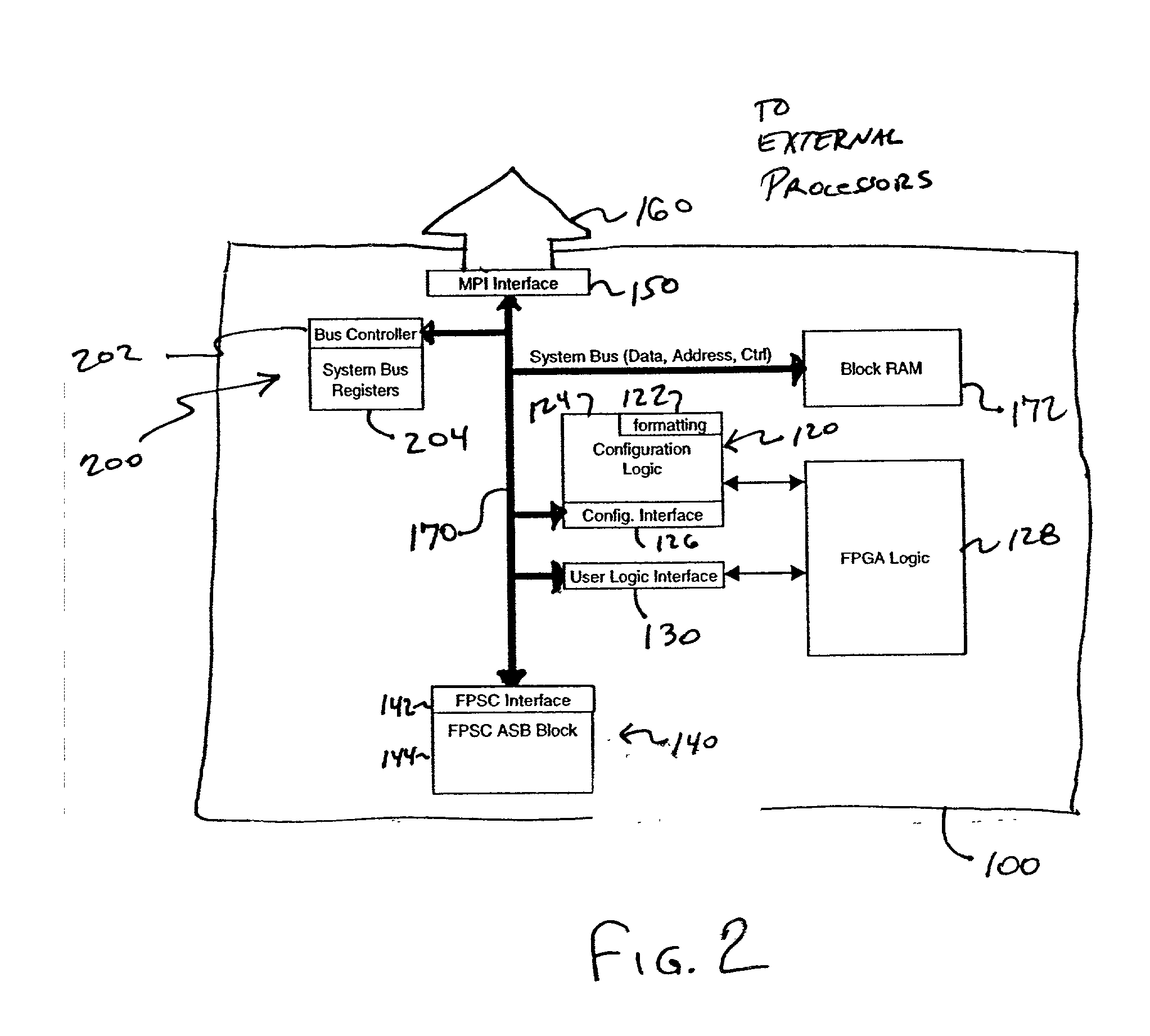

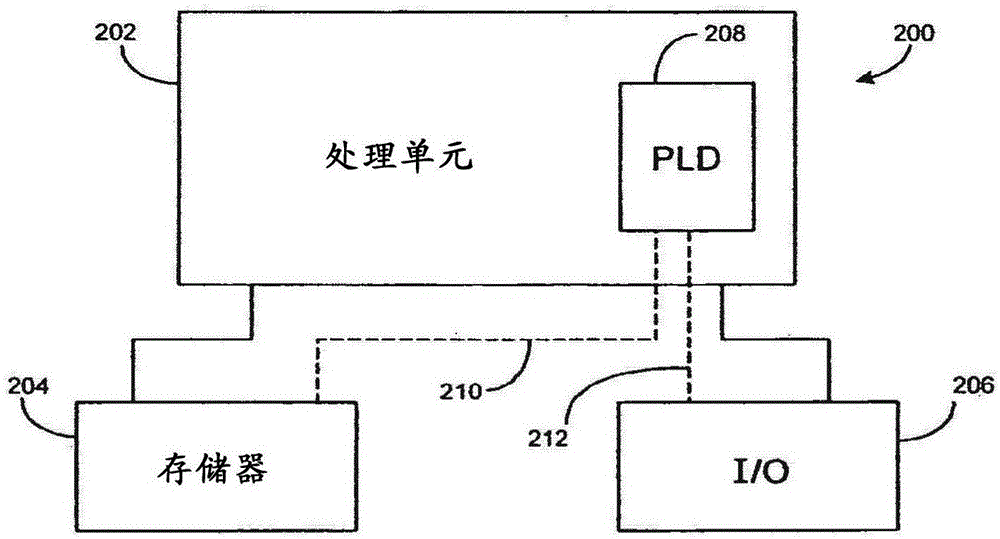

An embedded system bus is woven between a plurality of embedded master elements and at least one slave element within the FPGA device, and provides an external processor interface allowing direct access to any of the plurality of embedded slave elements. Using the embedded system bus, any of a plurality of masters may be allowed to program an embedded element, e.g., embedded FPGA logic, whereas conventional FPGAs allowed only a single master (e.g., a processor) to program the embedded FPGA logic. The embedded system bus is a group of signals, typically data, address and control, that connects system elements together and provides a basic protocol for the flow of data. The embedded system bus allows for control, configuration and status determination of the FPGA device. The embedded system bus is preferably a dedicated function available at all times for arbitrated access to allow communication between the various embedded system components.

Owner:LATTICE SEMICON CORP

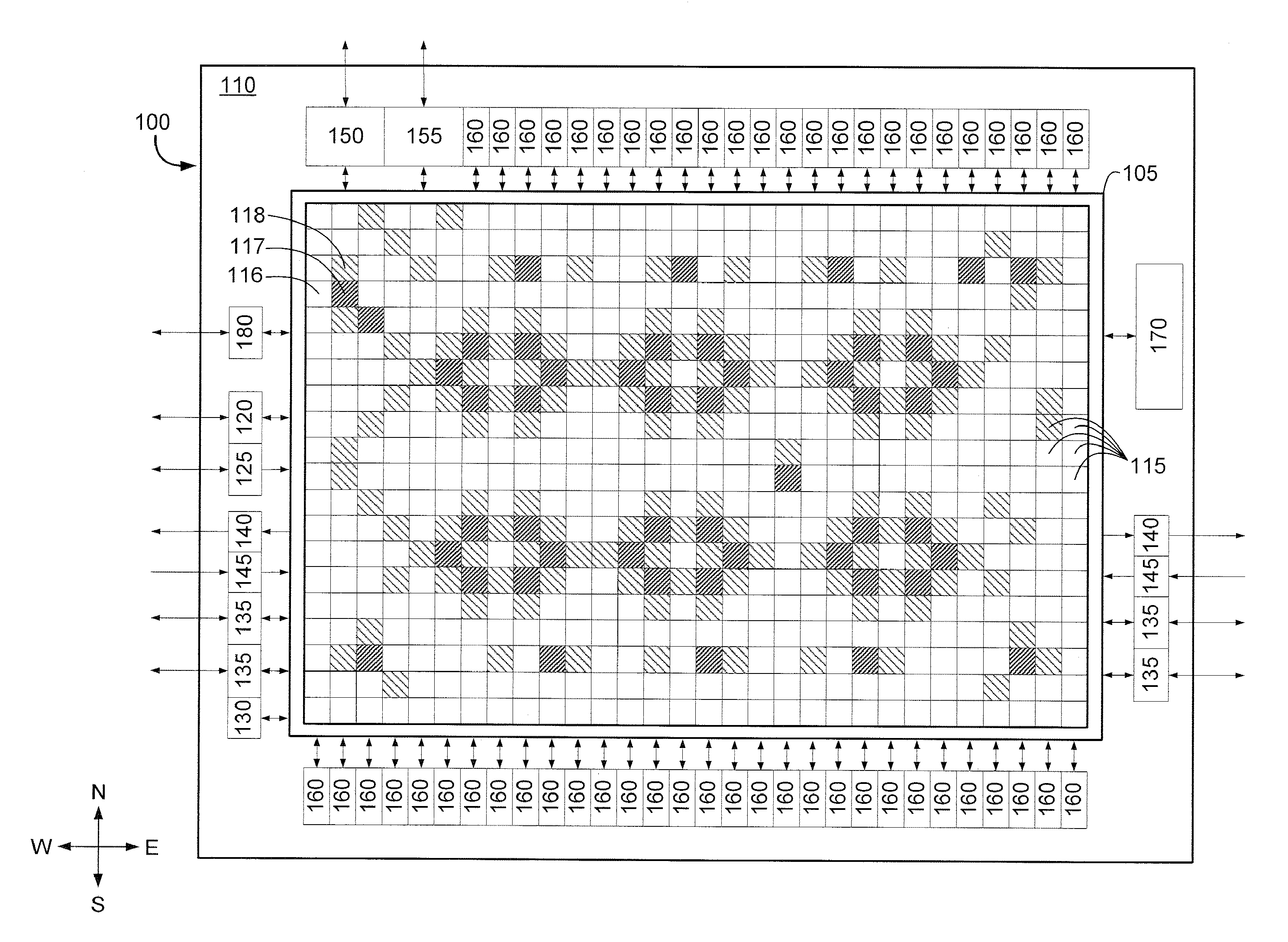

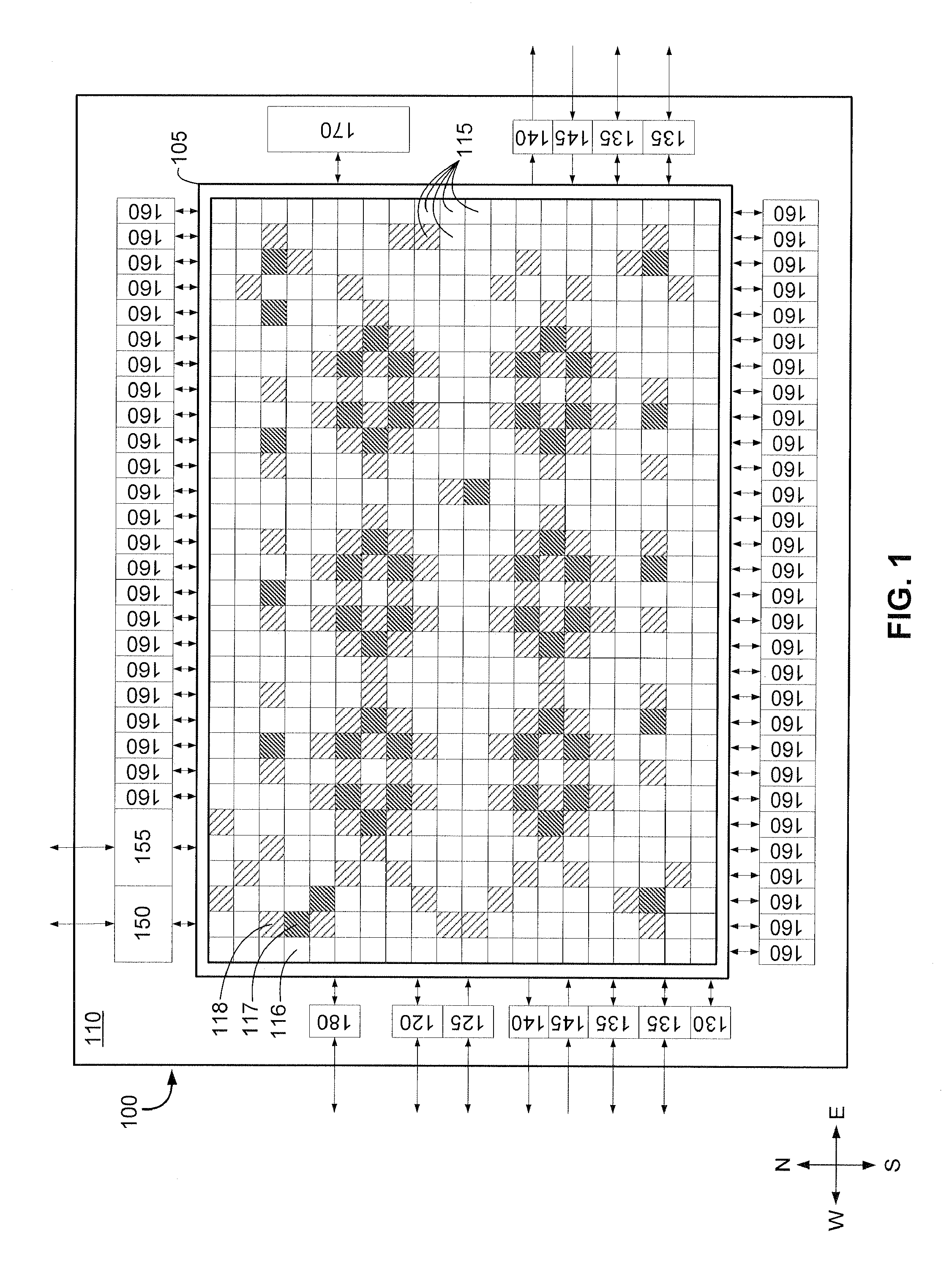

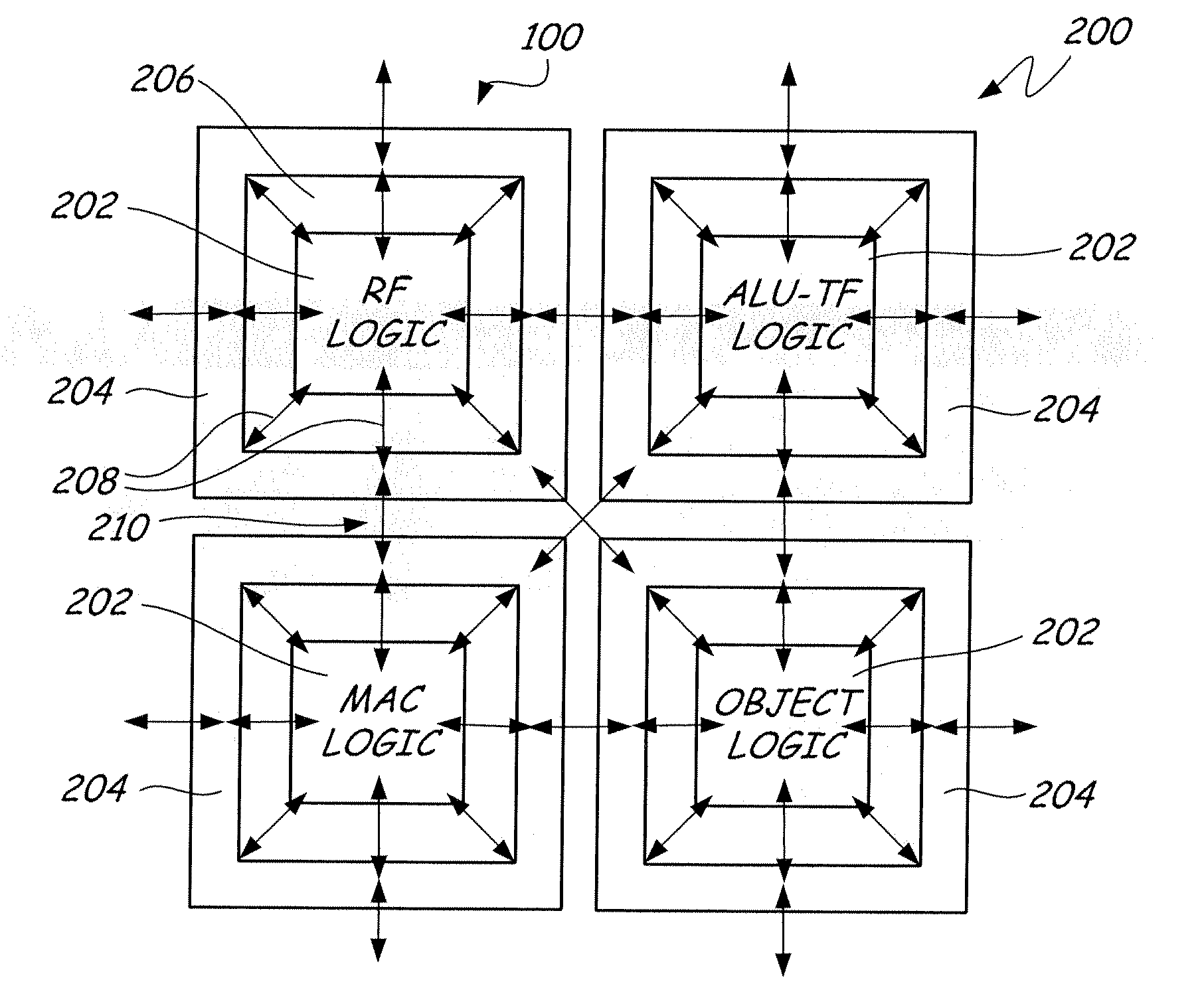

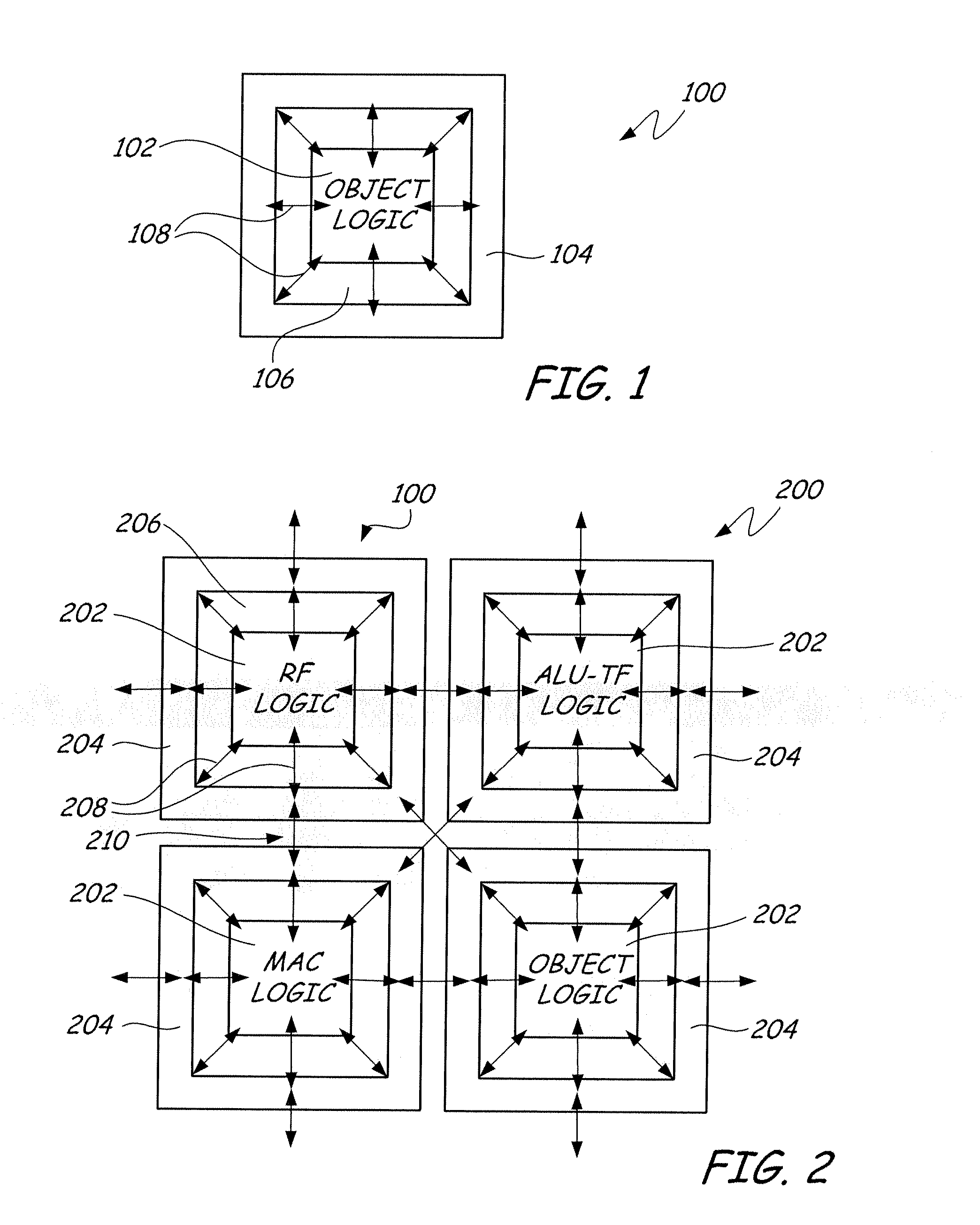

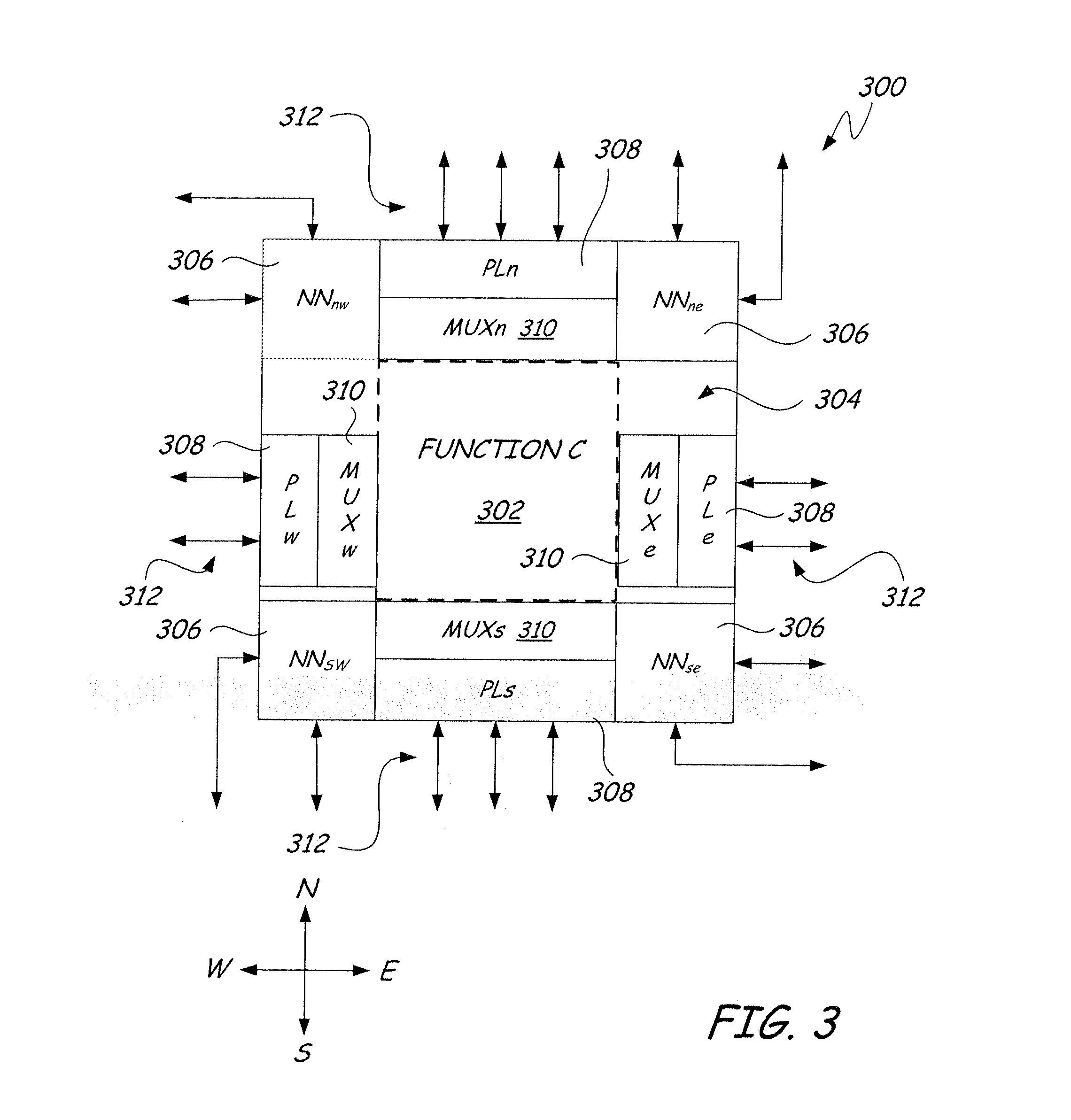

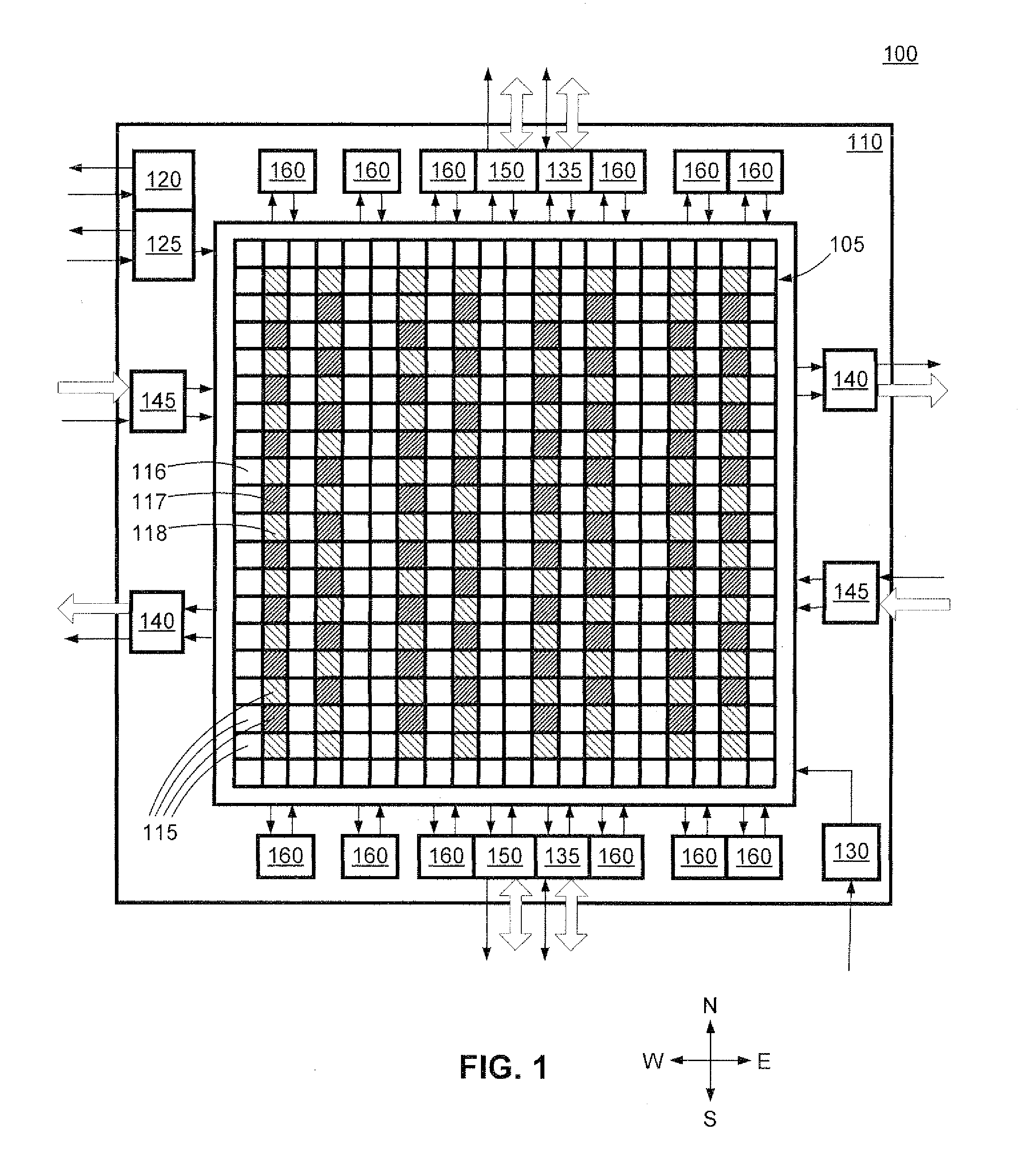

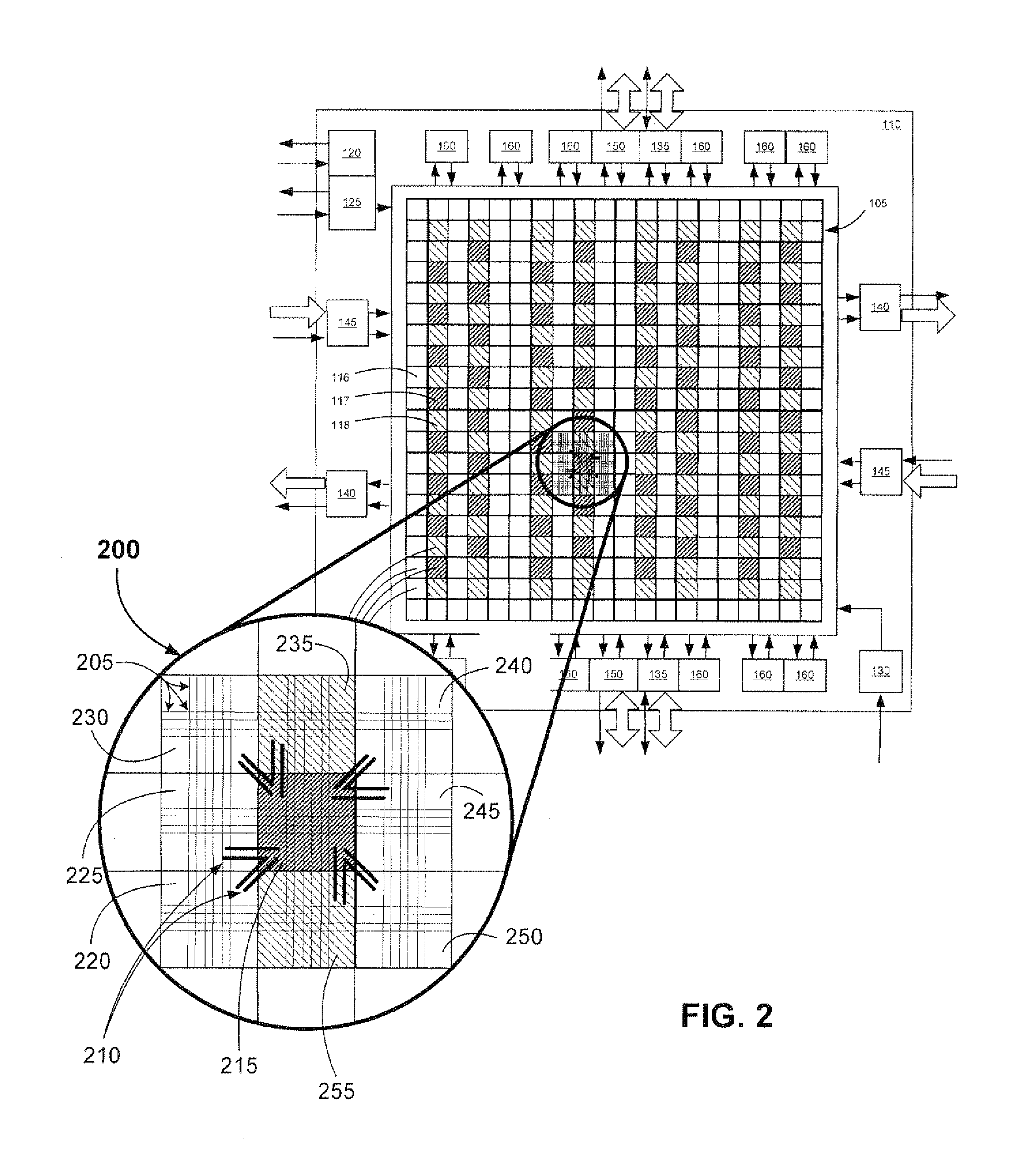

Field programmable semiconductor object array integrated circuit

InactiveUS20070247189A1Facilitating rapid designEasy to implementSolid-state devicesLogic circuits using elementary logic circuit componentsField-programmable object arrayEngineering

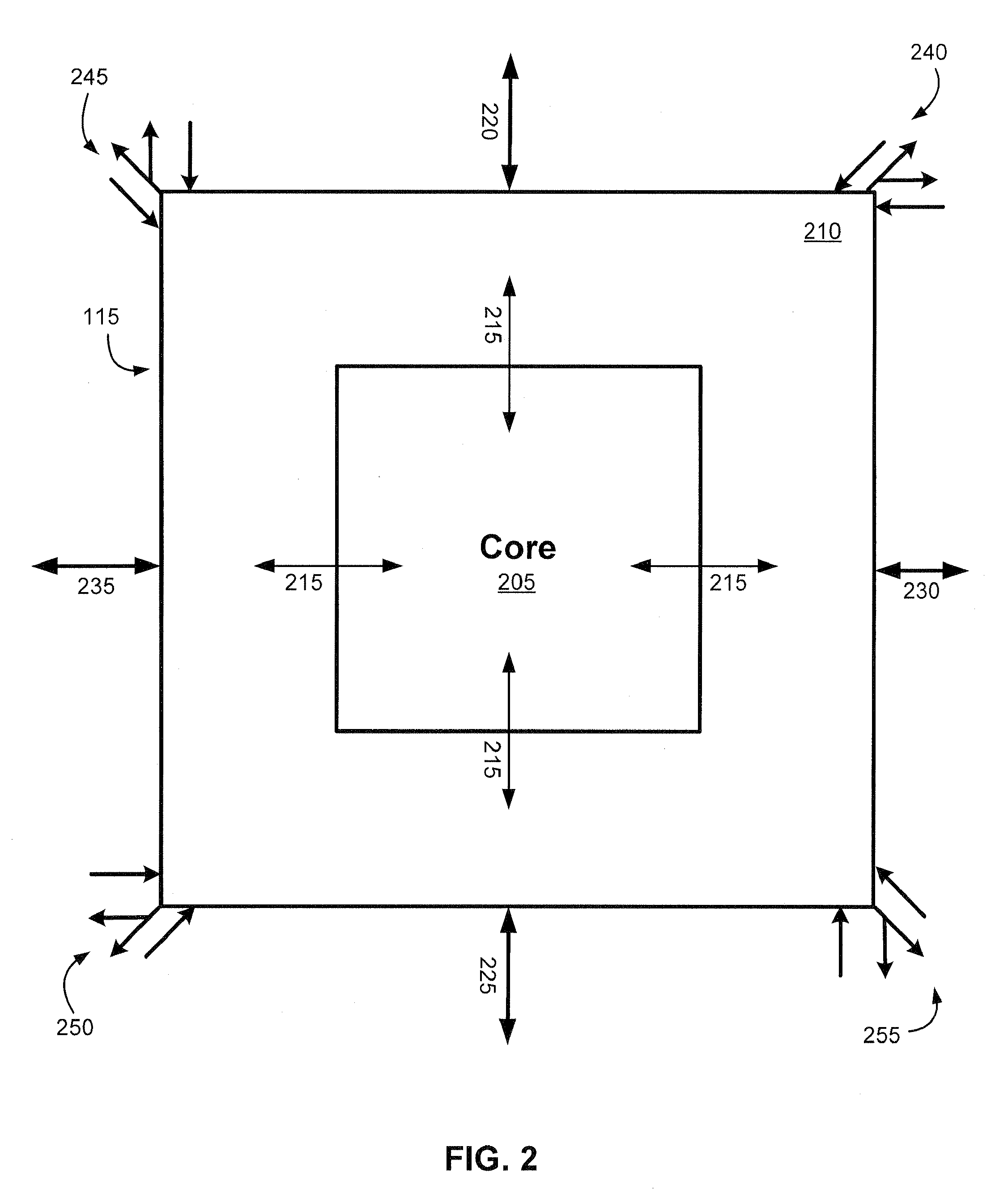

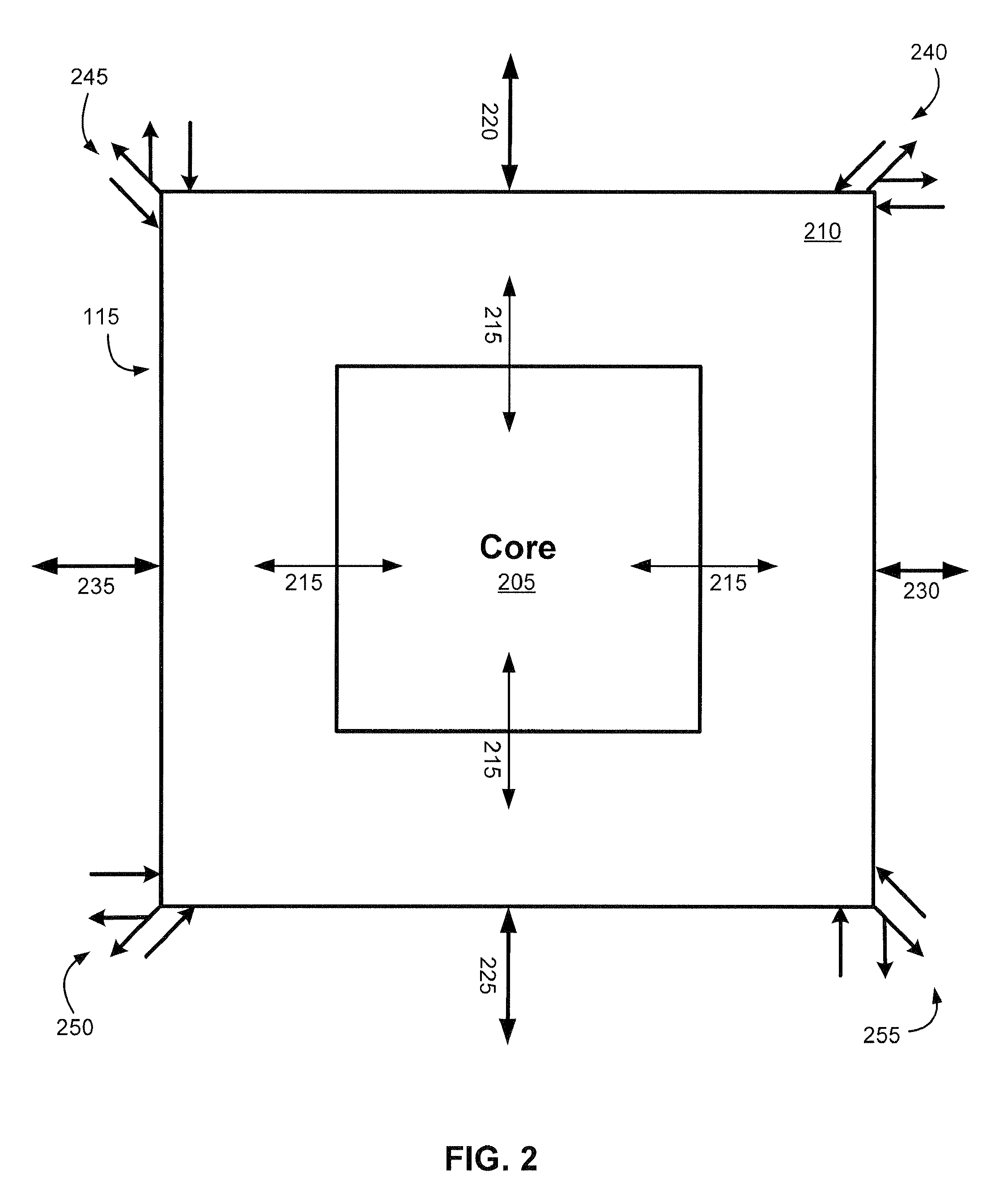

A field-programmable object array integrated circuit employs a course gain architecture comprising a core array of highly optimized silicon objects that are individually programmed and synchronously connected via high performance parallel communications structures permitting the user to configure the device to implement a variety of very high performance algorithms. The high level functions available in the objects combined with the unique interconnect structures enables performance superior to existing field programmable solutions while maintaining and enhancing the flexibility. A consistent peripheral “donut” structure around the core of each object makes them interchangeable to build up complex circuits without redesign of standard objects.

Owner:MATHSTAR +1

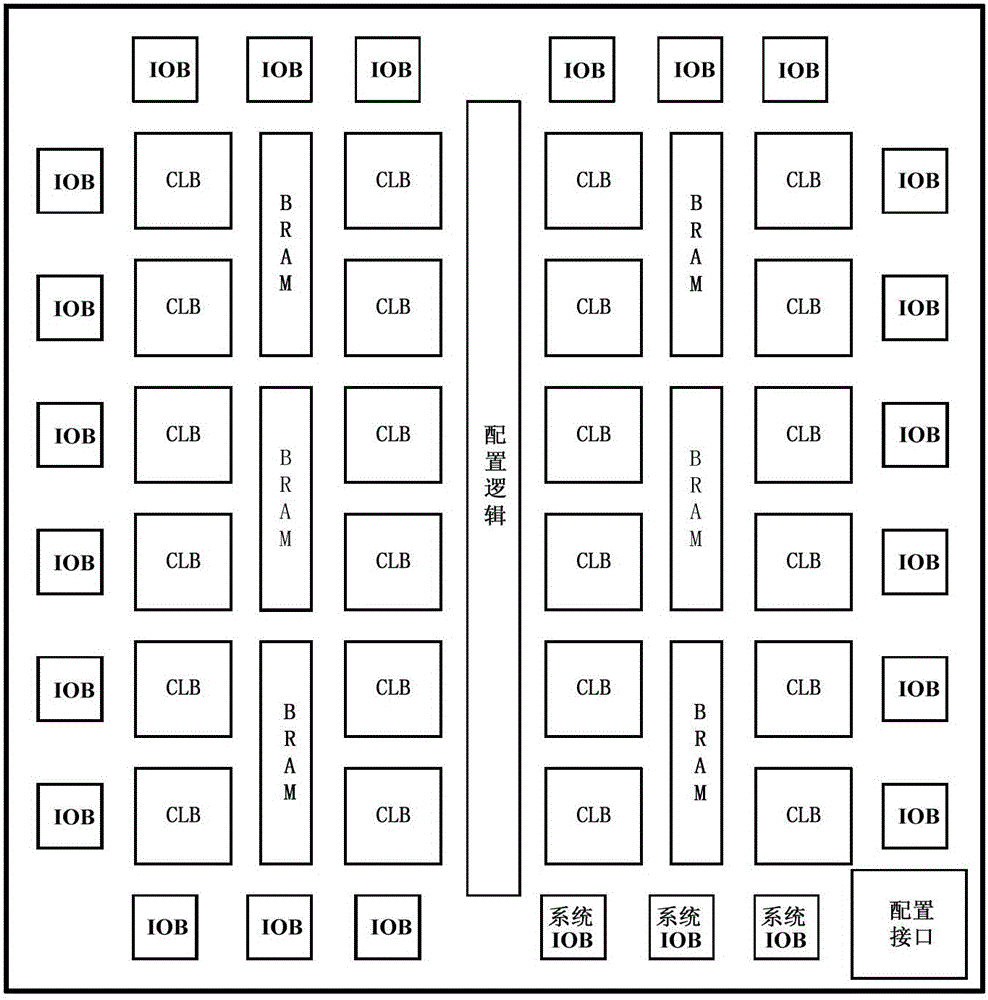

Traversal test method of configurable logic block (CLB) of field programmable gate array (FPGA) based on look-up table structure

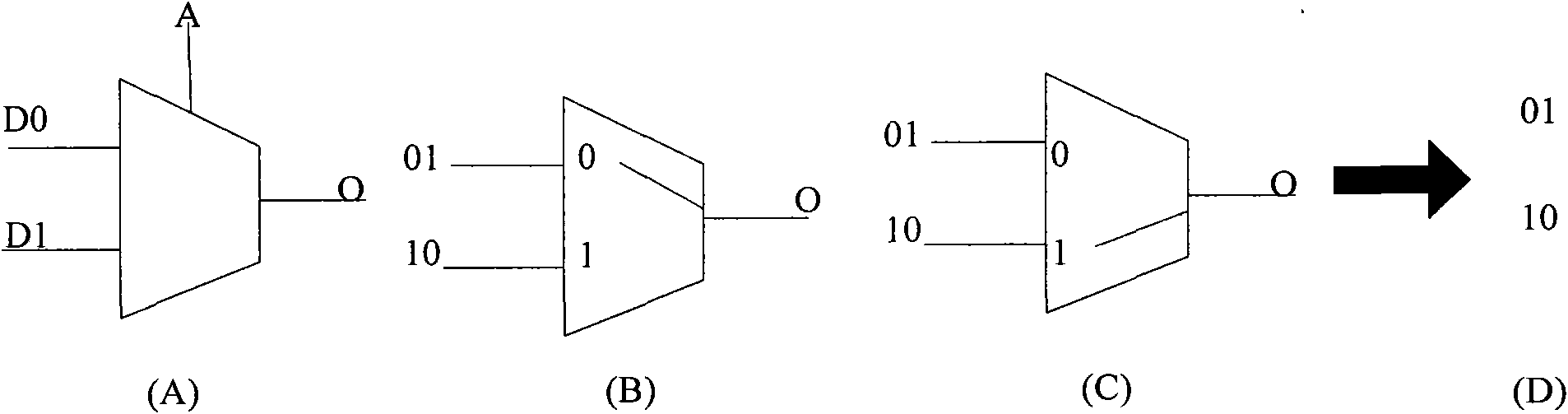

ActiveCN101865977AReduce occupancyRelieve pressureElectrical testingCode pointField-programmable object array

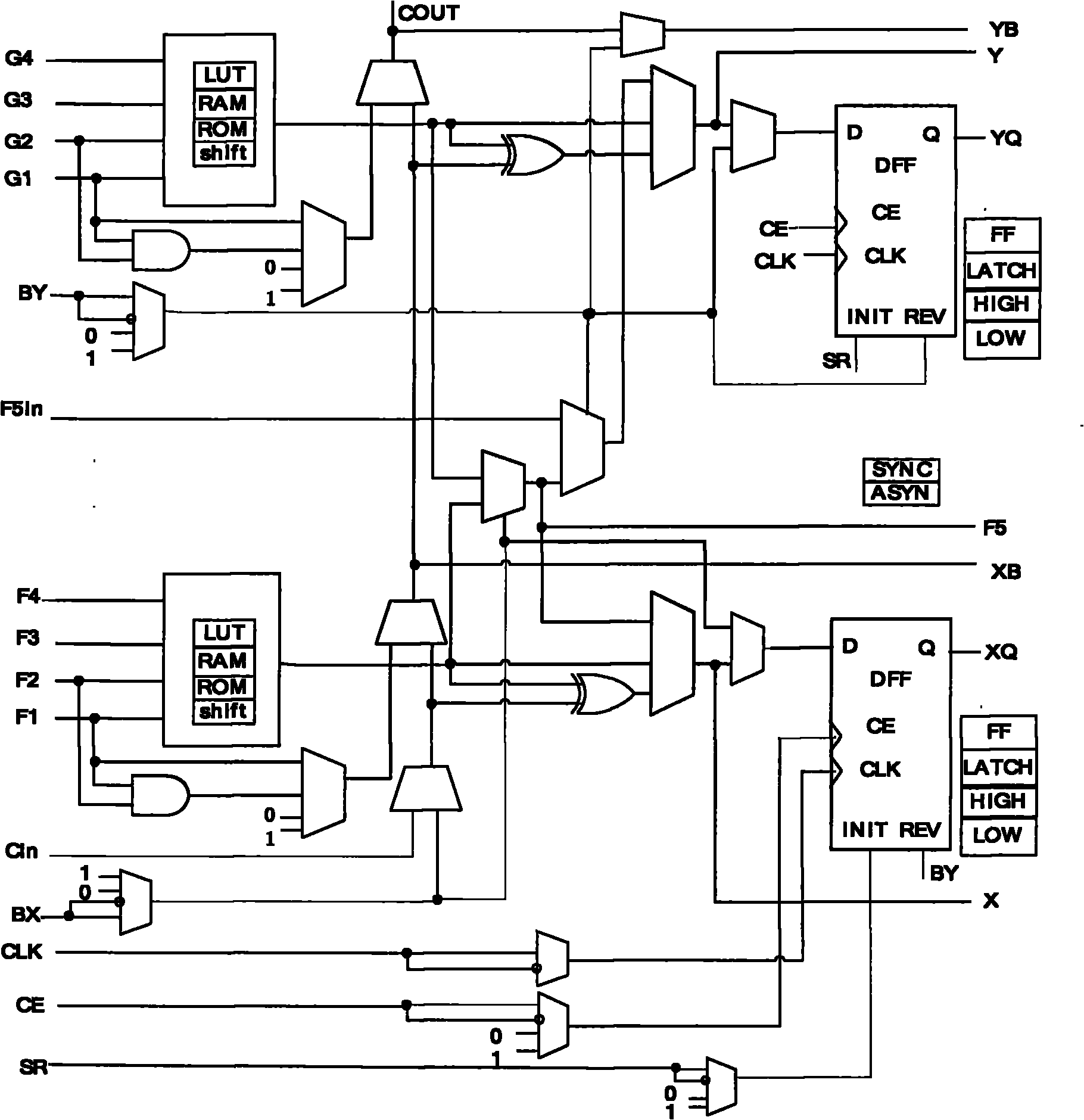

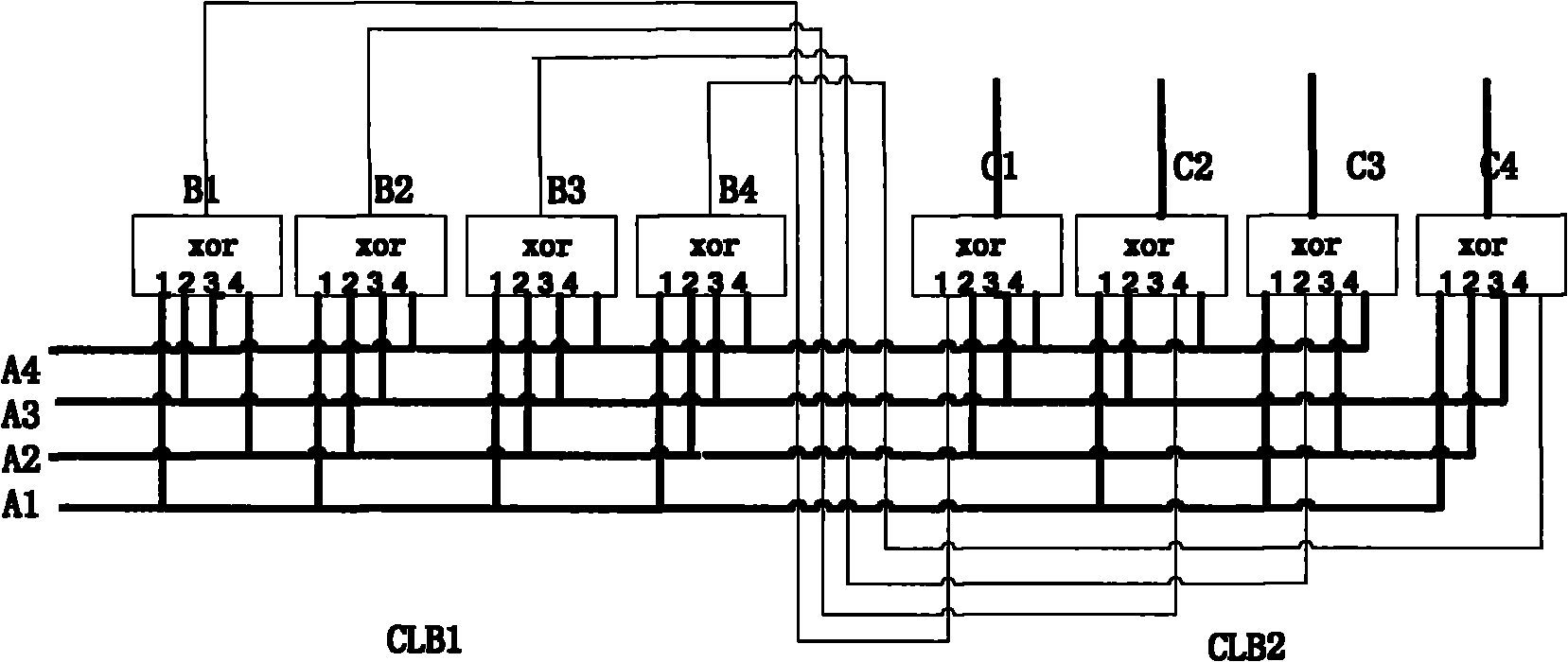

The invention belongs to the technical field of an integrated circuit, in particular to a traversal test method of a configurable logic block (CLB) of a field programmable gate array (FPGA) based on a look-up table (LUT) structure. The method comprises: carrying out traversal tests on the single-point fault of an LUT, testing the multiple-point fault of the LUT, carrying out traversal tests on a distributive RAM, assigning the initial value of the trigger to be 0 or 1, carrying out level fixing on a setting terminal and a resetting terminal, leading the enabling to be invalid, and carrying out traversal tests on setting, resetting and enabling and the like. The invention can complete all the tests on the confronting manufacturing of all the CLBs in FPGA chips, and can cover all the basic logic devices, programmable code points and internal interconnection resources inside the CLBs. The configuration times, configuration difficulty and test time required by the test can all be greatly optimized.

Owner:FUDAN UNIV

Multi-master multi-slave system bus in a field programmable gate array (FPGA)

InactiveUS20020008540A1Programmable logic circuit arrangementsPulse automatic controlData streamField-programmable object array

An embedded system bus is woven between a plurality of embedded master elements and at least one slave element within the FPGA device, and provides an external processor interface allowing direct access to any of the plurality of embedded slave elements. Using the embedded system bus, any of a plurality of masters may be allowed to program an embedded element, e.g., embedded FPGA logic, whereas conventional FPGAs allowed only a single master (e.g., a processor) to program the embedded FPGA logic. The embedded system bus is a group of signals, typically data, address and control, that connects system elements together and provides a basic protocol for the flow of data. The embedded system bus allows for control, configuration and status determination of the FPGA device. The embedded system bus is preferably a dedicated function available at all times for arbitrated access to allow communication between the various embedded system components.

Owner:LATTICE SEMICON CORP

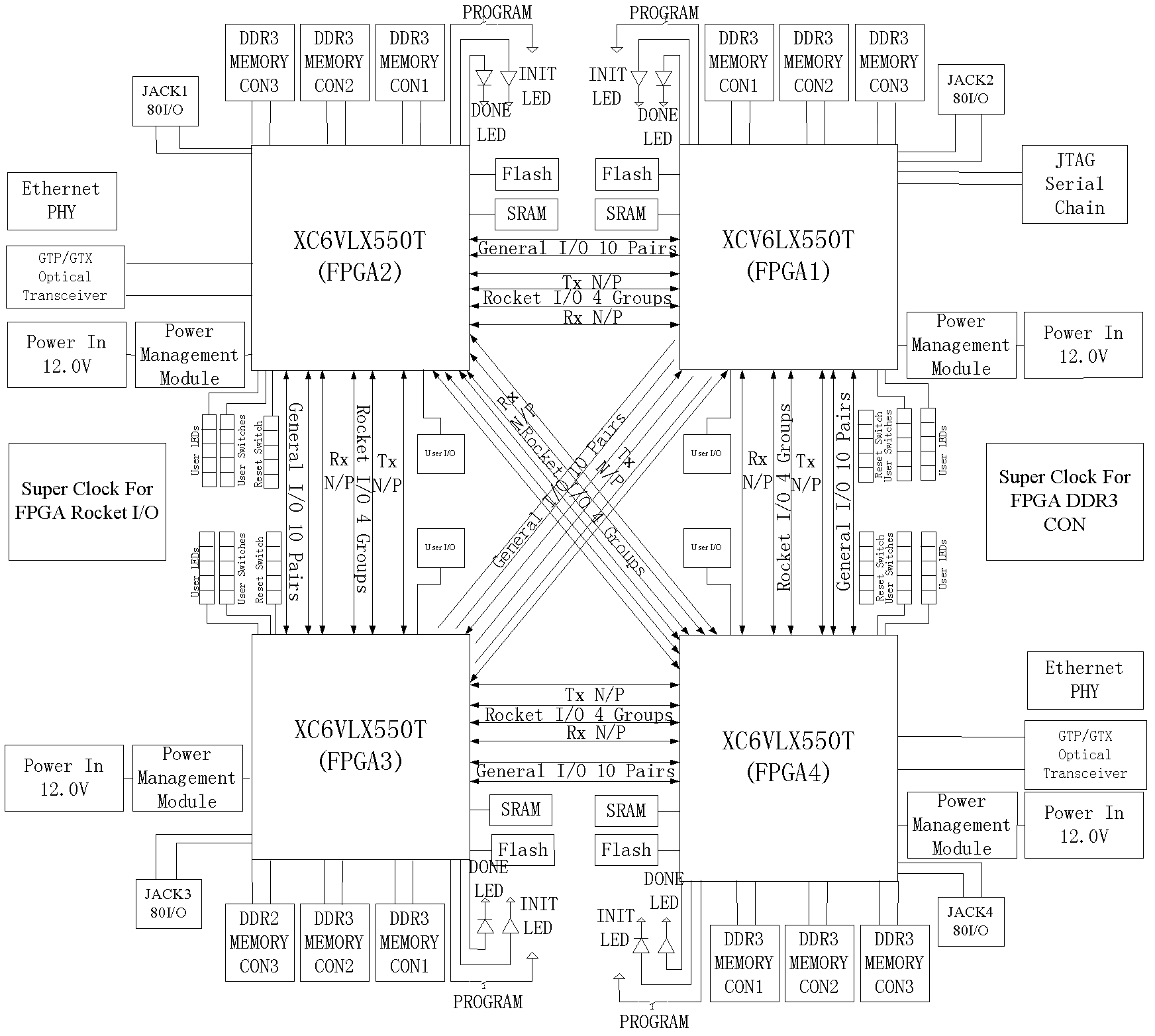

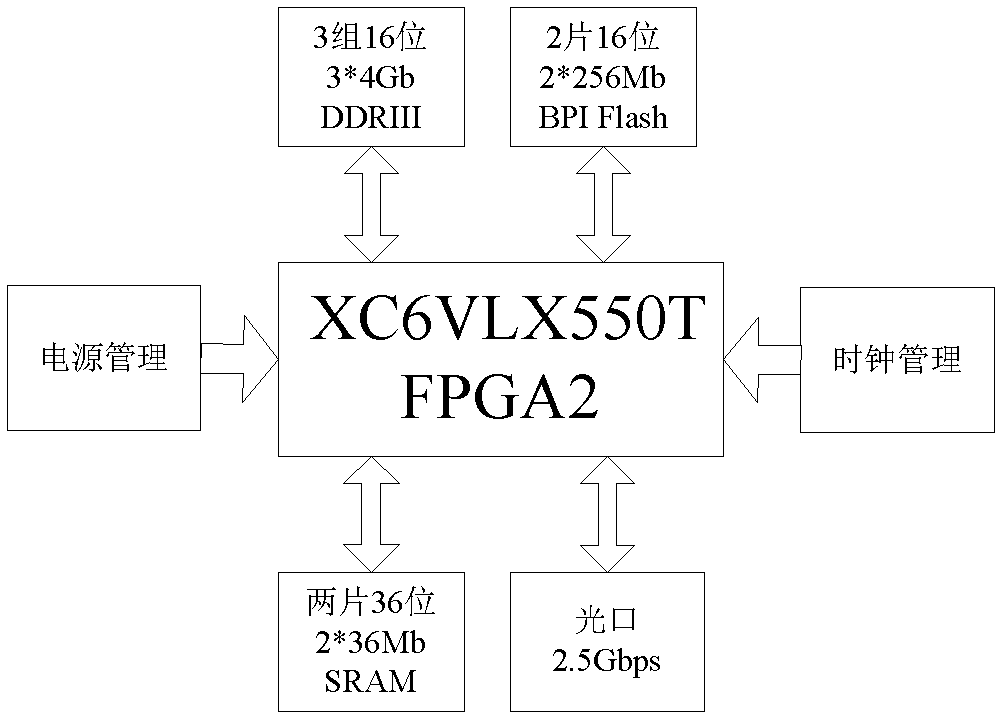

Development board of network multi-core processor on test board based on four field programmable gate arrays (FPGA)

InactiveCN102495568AMeet hardware resource requirementsHigh speed transmissionProgramme controlComputer controlFiberField-programmable object array

The invention discloses a development board of a network multi-core processor on a test board based on four field programmable gate arrays (FPGA). Four FPGA chips are interconnected to form an entire interconnected structure; each FPGA chip is provided with a GTX transmission channel and a GPIO transmission channel which are respectively connected with the other three FPGA chips; and each FPGA chip is provided with a power management module, a board level clock drive module and a memory system. Date input and output ports of the development board are respectively arranged on the second and the fourth FPGA chips; and the data input and output ports are full-duplex differential 2.5Gbps fiber interfaces. The emulated memory bandwidth of the development board reaches 759.2Gbps which is far from being achieved by the current circuit designs of the other development boards with multiple FPGAs; with the interconnection of the chips, the throughput is above 30Gbps; and the development board provides enough hardware resource for FPGA hardware designers so as to test and realize the design of a prototype chip of a VL (very large) multi-core processor based on NoC.

Owner:NANJING UNIV

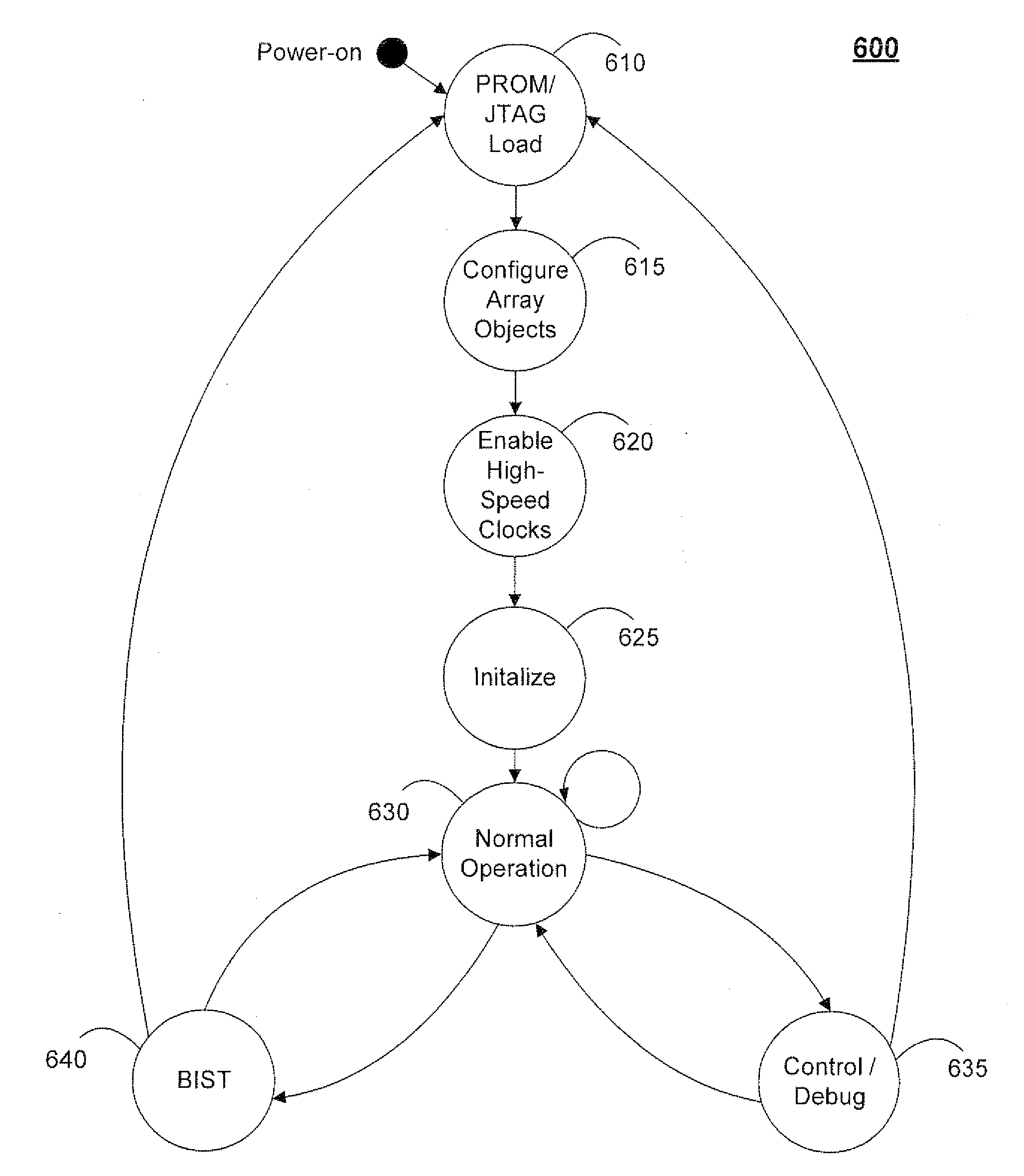

Built-in self-testing (BIST) of field programmable object arrays

InactiveUS20090144595A1Control power consumptionLow heat generationElectronic circuit testingFunctional testingField-programmable object arrayComputer science

A field programmable object array integrated circuit has built-in self-testing capability. The integrated circuit comprises an array of programmable objects, a plurality of interfaces, and a controller. The array of objects is designed to operate at an operational clock speed during non-testing operation, wherein the design of the objects is not constrained to require within an object extra circuitry not essential to non-testing operation to facilitate built-in self-testing. The interfaces are connected to the objects to enable communication with the objects and to thereby facilitate built-in self-testing of the objects. The controller causes a selected subset of the objects to be activated and configured for testing, to stimulate the selected subset for some time with an input test pattern delivered via the interfaces while the selected subset of objects operates at the operational clock speed, and to observe a response of the selected subset of objects.

Owner:MATHSTAR +1

Universal dynamic aging system for Virtex-5 FPGAs (field programmable gate arrays)

InactiveCN106569124ASolve non-universal problemsSolve the problem of lack of accurate measurement means of chip junction temperatureDigital circuit testingField-programmable object arrayEngineering

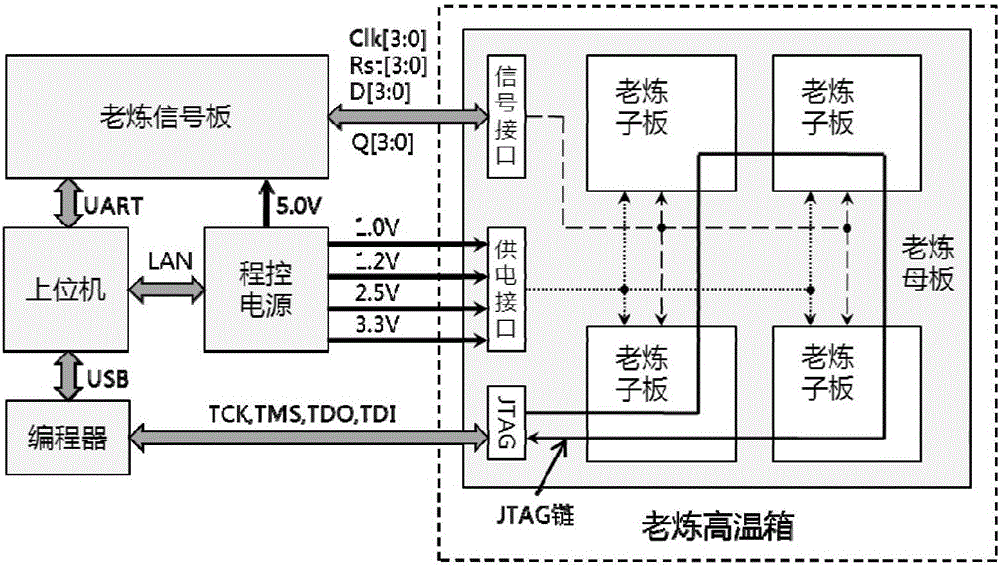

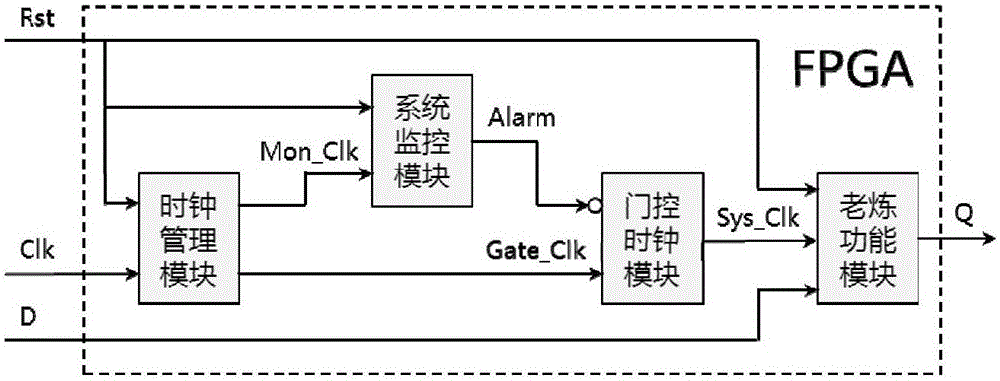

The invention relates to a universal dynamic aging system for Virtex-5 FPGAs (field programmable gate arrays). The universal dynamic aging system for the Virtex-5 FPGAs includes an upper computer, a program-controlled power source, a programmer, an aging signal board, a high temperature test box, an aging test board and an aging FPGA; the upper computer generates a power-on instruction, sends an aging FPGA configuration bit stream, receives and displays aging response data; the program-controlled power source supplies power; the programmer completes the bit stream configuration of the aging FPGA; the aging signal board generates aging excitation signals; the high temperature test box adjusts the temperature of the aging signal board and the aging FPGA; and the aging FPGA includes a clock management module, a system monitoring module, a clock gating module and an aging function module. According to the universal dynamic aging system for the Virtex-5 FPGAs (field programmable gate arrays), the status of the aging function module is automatically adjusted according to the temperature of a chip, and aging response data are generated.

Owner:CHINA ACADEMY OF SPACE TECHNOLOGY

Field programmable gate array (FPGA) online configuration method

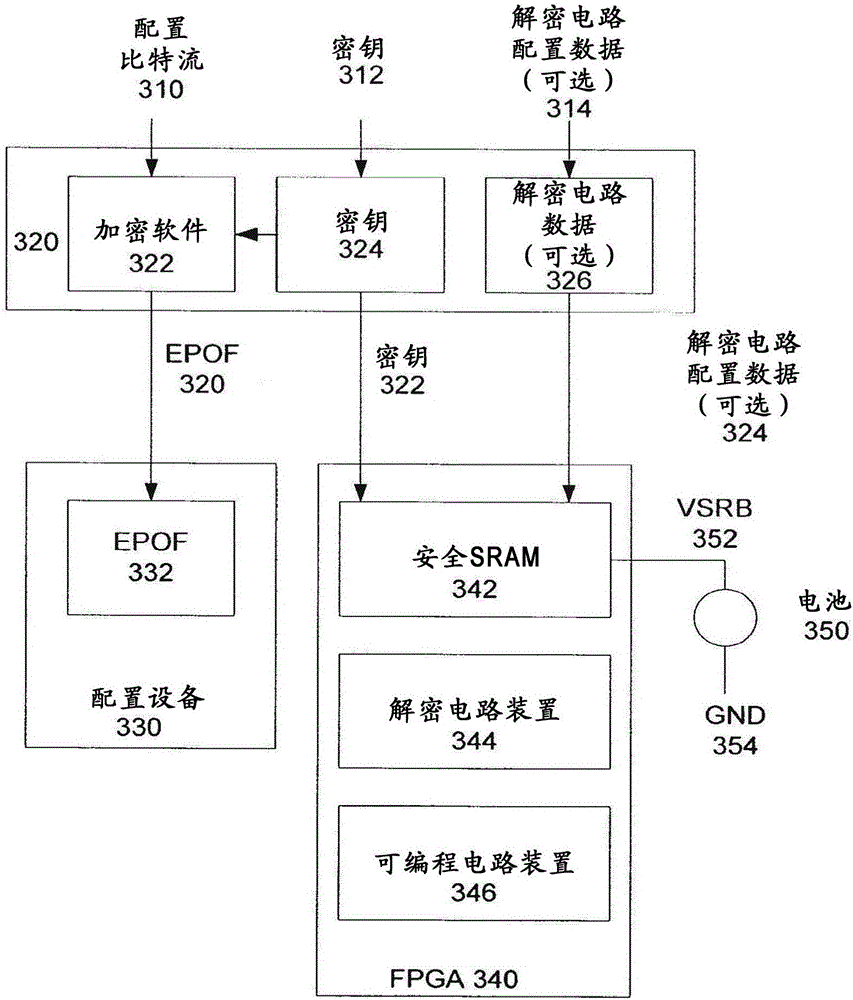

InactiveCN102377423ALow costAchieve confidentialityLogic circuits using elementary logic circuit componentsField-programmable object arrayConfidentiality

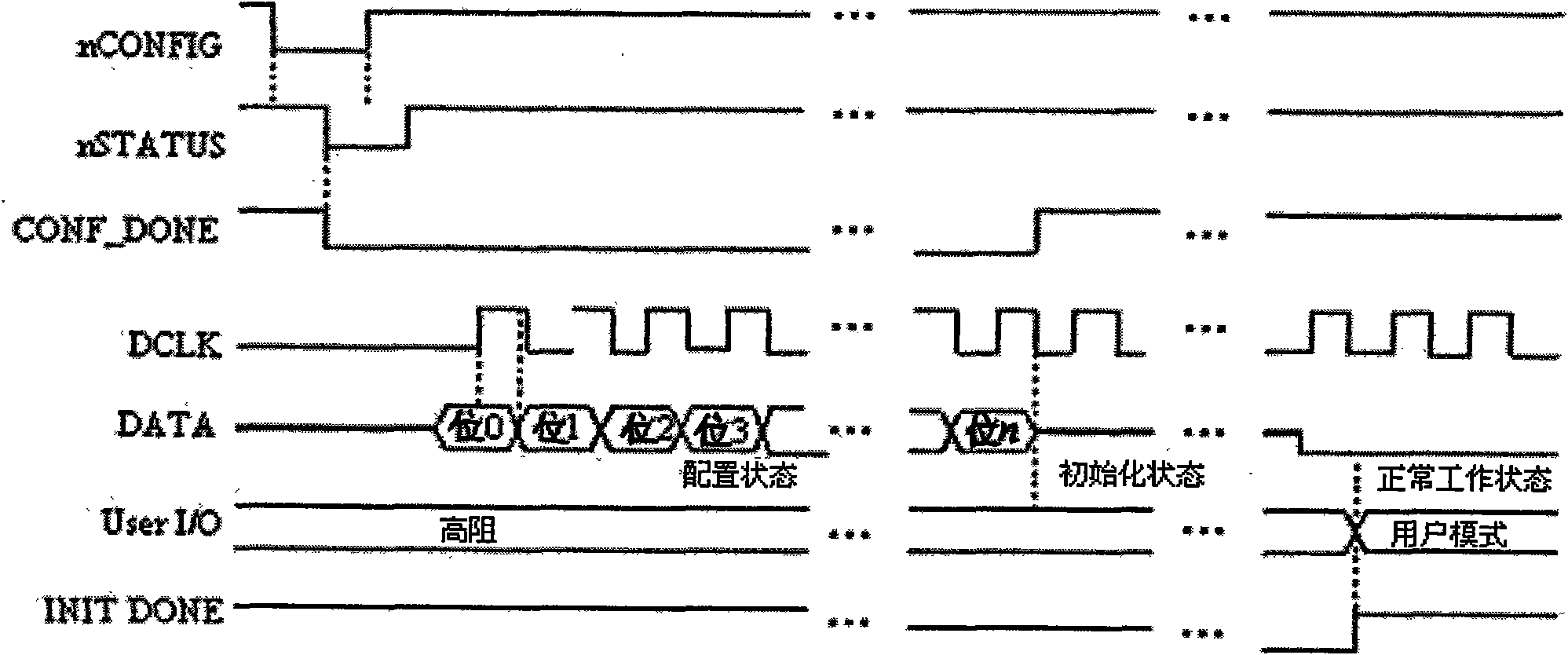

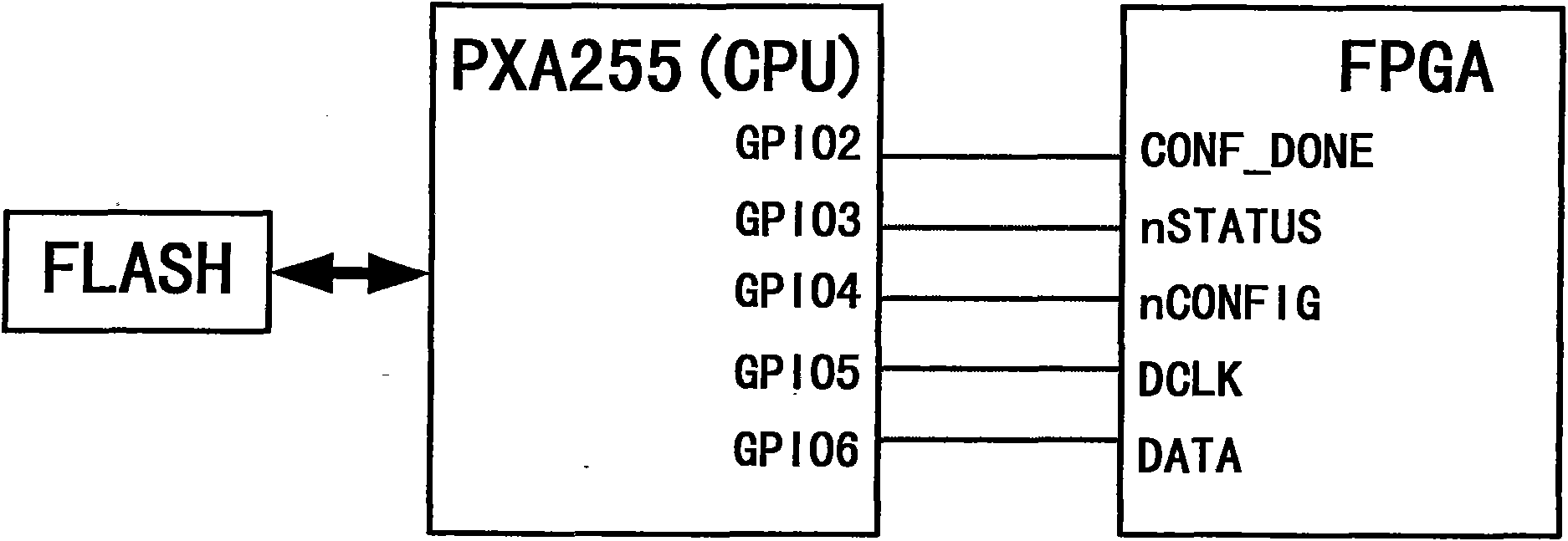

The invention discloses a field programmable gate array (FPGA) online configuration method. The method comprises the following steps of: connecting a central processing unit (CPU) and a storage in which FPGA configuration data is stored, and FPGA respectively, and connecting a general purpose input / output (GPIO) of the CPU and a pin of load data of the FPGA; retrieving configuration data from the storage by the CPU; and finishing loading the configuration data by controlling the time sequence relationship of the GPIO in a passive serial (PS) mode. By the method, cost can be reduced in the design, expensive non-erasable and erasable configuration chips can be replaced, the confidentiality and upgradeability requirements of the design can be met, and the updating of product software can be finished at any time by easily copying a file.

Owner:PANDA ELECTRONICS GROUP +2

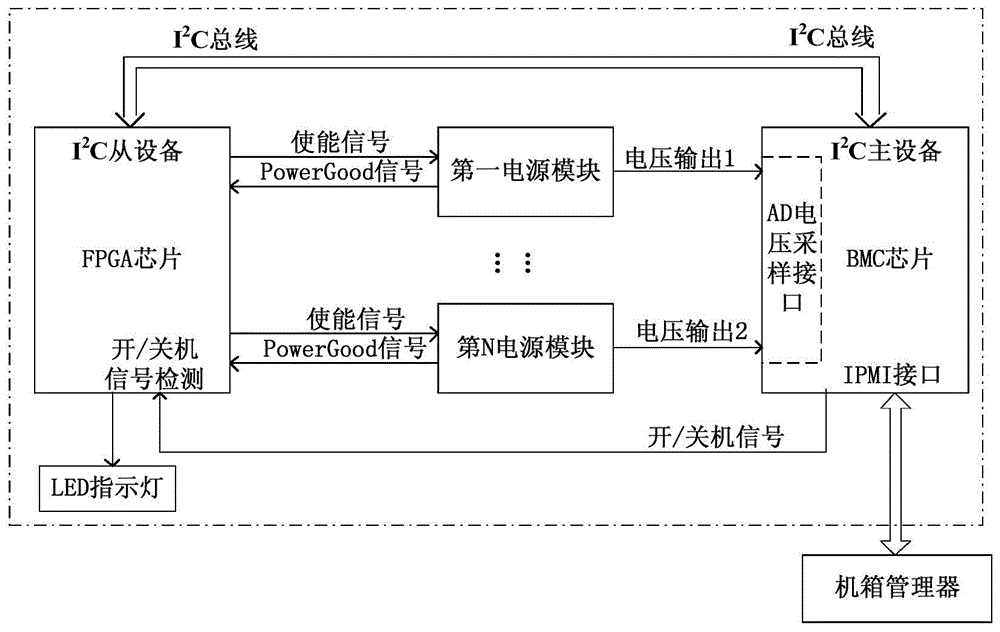

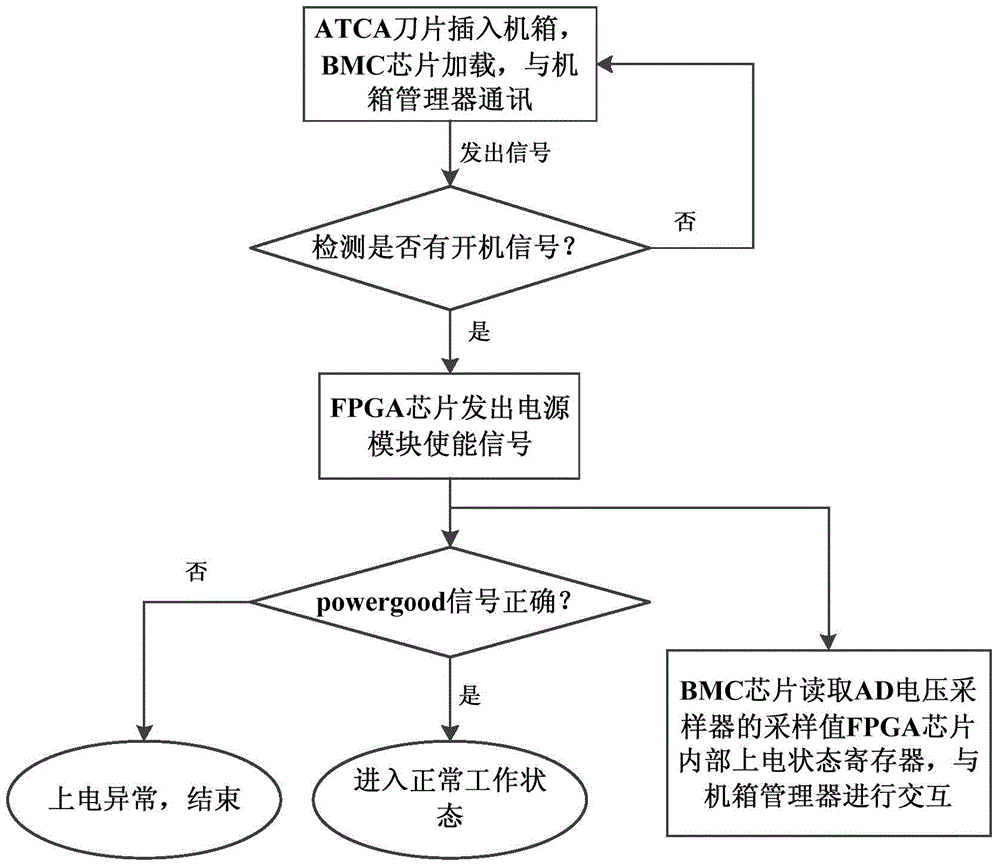

System and method for collaborative power management of FPGA (field programmable gata array) chip and BMC (baseboard management controller) chip used on ATCA (advanced telecom computing architecture) blade

ActiveCN103605596ASave power-on stateAvoid searchingHardware monitoringElectricityField-programmable object array

The invention provides a system and a method for collaborative power management of an FPGA (field programmable gata array) chip and a BMC (baseboard management controller) chip used on an ATCA (advanced telecom computing architecture) blade. The system comprises the FPGA chip, the BMC chip, N power modules and a cabinet manager. Enable pins and Power Good pins of the N power modules are respectively connected with IO (in-out)pins of the FPGA chip, output ends of the N power modules are all connected on an AD (analog-digital) sampling interface of the BMC chip, and the FPGA chip and the BMC chip are communicated through a I2C (inter-integrated circuit) bus. The cabinet manager and the BMC chip are connected bidirectionally. By the aid of the system and the method, whether or not power-on of the FPGA chip is normal is indicated according to state of an LED (light-emitting diode) indicator light, searching power failure by using hardware tools can be further avoided as far as possible, so that troubleshooting becomes simple and high-efficient.

Owner:DAWNING INFORMATION IND BEIJING +1

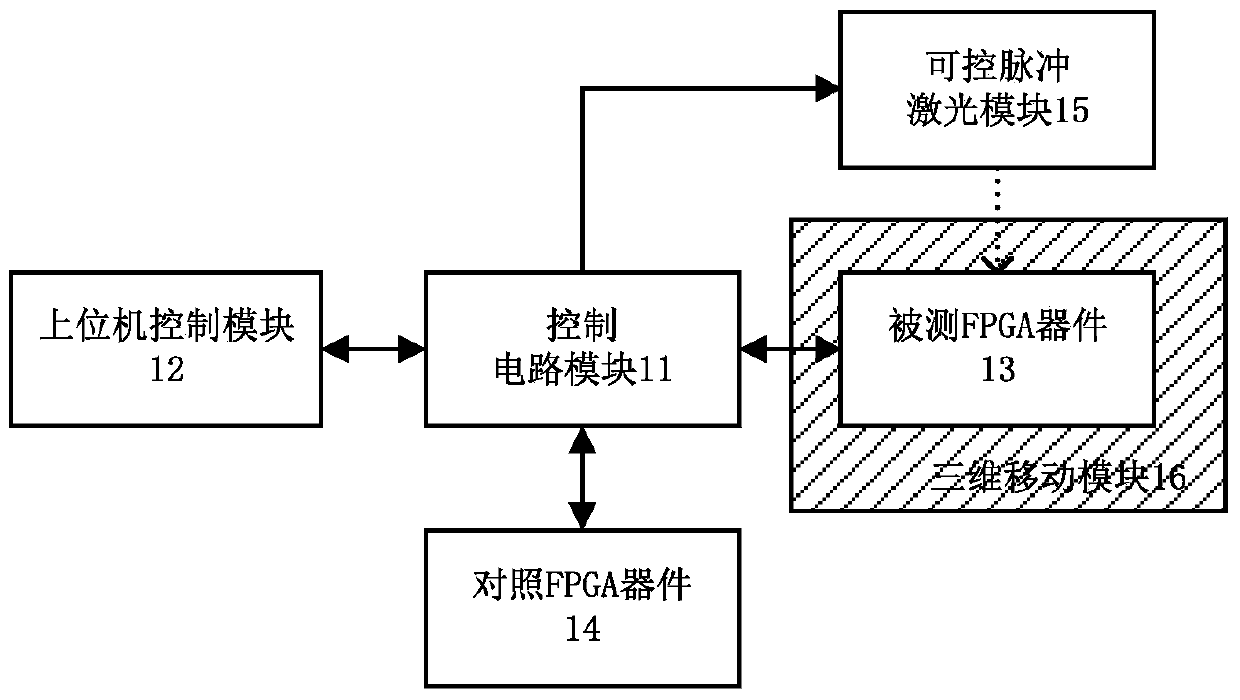

Device and method for field programmable gate array (FPGA) single event effect dynamic fault testing

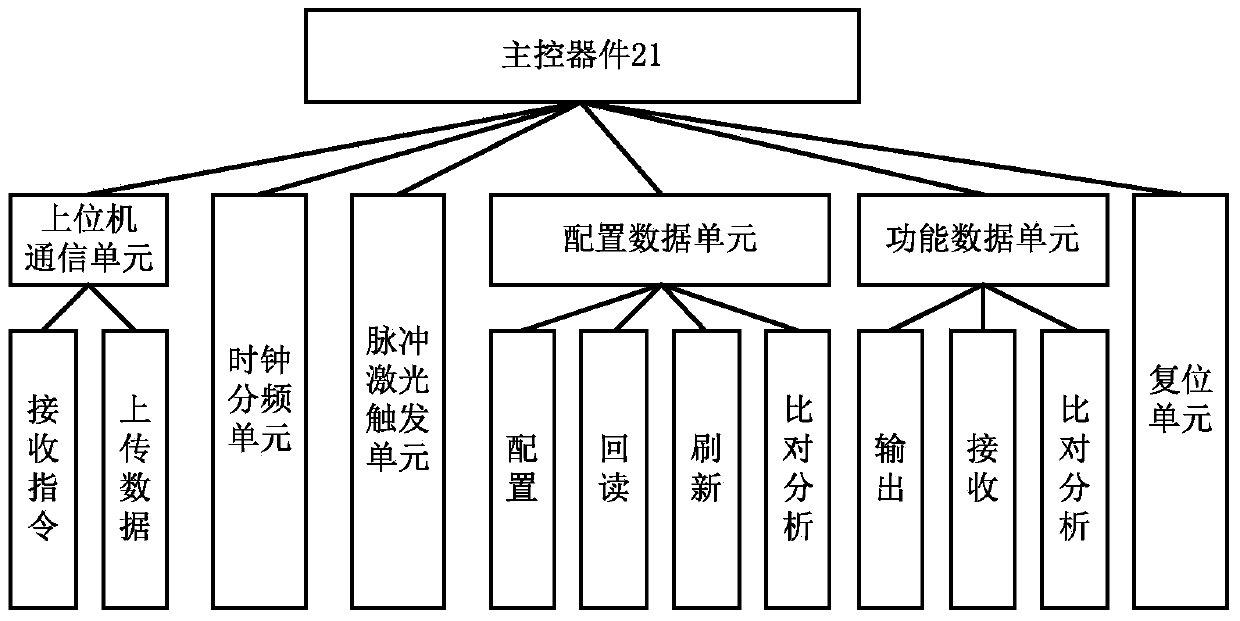

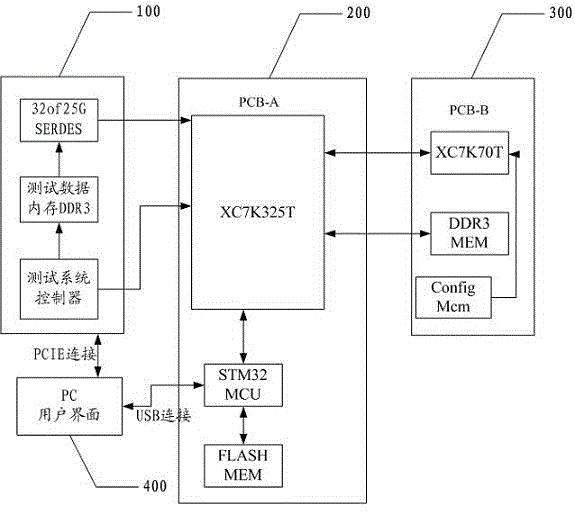

ActiveCN104181421APrecise positioningTrigger controllableElectrical testingField-programmable object arrayControl circuit

The invention relates to a device for field programmable gate array (FPGA) single event effect dynamic fault testing. The device comprises a control circuit module (11), an upper computer control module (12), a controllable pulse laser module (15) and a three-dimensional mobile module (16), wherein the three-dimensional mobile module (16) is used for installing a tested FPGA device (13) to be tested during the testing; the upper computer control module (12) is connected with the control circuit module (11), and the control circuit module (11) is connected to the controllable pulse laser module (15). During the testing, the control circuit module (11) is further connected with the tested FPGA device (13) and a contrast tested FPGA device (14) corresponding to the tested FPGA device (13).

Owner:NAT SPACE SCI CENT CAS

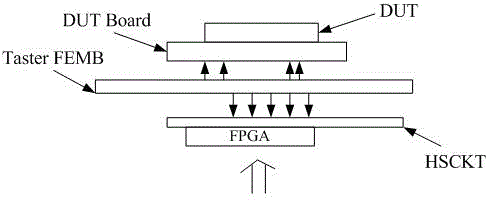

Testing device based on FPGA (field programmable gate array)

InactiveCN104569780AReduce power consumptionImprove performanceElectronic circuit testingLow speedField-programmable object array

The invention discloses a testing device based on FPGA (field programmable gate array). The corresponding testing device which is designed innovatively through an FPGA circuit and adjustability of an output and input standard and a mode replaces corresponding electronic circuits of an existing testing device. The performance is greatly improved, and meanwhile, the power consumption of the circuit and the physical size and the cost of key design are greatly reduced. Additionally, the high-speed data transmission performance of the FPGA is innovatively used for transmitting a large quantity of test data to a device directly connected with a tested element at a high speed, and one of the bottlenecks of miniaturization of the key design is eliminated. Further, a circuit related with a direct-current and low-speed performance test and a high-speed test circuit are completely separated and are connected with the tested element during the test of each of the circuits, so the two circuits are not mutually influenced; the circuits are connected when the circuits need to be connected together for a corresponding test. Therefore, the power consumption, the physical size and the cost are greatly reduced, and the testing device has a good market popularization and utilization prospect.

Owner:SHENZHEN AID TECH

Testing and locating method for FPGA (field programmable gate array) programmable logic unit

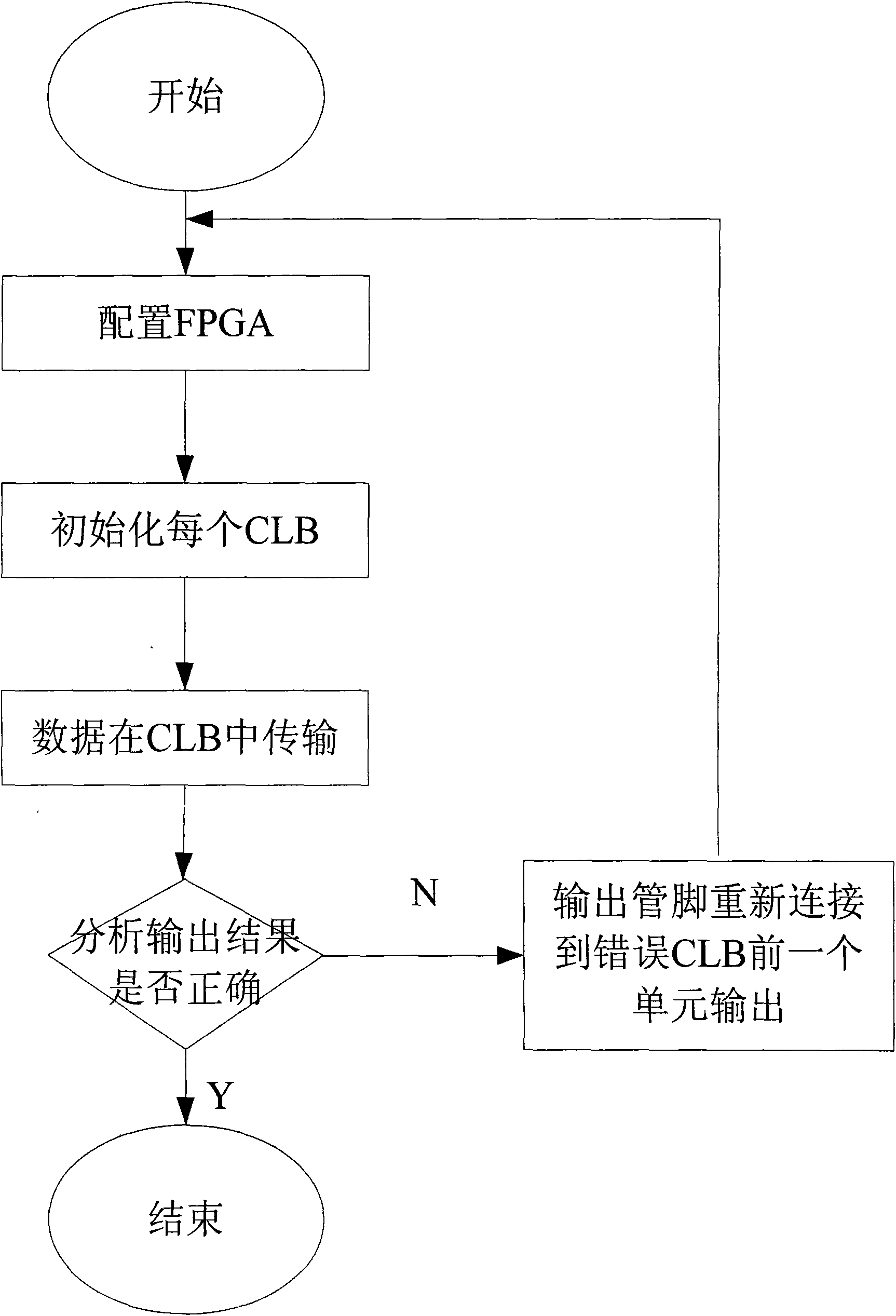

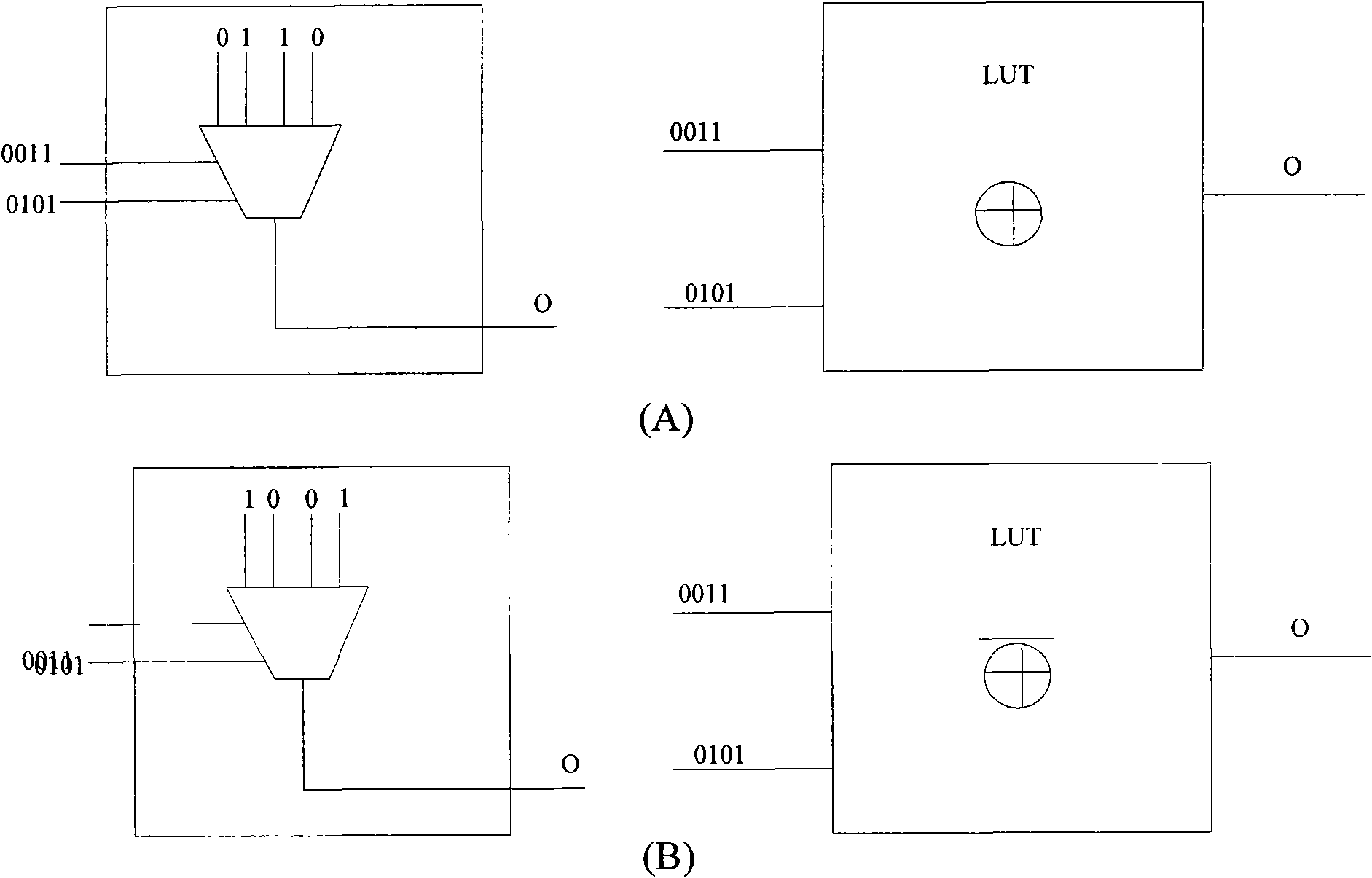

ActiveCN102841306AImprove test efficiencyGuaranteed test coverageElectrical testingProgrammable logic controllerLogic cell

The invention discloses a testing and locating method for an FPGA (field programmable gate array) programmable logic unit, comprising the following steps of: (1) arranging and configuring an FPGA logic unit; (2) initializing a CLB (configurable logic block) in the FPGA unit; and (3) testing and locating an error CLB module. By adopting the technical scheme of the invention, configuration frequency in a CLB testing process is reduced by more than 10 times, and CLB testing efficiency is greatly improved; and error locating in a process of testing the CLB unit in the FPGA is realized.

Owner:BEIJING UPTOPS DESIGN TECH

System and method for debugging FPGA (field programmable gate array) in real time

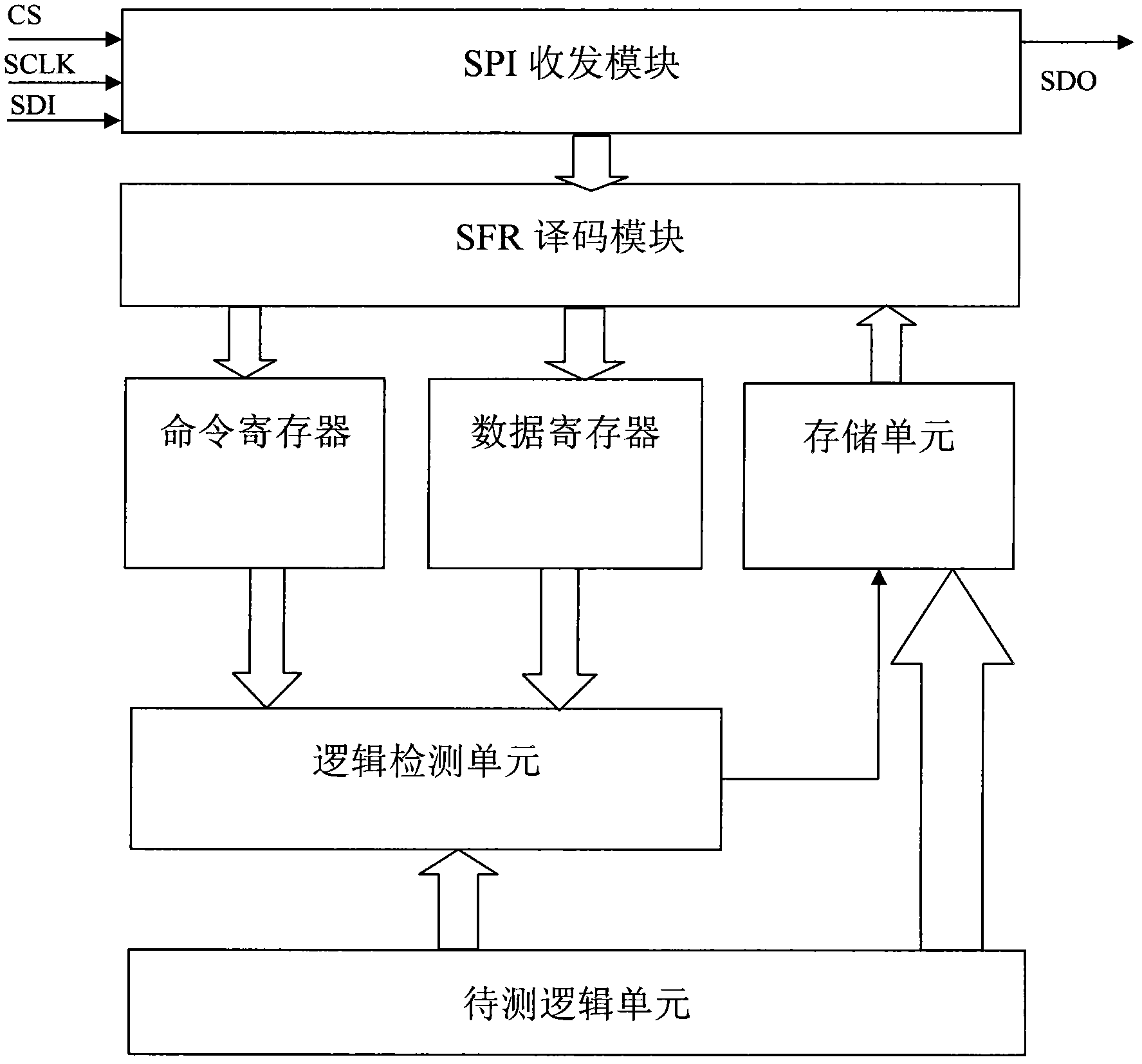

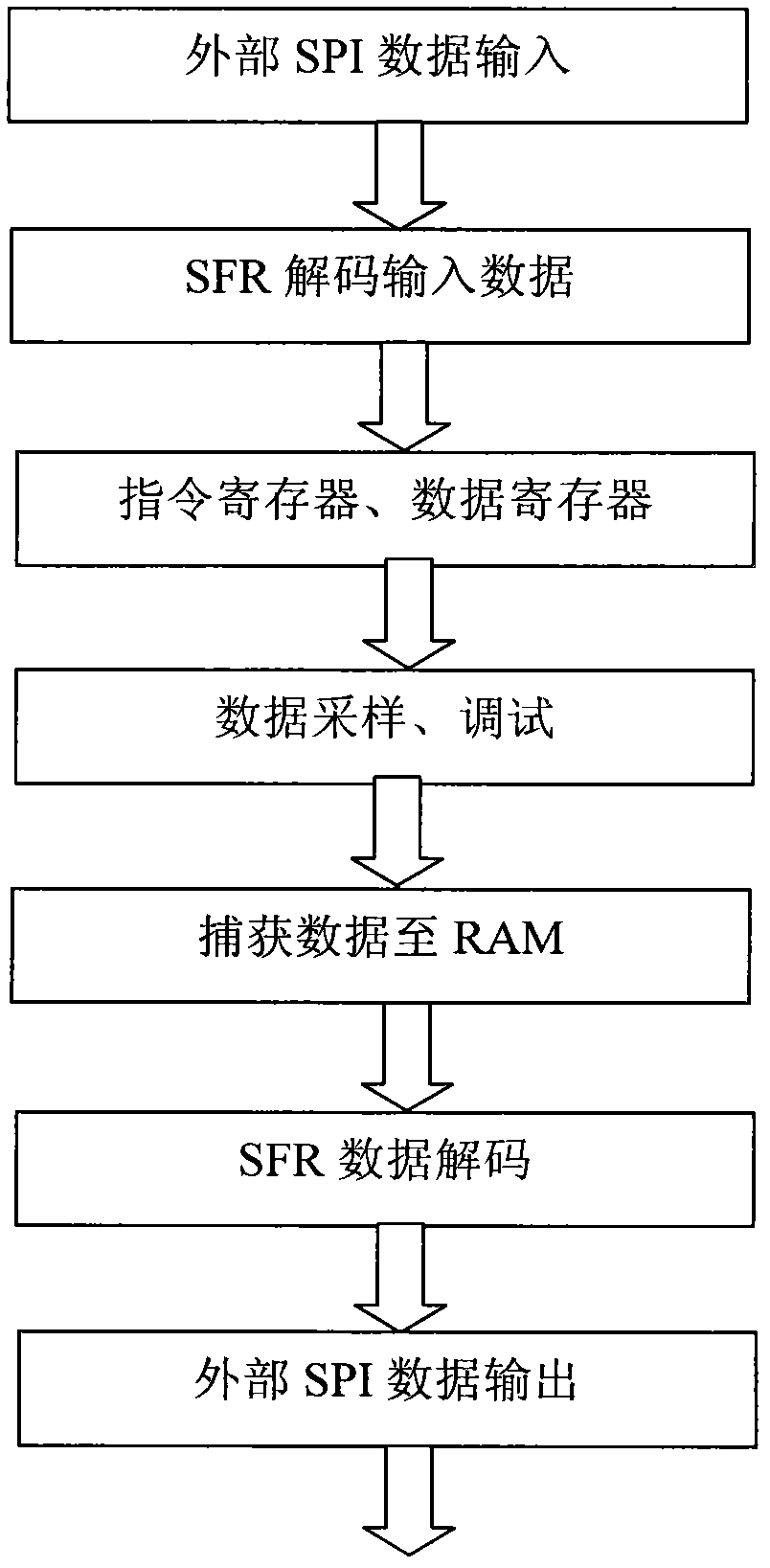

InactiveCN102841305AHigh speed designDigital circuit testingSpecial function registerField-programmable object array

The invention discloses a system for debugging FPGA (field programmable gate array) in real time, comprising an SPI (serial peripheral interface) transceiving module, an SFR (special function register) decoding module, a data storing unit and a logic detection unit, wherein the SPI transceiving module is used for receiving external data to form a detection command and detection data and sending an internal detection result and internal storage data; the SFR decoding module is used for decoding a register command with special functions; the data storing unit is used for storing specified sampled data; and the logic detection unit is used for being connected with at least one group of logic units to be detected and carrying out real-time verification to obtain a verification result; and the modules and the units are sequentially connected for carrying out data communication. A real-time debugging method of the system comprises the following steps that: the SPI transceiving module receives data of a monitoring system, the data received by the SPI transceiving module is converted into a detection instruction or detection data by virtue of the SFR module, is stored by the data storing unit and then is sent to the logic detection unit, the logic detection unit judges the logic units to be detected, and judgement data and result are stored and then are transmitted by the SPI transceiving module. The system disclosed by the invention takes an SPI bus protocol as a protocol used for realizing data interaction between a basic debugging device and equipment, and high-speed product debugging and verifying design and dynamic check debugging are realized.

Owner:BEIJING UPTOPS DESIGN TECH

FPGA-based (field programmable gate array-based) parallel detection method for thermal protectors in batches

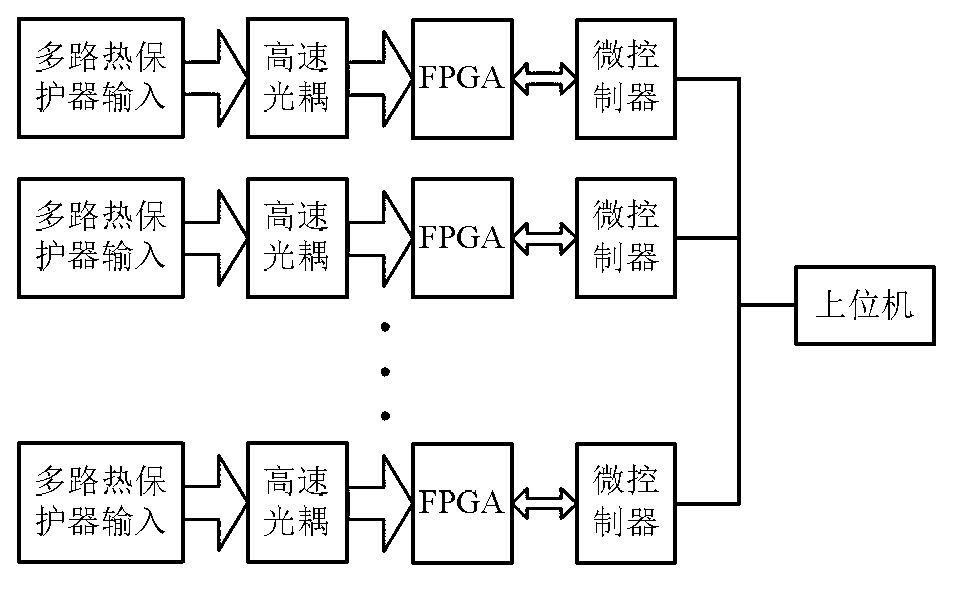

InactiveCN103176123AProcessing speedAccurate detectionProgramme controlComputer controlMicrocontrollerField-programmable object array

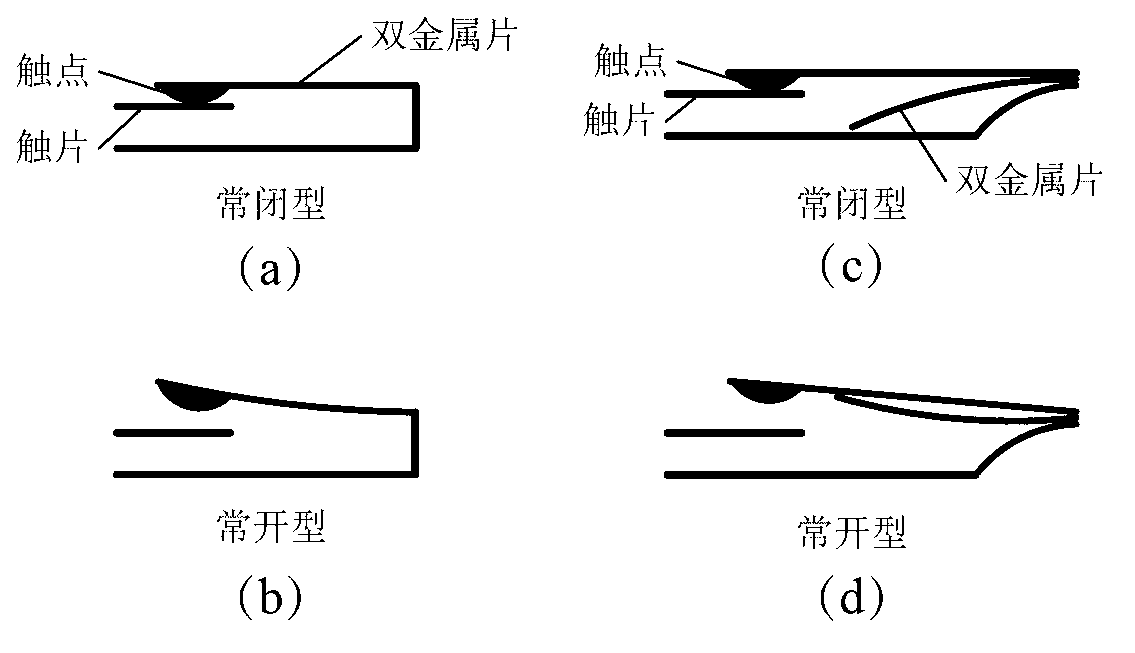

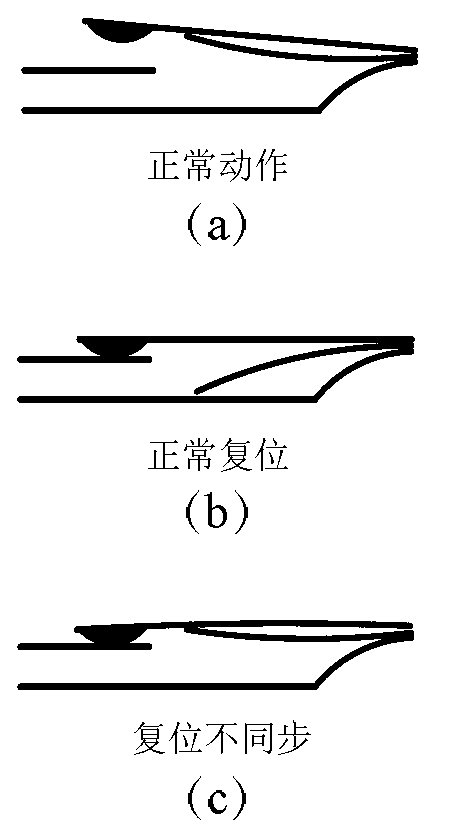

The invention discloses an FPGA-based (field programmable gate array-based) parallel detection method for thermal protectors in batches. The method includes the steps of initializing an FPGA, namely enabling chip selection, selecting normal on and normal off types of thermal protectors and zeroing stored data; allowing the FPGA to parallelly acquire switching states of the thermal protectors to generate flash features for representing the thermal protectors and switching data for asynchronous reset features; allowing the FPGA to analyze the switching data to obtain the flash features of the thermal protectors and the results of judgment on the asynchronous reset features, and storing the features and the results in the FPGA; allowing a microcontroller to read the switching states of the thermal protectors parallelly acquired by the FPGA in a cyclic scanning manner, judging action and reset of the thermal protectors, and controlling oven temperature curves, reading action temperature and reset temperature; after temperature rise and drop are complete in an oven according to the set temperature curves, allowing the microcontroller to read the flash features and the asynchronous reset feature judgment results stored in the FPGA.

Owner:HOHAI UNIV

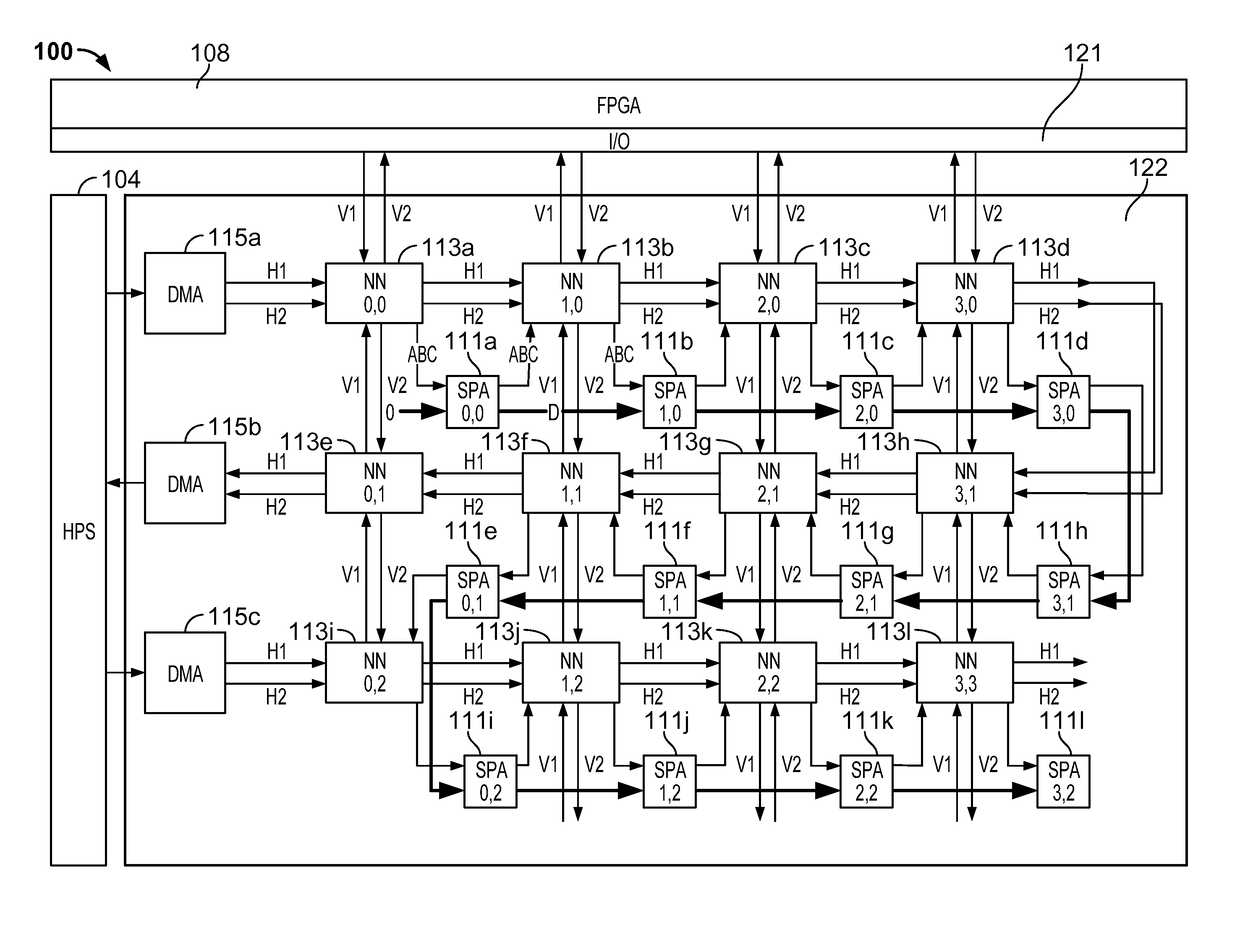

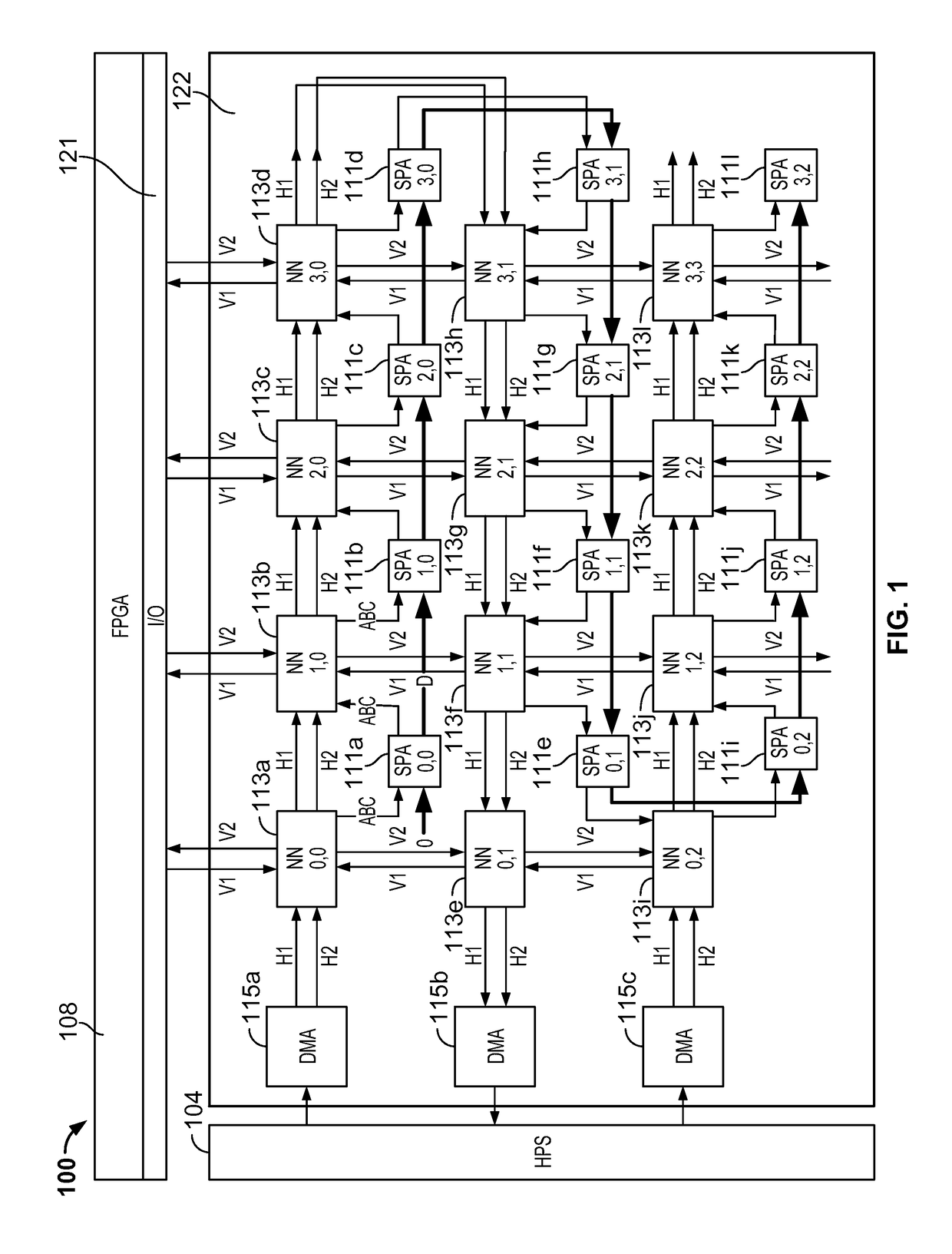

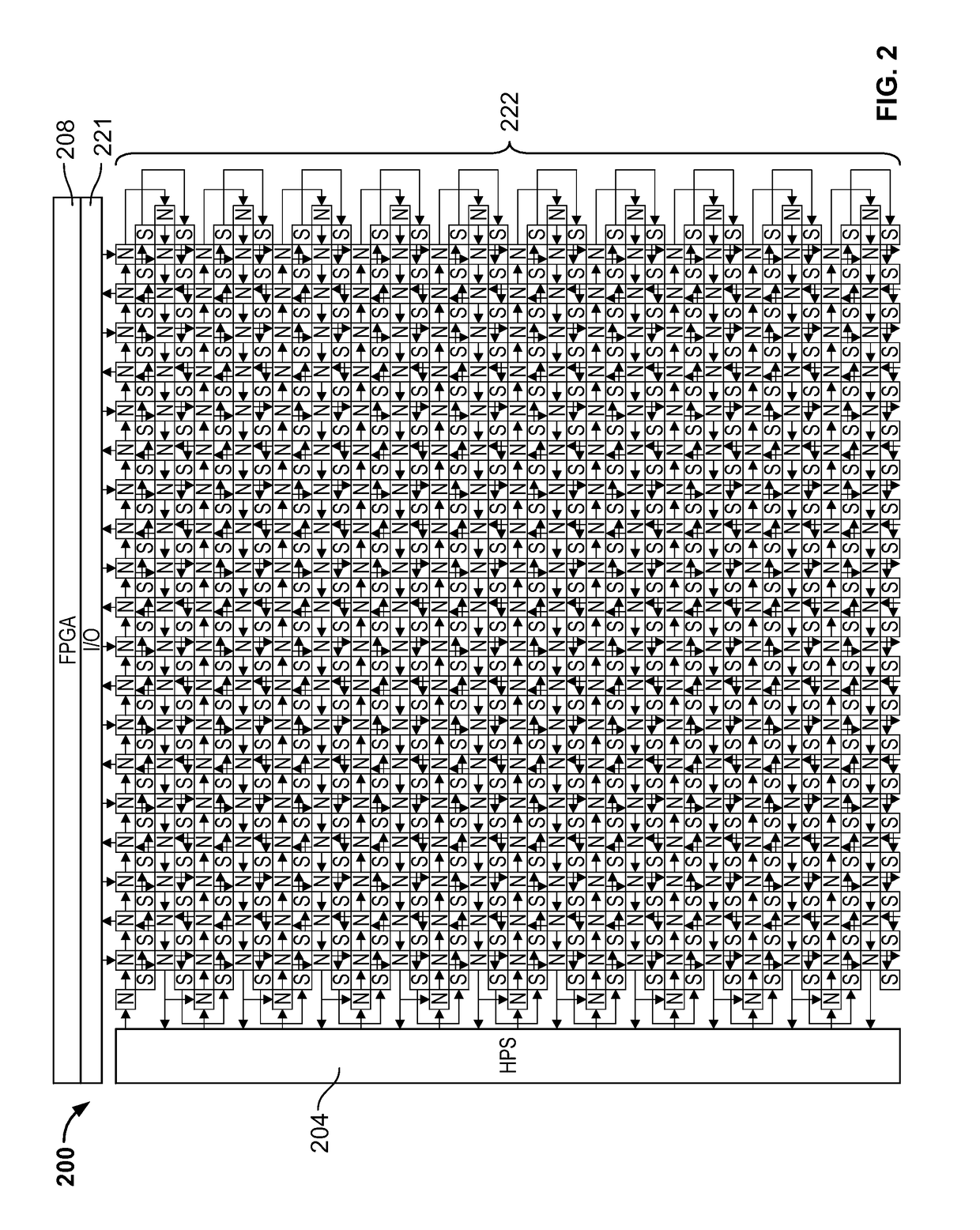

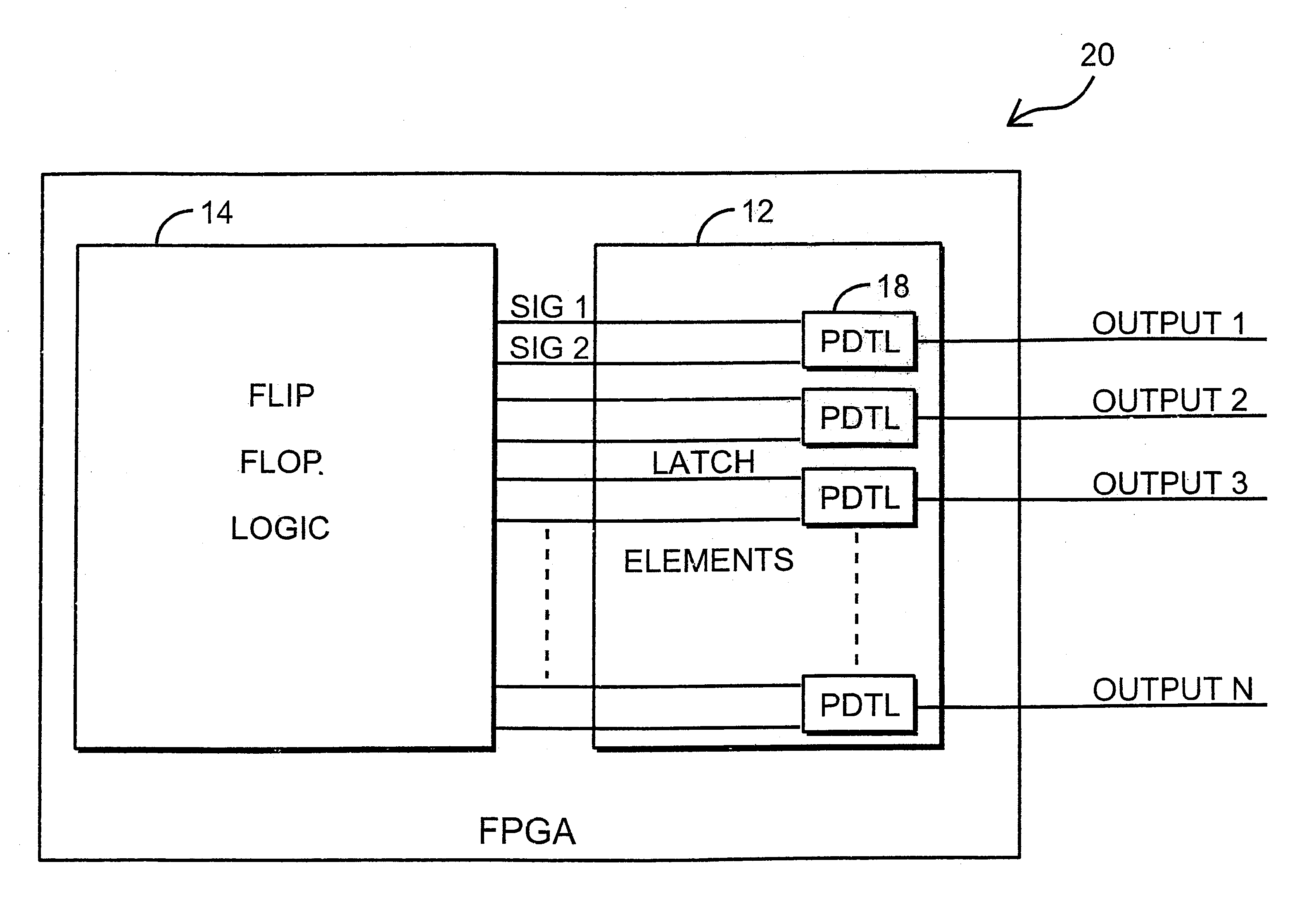

Hybrid architecture for signal processing and signal processing accelerator

ActiveUS9647667B1CAD circuit designEnergy efficient computingSignal routingField-programmable object array

Systems and methods for configuring circuitry for use with a field programmable gate array (FPGA) are disclosed. The circuitry includes an array of signal processing accelerators (SPAs) and an array of network nodes. The array of SPAs is separate from a field programmable gate array (FPGA), and the array of SPAs is configured to receive input signals from the FPGA. The array of network nodes controllably route the input signals to the array of SPAs.

Owner:ALTERA CORP

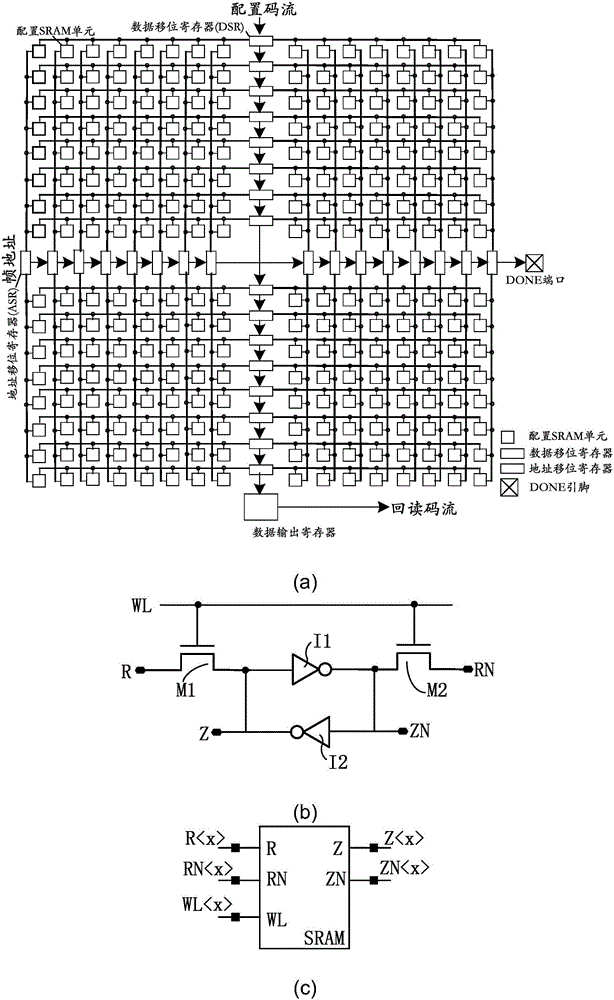

User register state capture circuit adopting single-event hardened FPGA (field programmable gate array)

ActiveCN105702296ANo interruption of user function logic workWide applicabilityDigital storageProcessor registerField-programmable object array

A user register state capture circuit adopting a single-event hardened FPGA (field programmable gate array) comprises a user register, a transistor M3, a transistor M4, an SRAM (static random-access memory) storage unit and a capture signal generation circuit, wherein the transistor M3 and the transistor M4 are arranged between the user register and the SRAM storage unit; the capture signal generation circuit generates an output signal CAPTURE, controls conduction of the transistor M3 and the transistor M4 and realizes data capture readback. Compared with the prior art, the state capture circuit has the advantages that through capture readback operation, dynamic partial reconfiguration can be performed if the condition that configuration bit stream stored in the CSRAM (custom SRAM) has single-event upset is discovered, corresponding logic can be reset if the state of the SRAM storage unit for storing the captured user register state in the CSRAM has an error, so that the single-event upset accumulation effect of an FPGA chip is reduced remarkably.

Owner:BEIJING MXTRONICS CORP +1

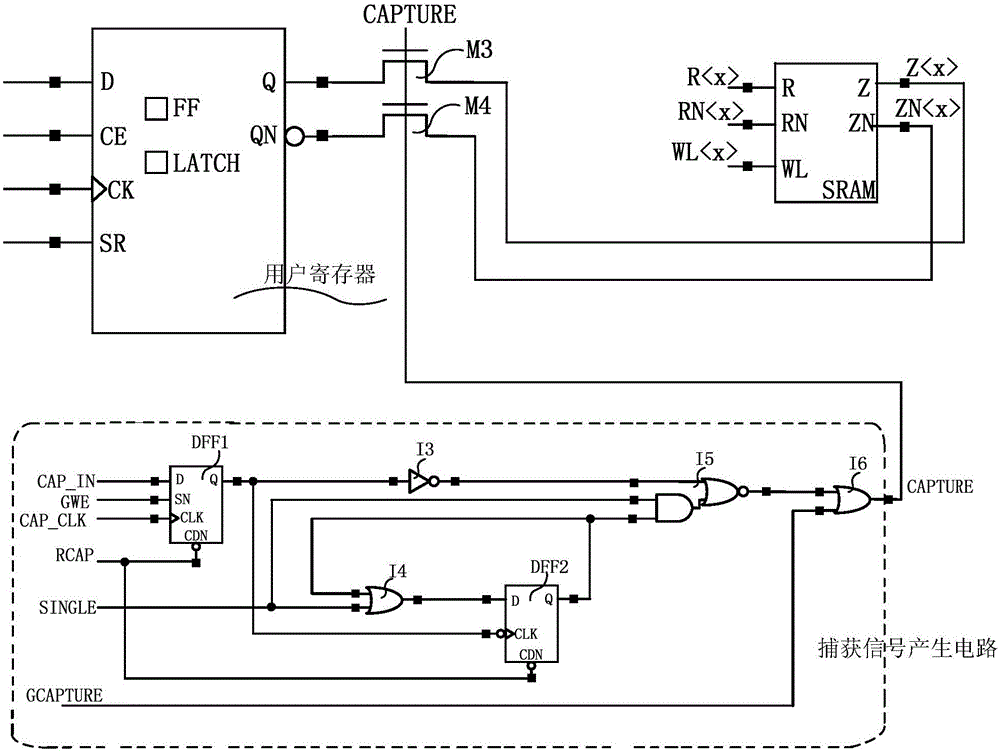

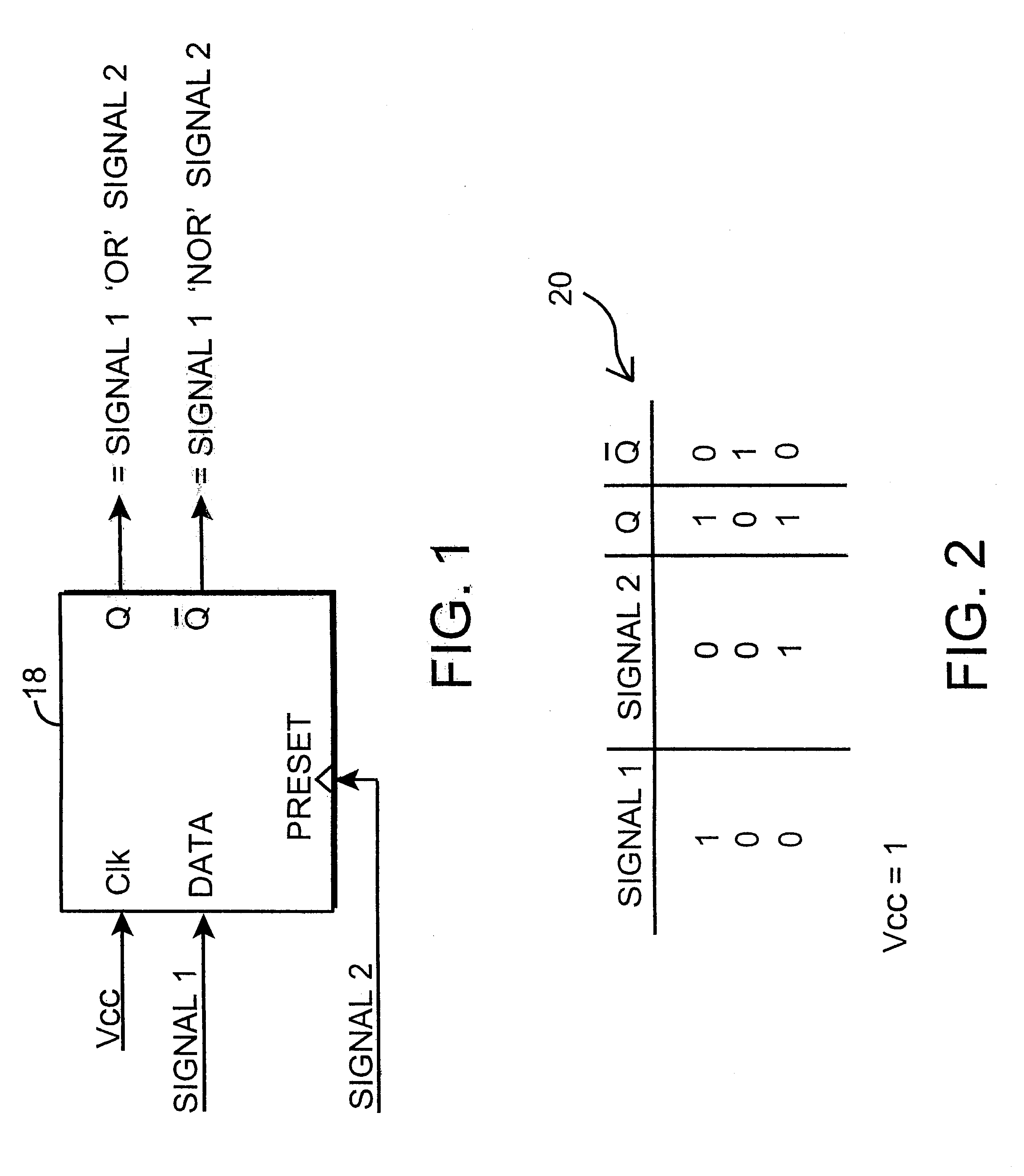

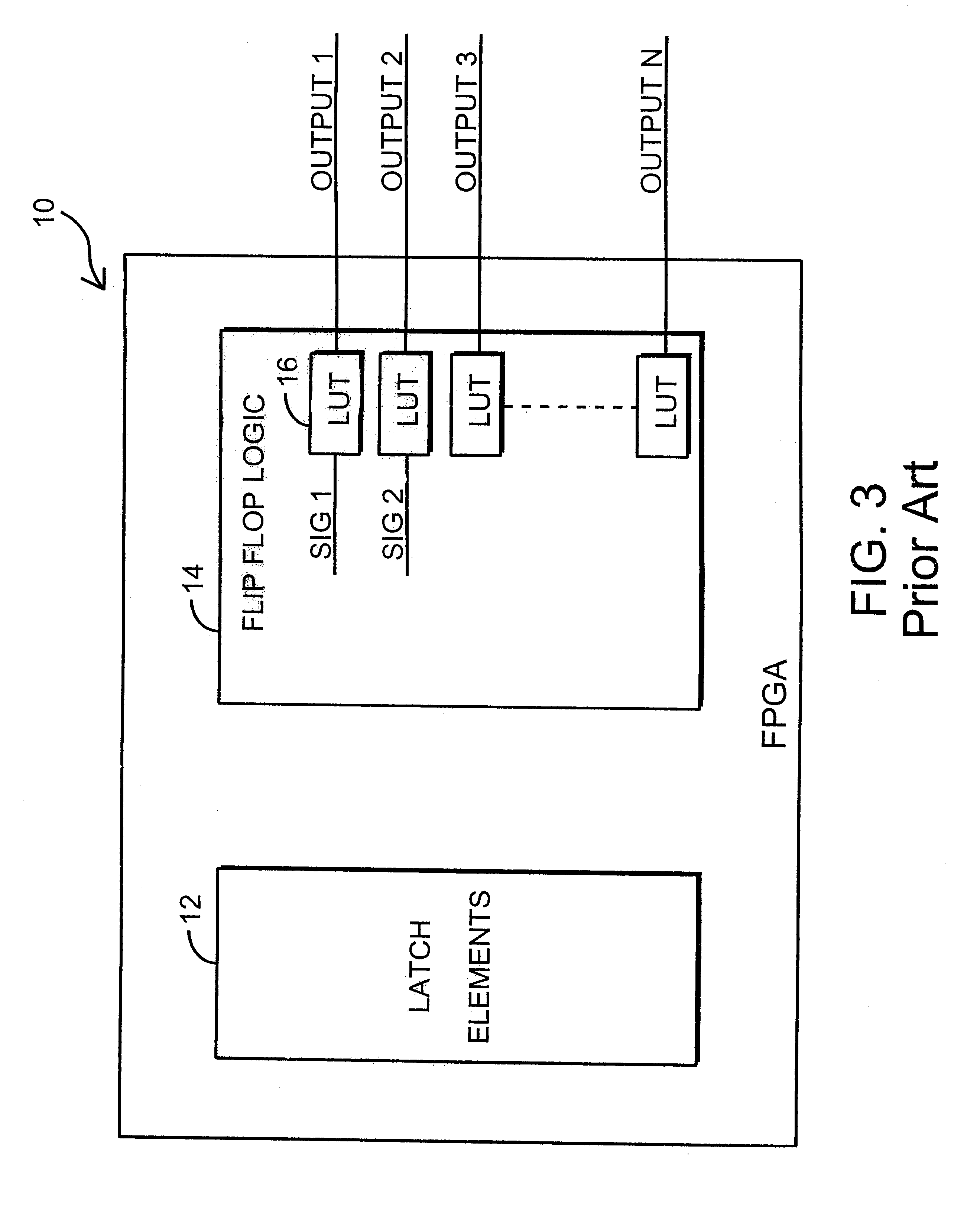

Asynchronous latch design for field programmable gate arrays

InactiveUS6556043B2Solid-state devicesElectric pulse generatorProgrammable logic deviceField-programmable object array

Owner:INT BUSINESS MASCH CORP

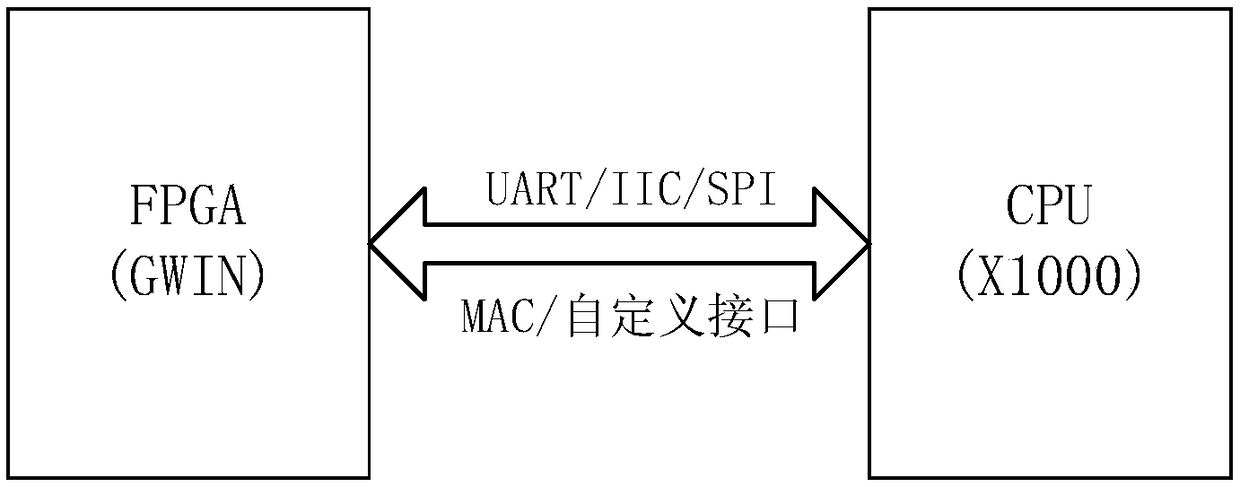

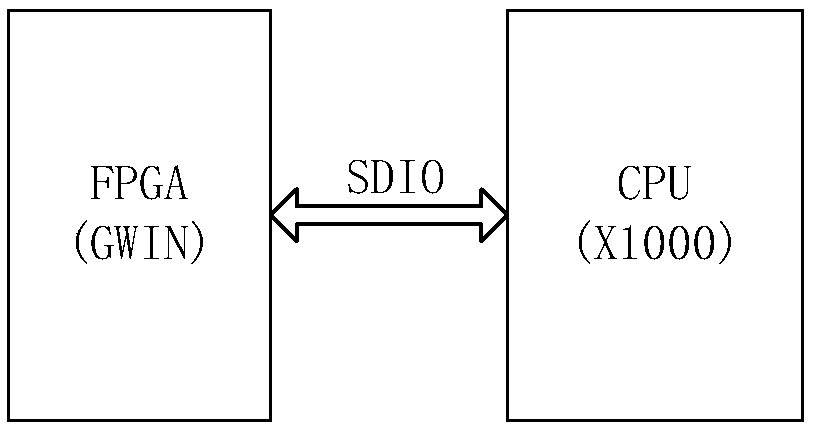

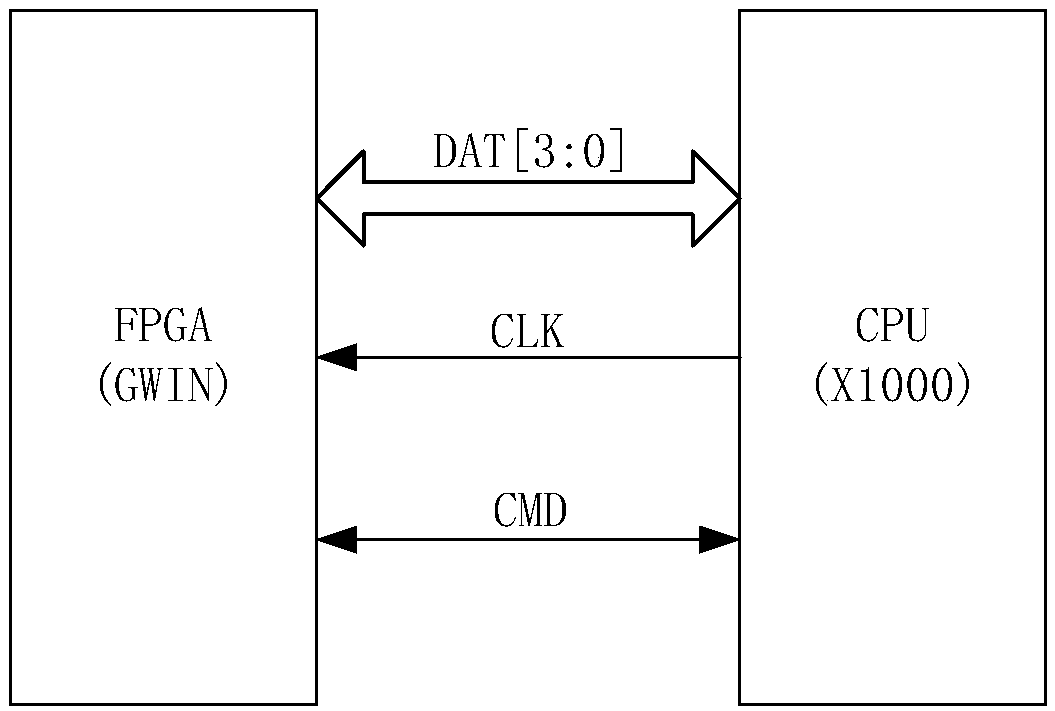

FPGA (field programmable gate array) and CPU (central processing unit) SDIO (secure digital input output) communication interface implementation method and device

ActiveCN108920193AReduce modificationImprove portabilityBootstrappingRedundant data error correctionCommunication interfaceField-programmable object array

The invention discloses an FPGA (field programmable gate array) and CPU (central processing unit) SDIO (secure digital input output) communication interface implementation method and device. An FPGA serves as a slave device without an IP (interface protocol) core, customizes an SDIO communication interface and adopts an SDIO communication protocol. A CPU serves as a master device, acquires a hybrid device drive process matched with an SDIO device and finishes drive registration and loading. The CPU can register one hybrid device in a drive, so that an application program can access the hybriddevice. The communication interface is applicable to the CPU and the FPGA in most design, and can meet the communication requirements of non-high-speed interfaces.

Owner:JUNENG SPECIAL COMM EQUIP CO LTD TOEC GRP

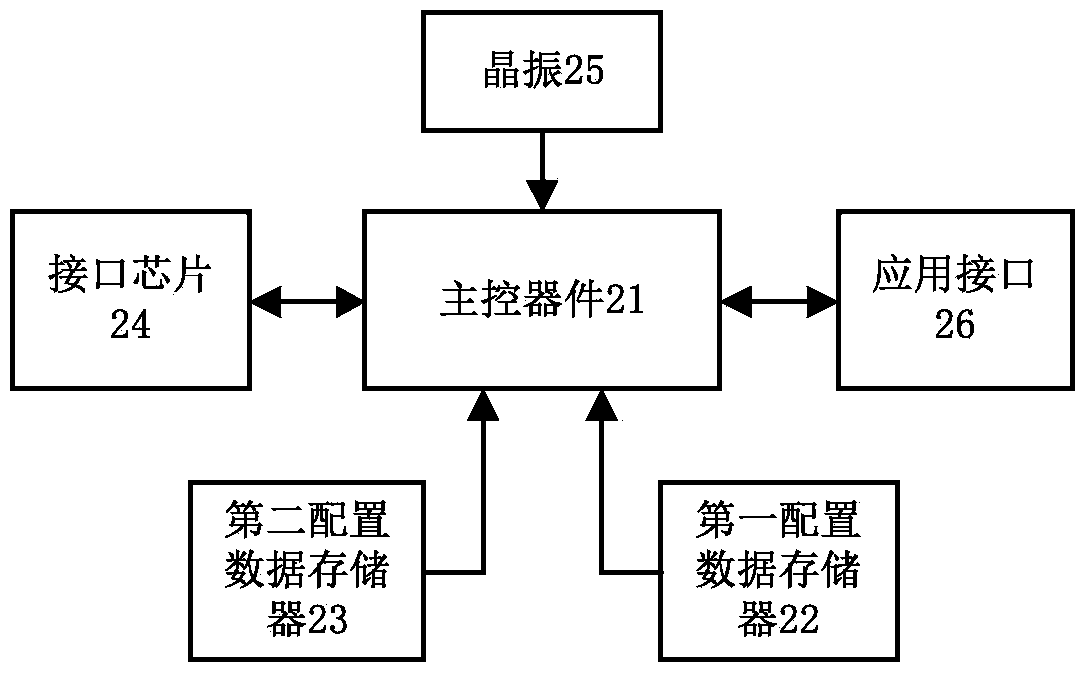

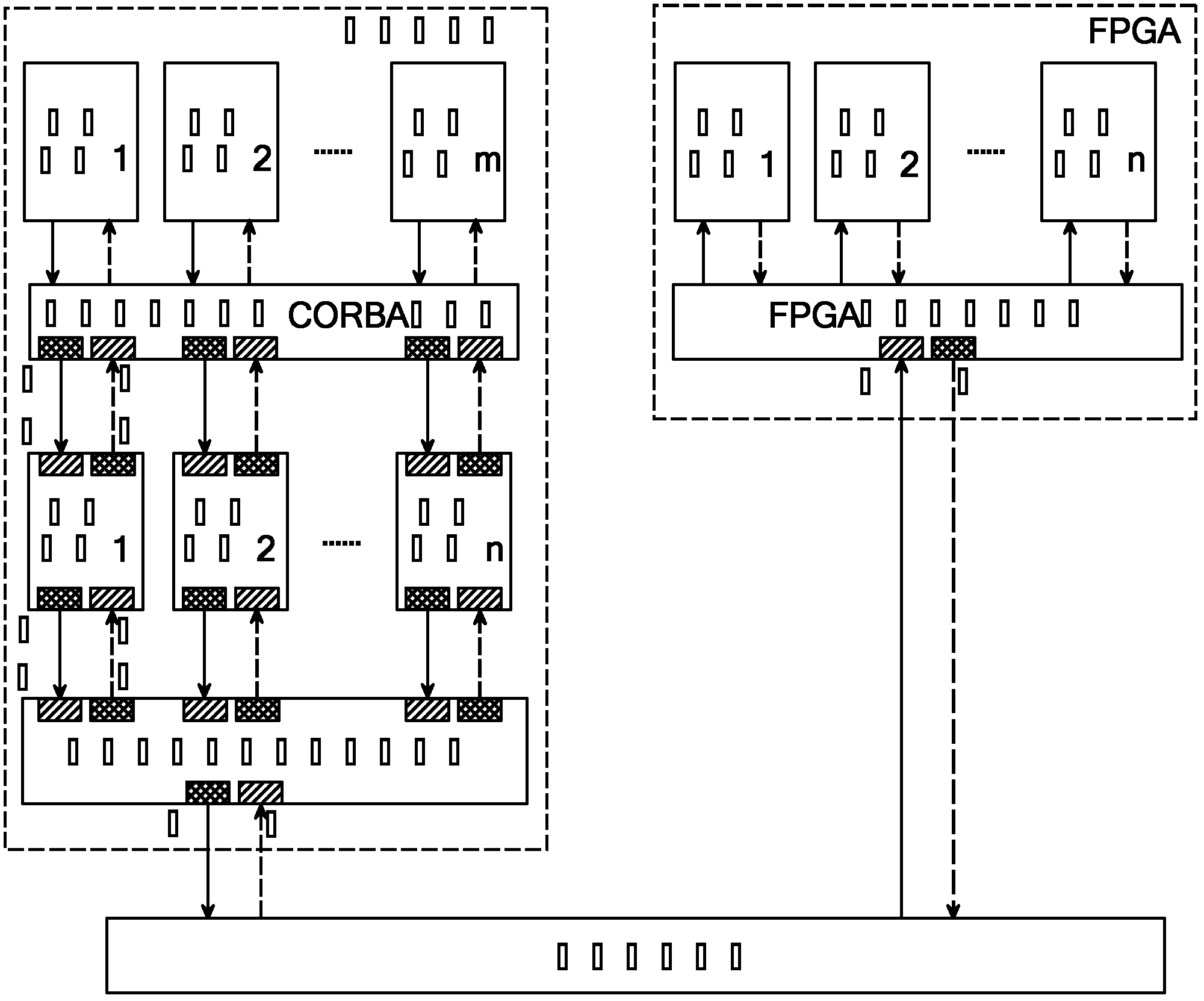

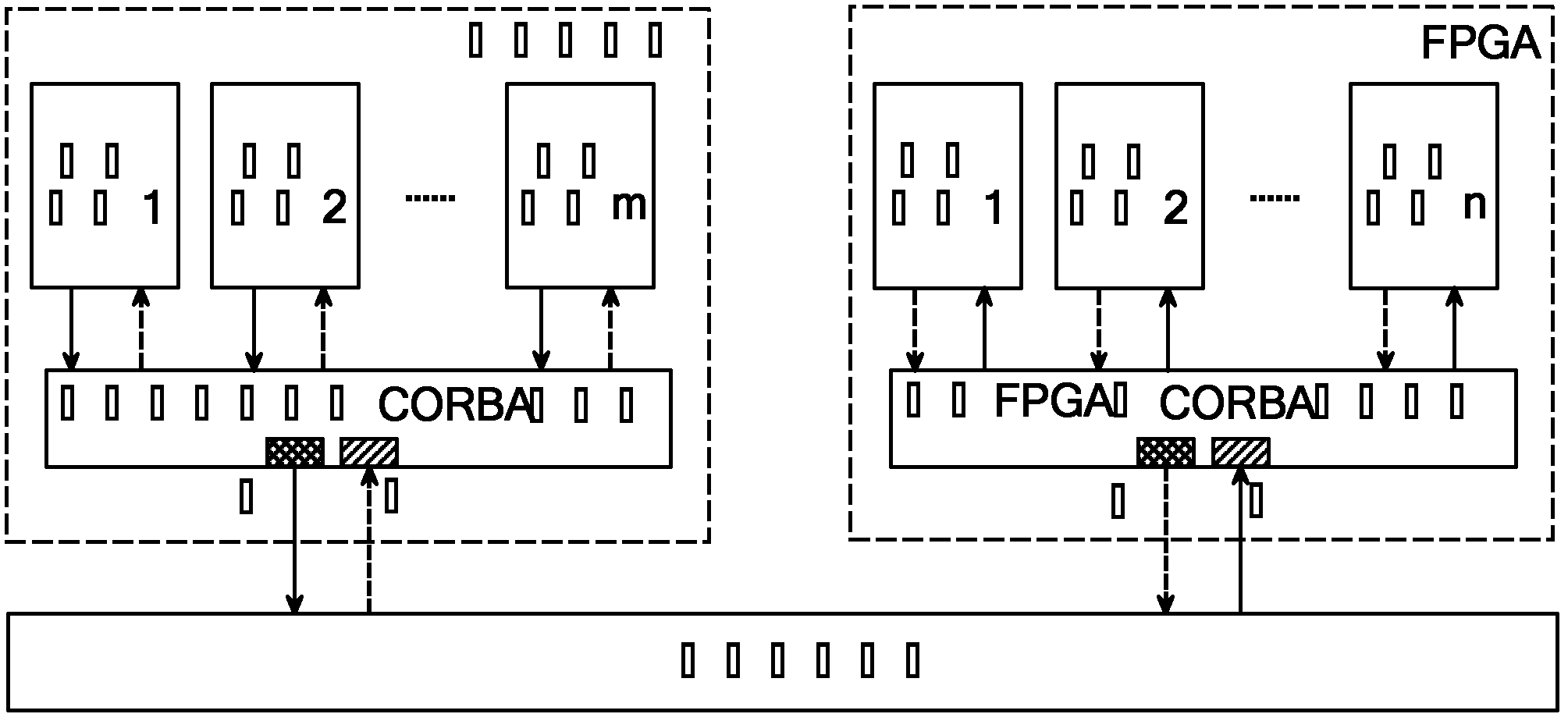

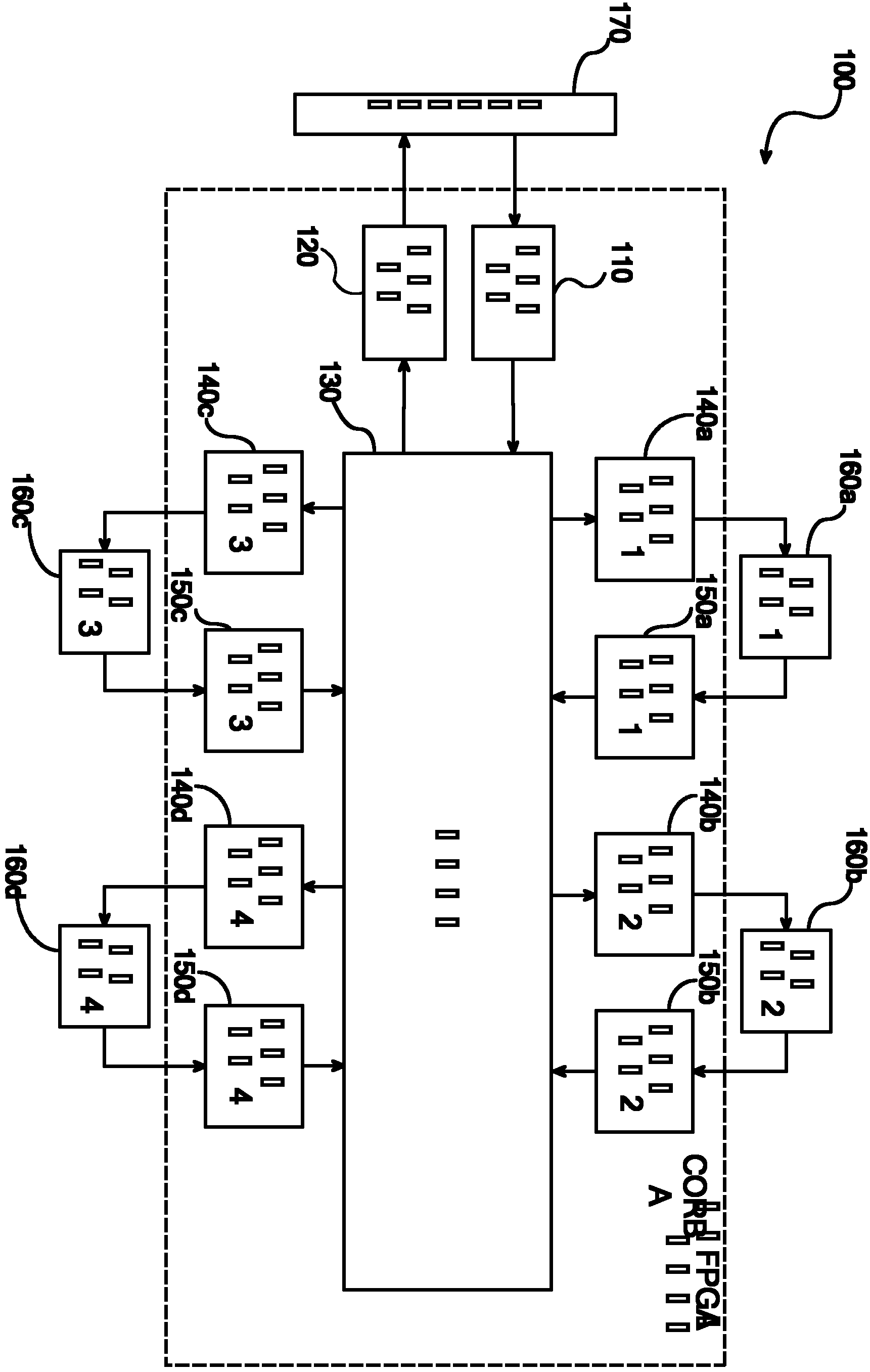

Field programmable gate array (FPGA)-based common object request broker architecture (CORBA) communication device

ActiveCN102208998AShorten call request latencyImprove communication efficiencyData switching networksGeneral purposeExternal data

The invention provides a field programmable gate array (FPGA)-based common object request broker architecture (CORBA) communication device, which comprises a master resolution module, a master packaging module, an interconnect module, a plurality of resolution sub-modules and a plurality of packaging sub-modules, wherein each resolution sub-module and each packaging sub-module correspond to each application module on an FPGA; the master resolution module performs data information exchange with other processors by external data interfaces, and transmits data information to the application modules by the interconnect module and the resolution sub-modules; and each application module transmits the data information to the master packaging module by corresponding packaging sub-modules and the interconnect module. The FPGA-based CORBA communication device is designed, implemented and run on the FPGA, is free from the limitations of the specific type of the FPGA, and can realize direct CORBAcommunication between the application modules on the FPGA and the application modules on the other processors without running any adaptor module and agent module on a general purpose processor.

Owner:NAT UNIV OF DEFENSE TECH

Field programmable object array and video compression processor for video data compression

ActiveUS9419620B2Improve performancePreserving FPOA capabilityPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningData compressionField-programmable object array

Owner:NYTELL SOFTWARE LLC

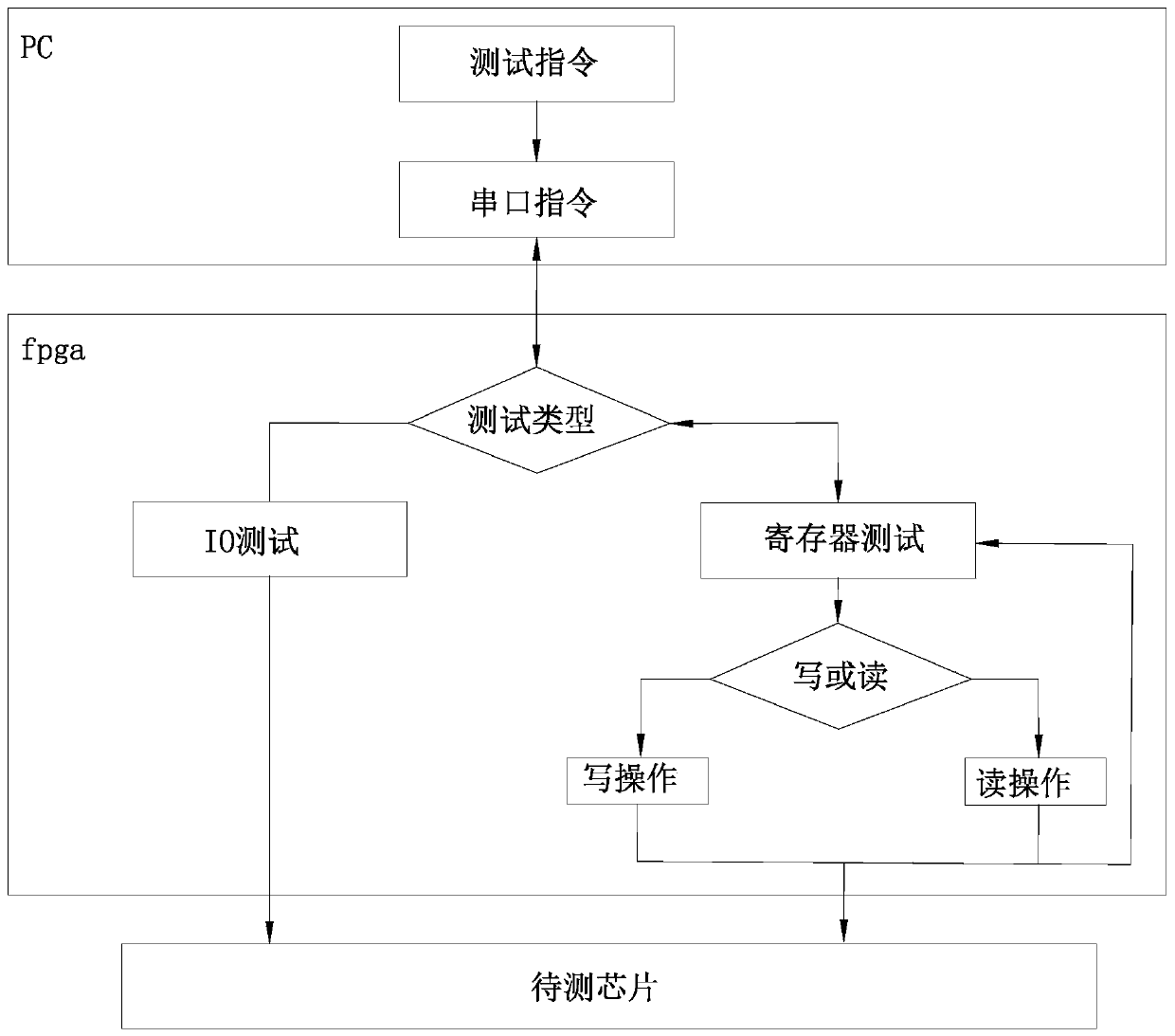

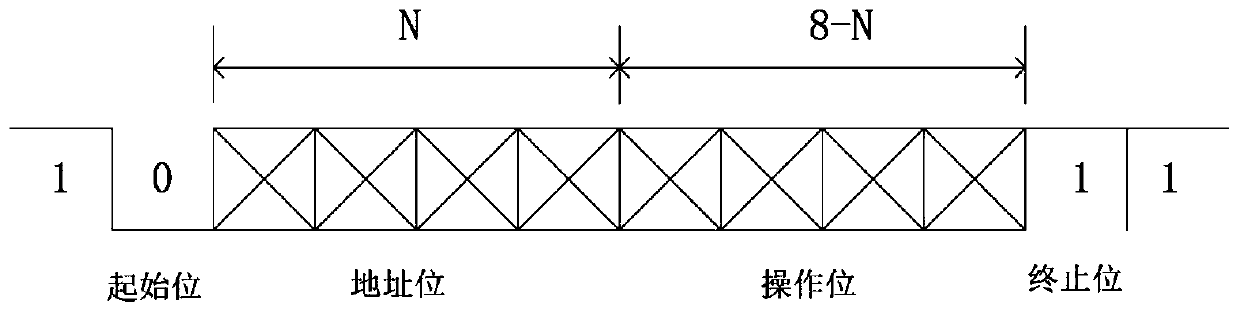

Chip testing system and method based on field programmable gata array (fpga)

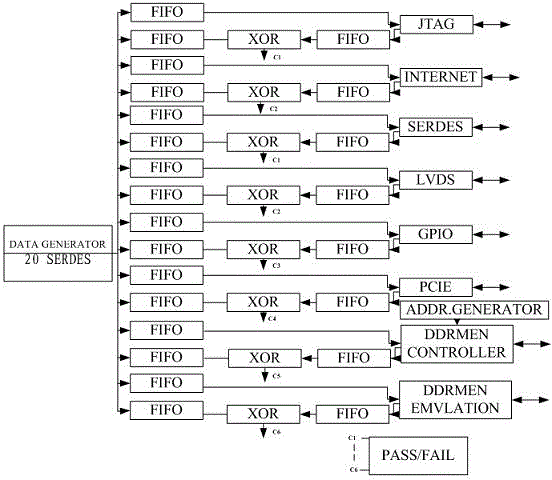

ActiveCN110058147AMeet testing needsShort compilation timePrinted circuit testingProcessor registerField-programmable object array

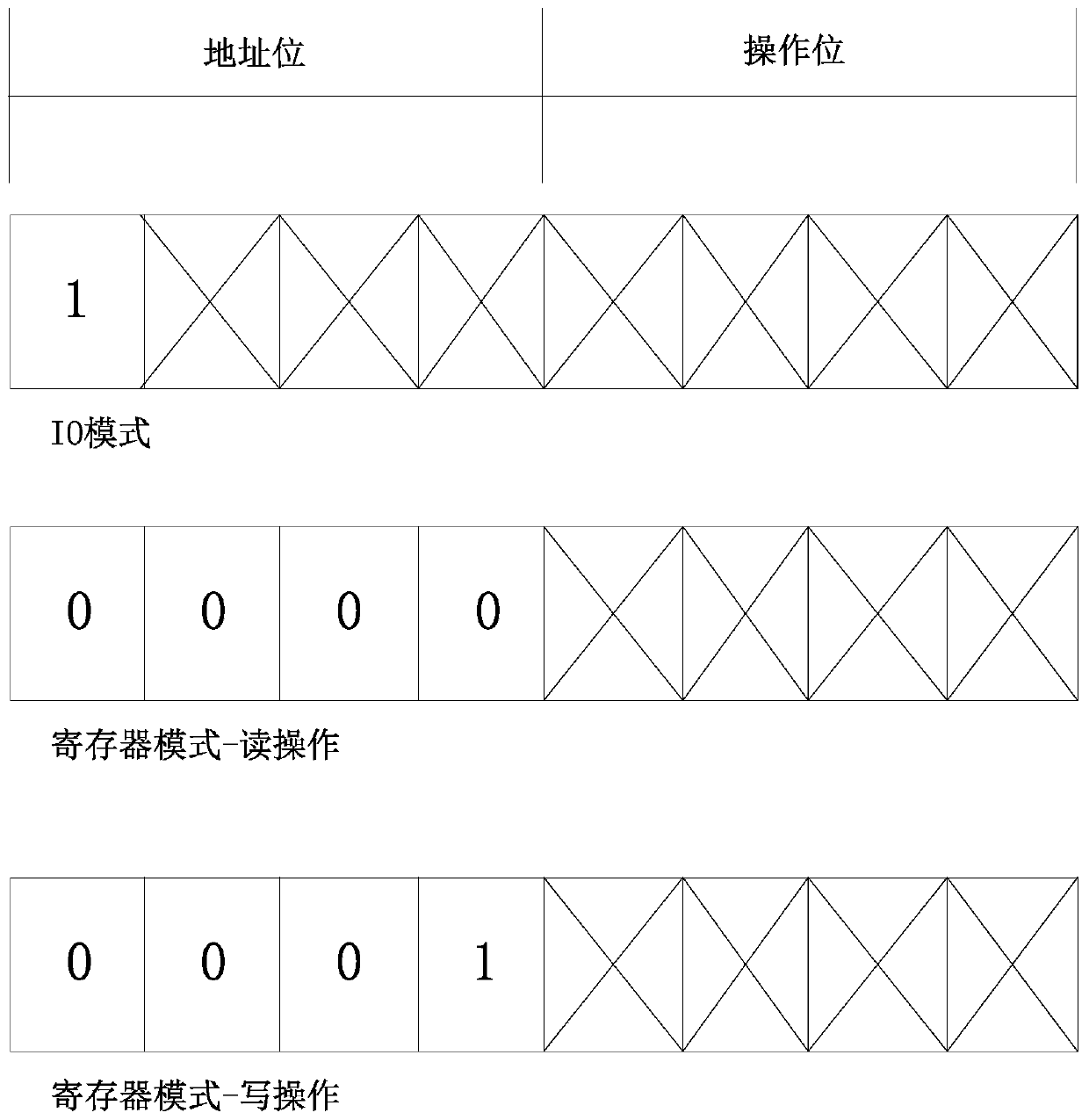

The invention discloses a chip testing system and method based on a field programmable gata array (fpga), and relates to the technical field of chip testing. The chip testing system based on the fpgacomprises a PC terminal and the fpga, wherein the PC terminal is used for applying a test incentive instruction and sending the test incentive instruction to the fpga; and the fpga is used for receiving the test incentive instruction, parsing the test incentive instruction and sending the test incentive instruction to a chip, the fpga can judge whether a test type is an IO test or a register test,the IO test comprises configuration of a chip test mode and vertical pull operation of chip IO, and the register test comprises read-write operation of a chip register. The chip testing system and method support two test types of IO and register read-write operation, users can debug test codes online, compilation time is short, and the chip testing system and method can flexibly meet various chiptesting requirements.

Owner:MOLCHIP TECH (SHANGHAI) CO LTD

Method using FPGA (field programmable gate array) for controlling DSP (digital signal processor) program load running

InactiveCN102567036AEasy to designEasy to debugProgram loading/initiatingProgramme control in sequence/logic controllersElectricityDigital signal processing

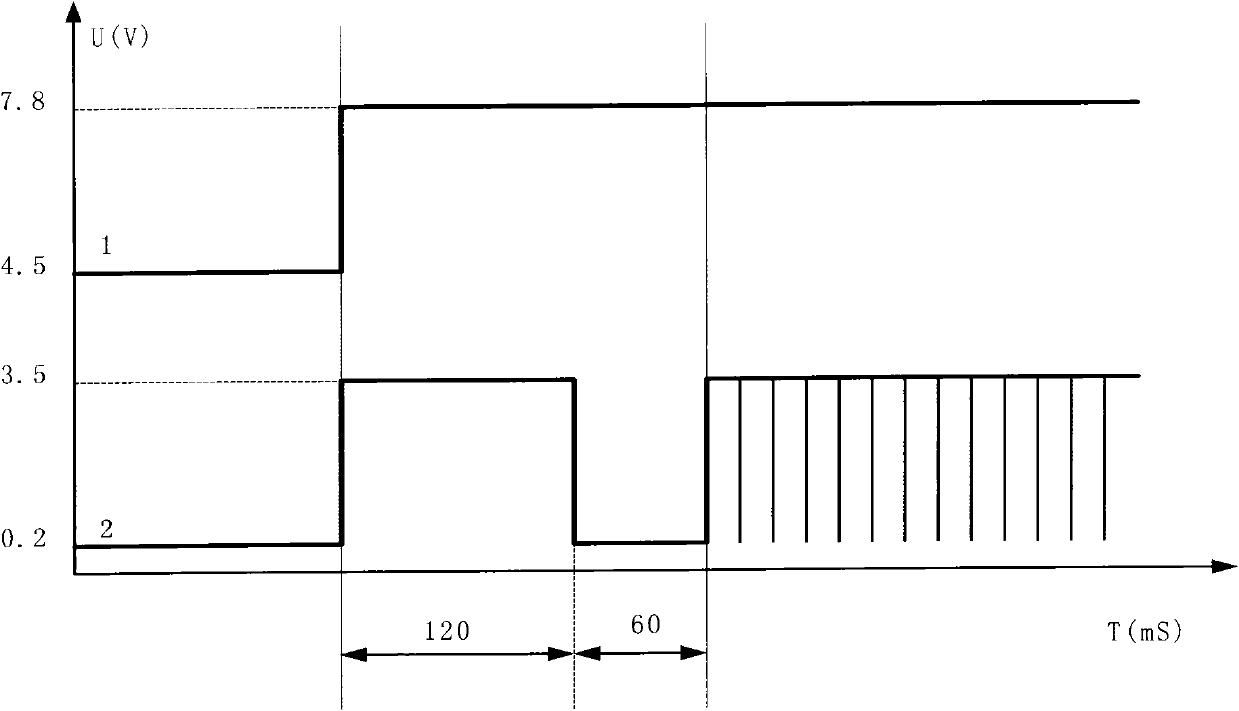

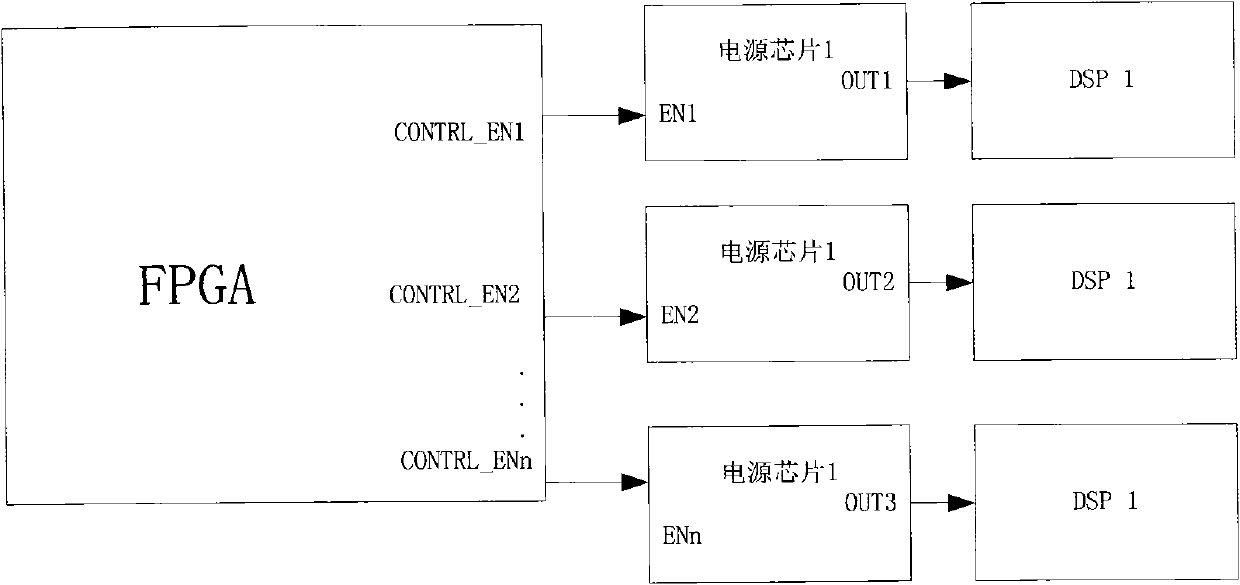

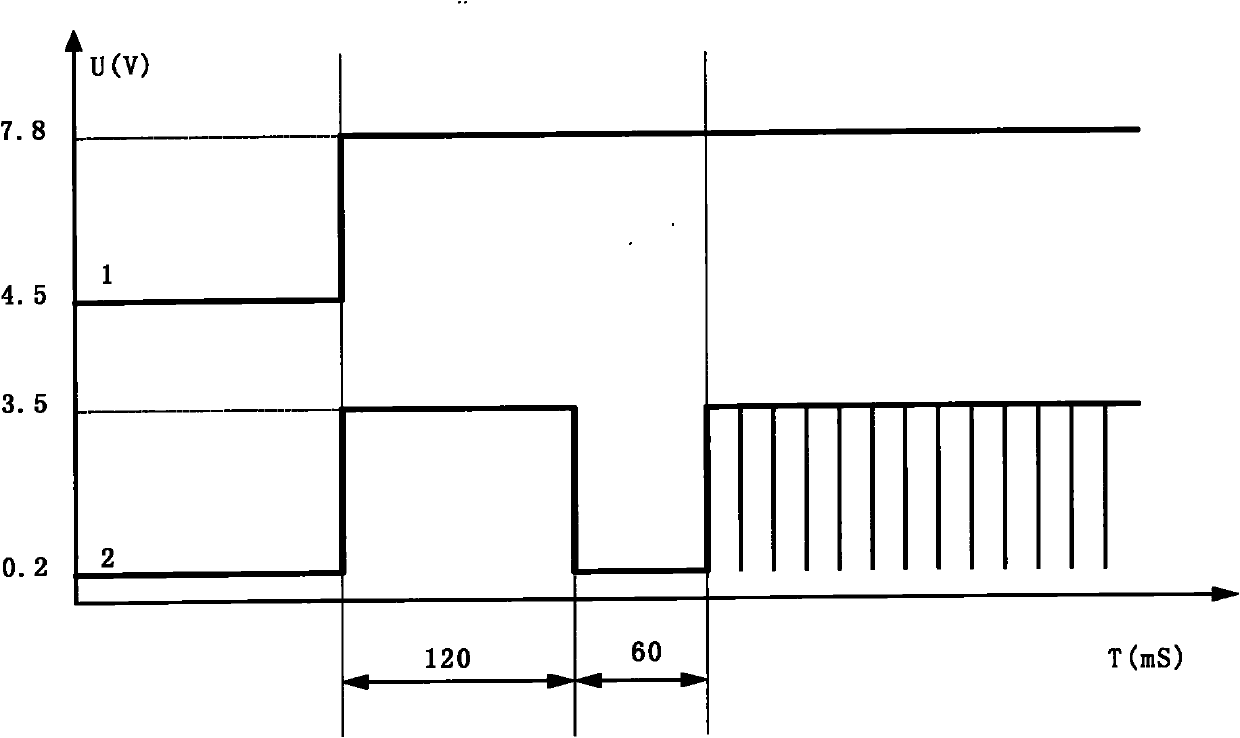

A method using an FPGA (field programmable gate array) for controlling DSP (digital signal processor) program load running, which includes the steps: 1 selecting a chip with a power output enable end EN to supply power to a DSP; 2 connecting a certain IO (input / output) pin of the FPGA to the enable end EN, and temporarily naming the IO pin as IO pin CONTRL_EN; and 3 editing FPGA codes, and enabling the IO pin CONTRL_EN to continuously output low level after FPGA loading is completed. The method has the advantages of simplicity, capability of leading design and debugging of a circuit to be simpler and easier and high flexibility and reliability. Particularly when a plurality of DSPs are connected with the FPGA, the method is convenient for arbitrarily defining the electrifying load sequence and delay time of the DSPs, which cannot be realized by any special chips.

Owner:XIAN KEYWAY TECH

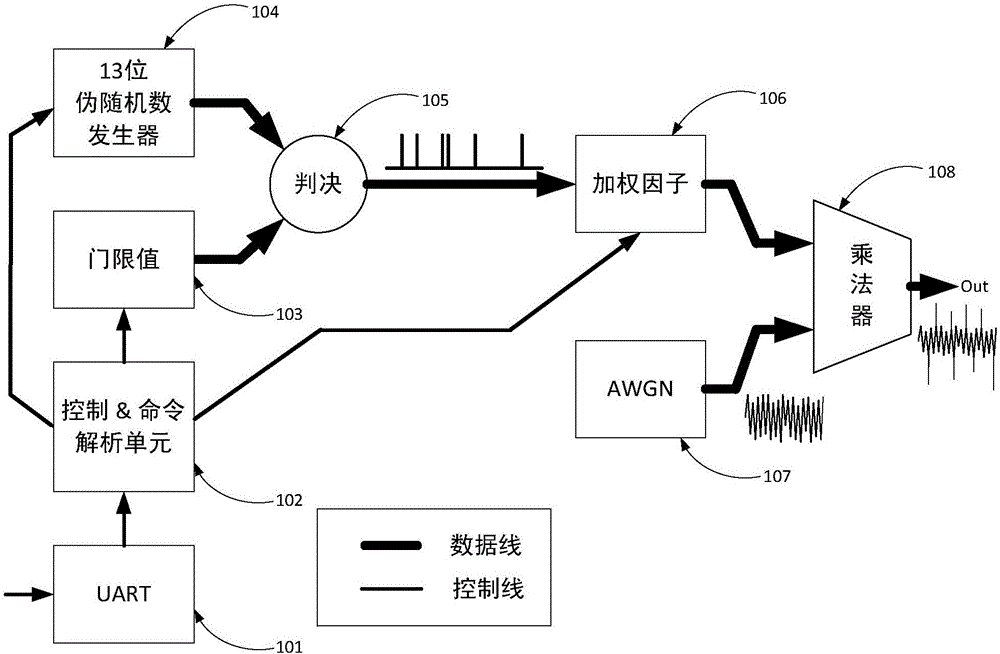

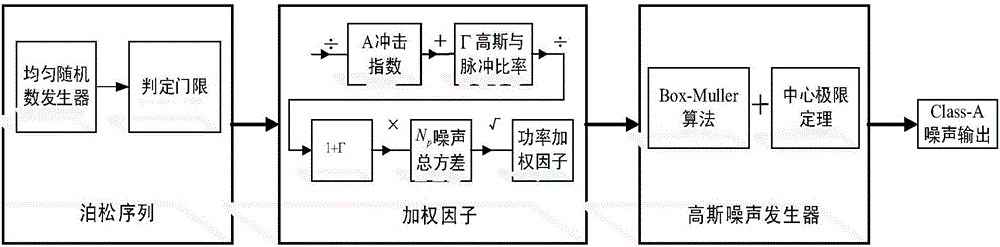

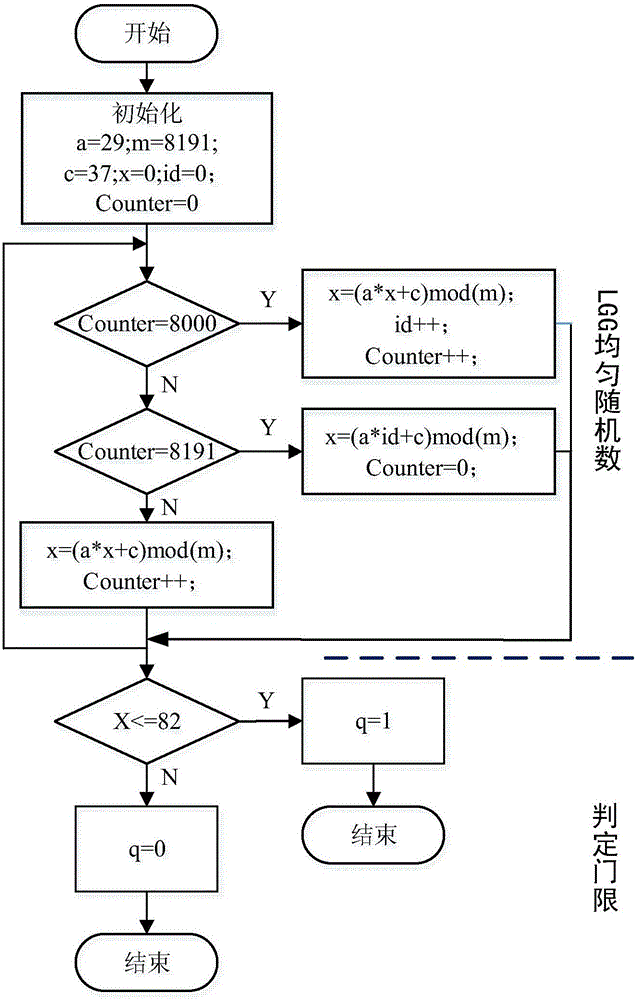

Random pulse generator based on FPGA (field programmable gate array)

ActiveCN106291011AEasy to implementSimple structureElectrical measurement instrument detailsElectrical testingField-programmable object arrayPulse sequence

The invention claims to protect a random pulse generator based on an FPGA (field programmable gate array). The random pulse generator mainly comprises a general asynchronous receiving and sending transmitter module, a control and command analysis unit, a pseudo-random number generator module, a judging module, a weighing factor module and a gaussian white noise generator module, wherein the general asynchronous receiving and sending transmitter module is used for receiving control information from a host and then sending the control information to the control and command analysis unit for command analysis; the control and command analysis unit is used for resetting a system, setting inside parameters and analyzing the command; the pseudorandom number generator module is used for generating the pseudorandom number sequence; the judging module is used for judging the threshold value obtained by the control and command analysis module and the value generated by the pseudorandom number module and outputting 0 and 1 pulse sequences; the weighing factor module is used for generating the weighing factors; the gaussian white noise generator module is used for generating gaussian white noise. The random pulse generator has the advantages that the structure is simple; the realization is easy; the integration degree is high; the hardware consumption is low; the generator parameter is flexible and settable.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

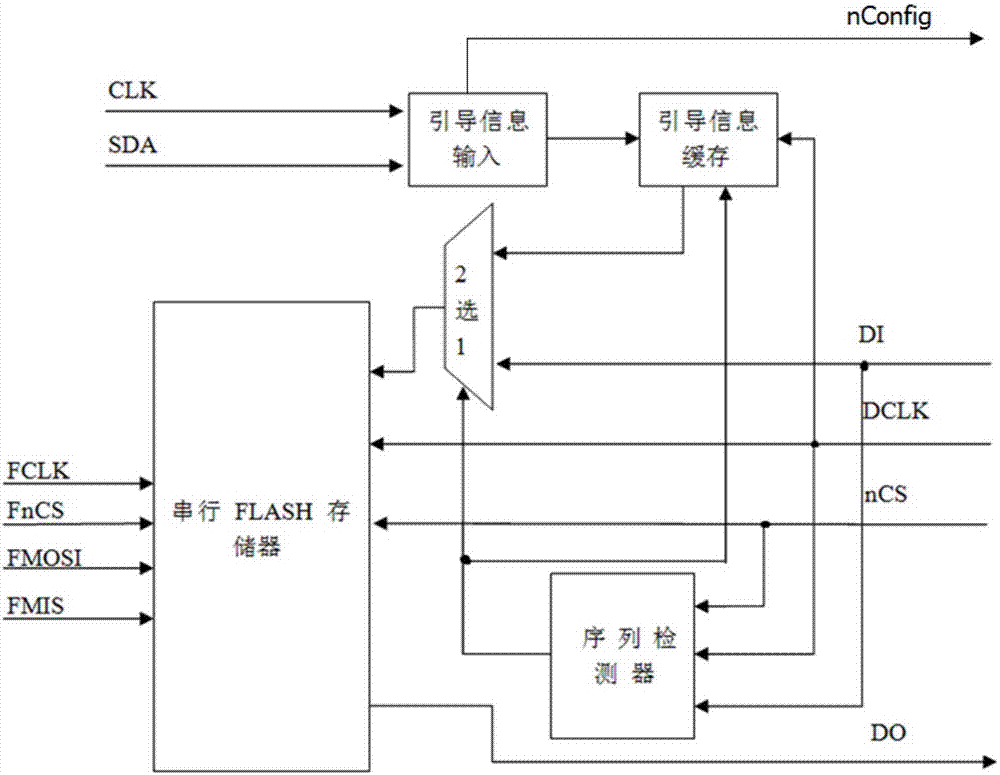

Guidable FPGA (field programmable gate array) configuration circuit

ActiveCN106940645AReduce in quantityRealize "hot switchingBootstrappingFpga field programmable gate arrayField-programmable object array

The invention belongs to the technical field of design and development of circuits, and discloses a guidable FPGA (field programmable gate array) configuration circuit. The guidable FPGA configuration circuit comprises a serial FLASH memory, wherein FCLK, FnCS, FMOSI and FMIS interfaces of the serial FLASH memory are connected with an external processor; the configuration information is written into the serial FLASH memory via the interfaces; CLK and SNA interfaces are connected with the external processor; the guiding information is set via the interfaces; nConfig, DI, DCLK, nCS and DO are connected with the FPGA. The guidable FPGA configuration circuit has the advantages that if the capacity of the FLASH memory is enough, multiple copies of FPGA configuration information can be stored in one FLASH chip, so that the number of chips can be reduced; the external processor can force the FPGA to reconfigure via CLK and SDA, so as to realize the heat exchange of the FPGA functions.

Owner:XIDIAN UNIV

Security RAM block with multiple partitions

ActiveCN106168931AUnauthorized memory use protectionInternal/peripheral component protectionField-programmable object arrayMessage authentication code

The disclosure relates to a security RAM block with multiple partitions. Circuits, methods, and apparatus for storing application data, keys, authorization codes, or other information in a volatile memory on an FPGA. A field programmable gate array (FPGA) can include multiple memory blocks and partition those blocks among multiple independent reconfigurable regions. Access to the memory blocks can then be restricted so that only authorized regions have access to particular memory partitions. In addition, each partition can store multiple message authentication codes (MACs) for further controlling access to data in each partition.

Owner:INTEL CORP

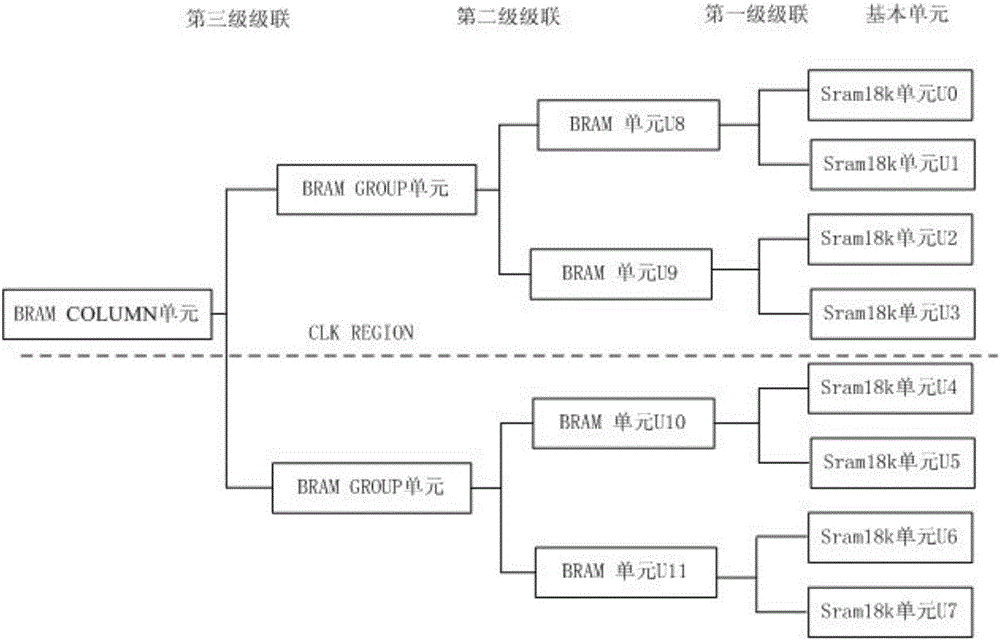

BLOCK RAM (Random Access Memory) cascade structure of field programmable gate array FPGA

InactiveCN105808474AMeet storage needsSave peripheral wiring resourcesElectric digital data processingStatic random-access memoryComputer architecture

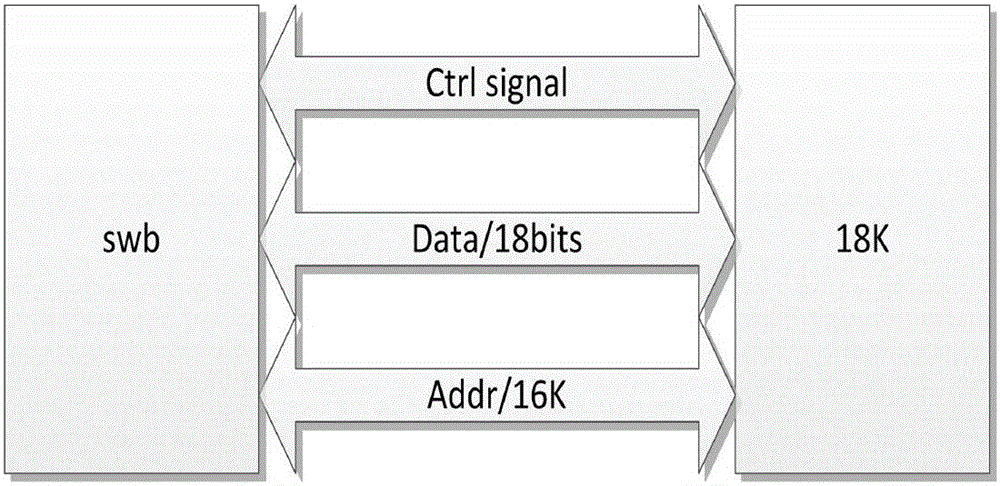

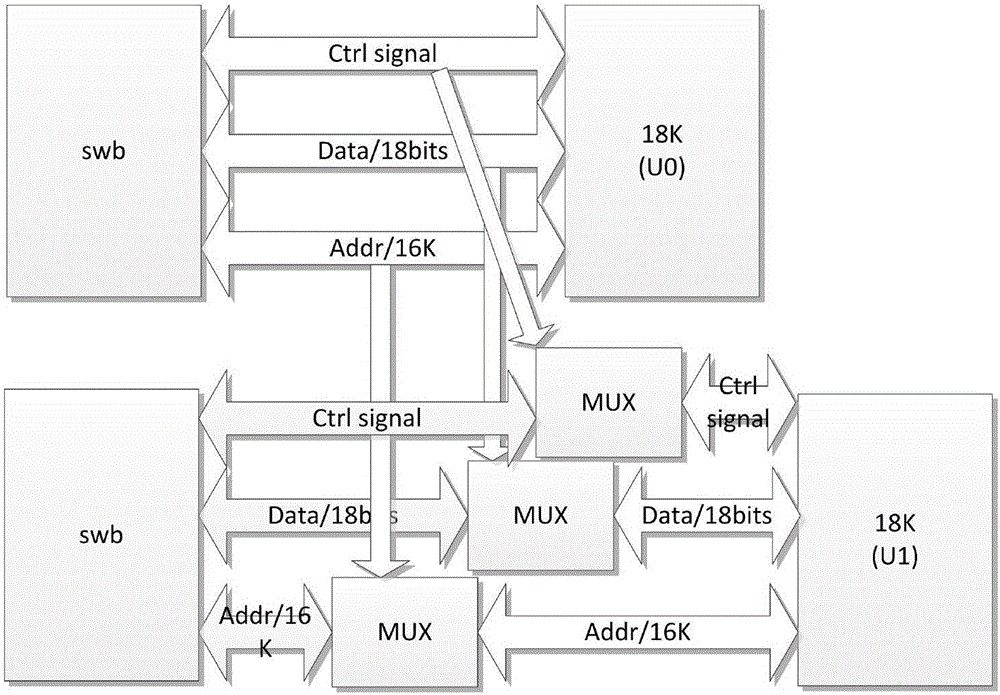

The invention relates to a BLOCK RAM (Random Access Memory) cascade structure of a field programmable gate array FPGA. The BLOCK RAM cascade structure comprises a column of SRAM18K (Static Random Access Memory) units, wherein two adjacent SRAM18K units in one column of the SRAM18K units are in address cascade or data parallel connection through a first stage ASIC (Application Specific Integrated Circuit) cascade logic routing architecture, and one BLOCK RAM unit is formed, and the like, taking wiring of a CLK REGION in the FPGA as the limit, two adjacent BLOCK RAM units are cascaded and one BRAM GROUP unit is formed; and two adjacent BRAM GROUP units are cascaded to form one BRAM COLUMN unit, and a BLOCK RAM cascade structure with the required address depth and data width can be formed. The BLOCK RAM cascade structure of the field programmable gate array FPGA provided by the invention can realize a memory cell RAM with the required address depth and data width, simplify a software algorithm and save peripheral wiring resources.

Owner:58TH RES INST OF CETC

Data communication method between processors and FPGA (field programmable gate array) equipment

InactiveCN103034613AReal time exchangeFlexible logic implementationDigital computer detailsElectric digital data processingFpga field programmable gate arrayField-programmable object array

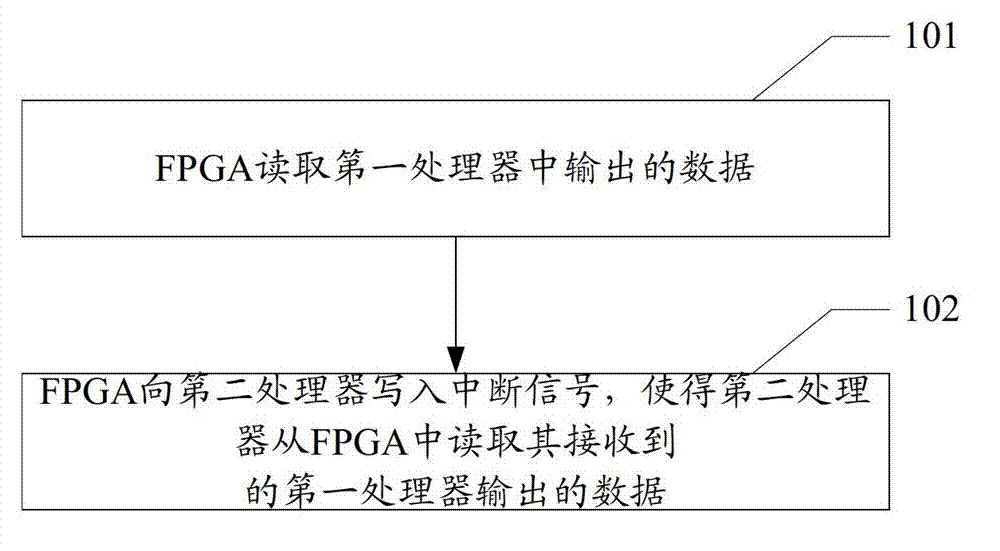

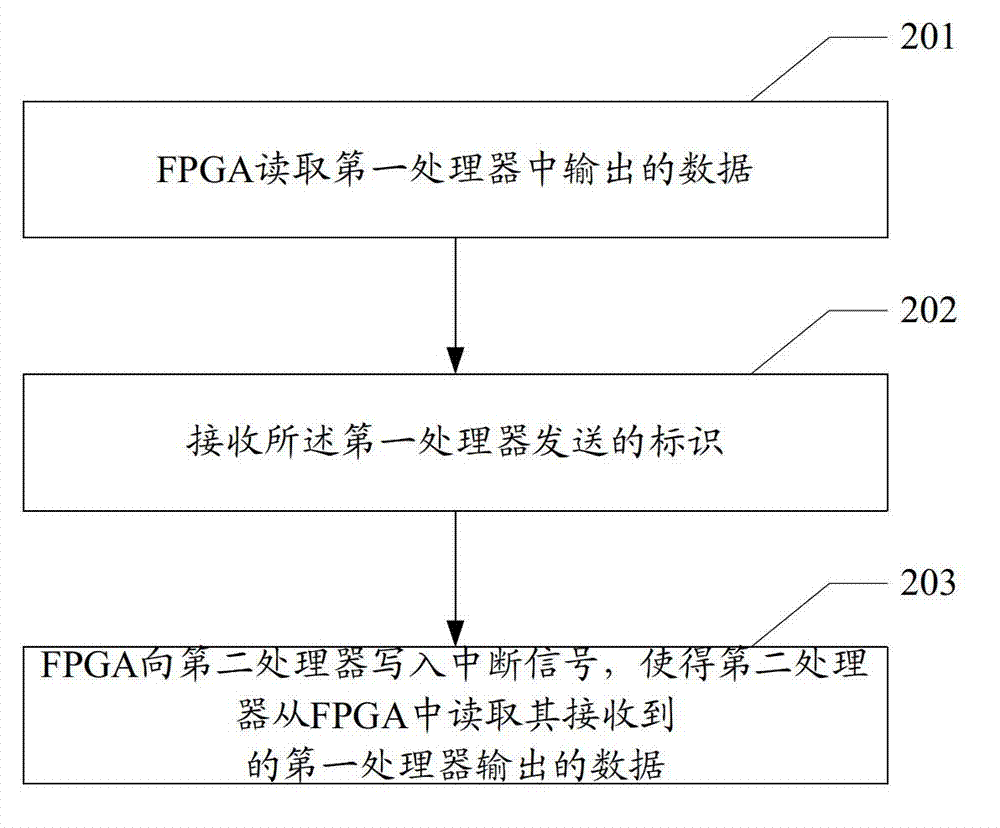

The embodiment of the invention provides a data communication method between processors and FPGA (field programmable gate array) equipment. Data output from a first processor is read by FPGA; an interruption signal is written into a second processor; and the second processor reads data which is output from the first processor and is read from the FPGA. Compared with the prior art that the communication mode between the processors is realized by a double-port RAM (random-access memory) chip, the communication method provided by the invention has the characteristics that data can be exchanged in time, logic realization is more flexible, and the cost performance is higher.

Owner:深圳市华力特电气有限公司