Universal dynamic aging system for Virtex-5 FPGAs (field programmable gate arrays)

A sophisticated and dynamic technology, applied in digital circuit testing, electronic circuit testing, etc., can solve the problems of large fluctuation range, FPGA over-temperature operation, low measurement accuracy, etc., to achieve high temperature control accuracy, standardized interface, universal strong effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Aiming at the deficiencies in the prior art, the present invention provides a Virtex-5 FPGA general-purpose dynamic burn-in system, which overcomes the defects that the existing FPGA dynamic burn-in technology does not have versatility and lacks accurate FPGA junction temperature measurement means. While having a certain generality, it can also accurately measure and control the junction temperature of the FPGA chip. The system of the present invention will be described in detail below in conjunction with the accompanying drawings.

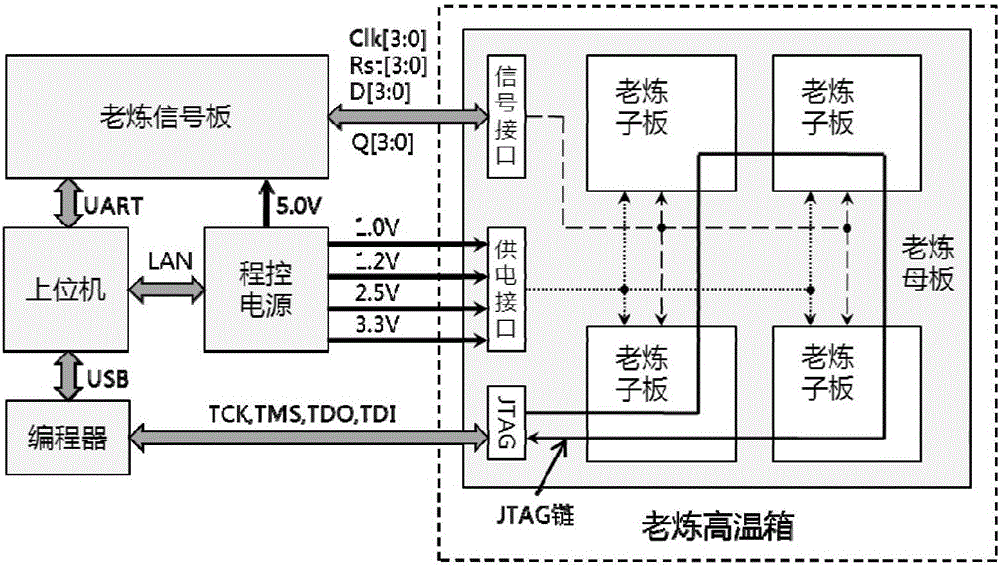

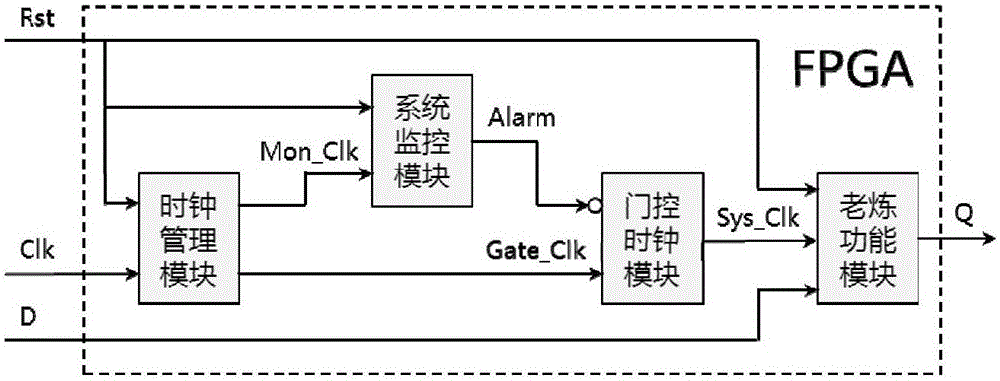

[0032] Such as figure 1 Shown is a kind of Virtex-5 FPGA general dynamic aging system structural schematic diagram of the present invention, a kind of Virtex-5 FPGA general dynamic aging system, comprises aging system hardware, upper computer software, lower computer software, wherein, aging System hardware includes upper computer, program-controlled power supply, programmer, burn-in signal board, high-temperature test chamber, burn-in test...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More