Multiple chips automatic test method based on programmable logic device

A technology of programming logic and automatic testing, which is applied in digital circuit testing, electronic circuit testing, etc., can solve problems such as long debugging cycle, high cost, and complicated testing process, and achieve fast development speed, low investment cost, and satisfy small batch products The effect of the test

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

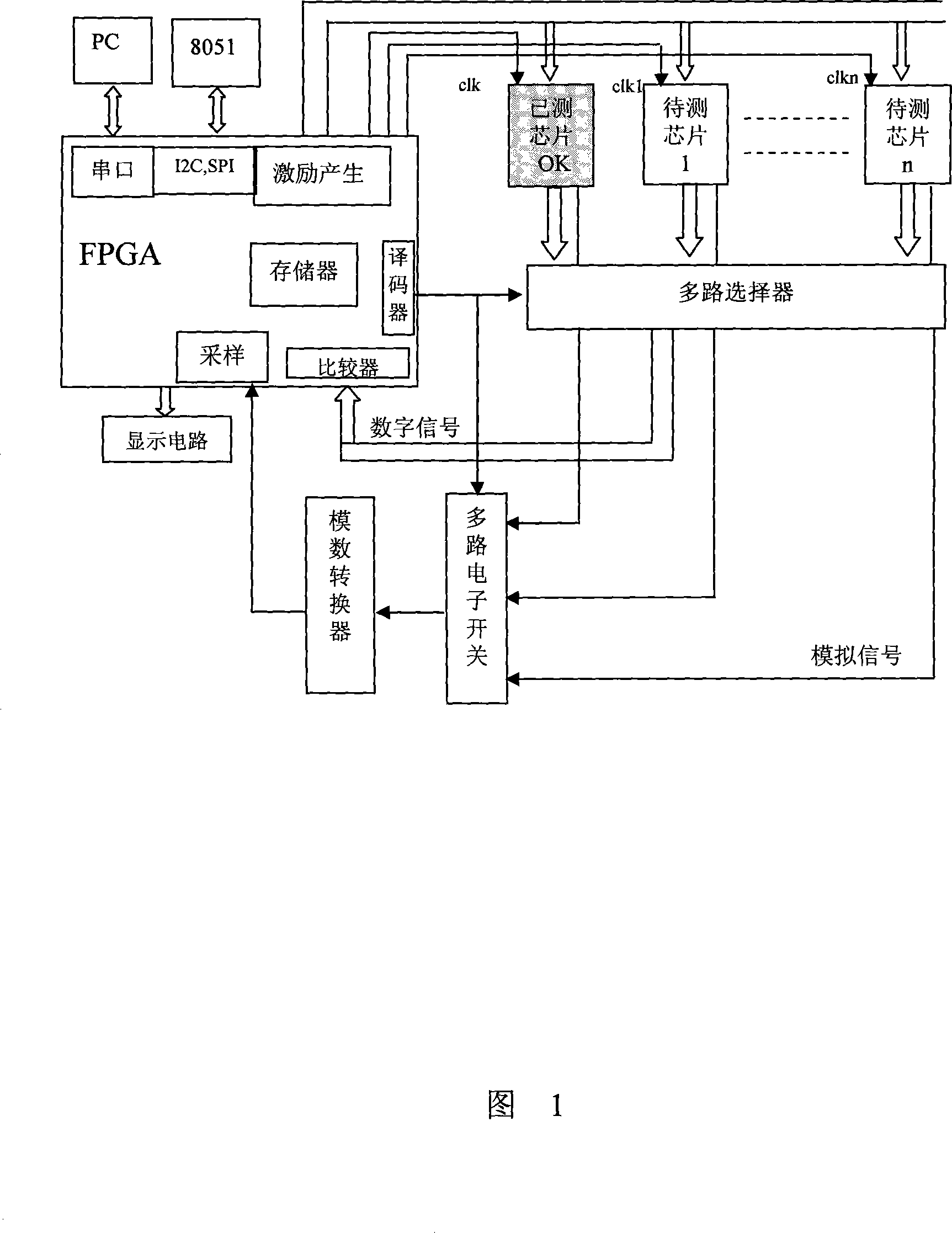

[0012] As shown in the figure: the programmable logic device includes a sampling circuit connected to each other, a digital comparator circuit, a decoder and an excitation generating circuit, and its characteristics are: the input terminal of the digital comparator circuit and the output terminal of the multiplexer Connection, the input terminal of the sampling circuit is connected with several chips under test; the multiplexer provides digital input signals for the digital comparator circuit; the chip under test provides digital input signals after analog-to-digital conversion for the sampling circuit; It is connected with several tested chips and one tested chip, and provides input signals and clock signals for the tested chip and the tested chip; the output terminal of the decoding circuit is connected with the multiplexer, and provides the loop control signal for the multiplexer , so that the multiplexer selects the output signal of the chip under test to be tested.

[001...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More