Patents

Literature

144 results about "Digital comparator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A digital comparator or magnitude comparator is a hardware electronic device that takes two numbers as input in binary form and determines whether one number is greater than, less than or equal to the other number. Comparators are used in central processing unit s (CPUs) and microcontrollers (MCUs). Examples of digital comparator include the CMOS 4063 and 4585 and the TTL 7485 and 74682.

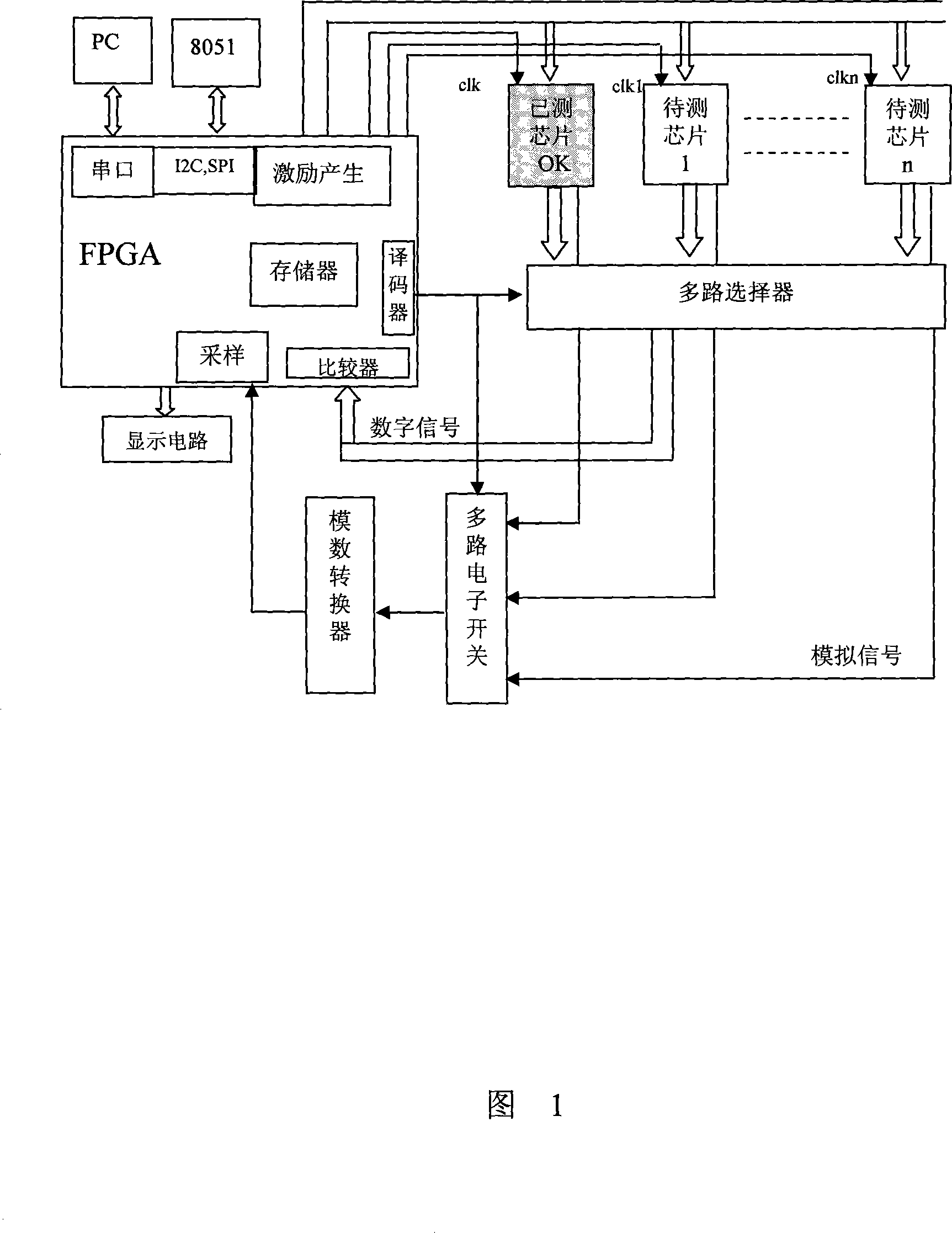

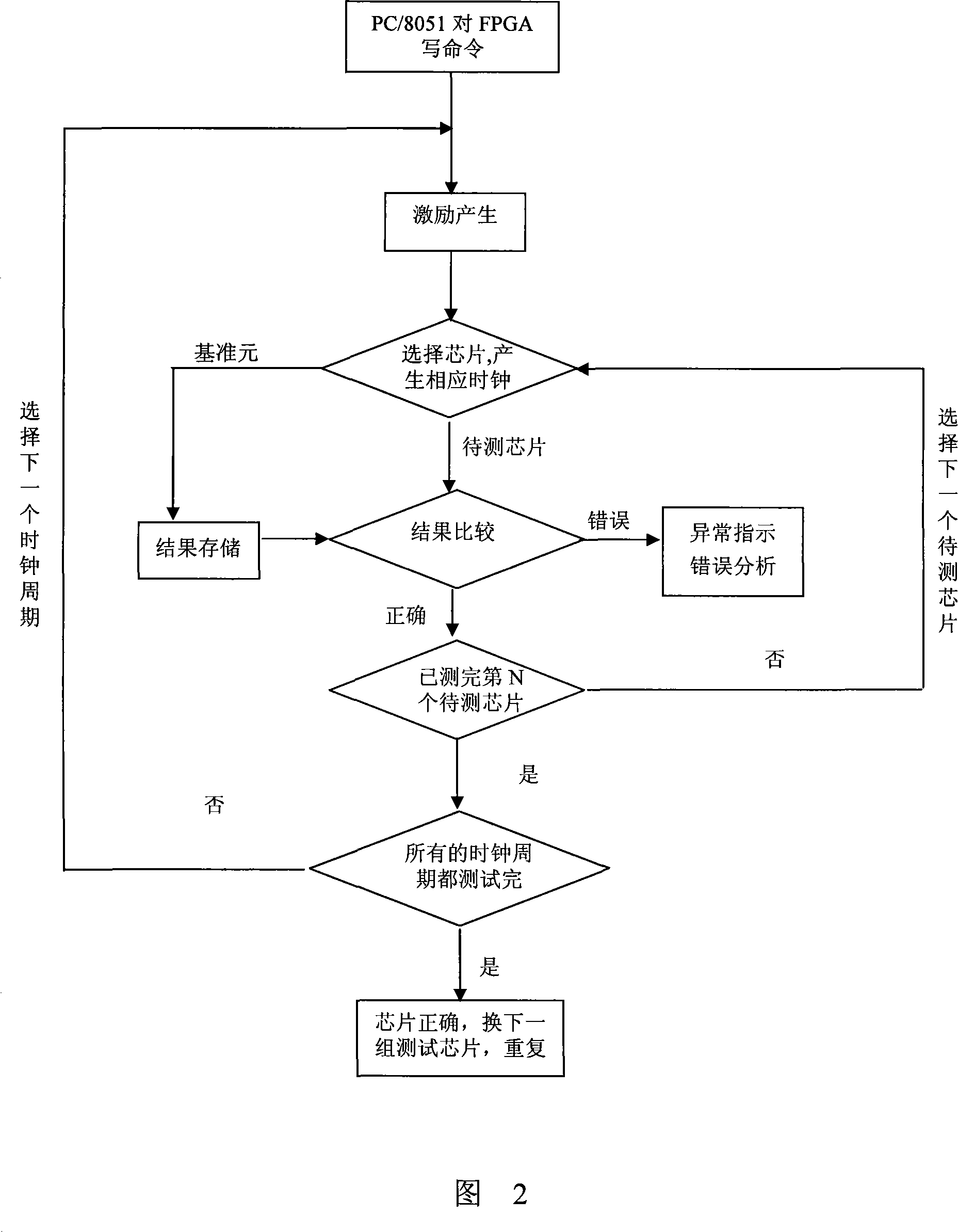

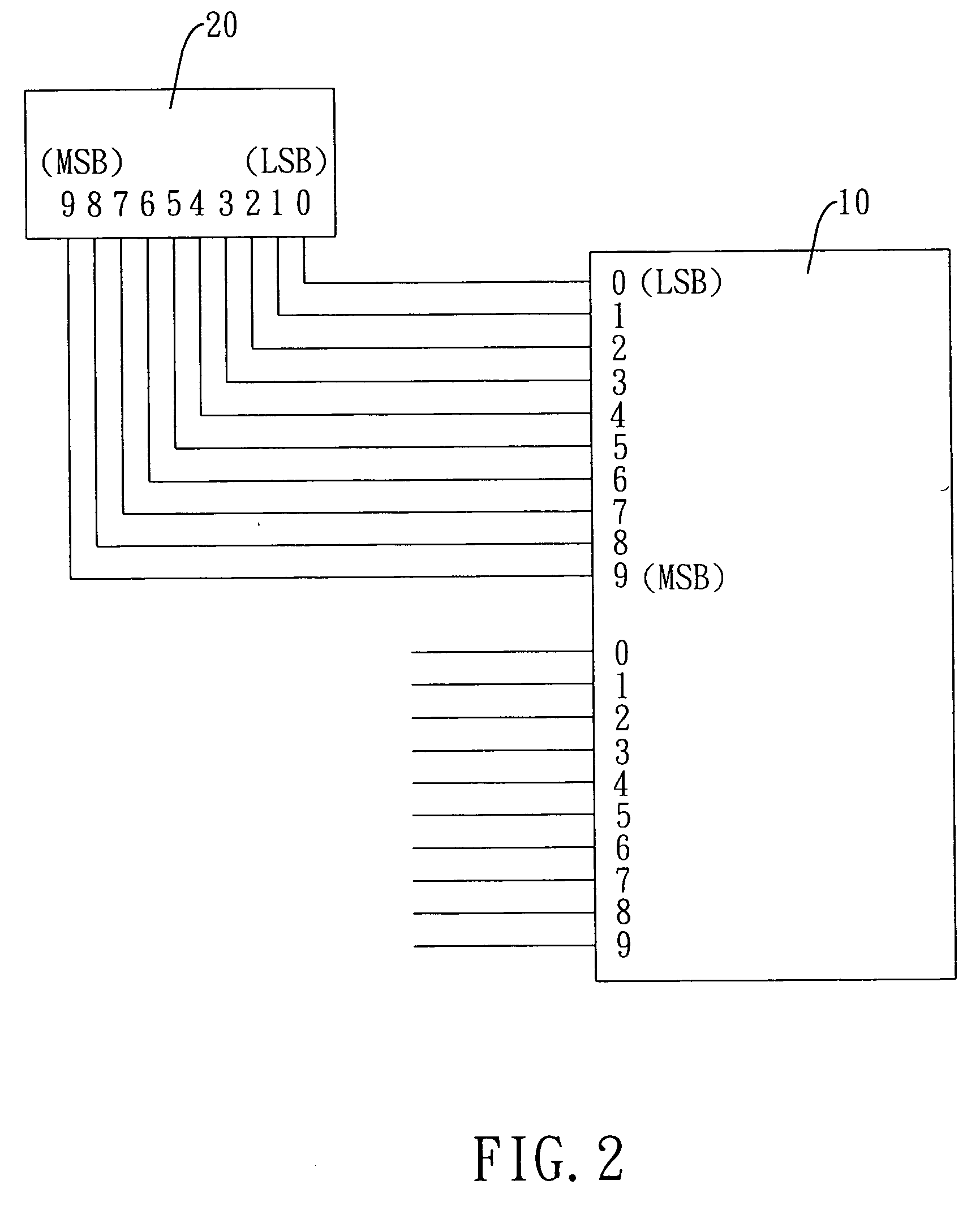

Multiple chips automatic test method based on programmable logic device

InactiveCN101158708AMeet the test requirementsImplement automated testingDigital circuit testingProgrammable logic deviceField-programmable object array

The invention relates to an automatic testing technology for molectron, in particular to an automatic testing method for multiple chips based on field programmable gate array (FPGA). According to the technical scheme provided by the invention, the field programmable gate array comprises the sample circuits that are connected to each other, a circuit of digital comparator, an encoder, and a pulse generating circuit. The technical scheme is characterized in that the input end of the circuit of digital comparator is connected with the output end of a multiplexer, the input end of the sample circuit is connected with a plurality of chips being tested; and the pulse generating circuit is connected with a plurality of chips being tested and a tested chip respectively; the output end of the encoder circuit is connected with the multiplexer. The invention uses the field programmable gate array (FPGA) to set up a simple automatic testing system, in which the automatic testing of a single or a plurality of chips can be implemented simultaneously on a testing board, The invention achieves automatic testing and has low input cost and rapid development, thus completely satisfying the requirement for the testing of small-lot products.

Owner:无锡汉柏信息技术有限公司

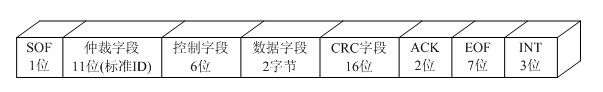

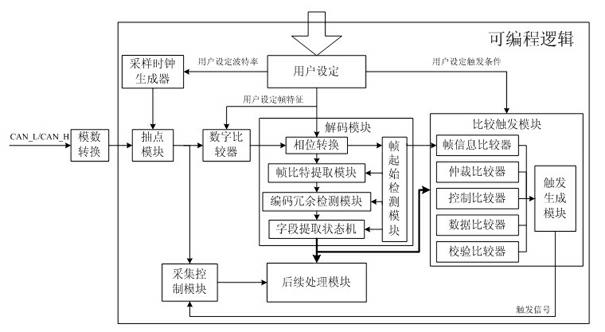

Method for analyzing and triggering controller area network (CAN) bus

InactiveCN102355382AEasy to readImprove debugging efficiencyBus networksArea networkMeasuring instrument

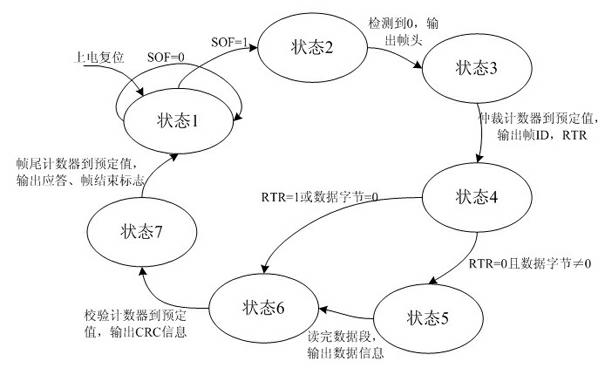

The invention discloses a method for analyzing and triggering a controller area network (CAN) bus, which can provide a triggering and decoding function of a CAN bus for a measuring instrument. The method comprises the following steps of: converting a CAN bus signal to be measured into a digital signal through an analog-to-digital converter; generating, by a sampling clock generator, sampling clock of corresponding frequency to a snapshot module to snapshot the digital signal according to baud rate set by a user; converting, by a digital comparator, into 0 / 1 value and then transmitting to a decoding module to extract frame information; transmitting to a comparative trigger module to compare with a trigger condition set by the user; and if the trigger condition is met, generating a trigger signal to an acquisition control module to control acquisition and storage of the signal after snapshot. The frame information output by the decoding module can be transmitted to a subsequent processing module together with acquired and stored waveform information so as to be used for further analysis processing. By adopting the method, the acquisition of an interesting CAN bus event of the measuring instrument is facilitated, interruption of the CAN bus information of the user is facilitated, and debugging efficiency of the CAN bus is increased.

Owner:SOUTHEAST UNIV

Settling Time and Effective Band Width for Op-Amps Using Miller Capacitance Compensation

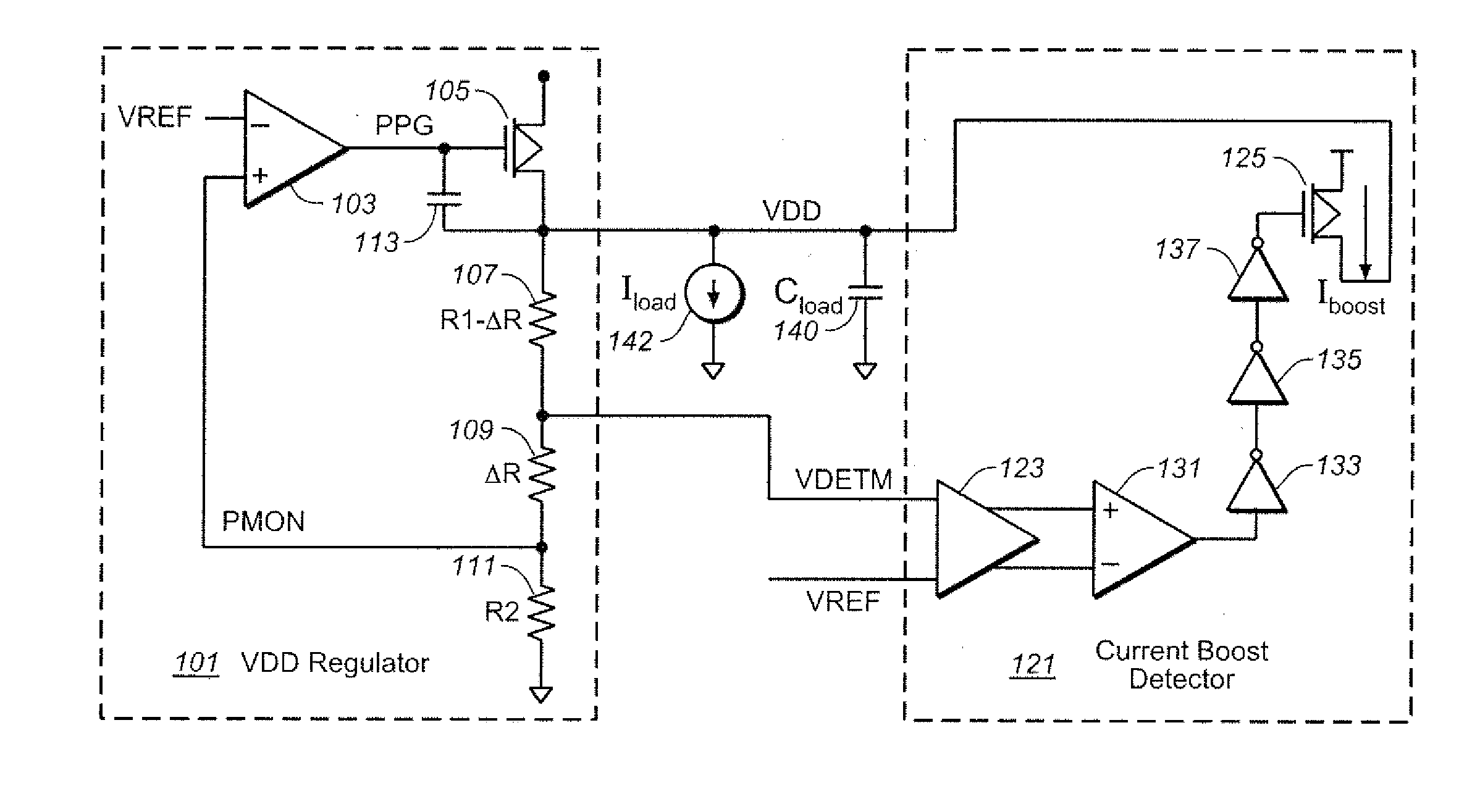

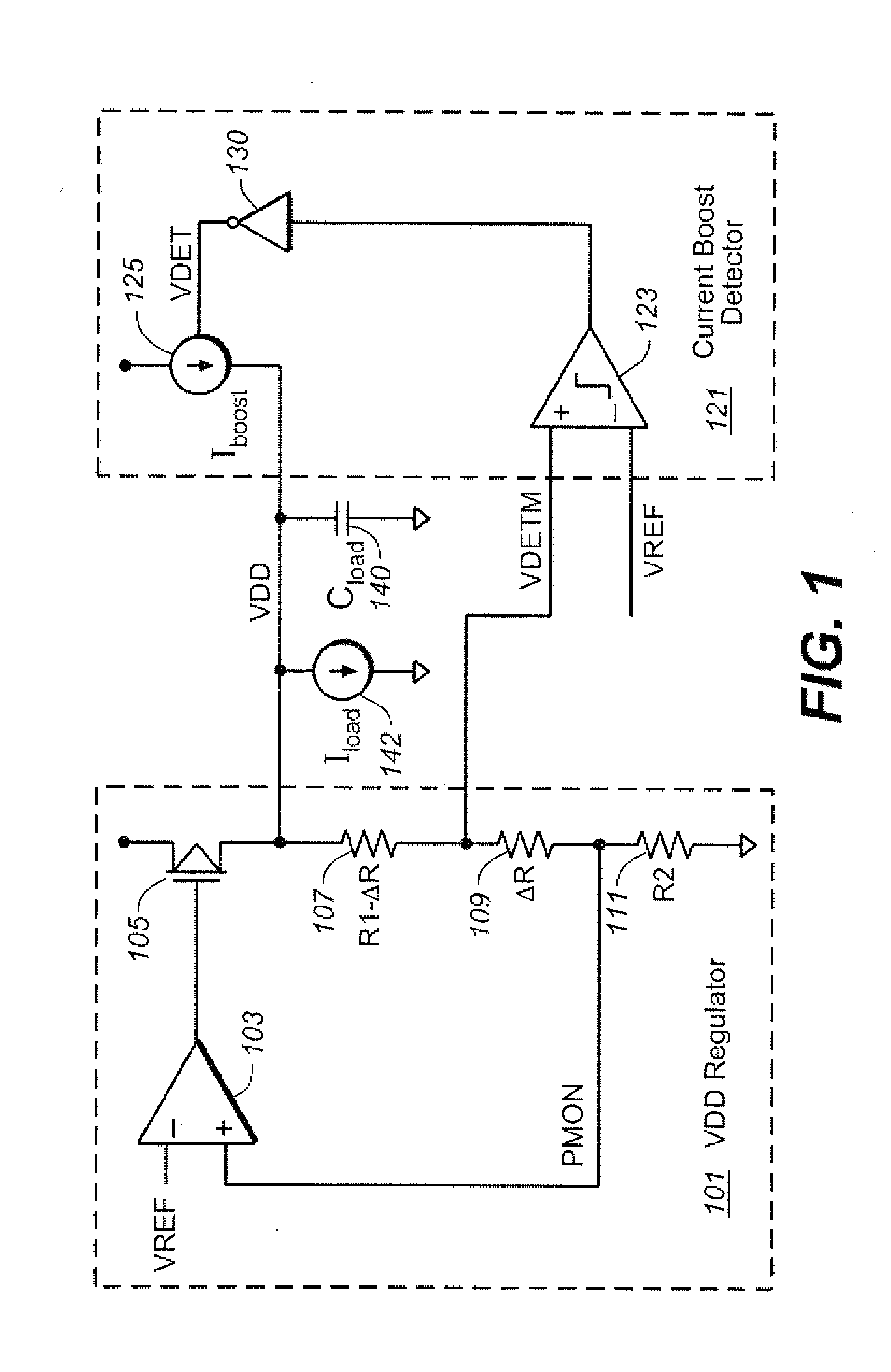

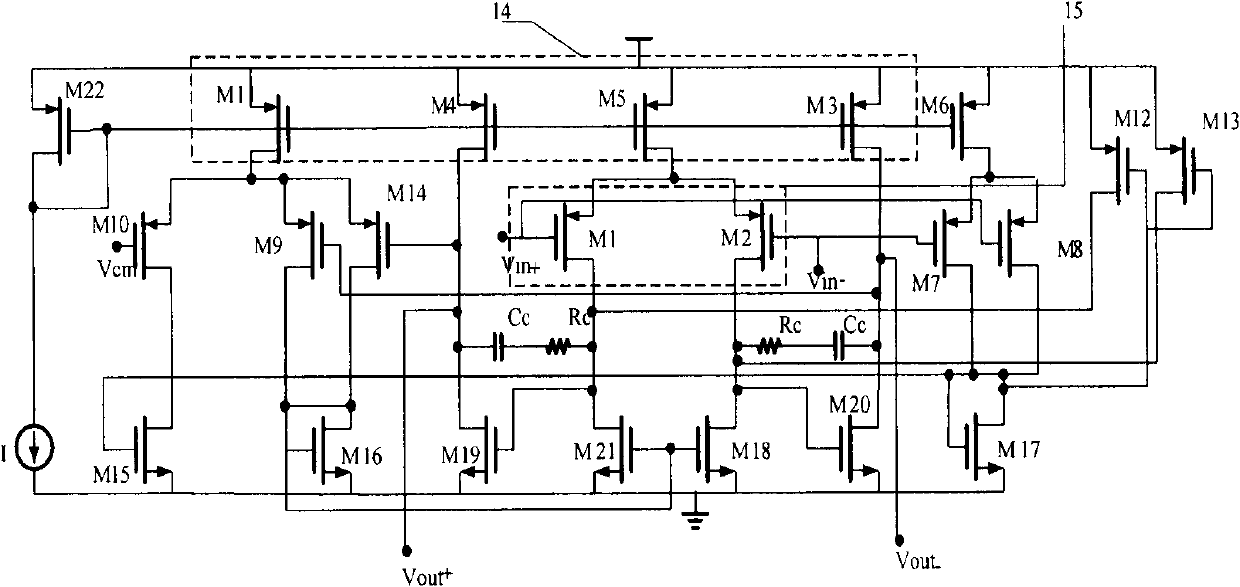

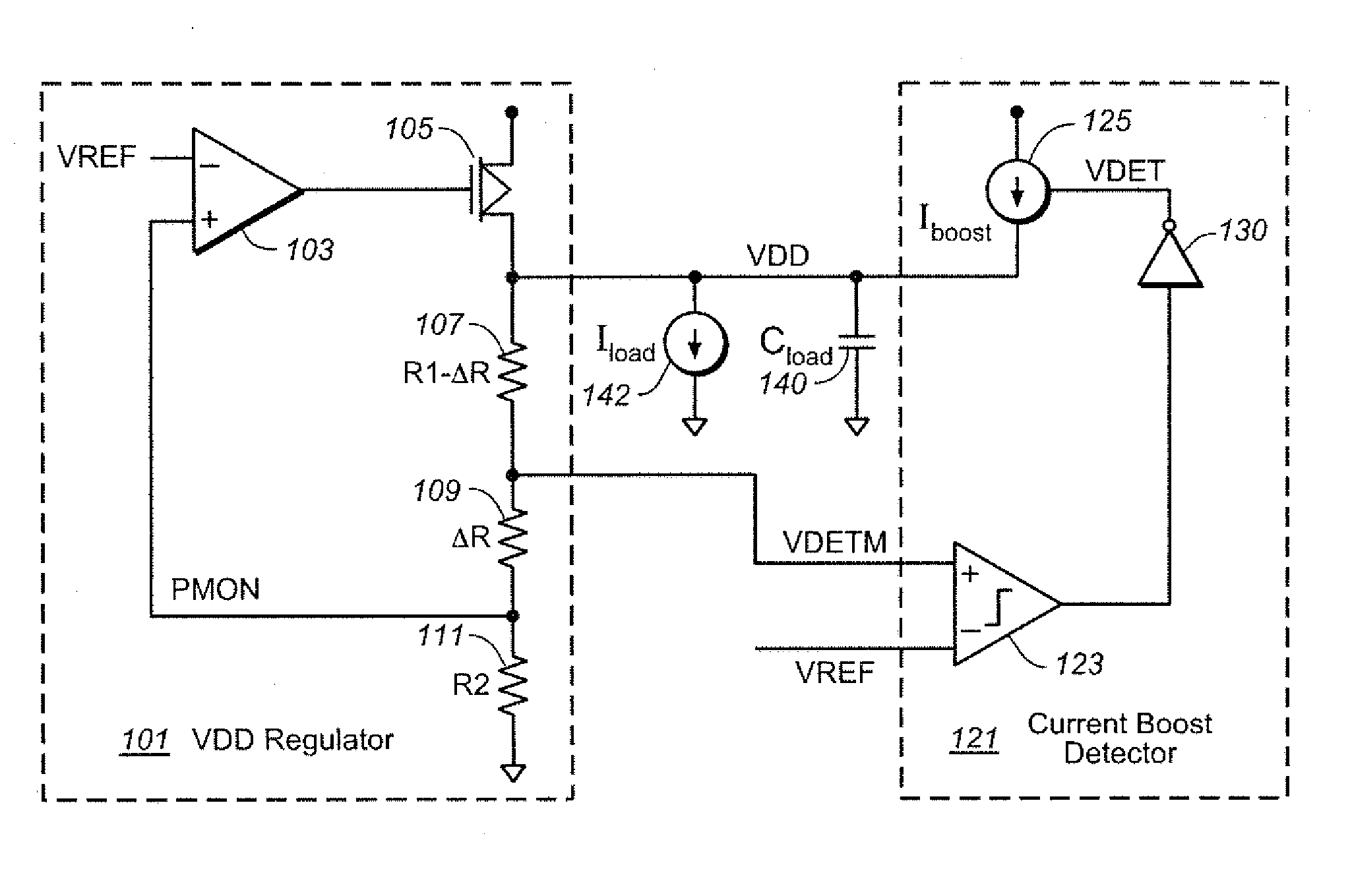

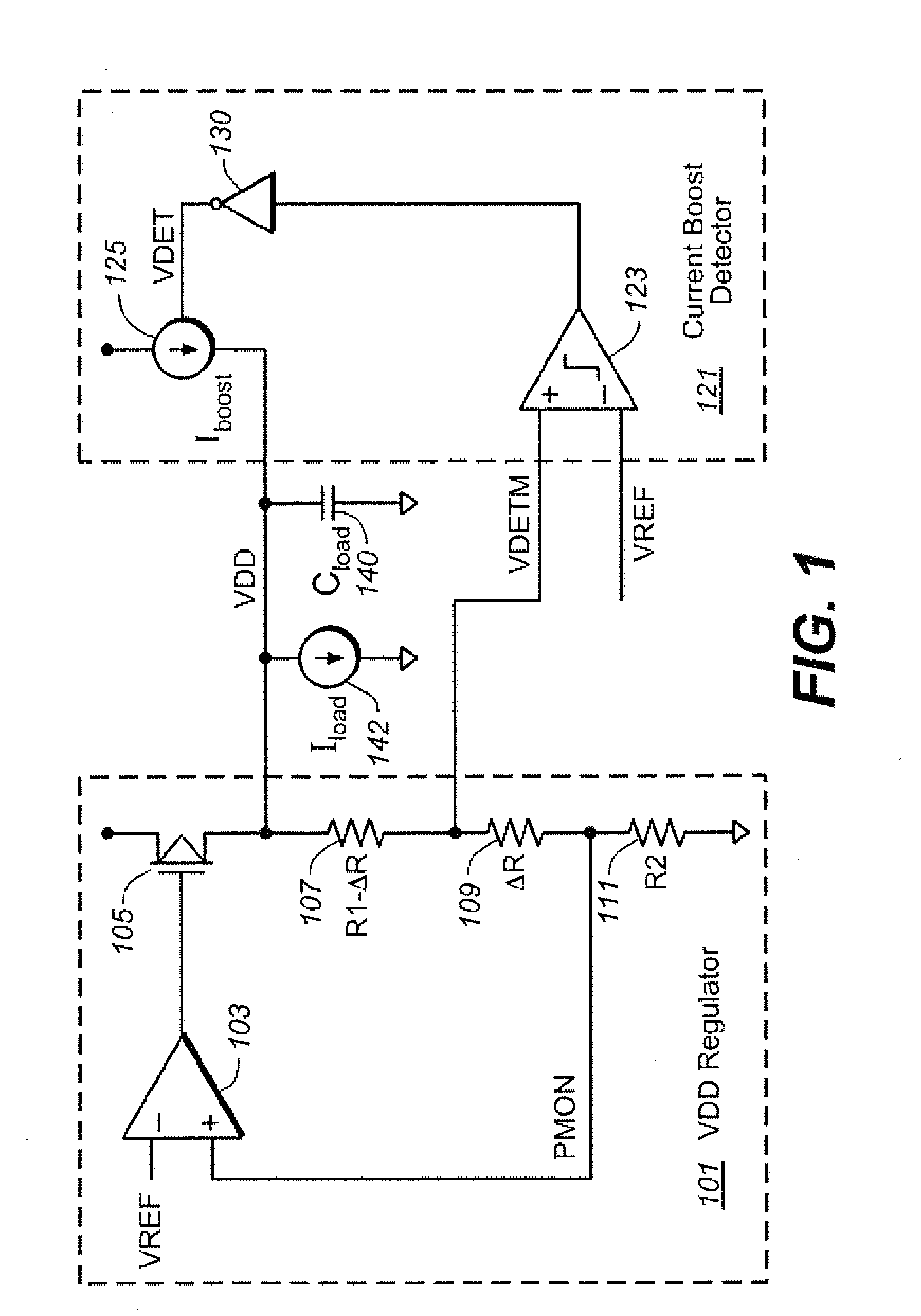

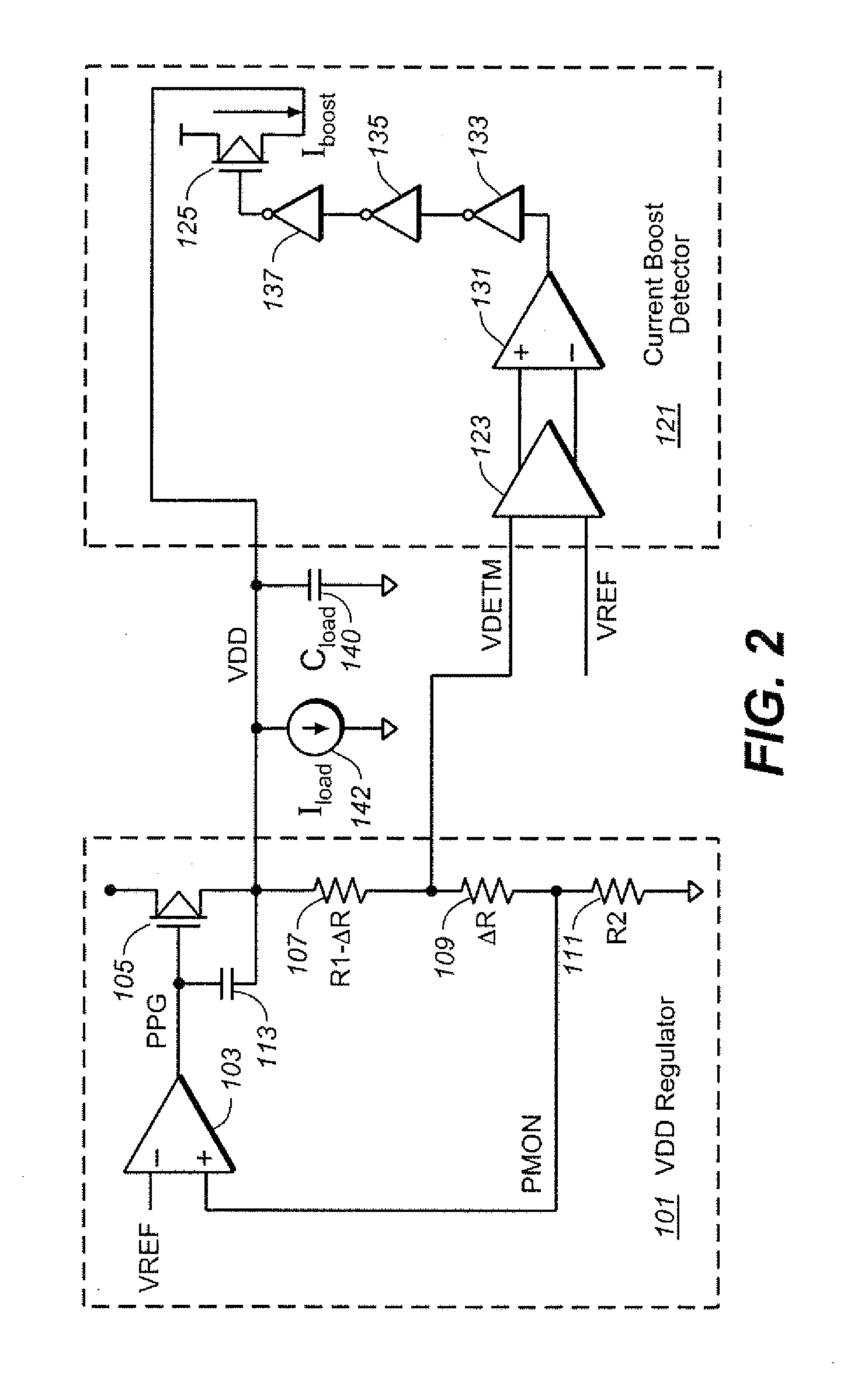

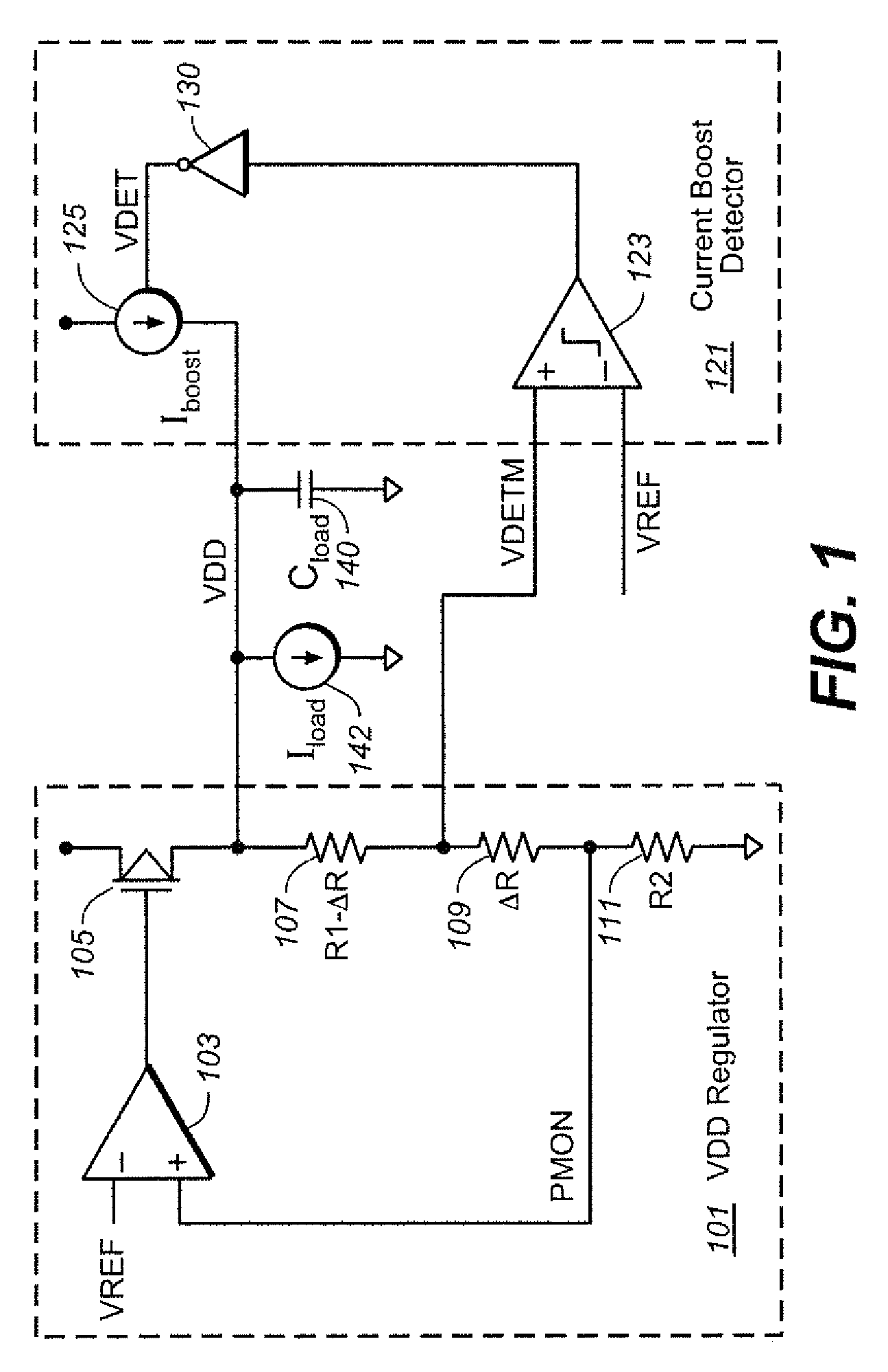

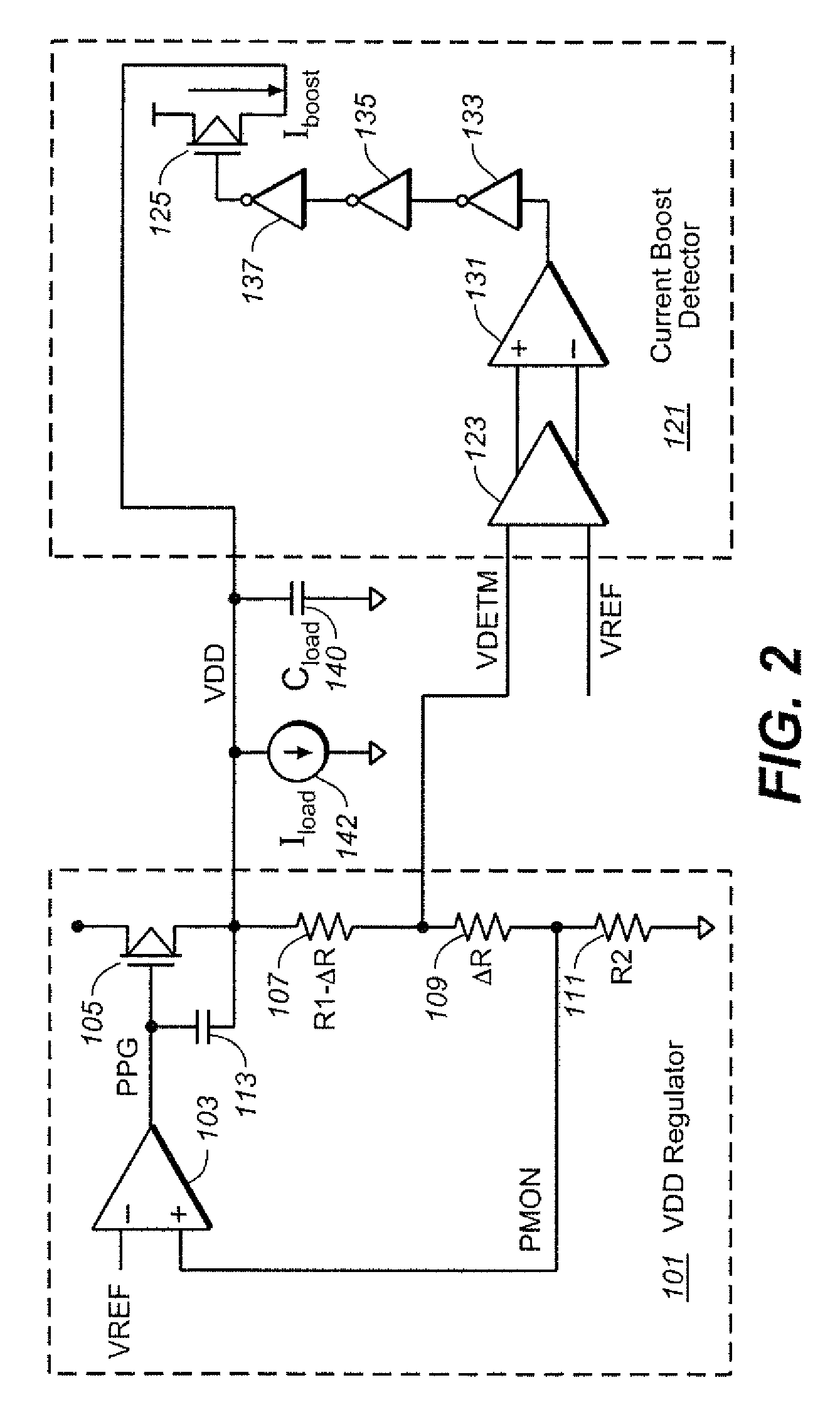

An LDO / HDO circuit adds a supplementary current source to supply the output node. The current boosting section includes a digital comparator with a first input connected to the LDO's feedback loop and a second input connected to a reference level. The comparator then generates a digital output used to control the supplementary current source. This approach also can be used in a far-side implementation, where the local supply level for the load is boosted by the current source based a comparison of this local level and the output of the LDO. Miller capacitive compensation is also considered. Current in shunted to ground from a node in the Miller loop, where the level is controlled by the output of a digital comparator base on a comparison of the circuit's output voltage and a reference level.

Owner:SANDISK TECH LLC

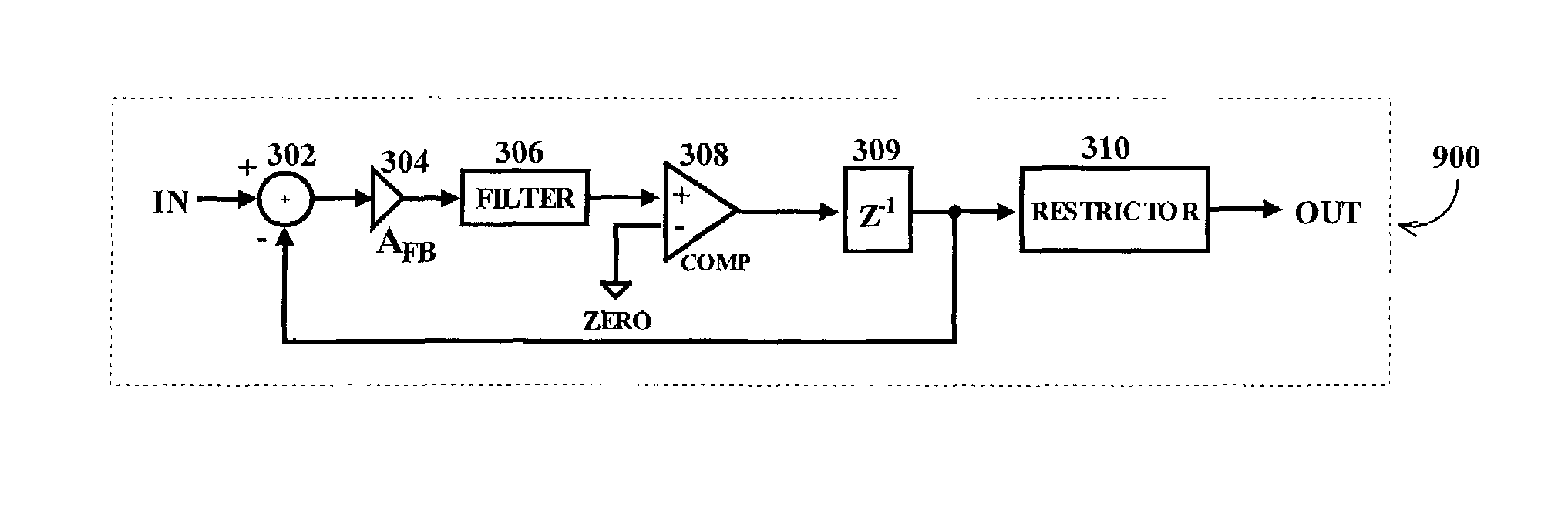

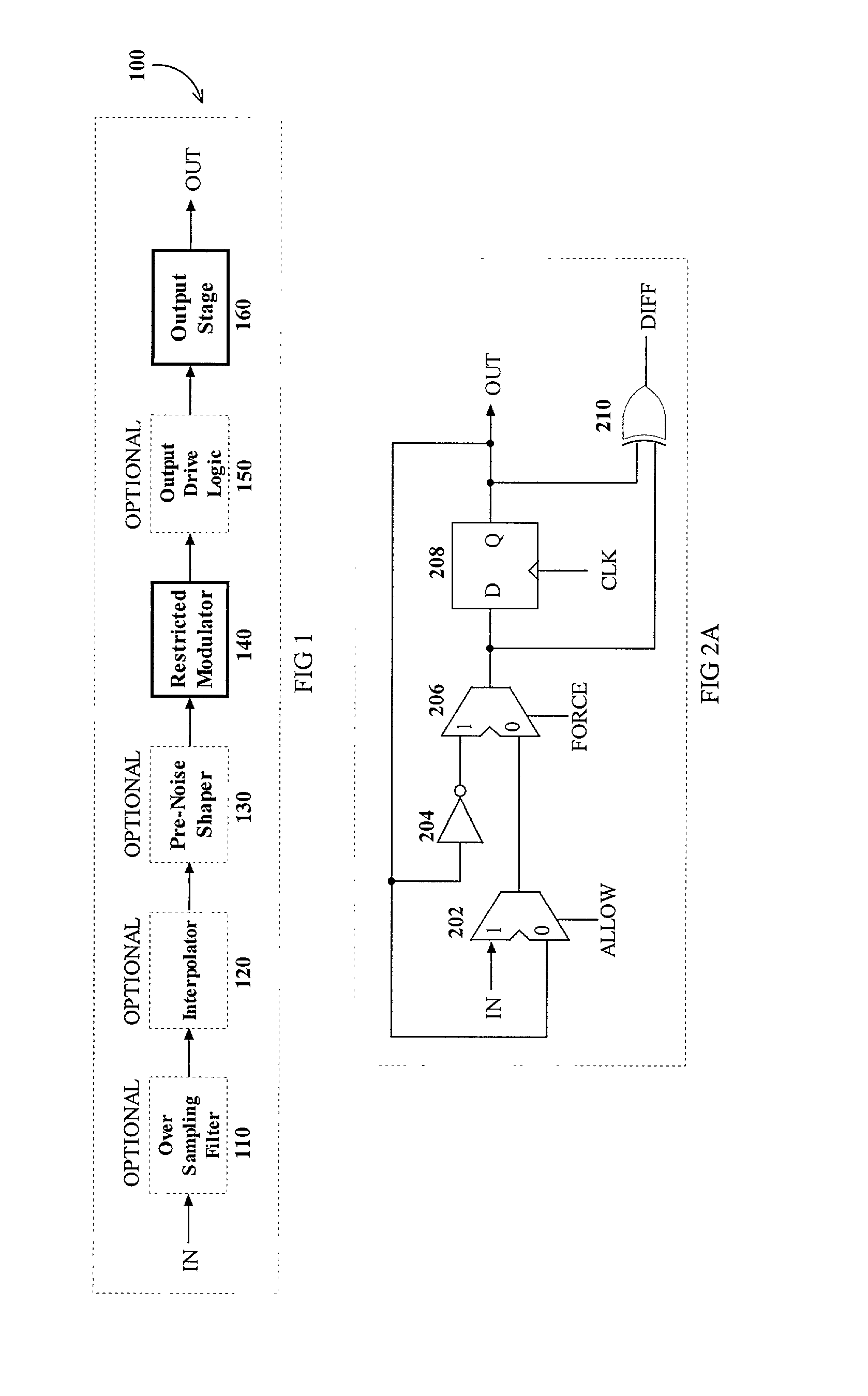

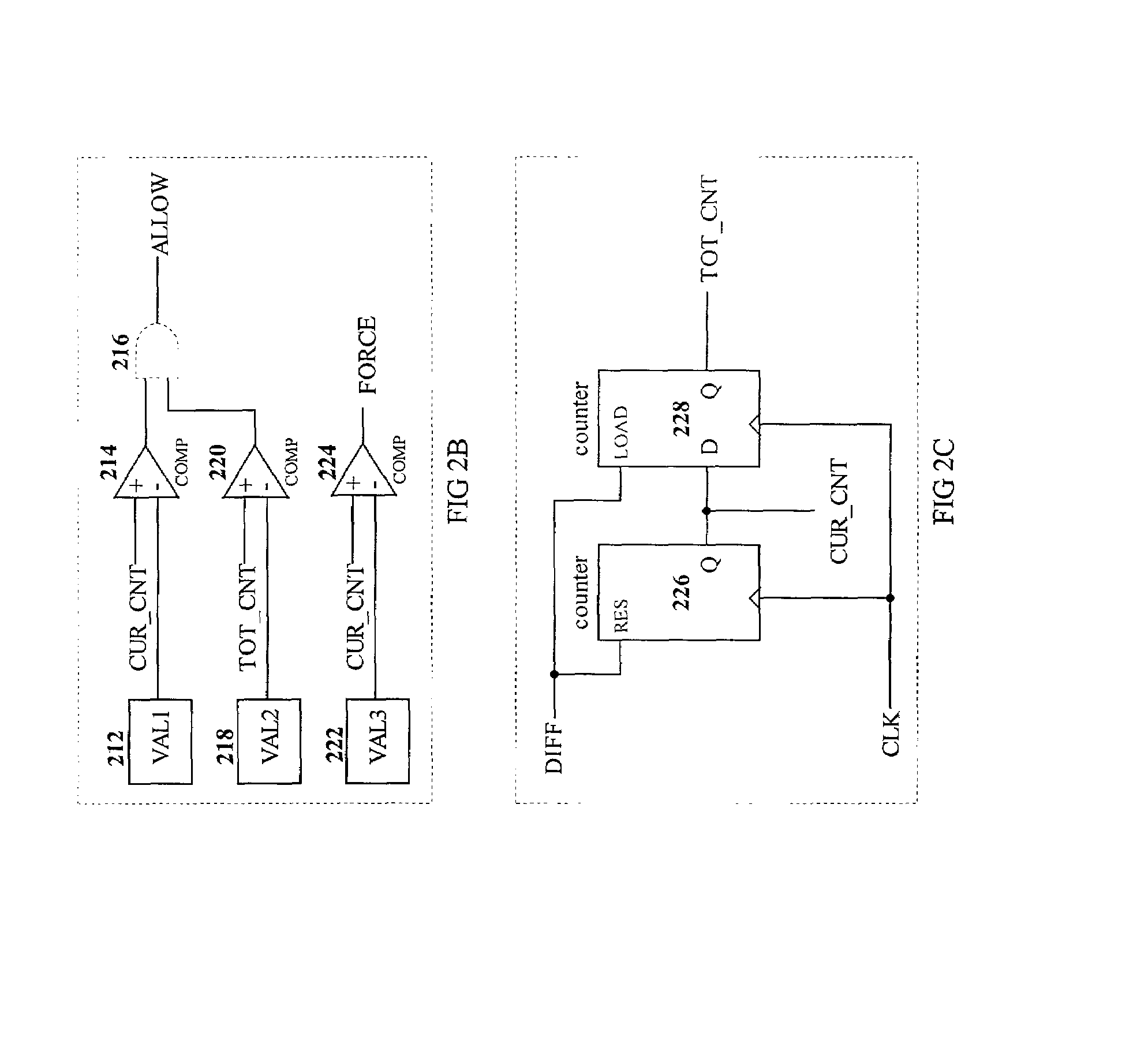

Modulator for digital amplifier

InactiveUS7200187B2Multiple input and output pulse circuitsBatteries circuit arrangementsSoftware engineeringDigital comparator

A digital modulator for driving a digital amplifier. The digital modulator has a subtractor which receives a digital input signal. A filter amplifier receives the output of the filter amplifier and is tuned to an idle frequency of the digital modulator. The digital modulator includes a delay element and a digital comparator. The digital comparator receives the output from the filter and applies it to the delay element. A feedback loop couples the output of the delay element to the subtractor.

Owner:OBRIEN AUDIO

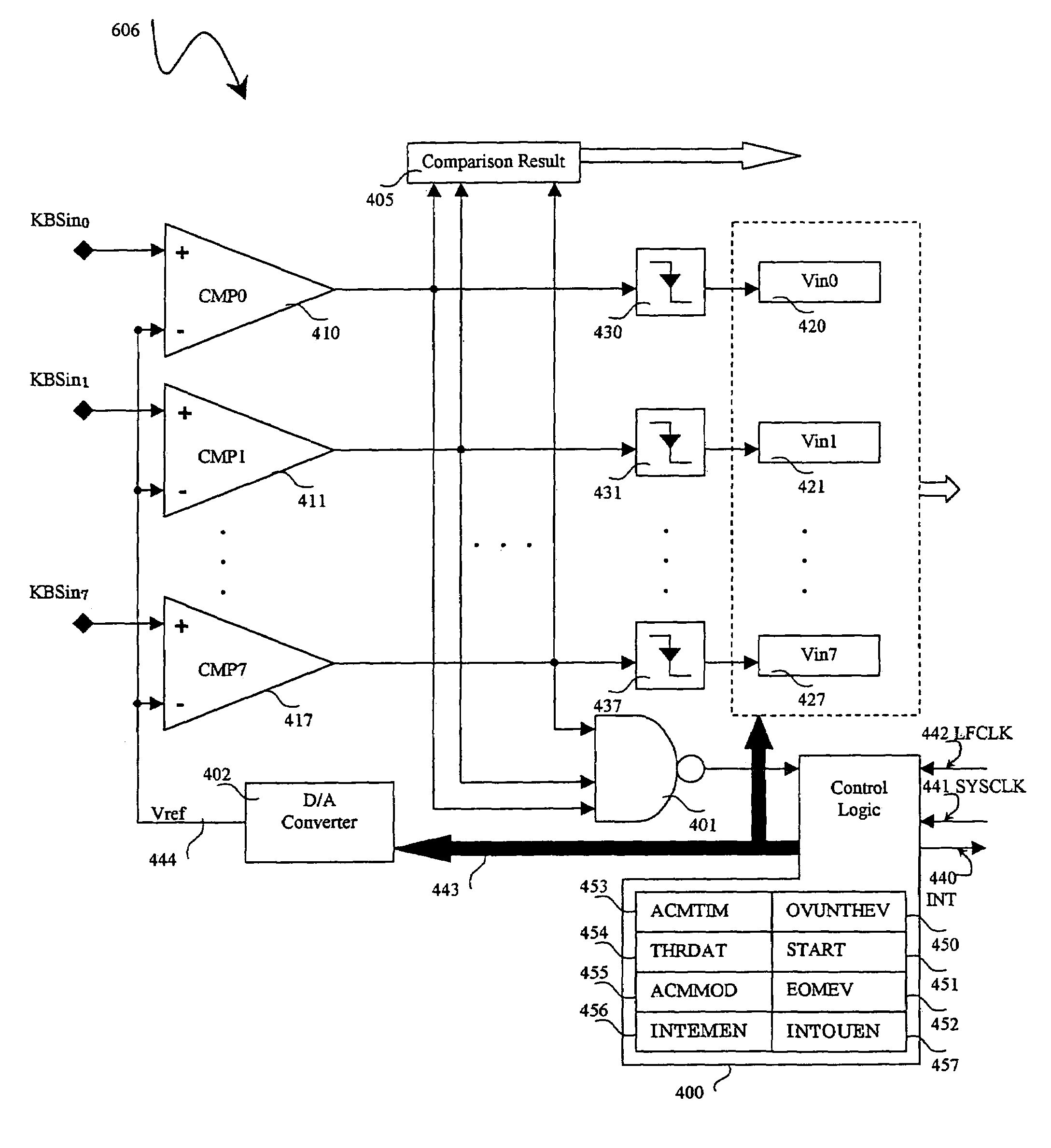

A/D converter with comparators and low-power detection mode for resistive matrix keyboards

InactiveUS7161505B1Low powerQuick checkInput/output for user-computer interactionTransistorLow voltageBuck converter

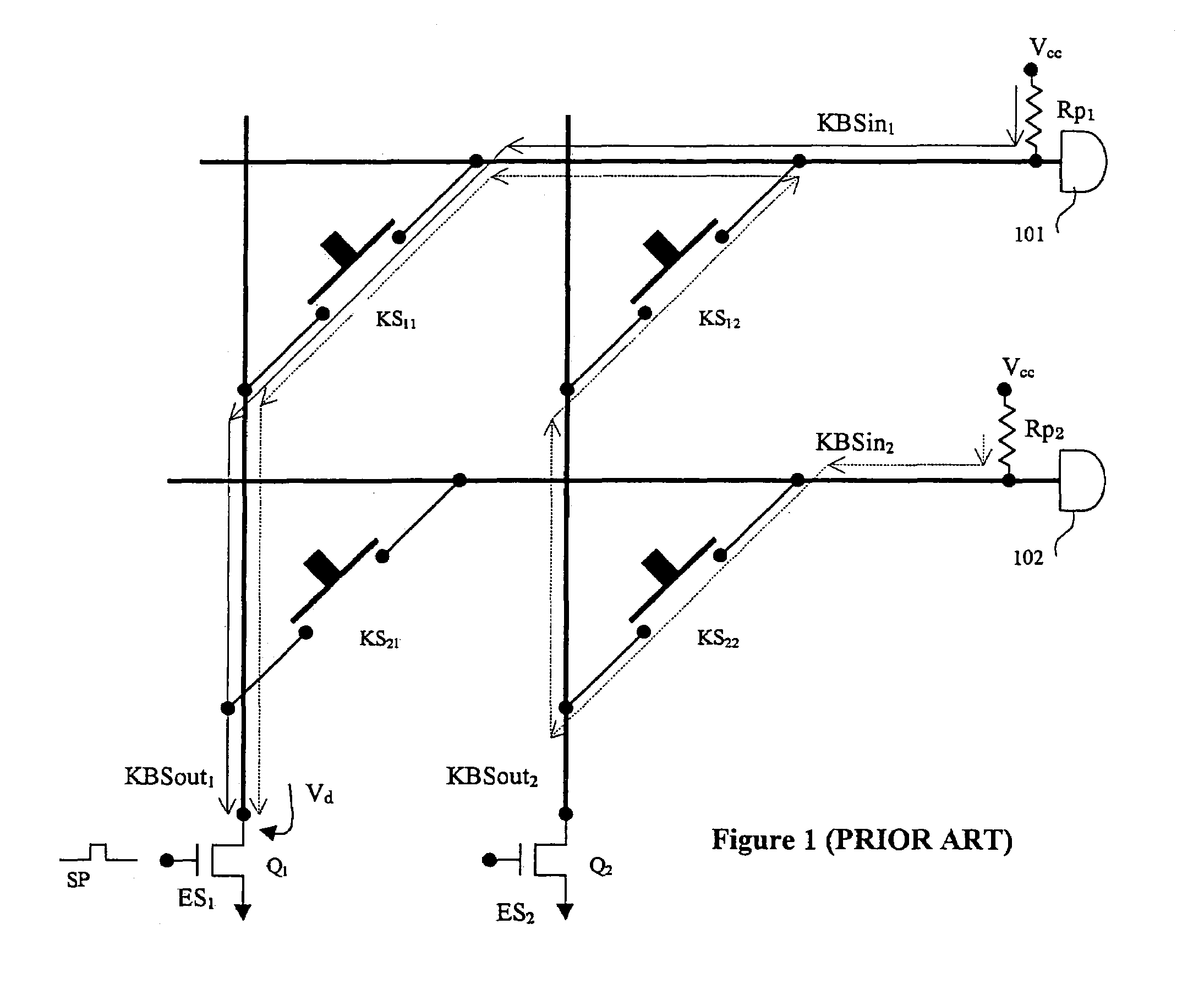

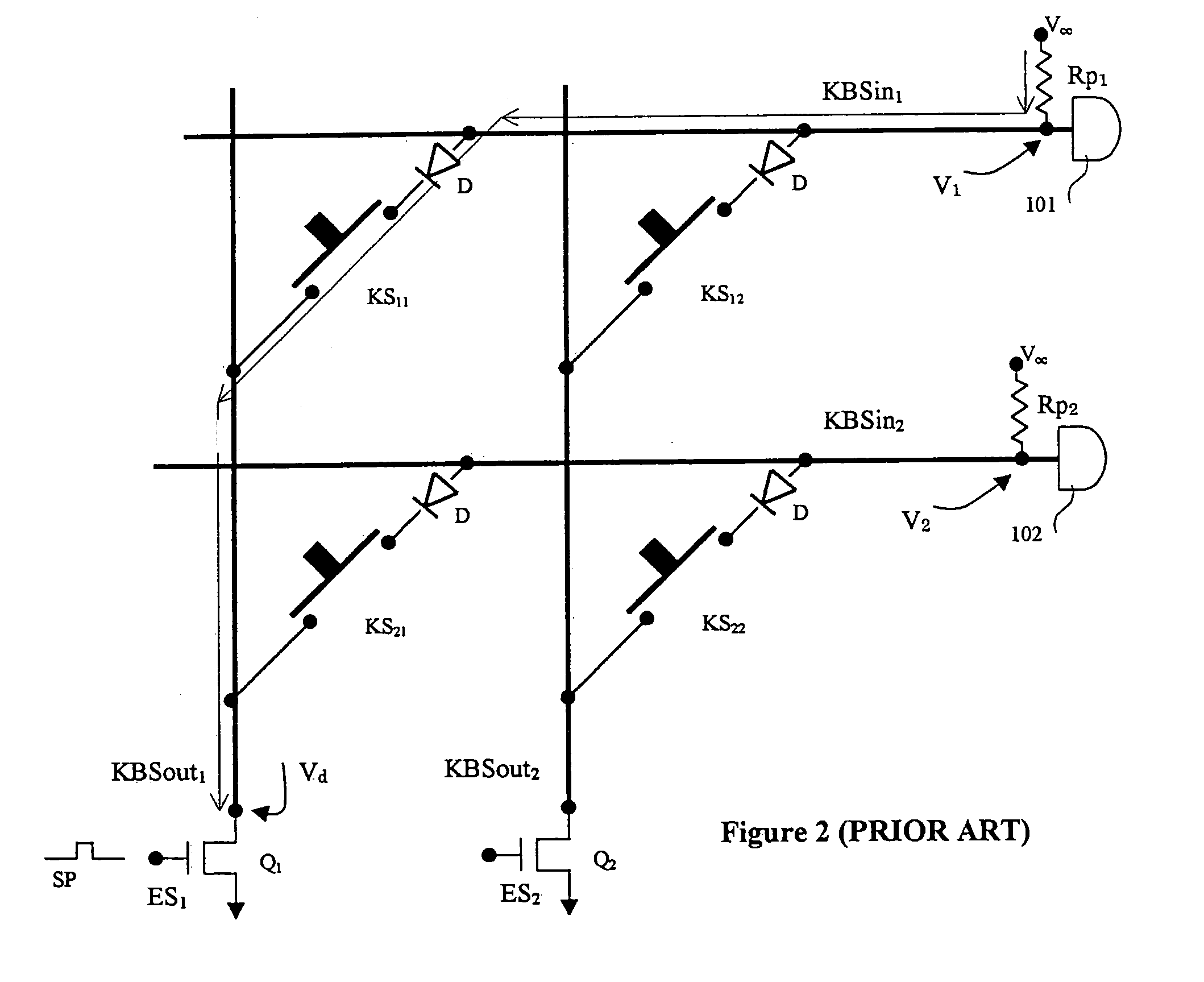

An apparatus and method is disclosed for providing a fast, low power consumption, detection of at least one depressed key in a resistive matrix keyboard. The common contact of each row of a resistive matrix is connected to a first input of each of a plurality of analog / digital comparators capable of switching between high and low voltage states. A common predetermined reference voltage is applied to a second input of each analog / digital comparator using a digital to analog converter. The output of a analog / digital comparator is in a first state if the voltage level applied to the first input is higher than the reference voltage, and in a second state if the voltage level applied to the first input is lower than the reference voltage. The reference voltage is varied to identify which analog / digital comparator has experienced a change of state.

Owner:WINBOND ELECTRONICS CORP

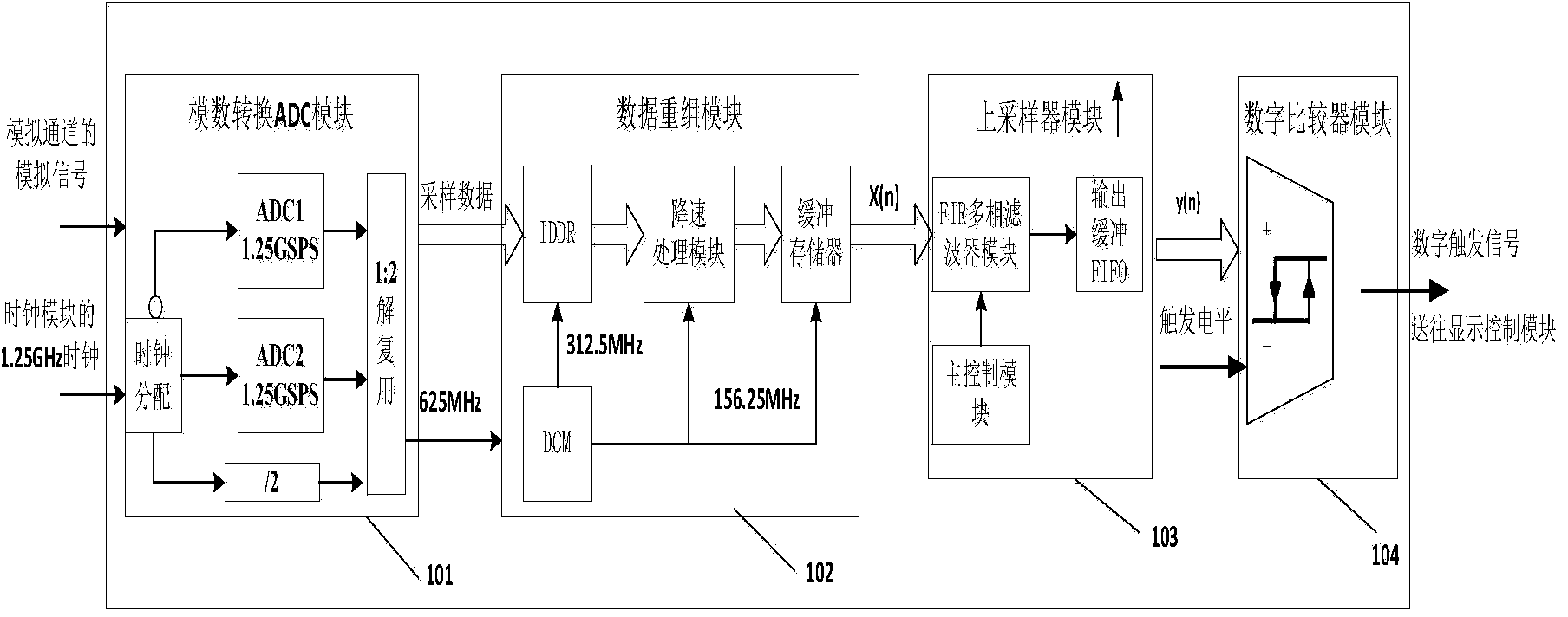

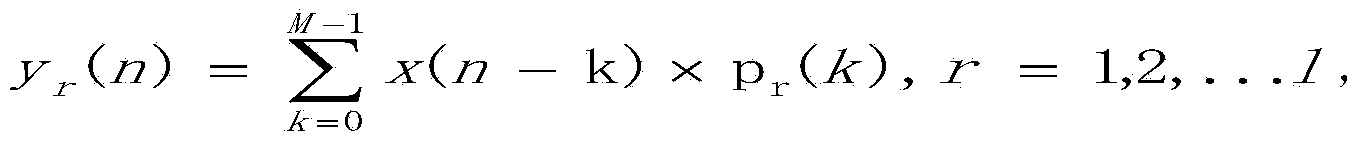

Digital triggering system of oscilloscope

ActiveCN103969483AReduce volumeReduce trigger jitterDigital variable displayData streamComputer module

The invention provides a digital triggering system of an oscilloscope. An ADC module is used for converting analog signals from an analog channel of the oscilloscope into digital signals. A data reconstitution module is used for receiving four 8-bit 625 Mbps data streams output by the ADC module in parallel and outputting x(n) to an up-sampler module in a buffering storage mode. The up-sampler module is used for receiving signals x(n) of the data reconstitution module, so that pixel points of a screen and waveform sampling points are kept consistent. A digital comparator compares signals y(n) output by an up-sampler with a specified triggering threshold value ranging from 0 to 255, an output level is changed, and triggering signals are output. By the adoption of the scheme, the digital triggering system is completely achieved in an FPGA; by the adoption of the digital interpolation mode, the precision of time interval measurement is improved, triggering jittering of the oscilloscope is reduced, and the processing speed and the refresh rate are greatly increased under the circumstance that digital post-processing compensation for jittering is not needed.

Owner:CHINA ELECTRONIS TECH INSTR CO LTD

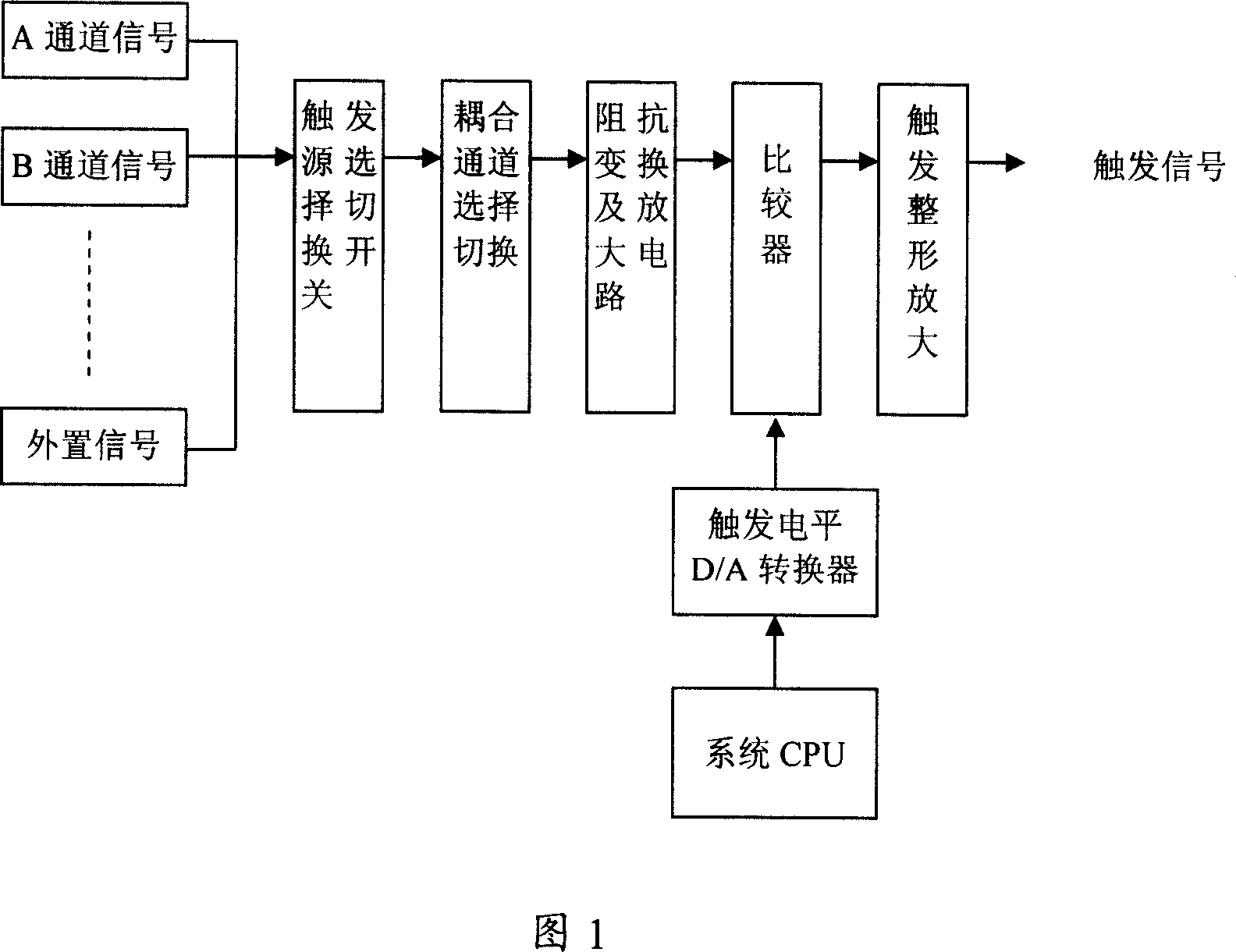

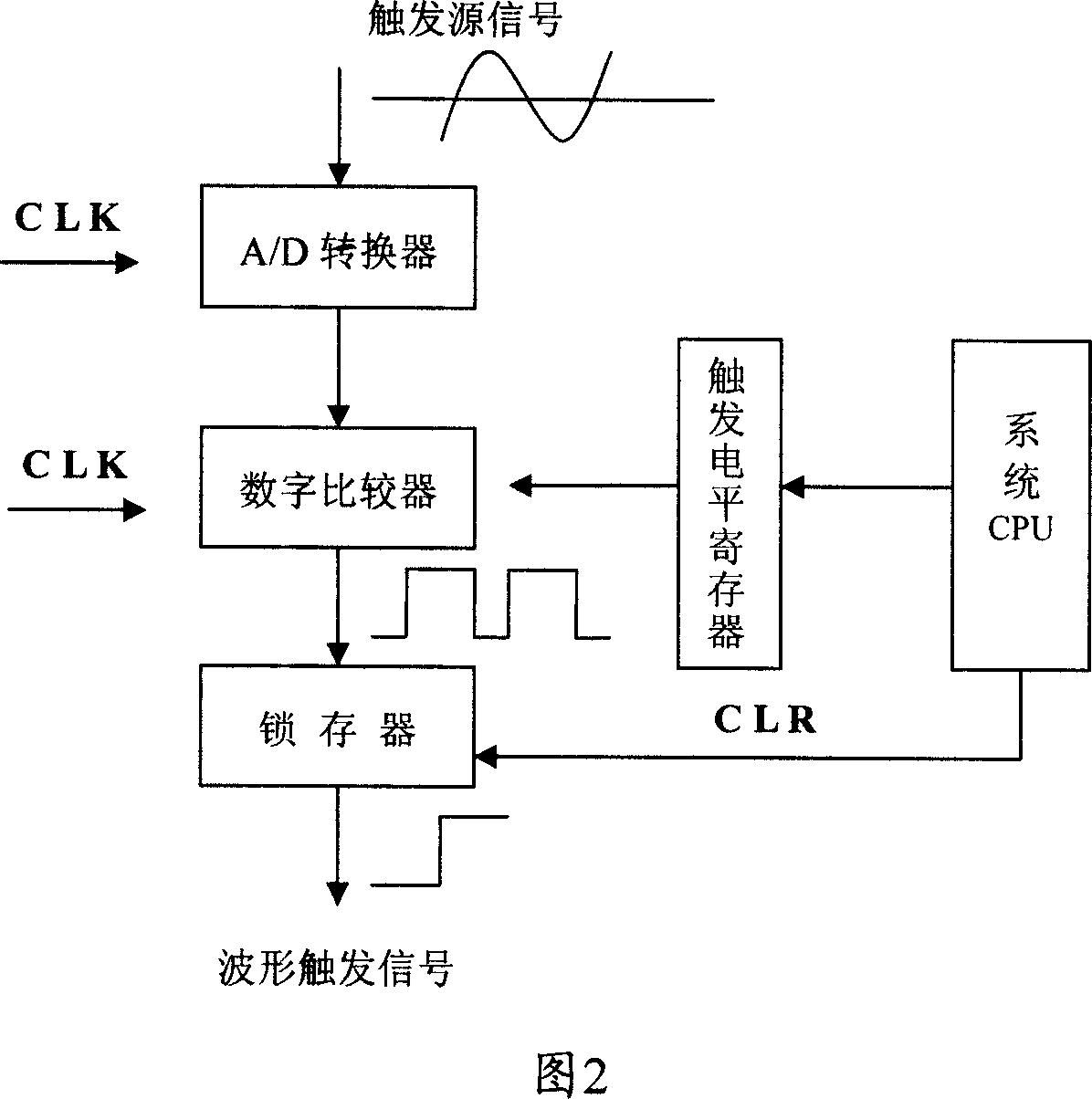

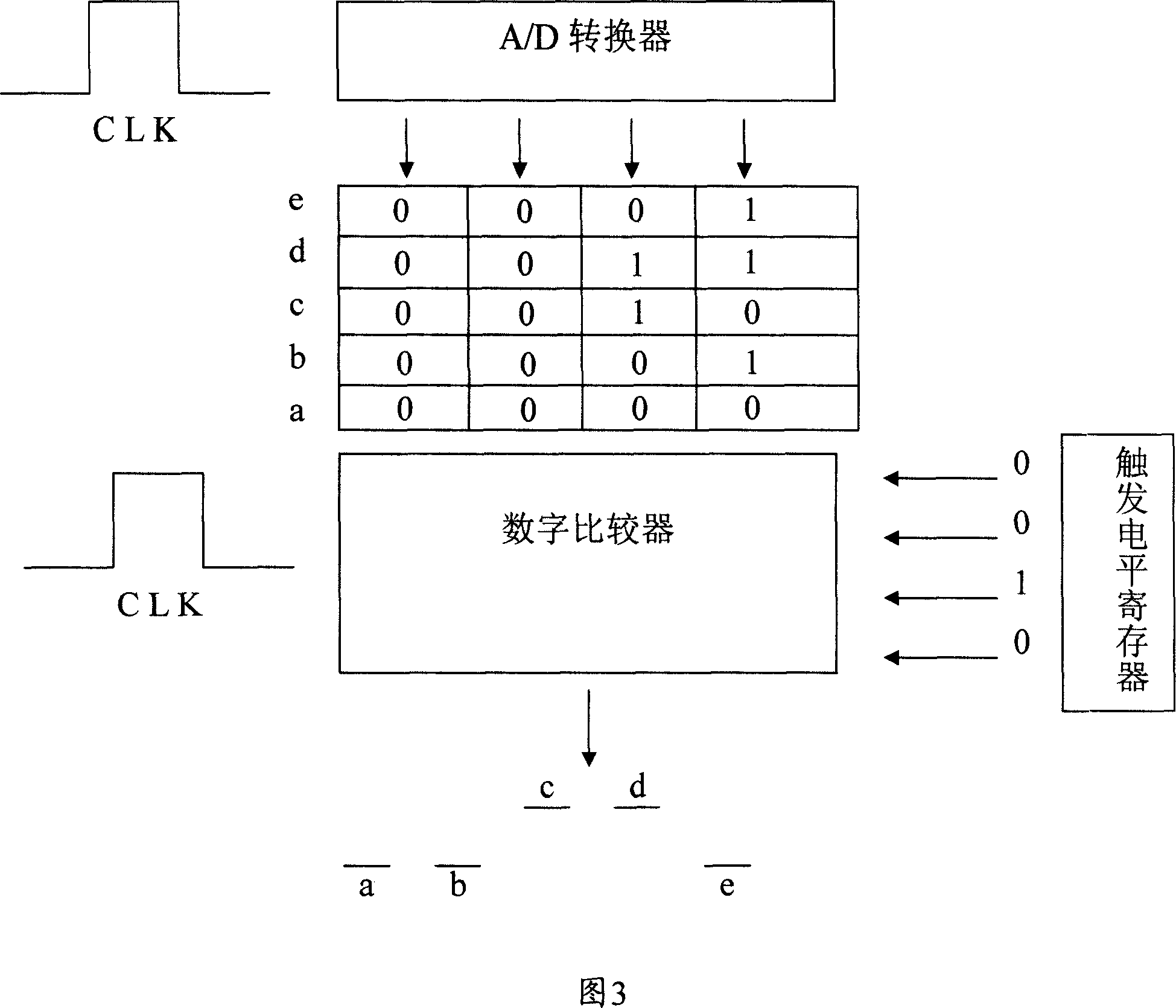

Method and circuit of obtaining wave shape trigger signal of oscilloscope

InactiveCN1948973ASimple selectivityEasy to controlDigital variable displayCathode-ray oscilloscopesWave shapeEngineering

The invention discloses oscilloscope obtaining waveform trigger signal method and circuit. The method includes the following steps: real time sampling for the trigger source signal to gain waveform digital signal; setting trigger level and storing it in trigger level register; using digital comparator to compare waveform digital signal with trigger level to gain compared impulse; using latch to store rising edge or falling edge of the compared impulse to gain waveform trigger signal. It has the advantages of simple circuit, precise and reliable gained waveform trigger signal, low circuit cost etc.

Owner:史松涛

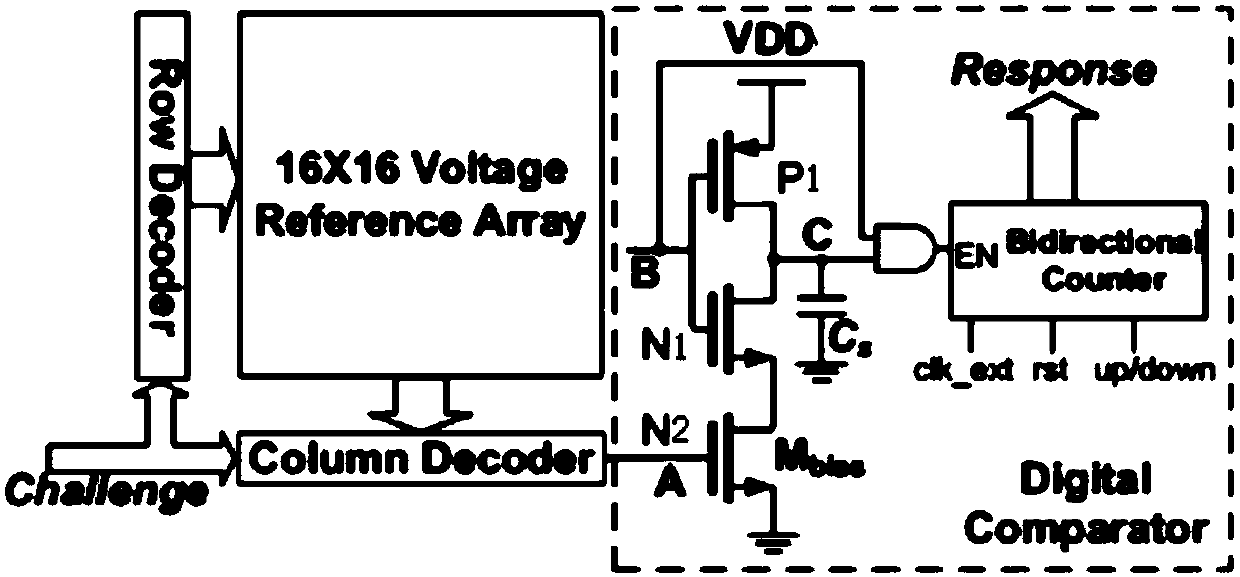

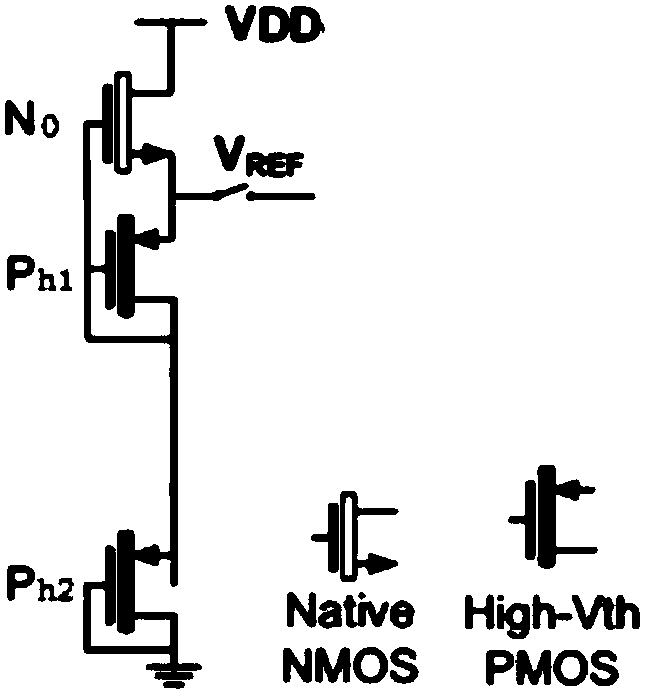

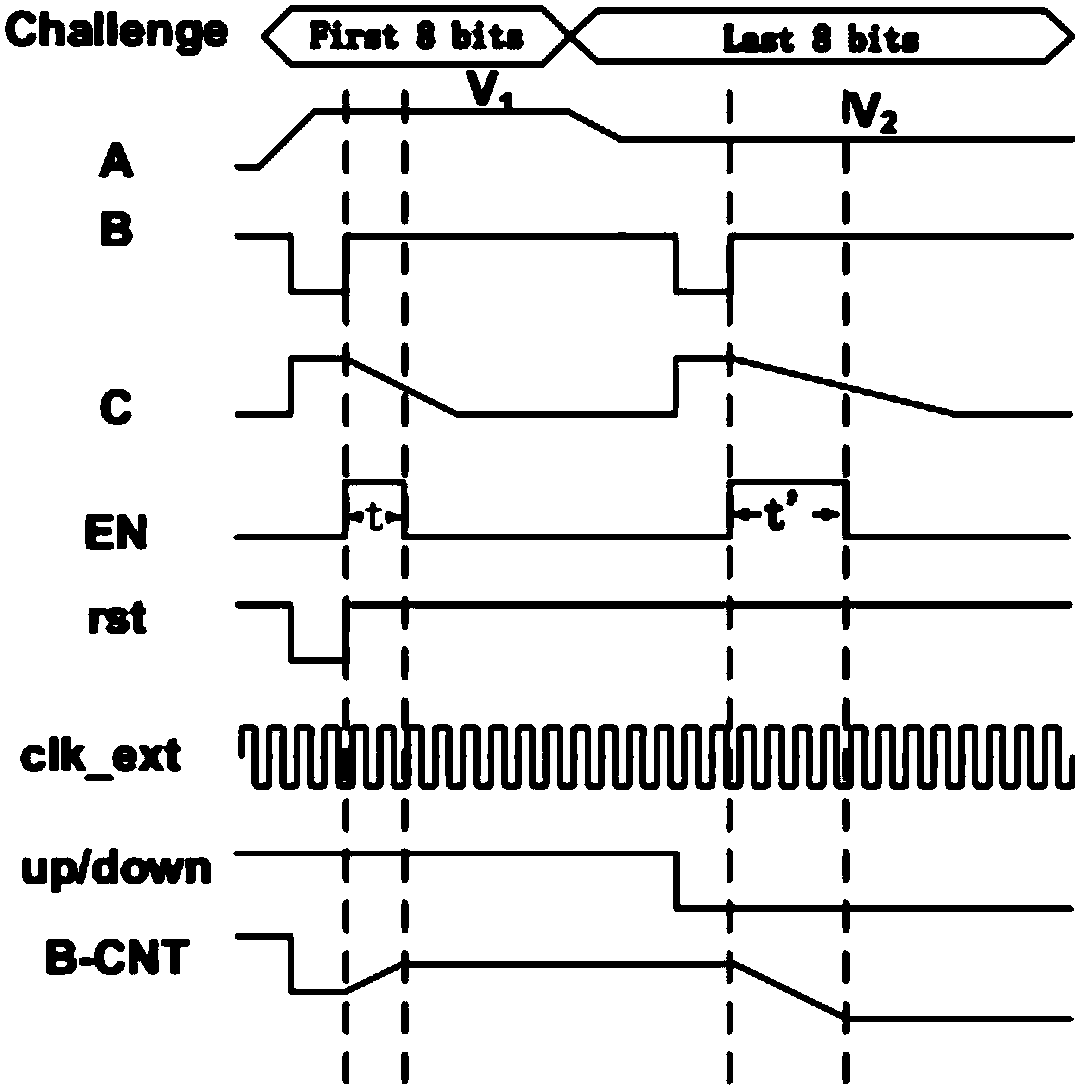

Physical unclonable function (PUF) circuit based on threshold voltage reference

ActiveCN107766750AImprove stabilityReduce areaUser identity/authority verificationInternal/peripheral component protectionCapacitanceHemt circuits

The invention discloses a physical unclonable function (PUF) circuit based on threshold voltage reference. The PUF circuit comprises a threshold voltage reference array, a row decoder, a column decoder and a digital comparator; an input end of the PUF circuit is connected with an input end of the row decoder and an input end of the column decoder; an output end of the row decoder is connected withthe column decoder by means of the threshold voltage reference array; an output end of the column decoder is connected with an input end of the digital comparator; the threshold voltage reference array comprises at least two same single voltage reference circuits, and each single voltage reference circuit comprises a zero-threshold N-channel metal oxide semiconductor (NMOS) transistor, a first high-threshold P-channel metal oxide semiconductor (PMOS) transistor and a second high-threshold PMOS transistor; the digital comparator comprises a first PMOS transistor, a first NMOS transistor, a second NMOS transistor, a sampling capacitor, an AND gate and a bidirectional counter, wherein an output end of the bidirectional counter is taken as an output end of the PUF circuit. The PUF circuit based on threshold voltage reference has the advantages of very high competitiveness in the aspects of uniqueness and reliability, and low power consumption.

Owner:HOHAI UNIV CHANGZHOU

Capacitor measurement device and method thereof

InactiveCN101799496AReduced measurement timeFast measurementResistance/reactance/impedenceElectrical testingMeasurement deviceDisplay device

The invention relates to capacitor measurement device and method thereof. The device comprises a four-threshold digital comparator, a variable gain amplifier, a size variable positive and negative constant flow source, a rapid analog / digital converter, a microprocessor and a display, wherein the microprocessor receives output signals of the four-threshold digital comparator and the analog / digitalconverter and outputs measurement results to the display; the microprocessor selects the positive and negative constant flow source and the amplification factor of the amplifier according to the capacity of a measured capacitor; and voltage on the measured capacitor amplified by the variable gain amplifier is measured by the rapid analog / digital converter, and the measurement results are output to the four-threshold digital comparator. In the capacitor measurement method, by the constant flow forward charge and back discharge of the measured capacitor, the microprocessor figures out the measurement result of a primary capacitance value according to time interval of the forward charge and back discharge between two threshold values preset by the four-threshold digital comparator, the numerical value of the constant flow source and the amplification factor of the variable gain amplifier. The invention greatly reduces the measurement time of the capacitor under the condition of using smaller charge / discharge current and eliminates the influence of the absorption effect of the capacitor on the measurement accuracy by the installation of the four-threshold digital comparator.

Owner:臧佳菁

Increasing error correction in data streams encoded with linear block code

ActiveUS7921351B2Increase error correction capability of decoderCorrection capabilityError preventionCode conversionData streamBlock code

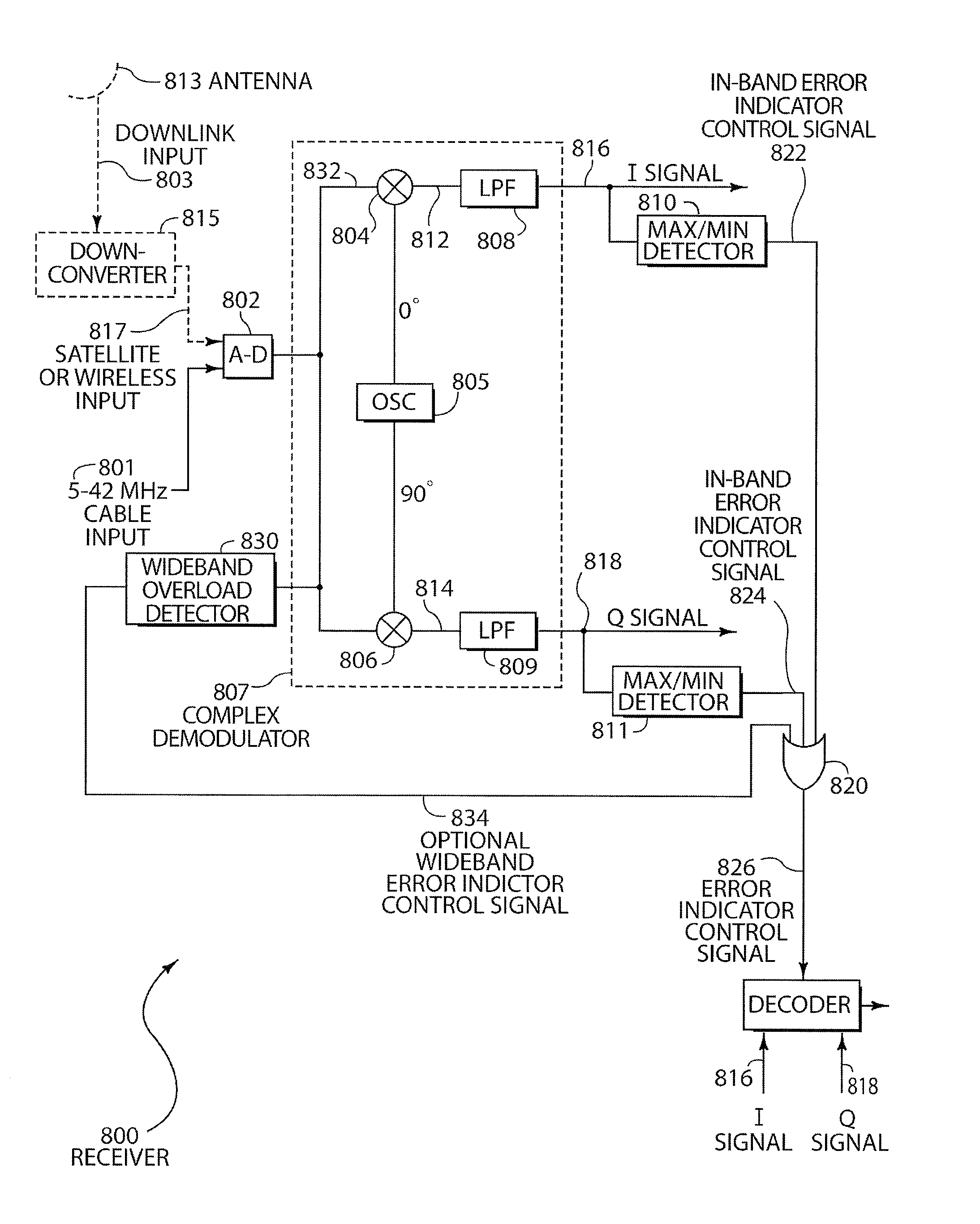

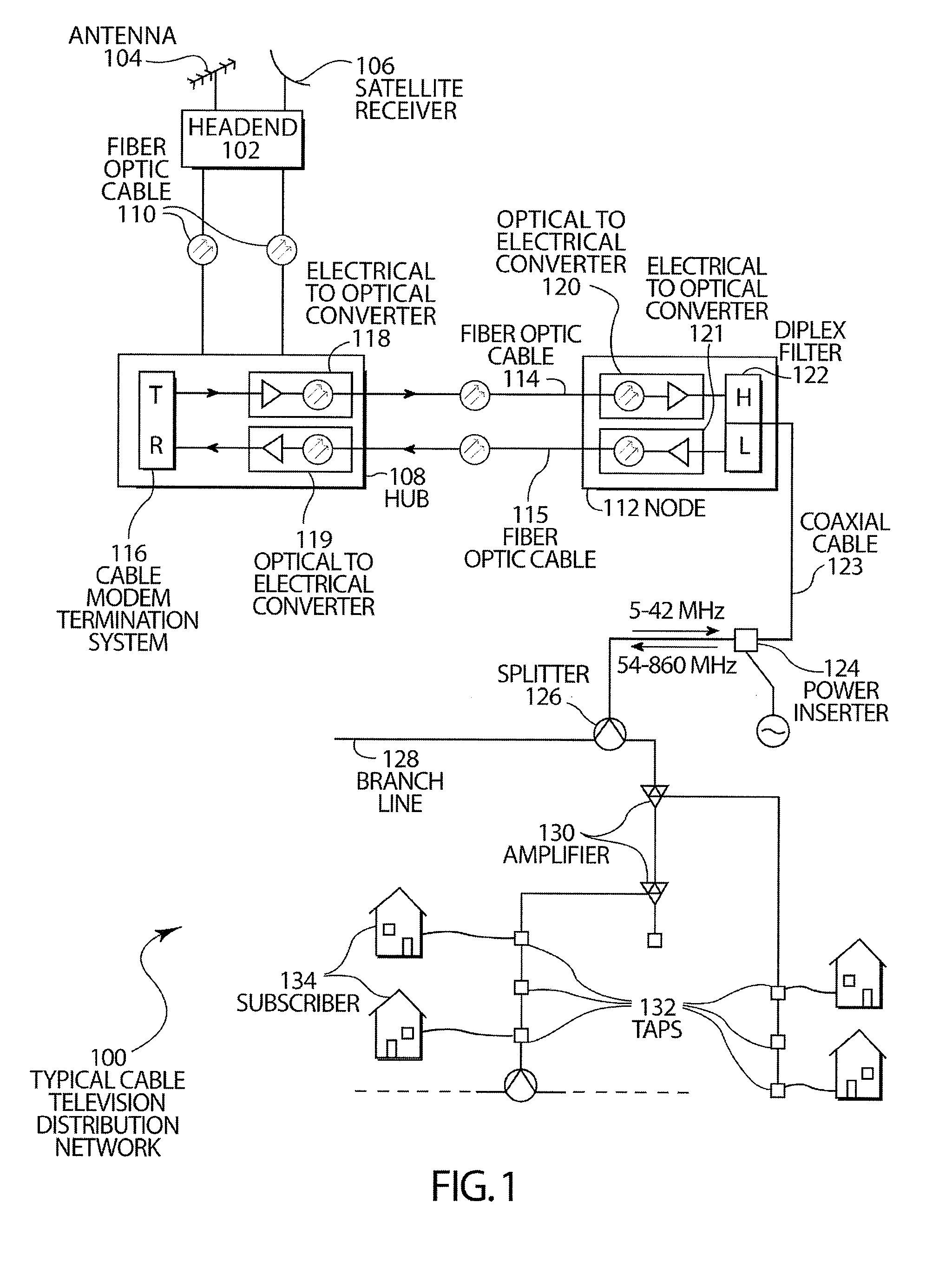

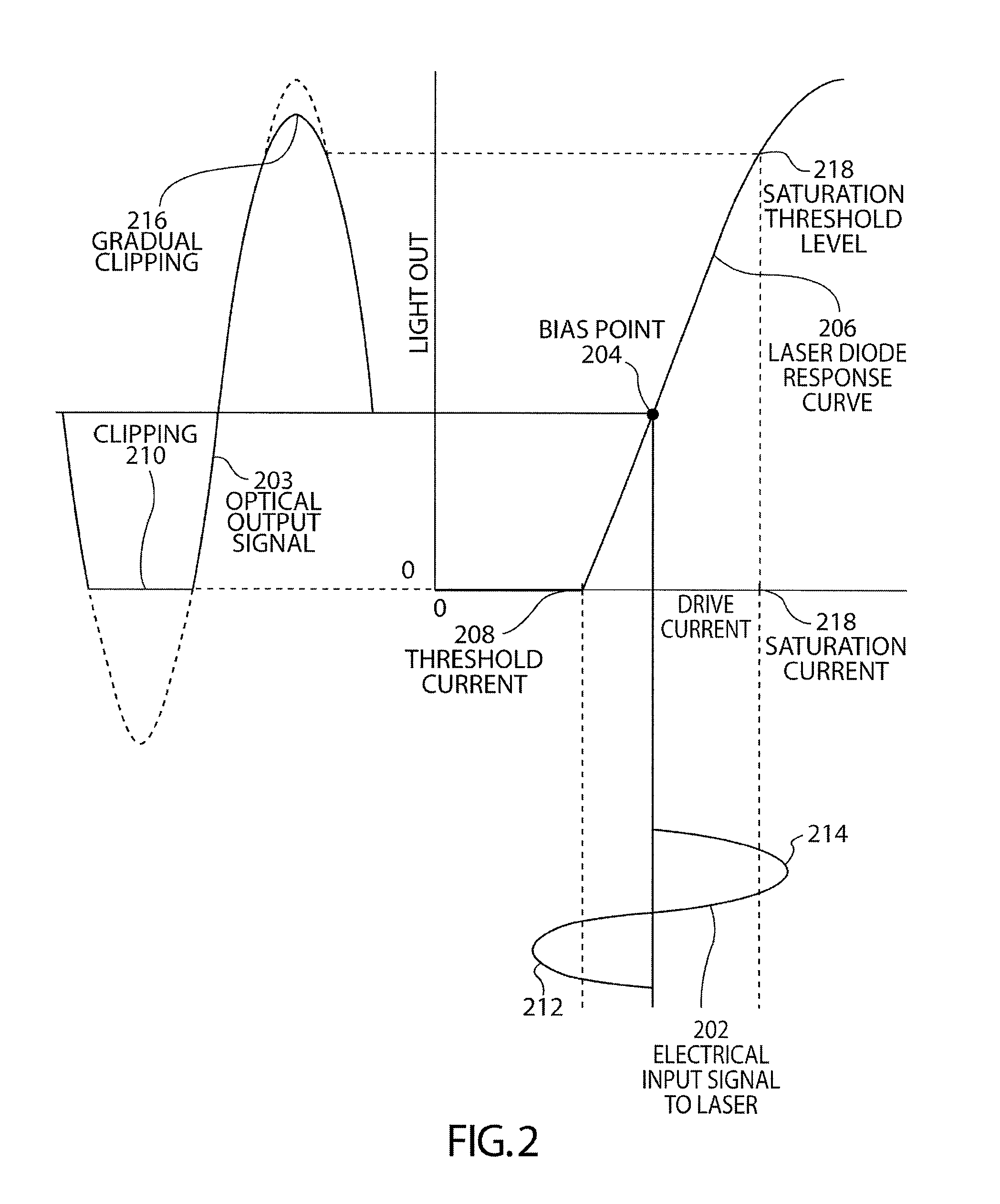

Disclosed is an apparatus and method for increasing the error correction capabilities of a receiver circuit that receives a data stream of encoded data symbols that are encoded with a linear block code. Analog and digital comparator circuits are used to detect laser clipping or analog to digital converter overloading. Corrupted symbols are detected by comparing in-phase and / or quadrature phase baseband signals with pre-determined threshold limits that indicate that the in-phase and quadrature phase signals have exceeded the normal signal trajectory of an unimpaired signal. Corrupted symbols may also be detected by determining that the laser has been clipped. Corrupted symbols are marked for erasure prior to decoding and error correction. Erasure of corrupted signals increases the error correction capabilities of the decoder circuit.

Owner:CABLE TELEVISION LAB

Feedforward automatic gain control circuit working in extremely low voltage current mode

ActiveCN102571009AReduce power consumptionResolve continuityGain controlAutomatic controlLow voltage

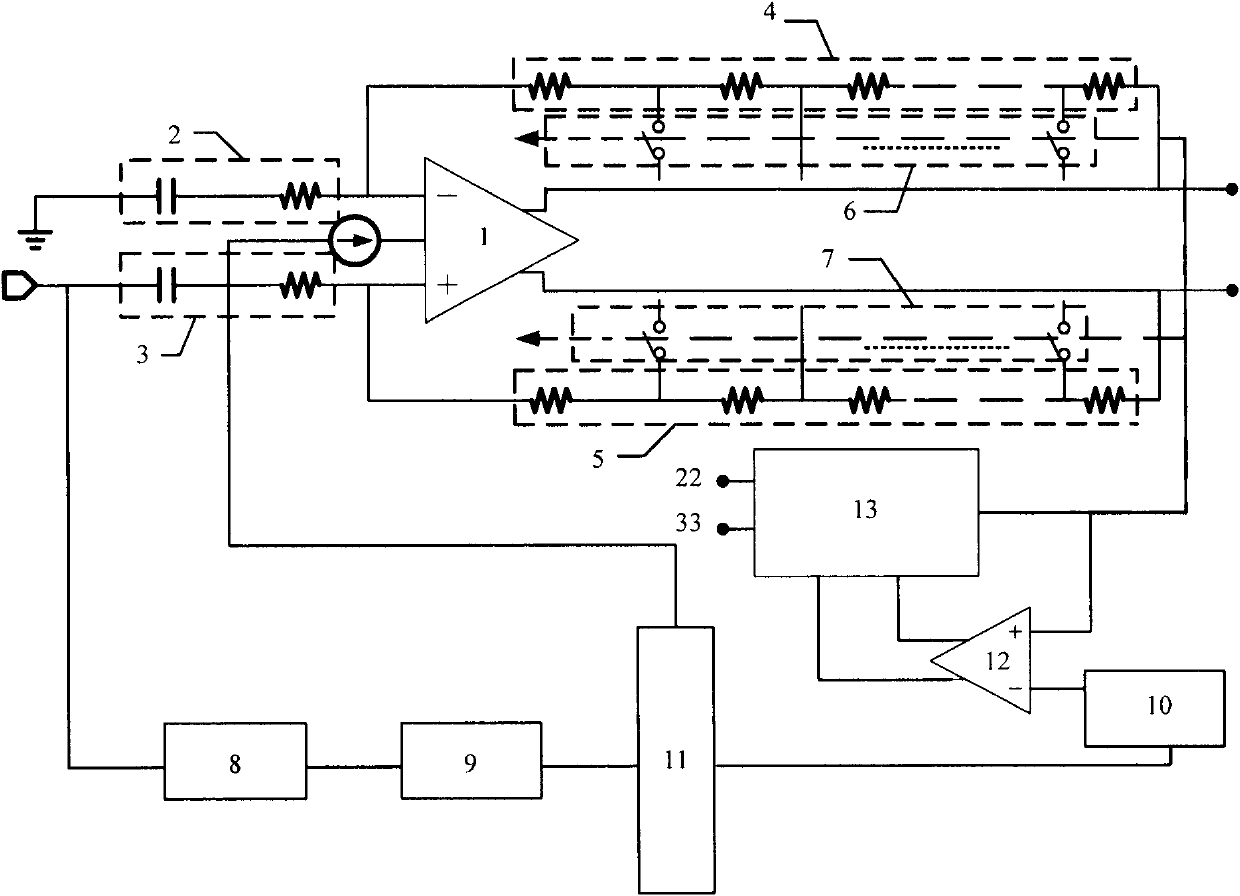

The invention provides a feedforward automatic gain control circuit working in an extremely low voltage current mode, and relates to the technology of sensors. The feedforward automatic gain control circuit comprises a fully differential operational amplification unit, a capacitive-resistance device, a resistor array, a control switch, rectifier, a filter, a controller, a digital reference table, a digital comparator and an add-subtract counter, wherein the fully differential operational amplification unit is used for correspondingly amplifying voltage signals of an output end of a microphone according to variation of the resistance array; the rectifier is used for converting the voltage signals into current signals and rectifying current; the filter is used for filtering the current output by the rectifier and carrying out envelop detection on input signals; the digital controller is used for comparing current output by the filter with the reference current to obtain digital control signals in the digital reference table; the digital comparator is used for comparing output of the add-subtract counter with the digital control signals, when the sound volume is in different levels, the amplifying multiple of the fully differential operational amplification unit is adjusted, so that the hearing of the auditorily handicapped is protected; when the sound volume is in a normal state, the amplifying multiple of the fully differential operational amplification unit is restored to the original value, so that the automatic gain control on the different sound volumes is realized.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

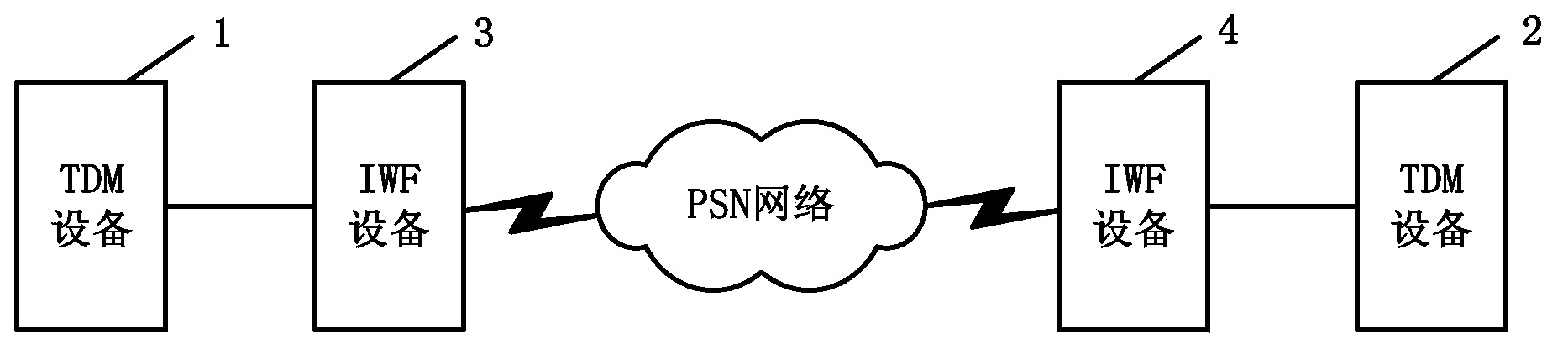

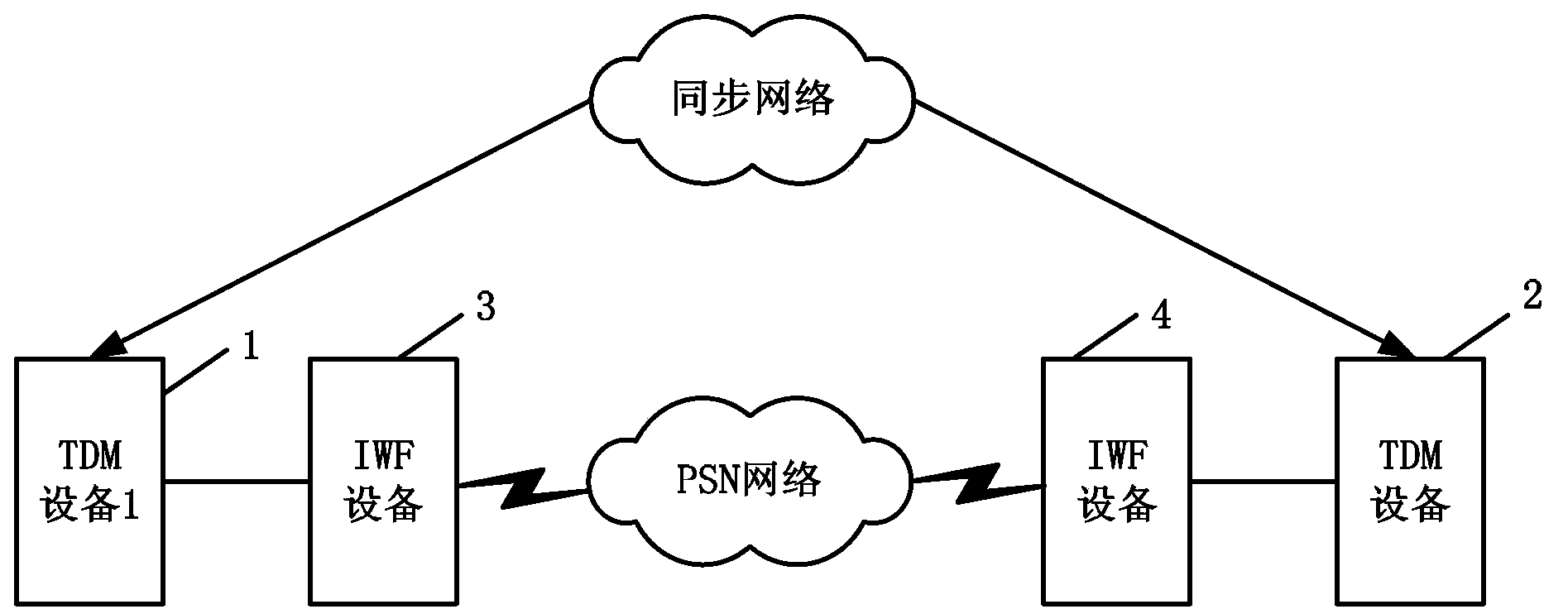

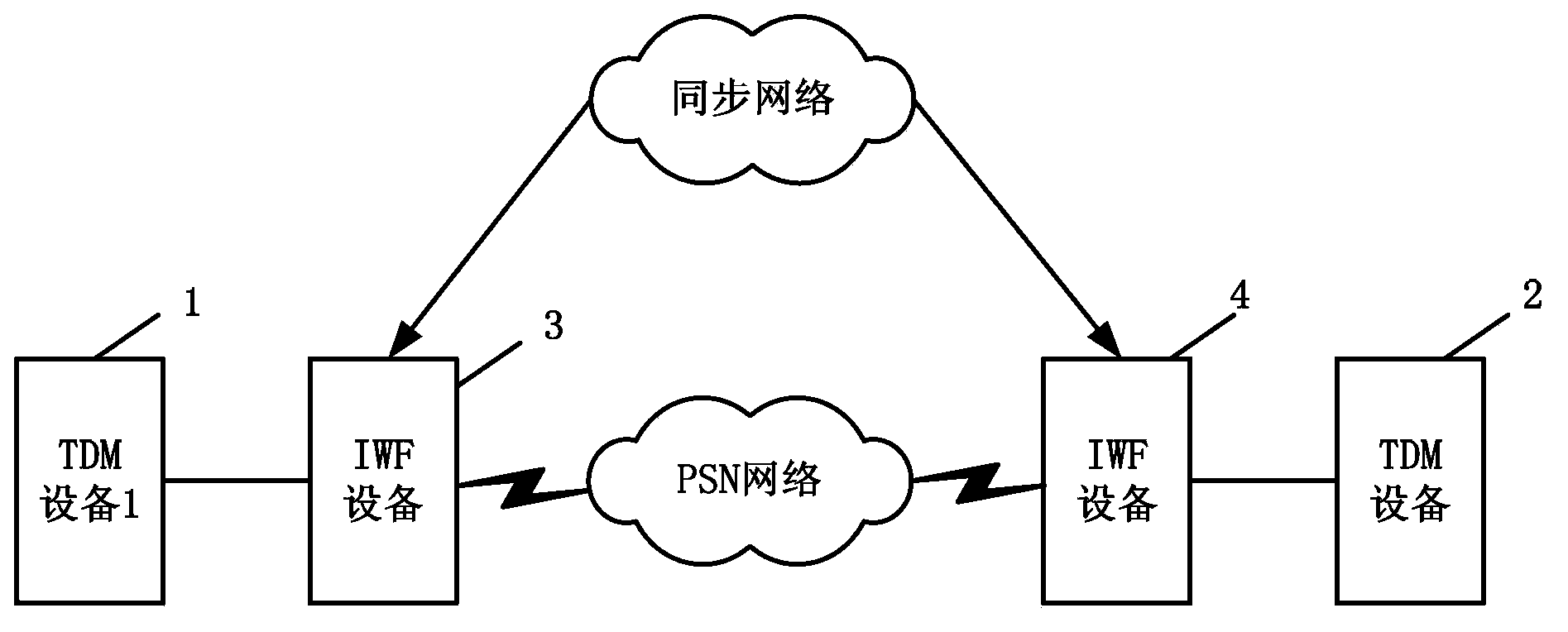

Method, device and system for clock synchronization

The invention discloses a method, device and system for clock synchronization. According to the method for clock synchronization, after a triggering controller in a secondary IWF device receives a master clock pulse count value sent by a primary IWF device, if the primary clock pulse count value is judged as the first primary clock pulse count value received by the secondary IWF device, the triggering controller indicates a secondary pulse counter to count output clock signals of a voltage-controlled oscillator with the primary clock pulse count value as an initial value, otherwise, the triggering controller indicates a numeric comparator to load the primary clock pulse count value and the secondary clock pulse count values, the numeric comparator generates a control signal according to the difference values of the primary clock pulse count value and the secondary clock pulse count values, and the output clock frequency of the voltage-controlled oscillator is adjusted. Due to the fact that the clock frequency of the secondary IWF device follows the clock frequency of the primary IWF device all the time, the transmission quality of TDM data can be maintained at the normal level through the shaking and drifting indexes of clock recovering.

Owner:CHINA TELECOM CORP LTD

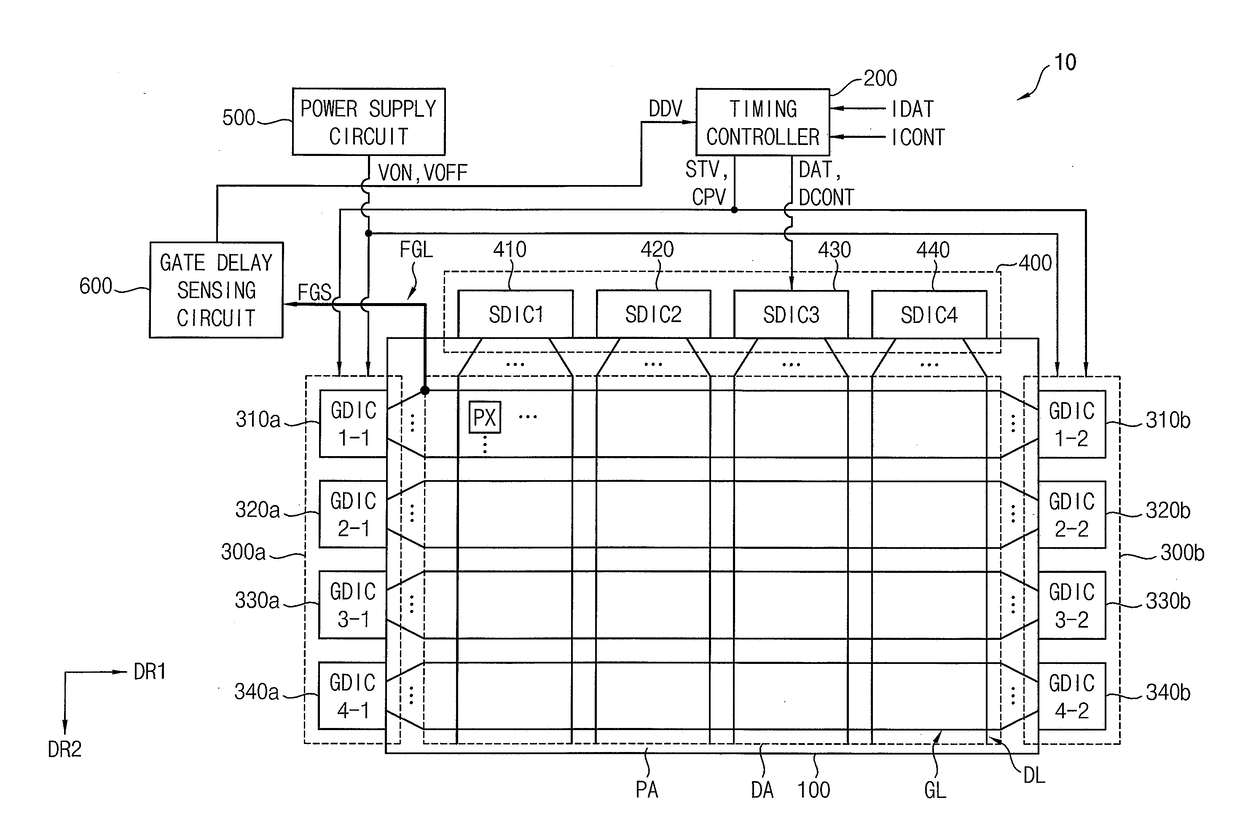

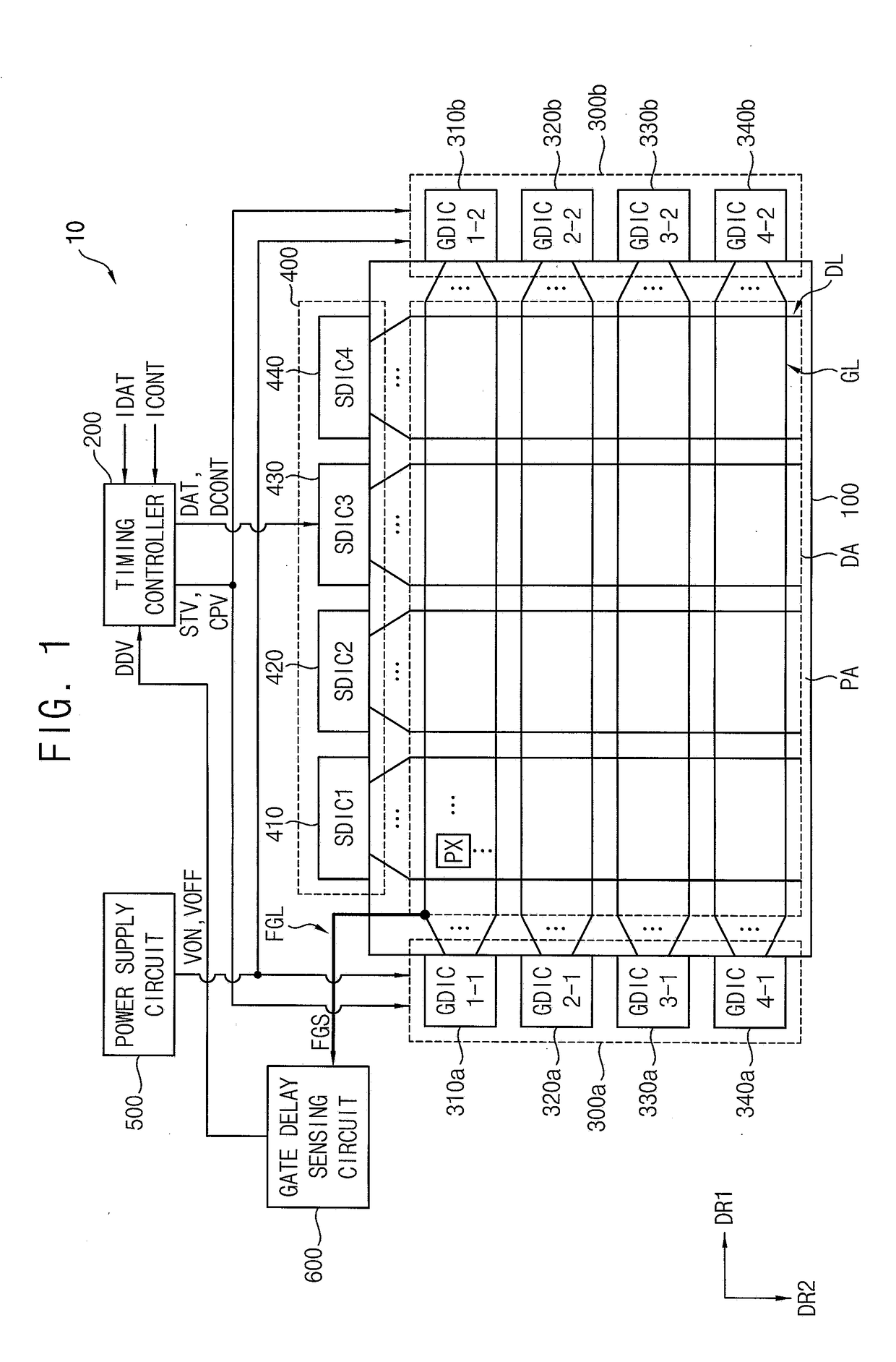

Display apparatus

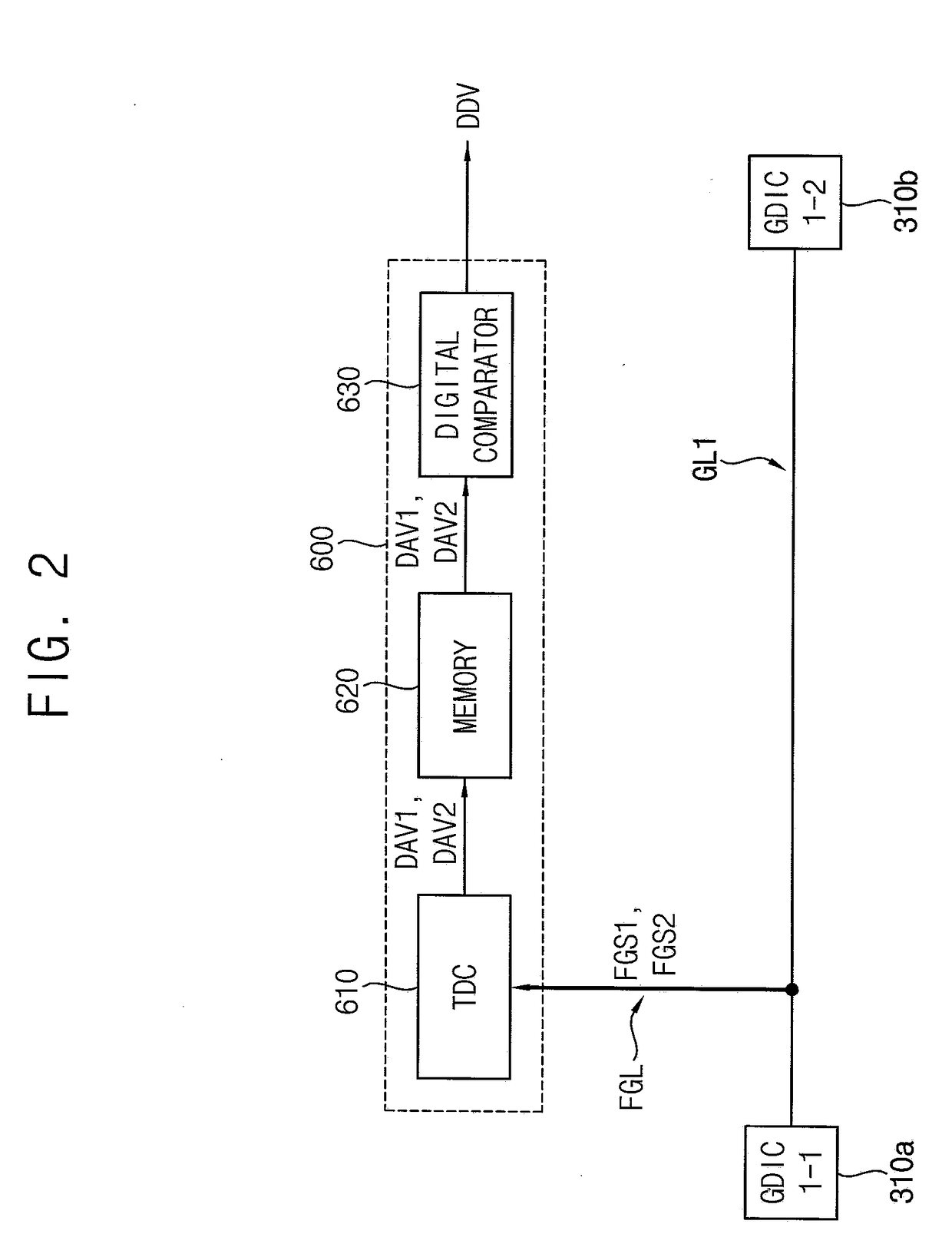

ActiveUS20180315369A1Efficient detectionRate of pixel be improvedStatic indicating devicesDigital down converterEngineering

A display apparatus includes a display panel including a plurality of first gate lines, a first gate driver connected to first ends of the plurality of first gate lines, a second gate driver connected to second ends of the plurality of first gate lines, a feedback line connected adjacent to the first end of one of the plurality of first gate lines, and a gate delay sensing circuit connected to the feedback line. The gate delay sensing circuit includes a time-to-digital converter and a digital comparator. The time-to-digital converter converts an activation time of a feedback gate signal into a digital activation value. The feedback gate signal is retrieved from the feedback line. The digital comparator generates a digital delay value based on the digital activation value. The digital delay value indicates resistive-capacitive (“RC”) delay of the one of the plurality of first gate lines connected to the feedback line.

Owner:SAMSUNG DISPLAY CO LTD

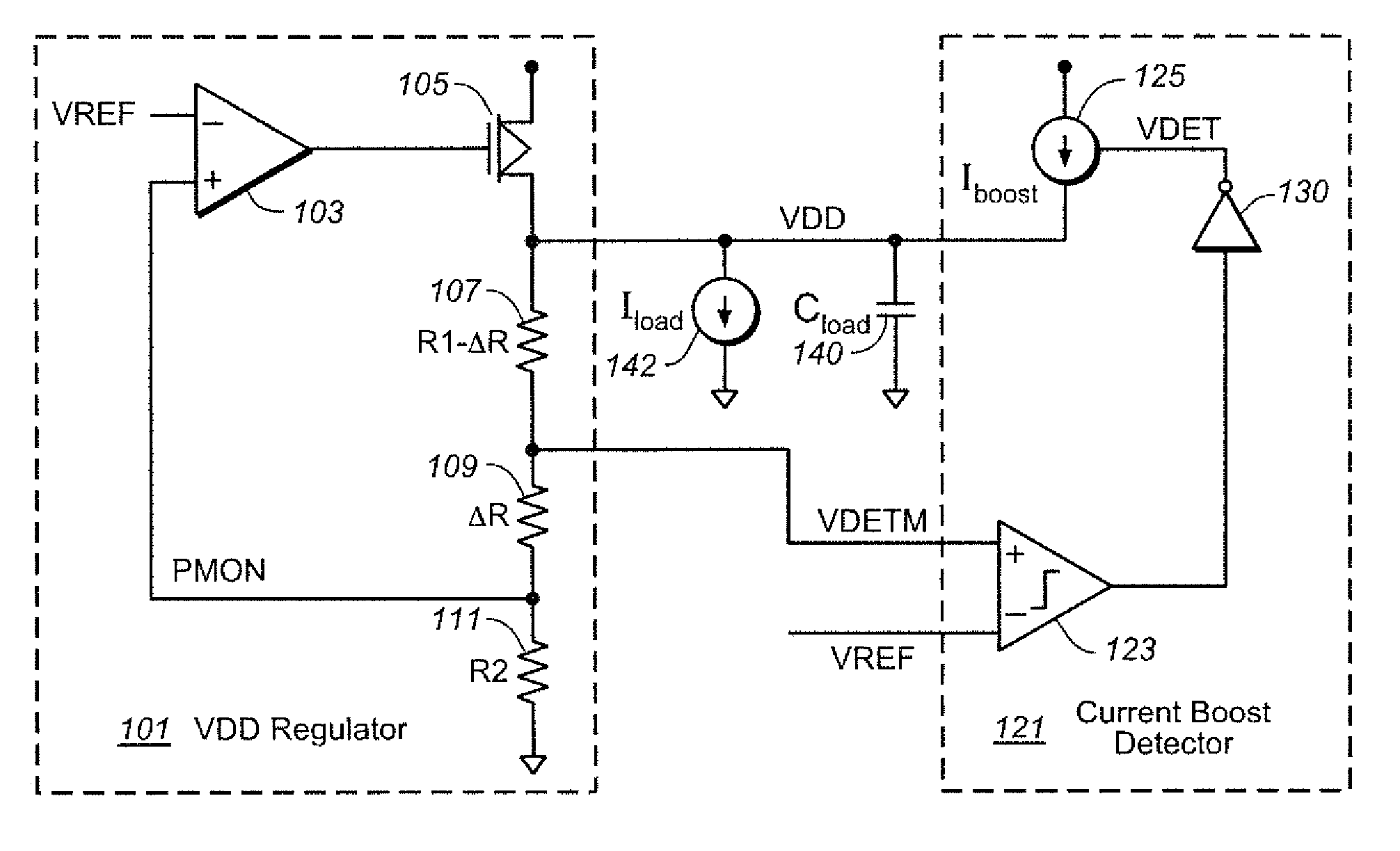

LDO/HDO Architecture Using Supplementary Current Source to Improve Effective System Bandwidth

An LDO / HDO circuit adds a supplementary current source to supply the output node. The current boosting section includes a digital comparator with a first input connected to the LDO's feedback loop and a second input connected to a reference level. The comparator then generates a digital output used to control the supplementary current source. This approach also can be used in a far-side implementation, where the local supply level for the load is boosted by the current source based a comparison of this local level and the output of the LDO. Miller capacitive compensation is also considered. Current in shunted to ground from a node in the Miller loop, where the level is controlled by the output of a digital comparator base on a comparison of the circuit's output voltage and a reference level.

Owner:SANDISK TECH LLC

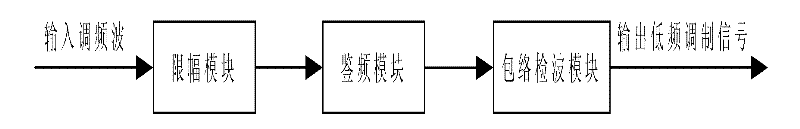

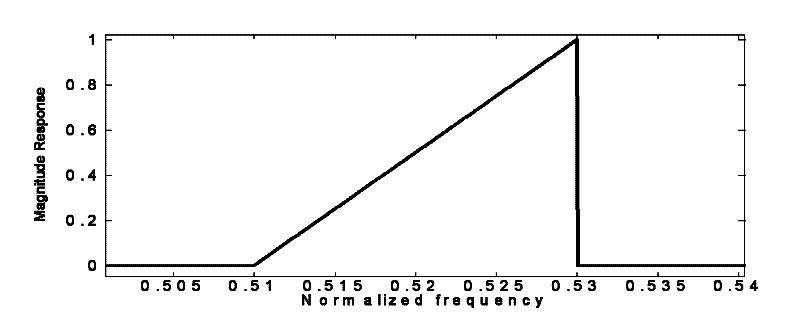

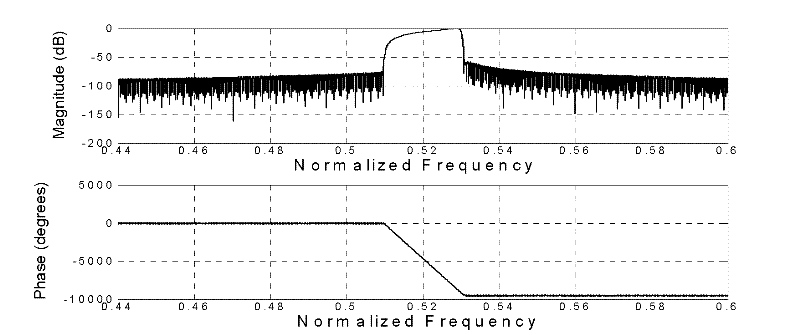

Digital ultrasonic transcranial Doppler digital demodulation signal processing method and device

InactiveCN102176121ASolve the shortcomings of single frequency scanning distance, low precision, etc.Achieve full depth scanBlood flow measurement devicesSimulator controlFrequency spectrumSonification

The invention discloses a digital ultrasonic transcranial Doppler digital demodulation signal processing method and device. The method comprises the following steps: performing the A / D (analog / digital) sampling on an input frequency-modulated wave which is a non-demodulated ultrasonic echo signal, and then performing the amplitude limiting through a digital comparator; detecting a modulation signal reflected on the frequency conversion in a frequency-modulated save subjected to the amplitude limiting; and taking the absolute value of the modulation signal, responding the changes of the amplitude of the modulation signal to an envelope line, and acquiring a low-frequency modulation signal through a down-sampling low-pass filter. The device comprises an AD converter, at least two large-capacity high-speed caches FIFO (first in first out), a DSP digital signal processor), and an FPGA (field programmable gate array). According to the invention, the wide frequency band scanning and the full-depth scanning can be realized, the timeliness and signal-to-noise ratio (SNR) of the system are improved, a blood flow dynamic parameter is accurately extracted, the SNR of a detecting signal is improved, and the quality of a frequency spectrum image is improved.

Owner:HOHAI UNIV

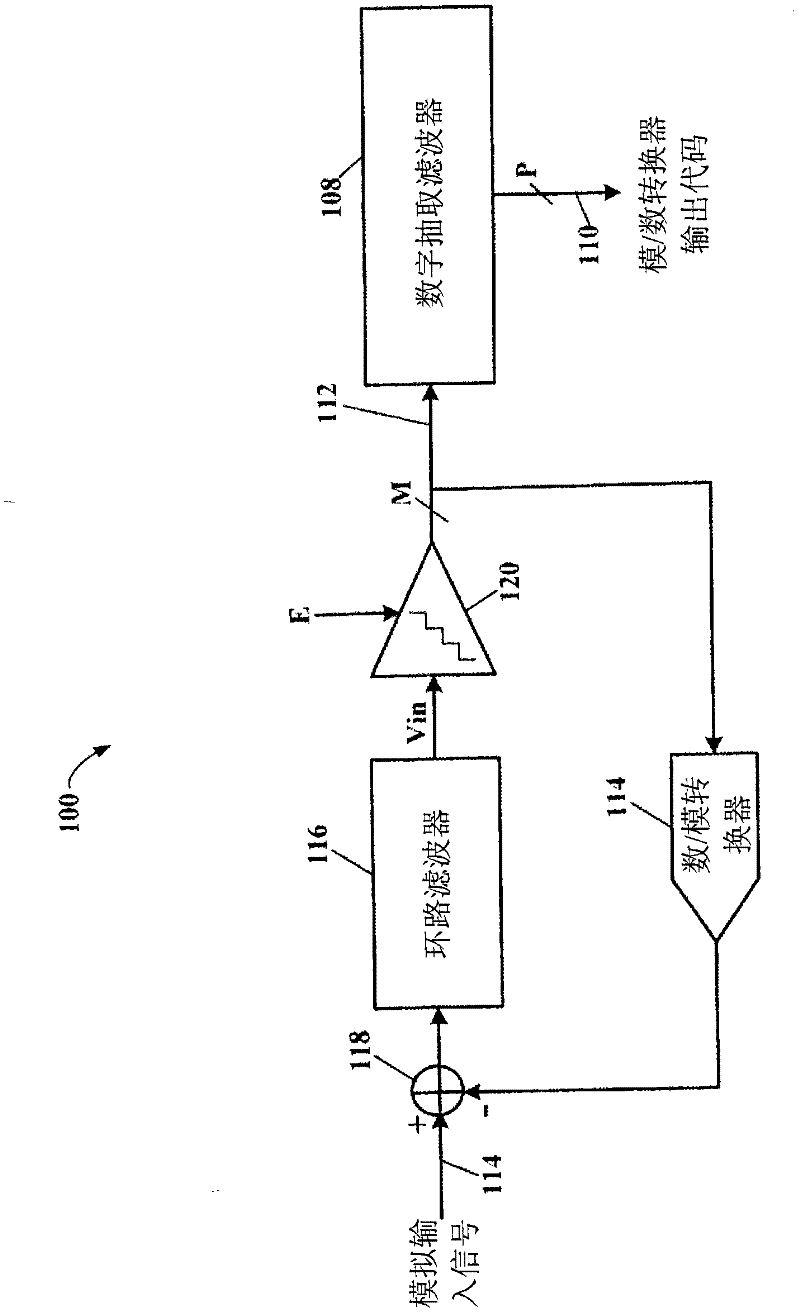

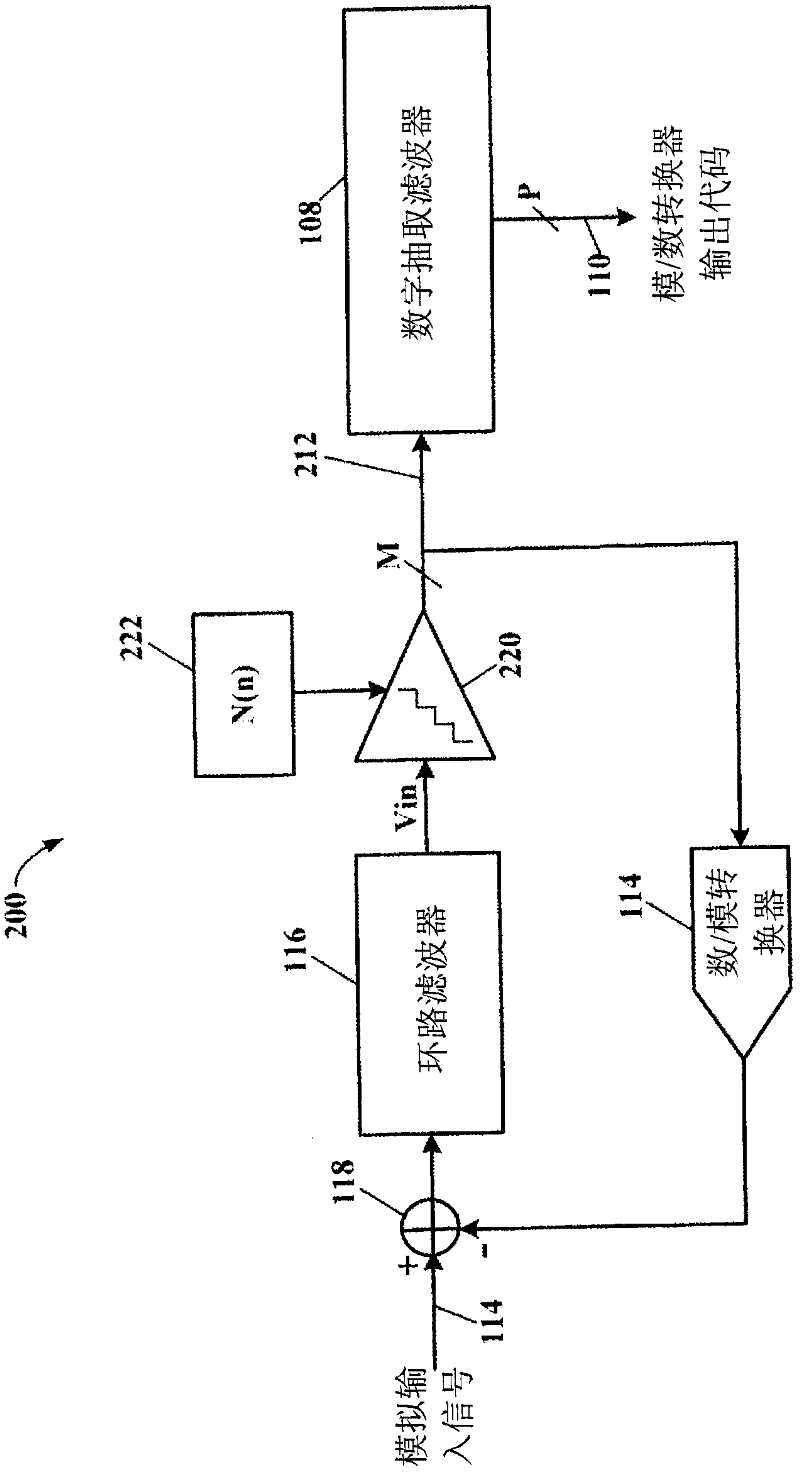

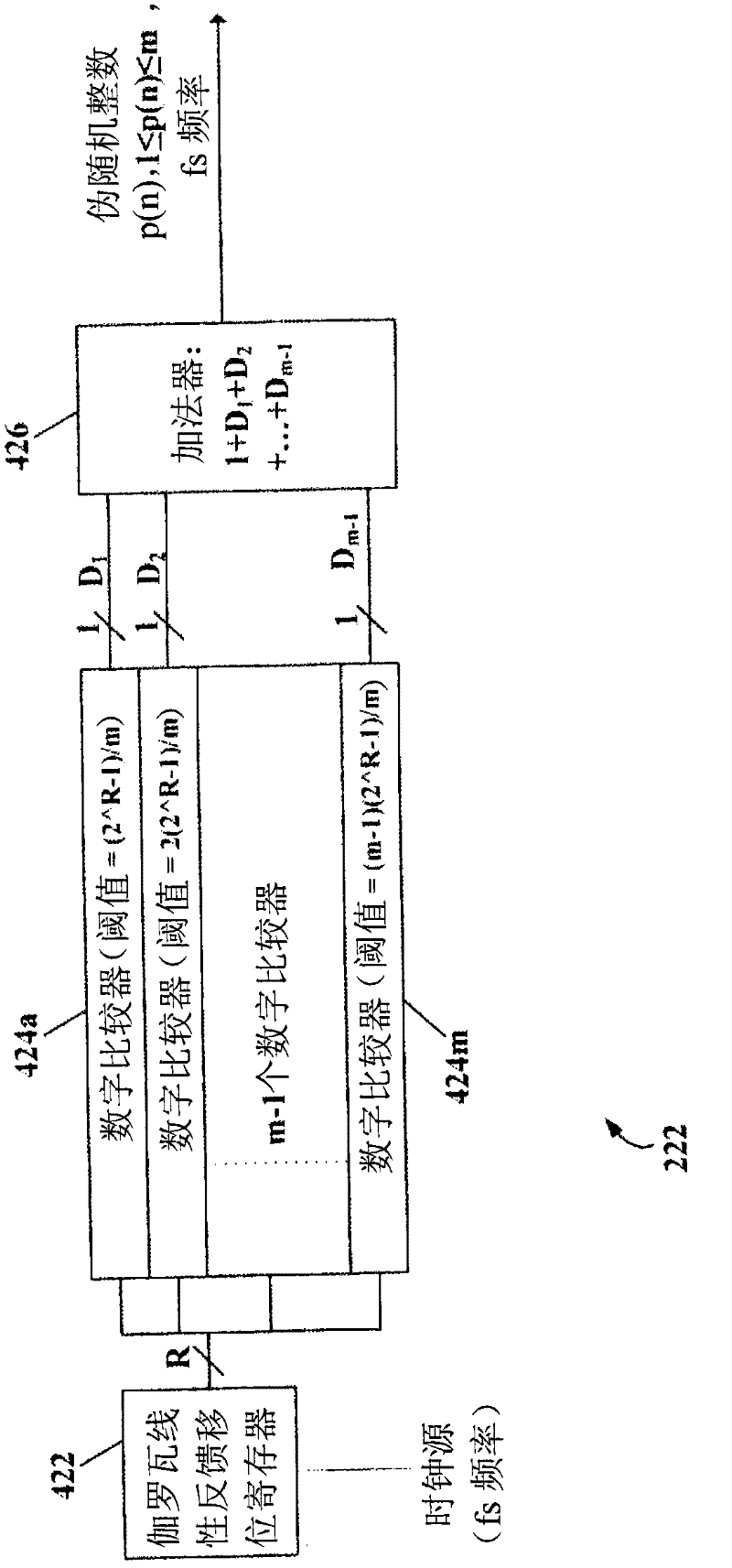

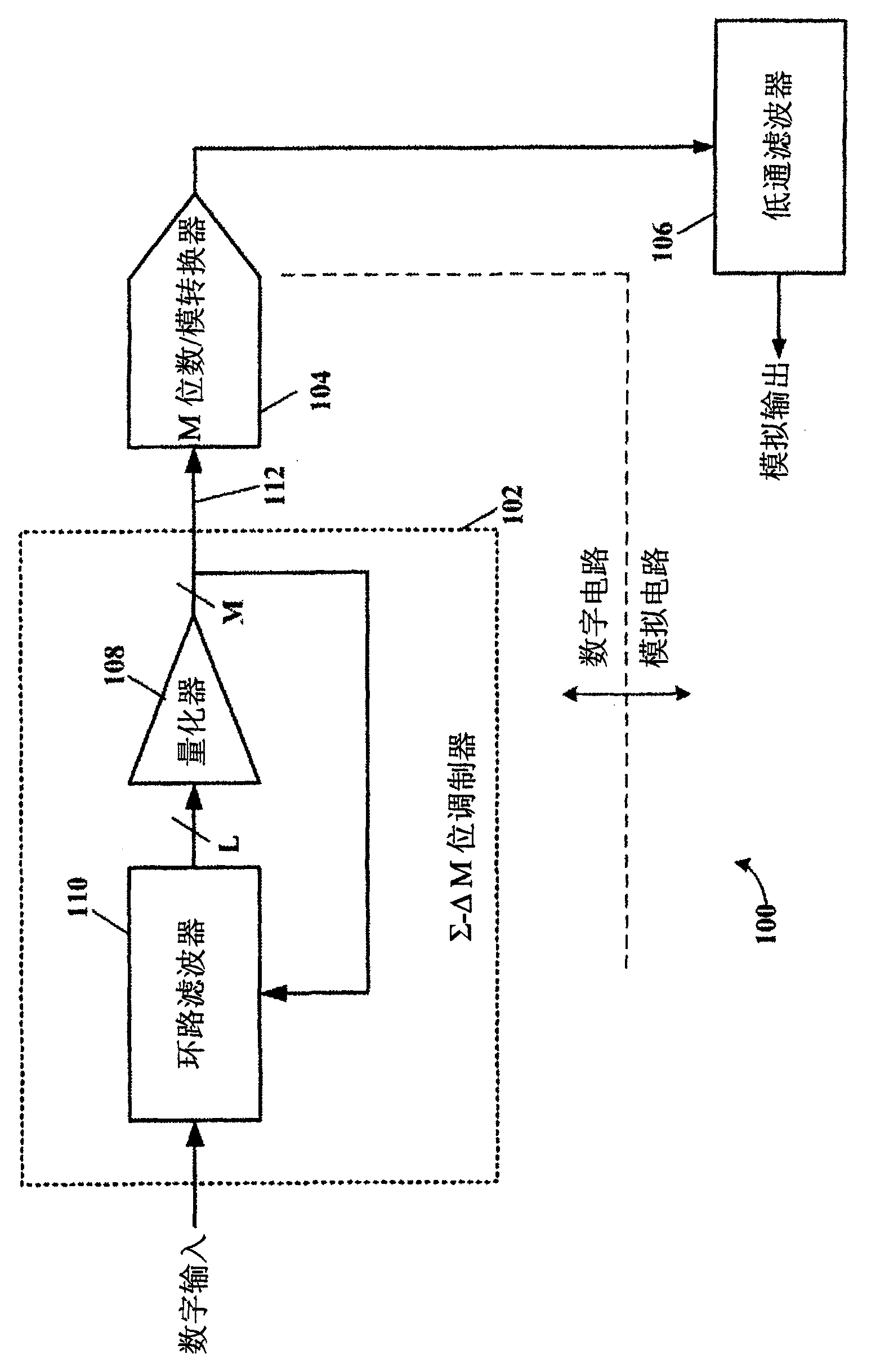

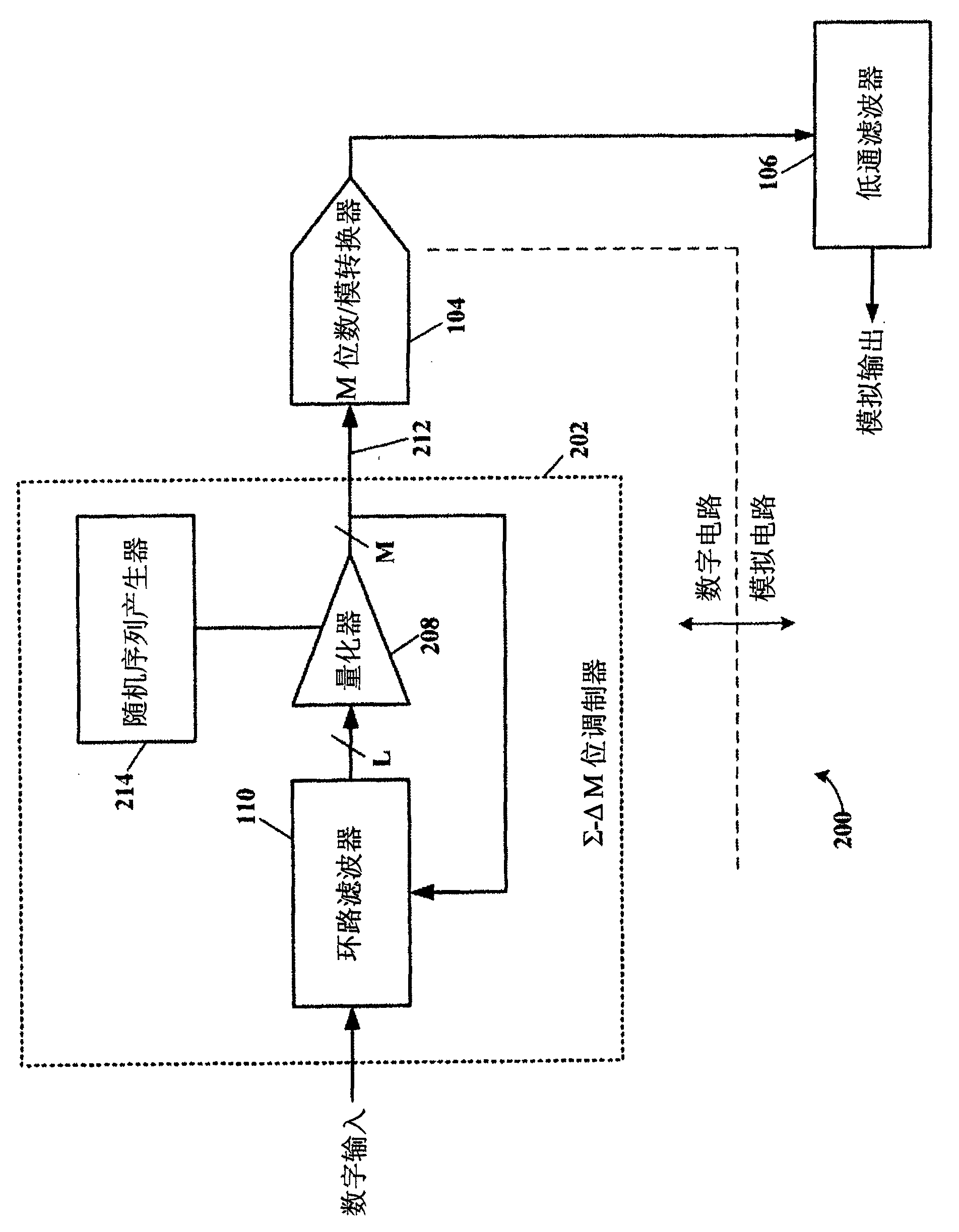

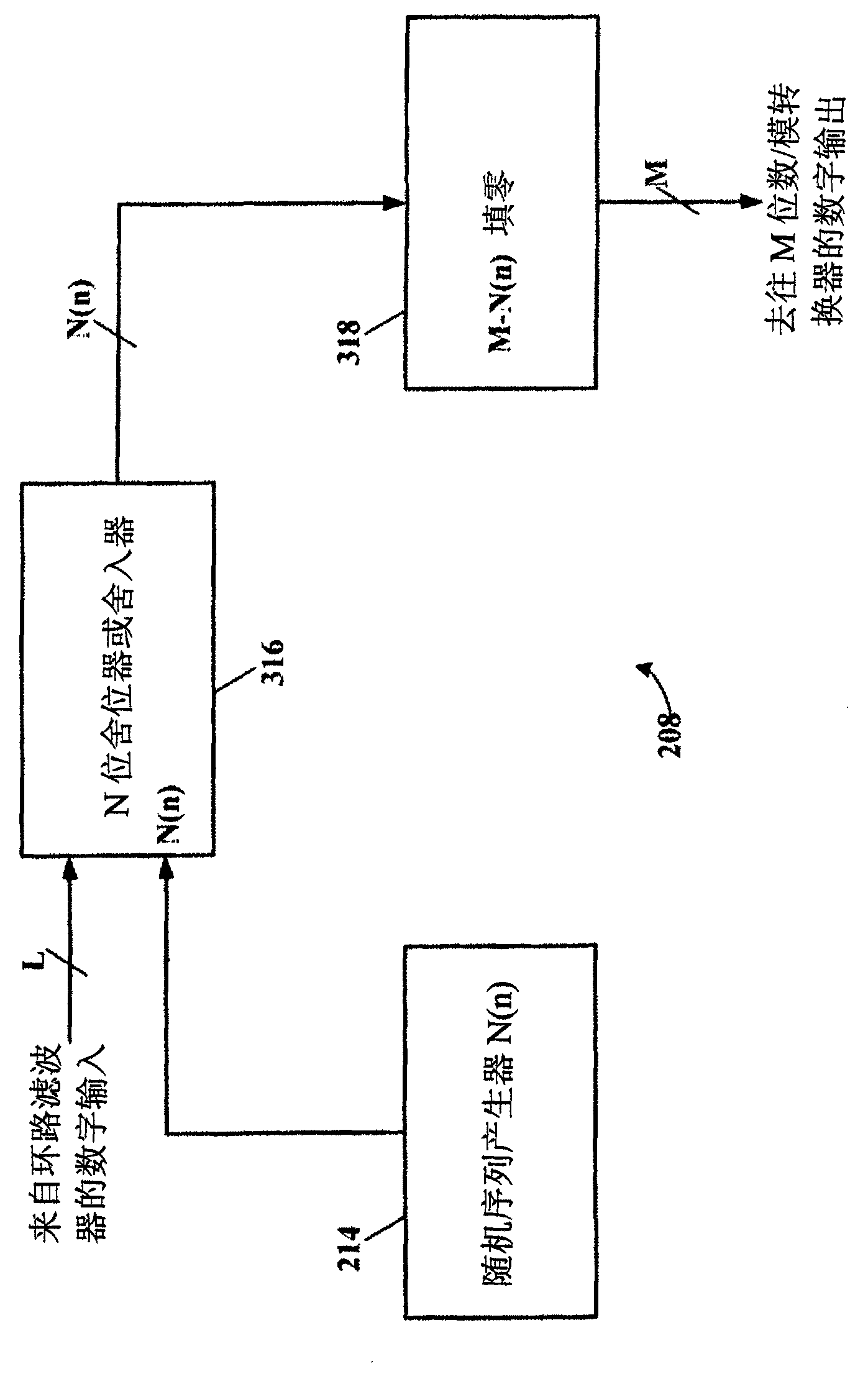

Method and apparatus for dithering in multi-bit sigma-delta analog-to-digital converters

ActiveCN102165697AGuaranteed stabilityReduce Harmonic DistortionAnalogue conversionImage resolutionVariable resolution

A multi-bit (M-bit, M> 1 ) or multi-level (nlev levels, nlev>2, encoded on M bits where M=Floor(log2(nlev))) sigma-delta analog-to-digital converter (ADC) with a variable resolution multi-bit quantizer having its resolution (number of distinct output levels) and associated quantization thresholds changed for each voltage sample with a random or pseudo-random sequence N(n) to provide automatic dynamic dithering for removing undesired idle tones in the digital output of the sigma-delta ADC. The random integer numbers N(n) between 2 and nlev may be provided by a random or pseudo-random sequence generator, e.g., Galois linear feedback shift register in combination with digital comparators and an adder.

Owner:MICROCHIP TECH INC

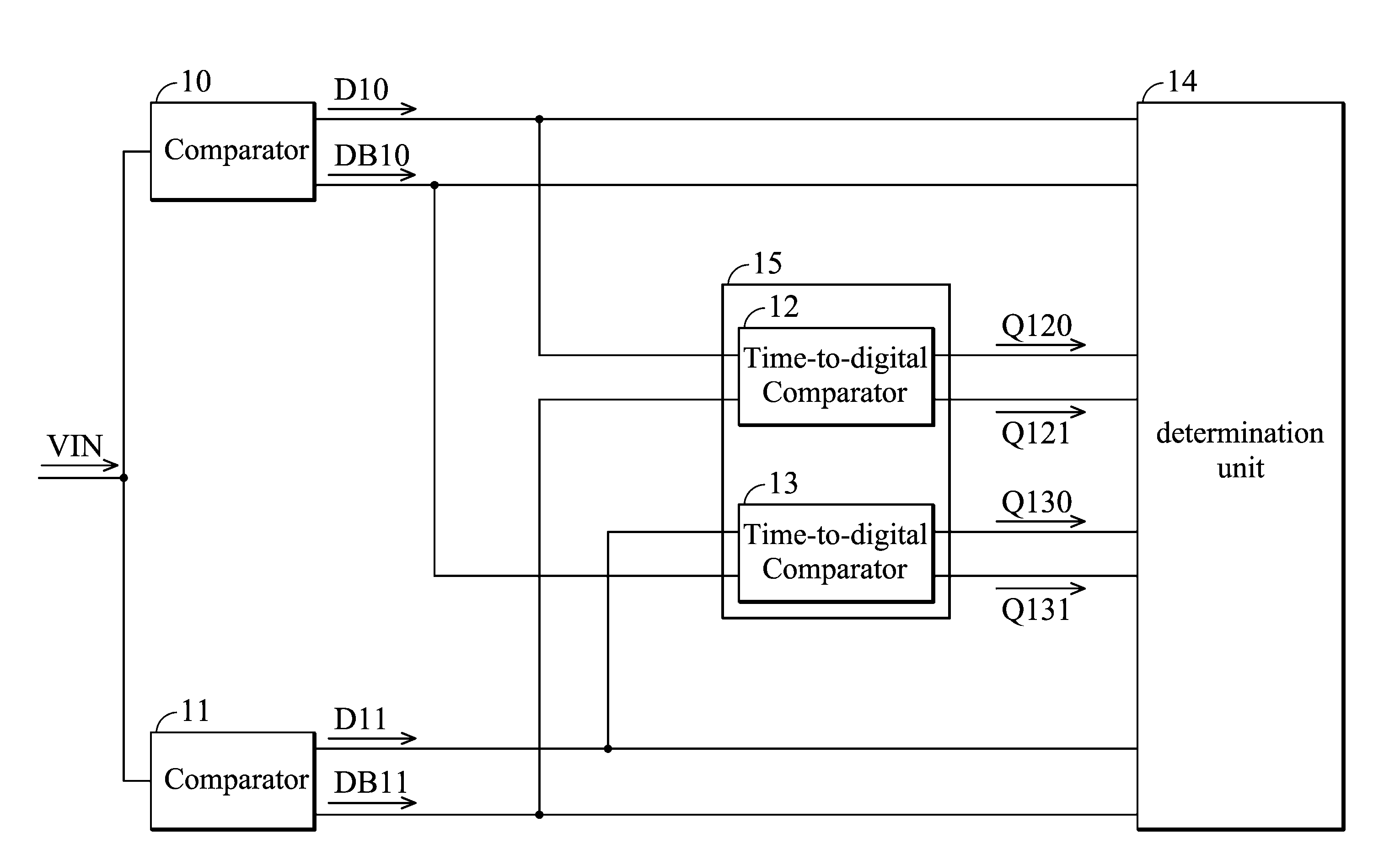

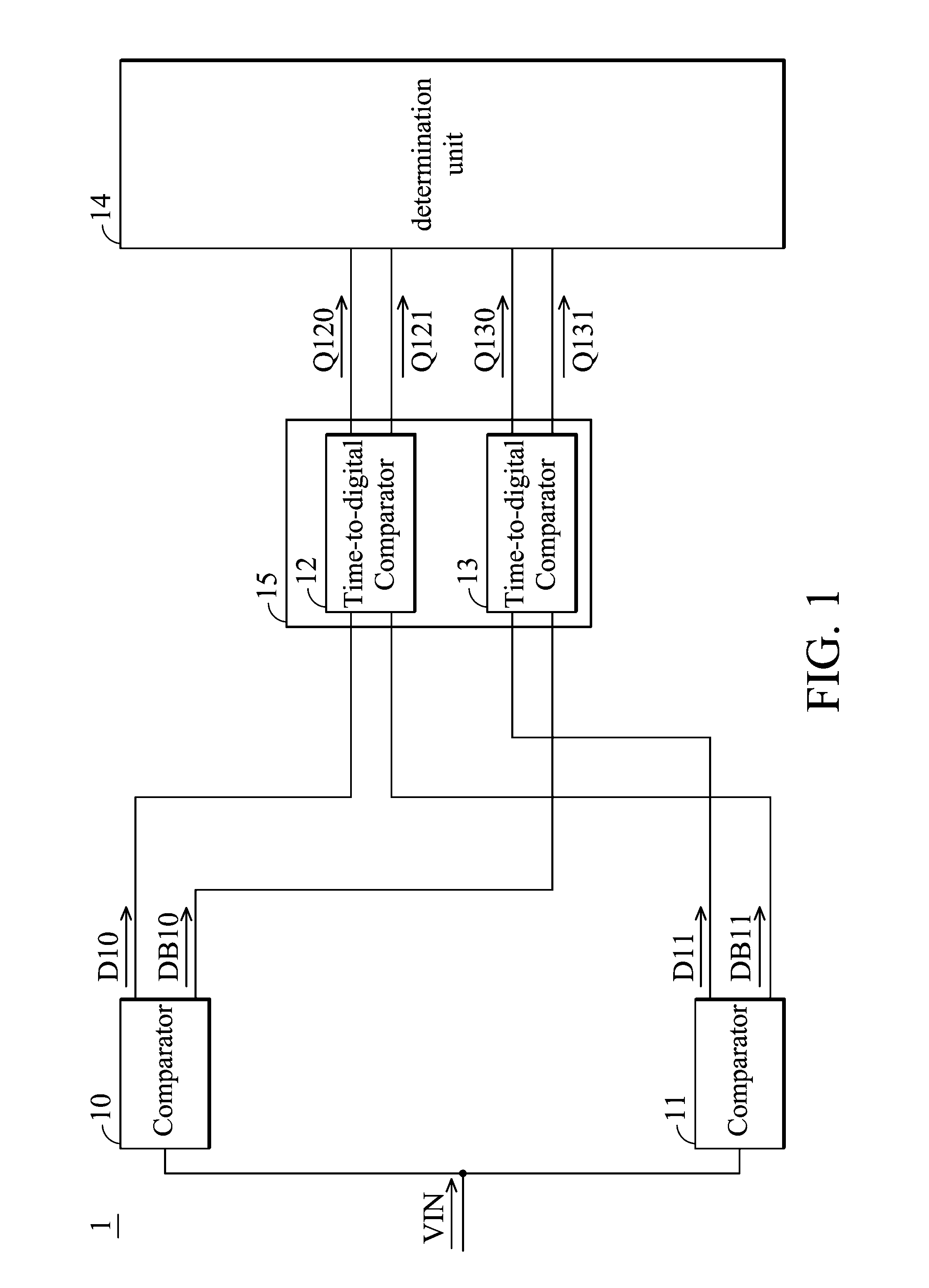

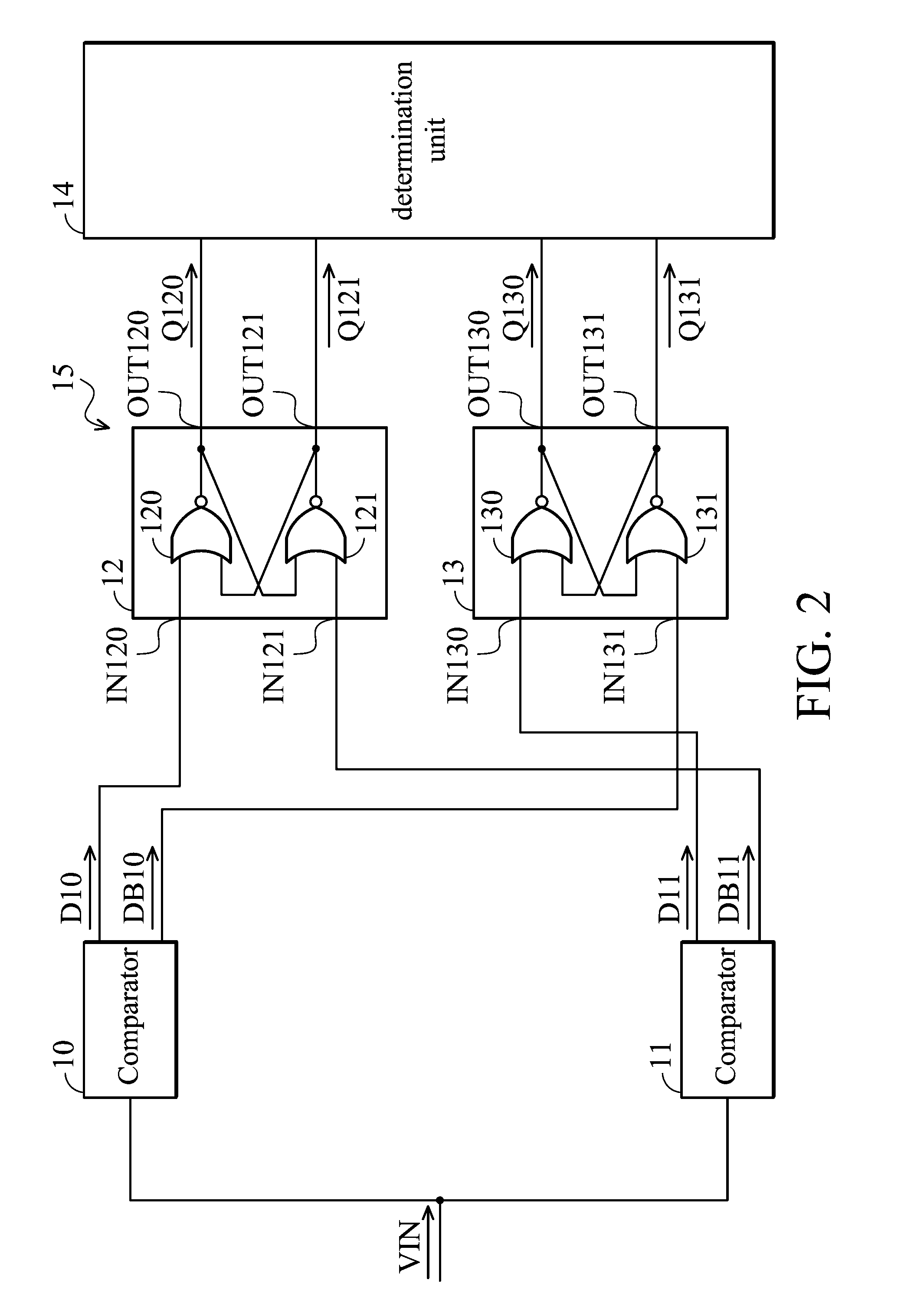

Comparison circuits

ActiveUS8514121B1Minimal areaElectric signal transmission systemsAnalogue-digital convertersEngineeringDigital comparator

A comparison circuit is provided and includes first and second comparators and a first time-to-digital comparator. The first comparator with a first offset voltage receives an input signal and generates a first comparison signal and a first inverse comparison signal. The second comparator receives the input signal and generates a second comparison signal and a second inverse comparison signal. The first offset voltage is larger than the second offset voltage. The first time-to-digital comparator receives the first comparison signal and the second inverse comparison signal and generates first and second determination signals according to the first comparison signal and the second inverse comparison signal. The first and second determination signals indicate whether a voltage of the input signal is larger than a first middle voltage. The first middle voltage is equal to a half of the sum of the first offset voltage and the second offset voltage.

Owner:MEDIATEK INC

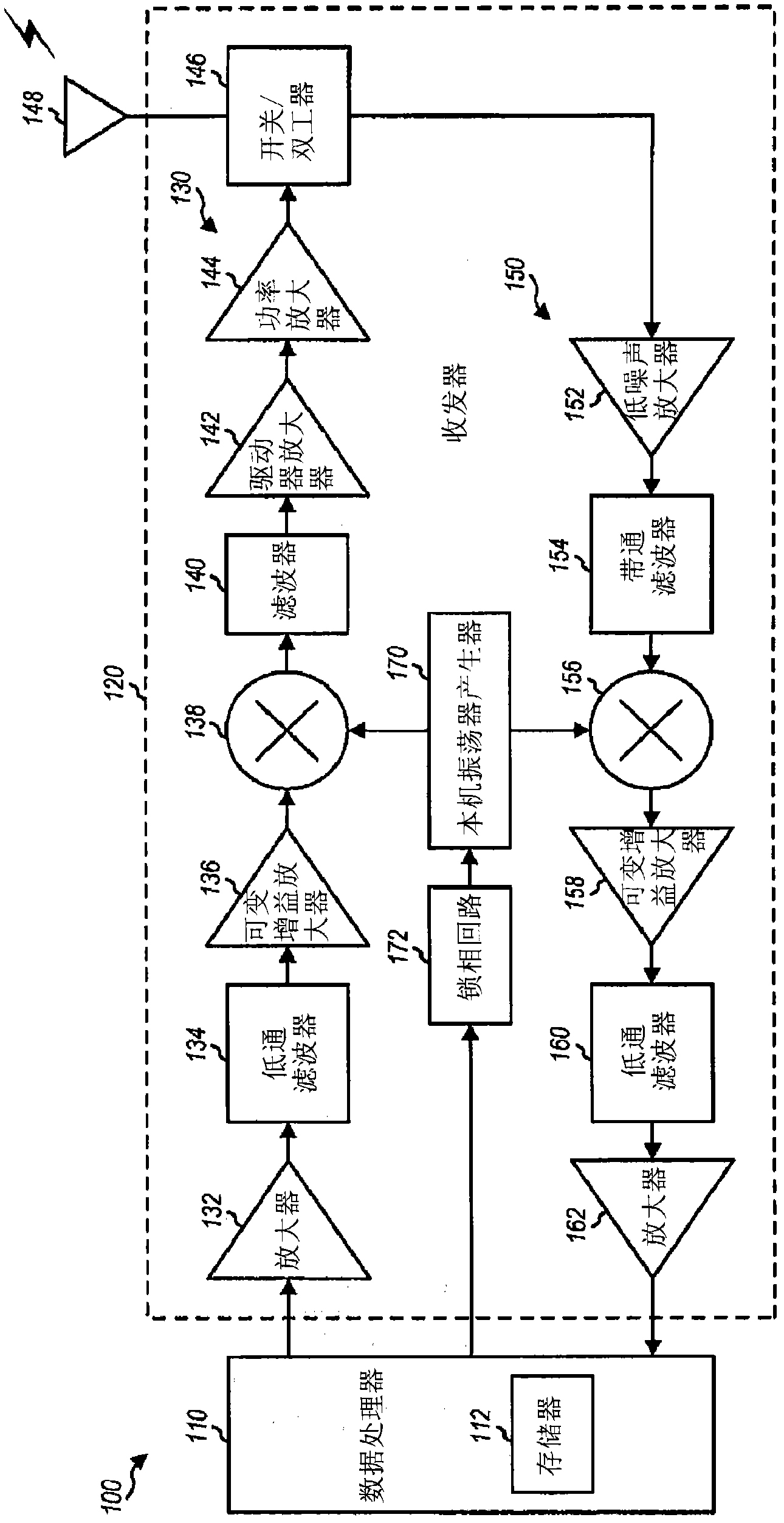

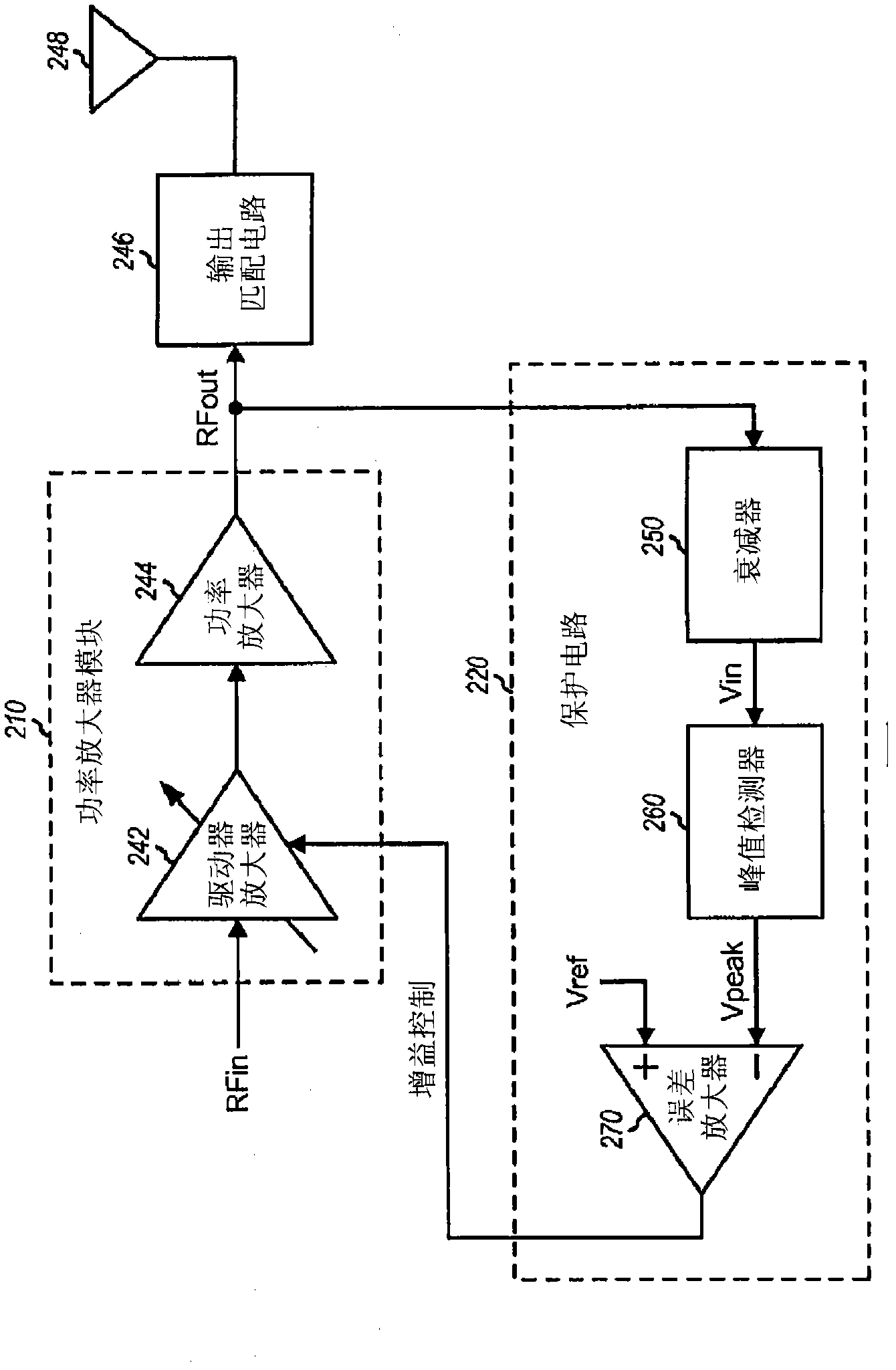

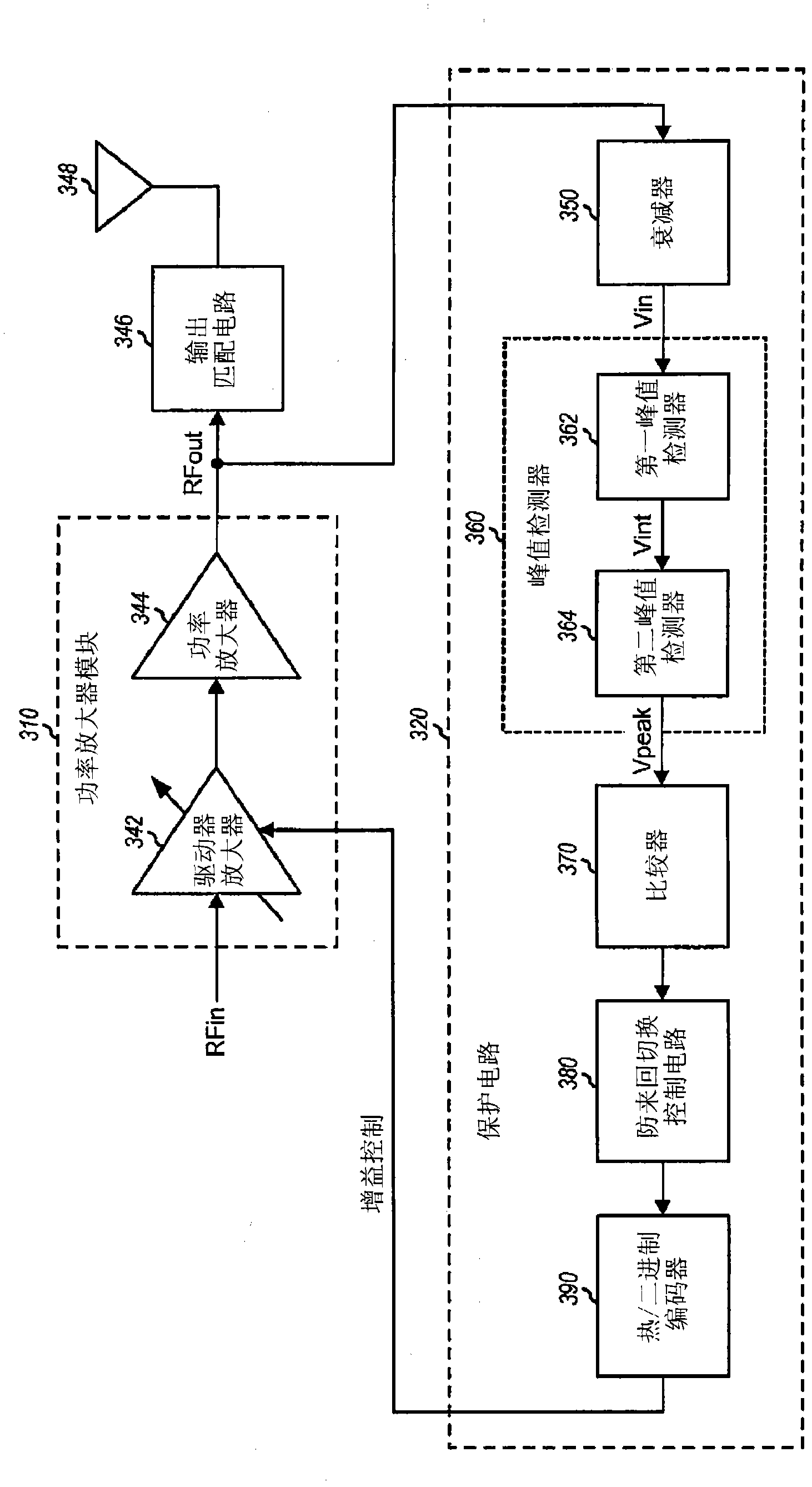

Protection circuit for power amplifier

Techniques for protecting a power amplifier (PA) are described. In an exemplary design, an apparatus includes a PA module (310) to amplify an input RF signal and provide an output RF signal and a protection circuit (320) to control a transmitter gain to protect the PA module against high peak voltage. In an exemplary design, the protection circuit (329) includes a set of comparators (370) to quantize an analog input signal and provide digital comparator output signals used to adjust the transmitter gain. In another exemplary design, the protection circuit reduces and increases the transmitter gain with hysteresis. In yet another exemplary design, the protection circuit has faster response to rising amplitude than falling amplitude of the output RF signal. The hysteresis and / or the different rise and fall responses may allow the protection circuit to avoid toggling the transmitter gain under severe load mismatch and to handle time-varying envelope due to amplitude modulation.

Owner:QUALCOMM INC

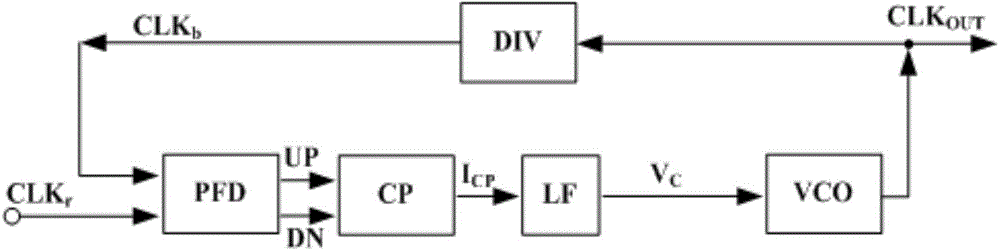

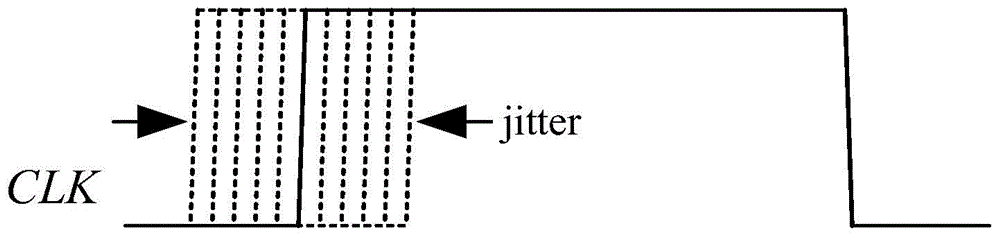

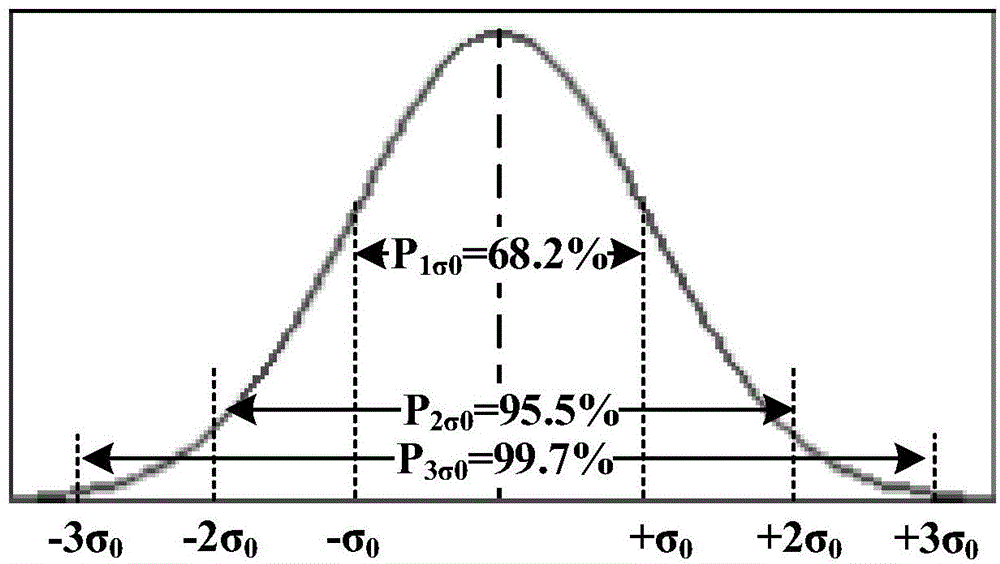

Phase-locked loop with correction and correction method thereof

InactiveCN104682956ARealize detectionSimple structurePulse automatic controlDiscriminatorLow-pass filter

The invention provides a phase-locked loop with correction and a correction method thereof, which are used for reducing jitter of an output clock of the phase-locked loop. The phase-locked loop with correction is divided into a main loop and a correction loop, wherein the main loop comprises a frequency discriminator / phase discriminator, a charge pump, a low-pass filter, a voltage-controlled oscillator and a frequency divider; the correction loop comprises a lock detector, a time digital converter, two counters, two digital comparators and a digital to analog converter, and the specific connection mode is that a feedback clock and a reference clock are taken as input of the time lock detector and input of the time digital converter; the output of the time digital converter is connected to the input of the first counter and the input of the second counter; the output of the first counter and the output of the second counter are respectively connected to the input of the first comparator and the input of the second comparator, and the outputs of the comparators and the output of the lock detector are connected to the input of the digital to analog converter; the output of the digital to analog converter is connected to the charge pump for controlling the output current of the charge pump.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

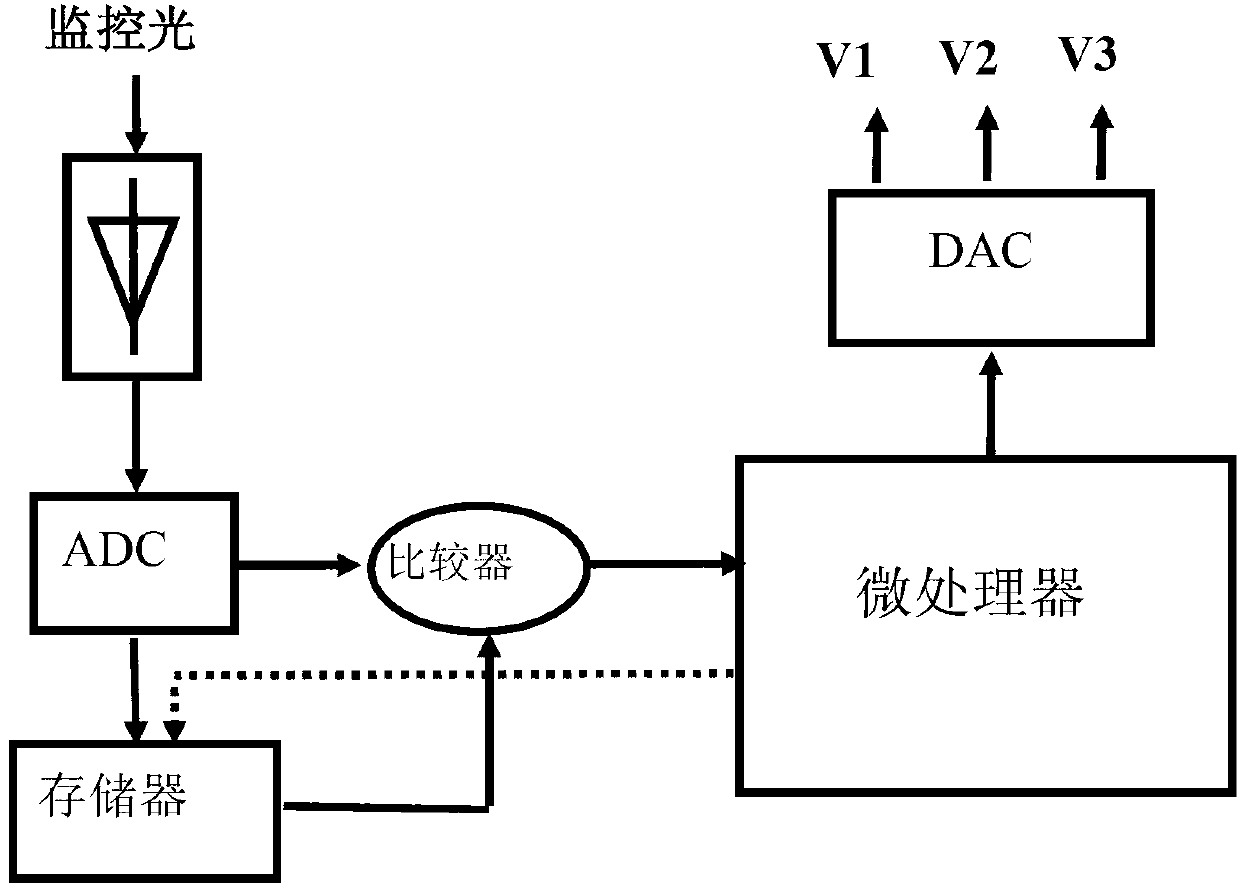

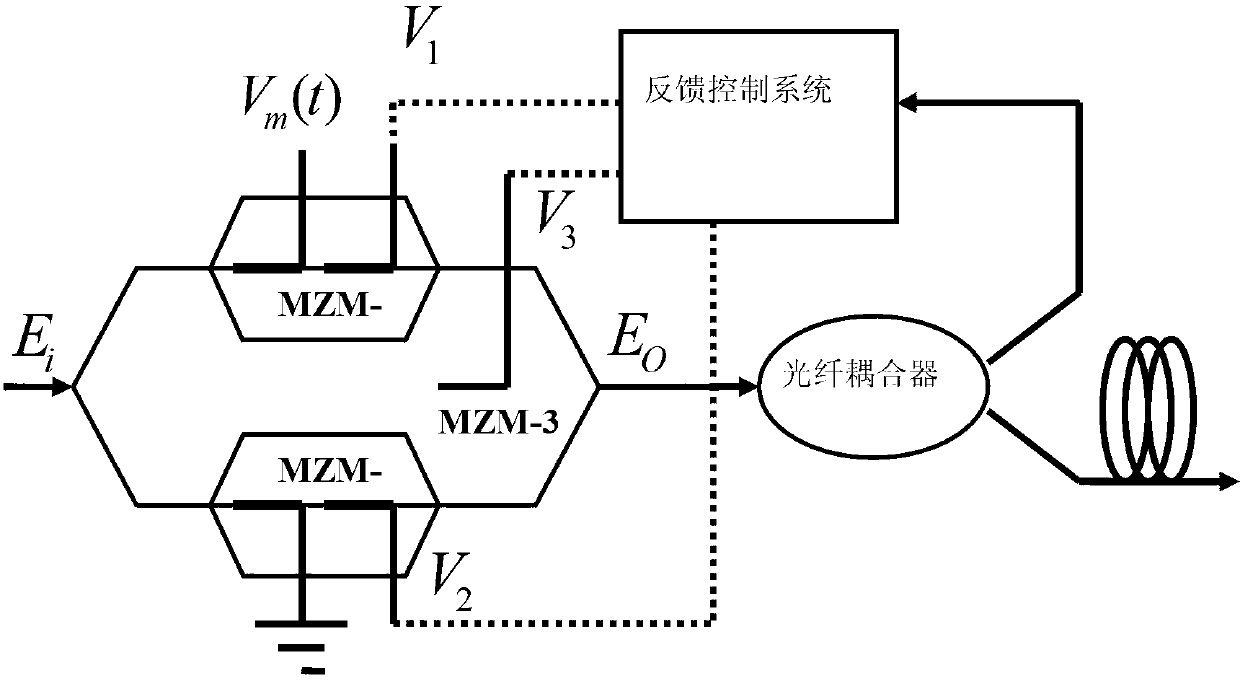

Feedback control system and method for controlling output light intensity of dual-parallel MZM modulator

InactiveCN103346842AOutput optical power real-time monitoringConstant output optical powerElectromagnetic transmittersControl systemOptical power

The invention discloses a feedback control system and method for controlling output light intensity of a dual-parallel MZM modulator. The input end of an optical fiber coupler of the feedback control system is connected with an output end of the dual-parallel MZM modulator, the input end of an optical receiving module of the feedback control system is connected with a secondary output end of the optical fiber coupler, the output end of the optical receiving module is connected with the input end of an A / D converter, two output ends of the A / D converter are connected with one input end of a digital comparator and the input end of a memory respectively, the output end of the memory is connected with the other input end of the digital comparator, the output end of the digital comparator is connected with the input end of a microprocessor, and the output end of the microprocessor is connected with the power source end of the dual-parallel MZM modulator through a D / A converter. The feedback control system and method for controlling the output light intensity of the dual-parallel MZM modulator can carry out real-time monitoring on output optical power of the dual-parallel MZM modulator, signals are fed back to control the dual-parallel MZM modulator through the feedback control system, the output power can be constant, and system performance can be optimal.

Owner:GUILIN UNIV OF ELECTRONIC TECH

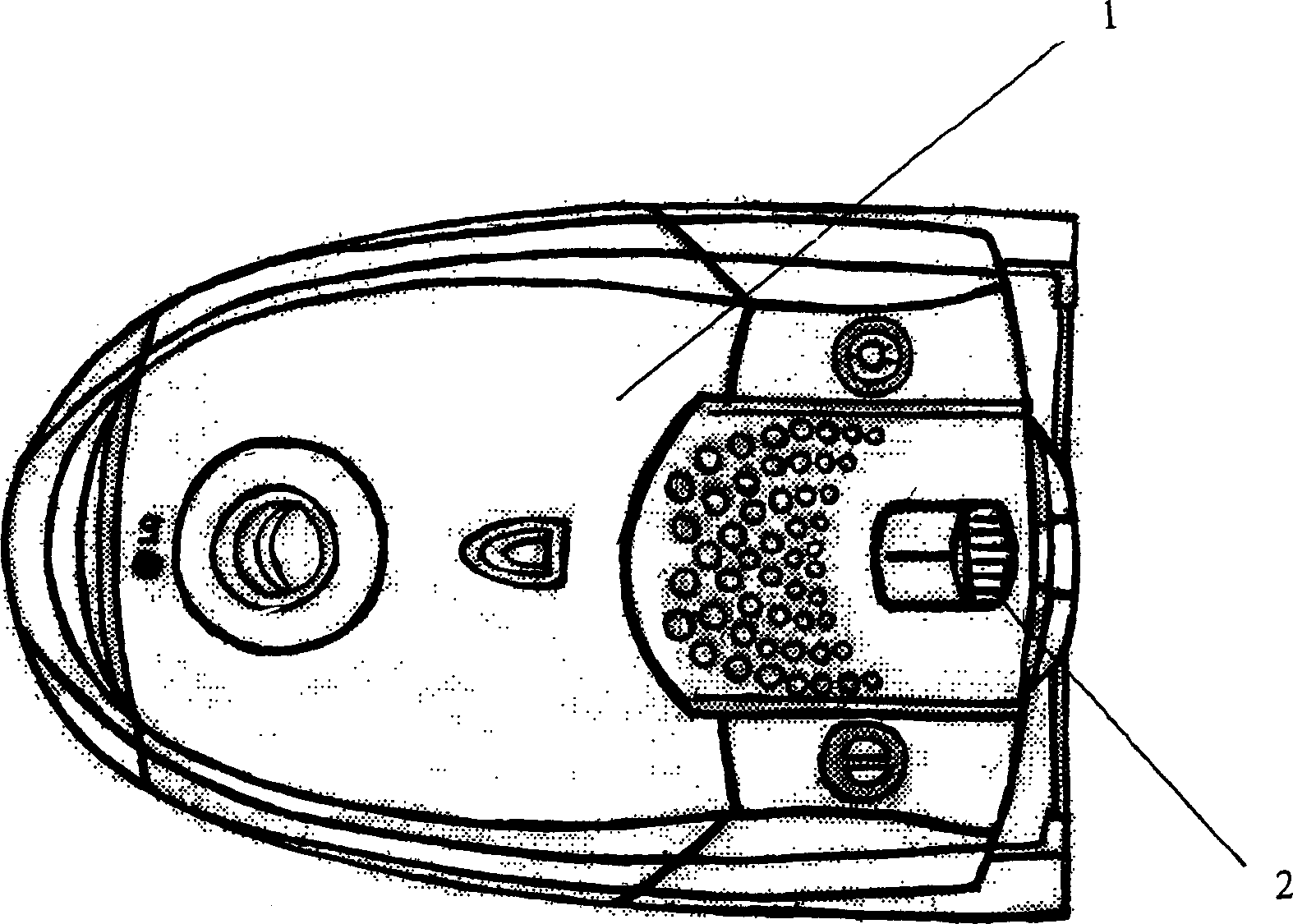

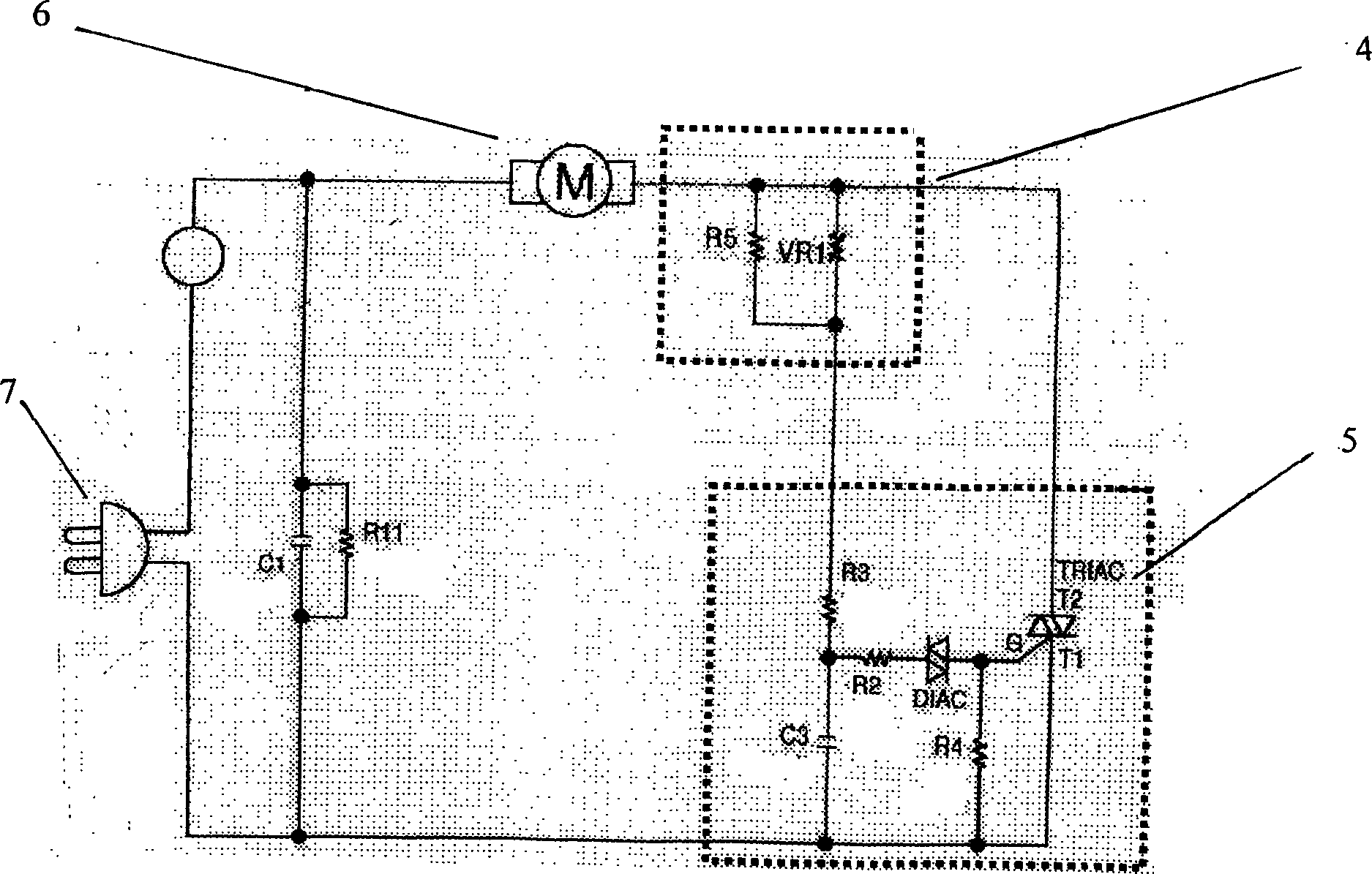

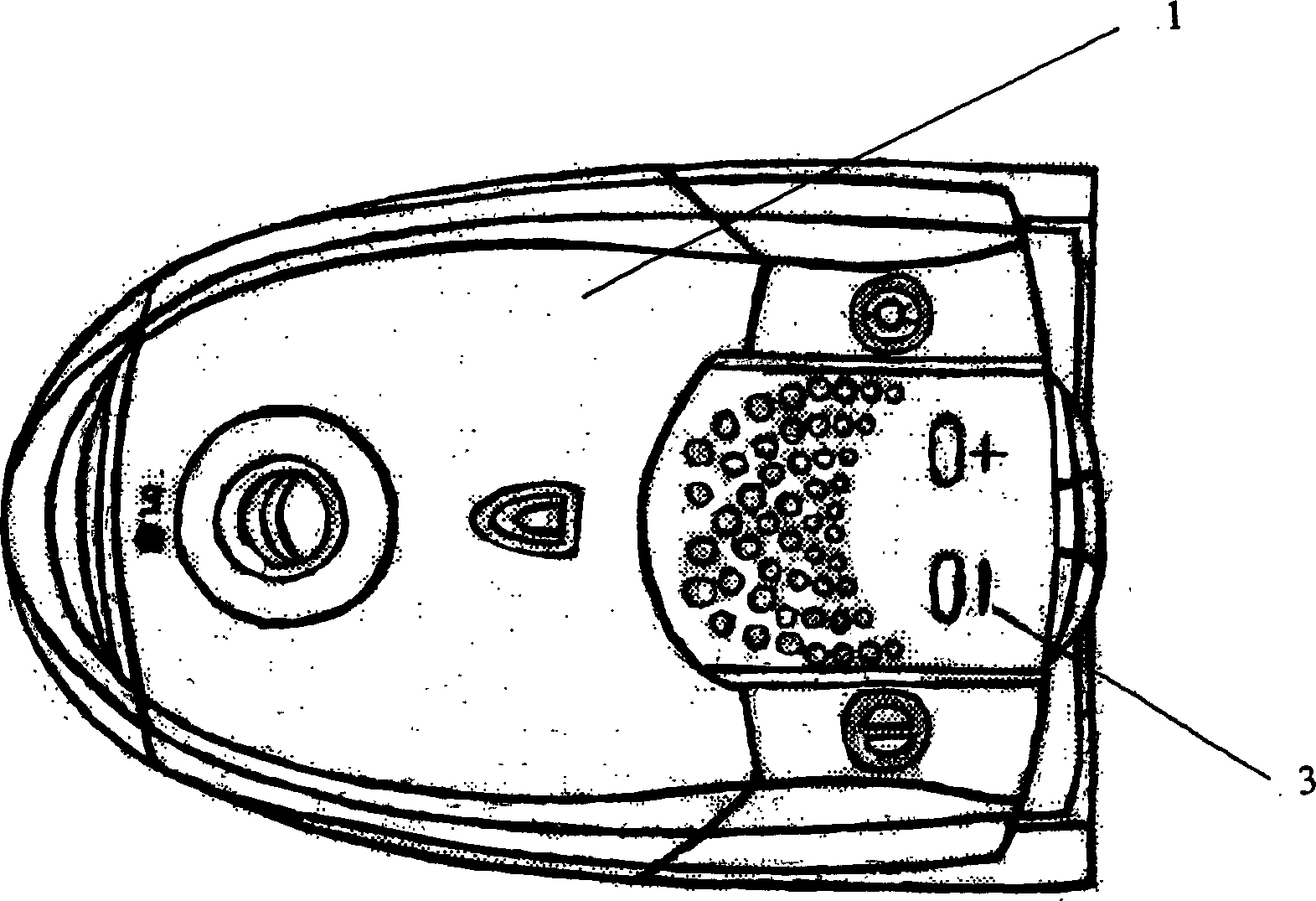

Touching type induction regulator for vacuum cleaner

InactiveCN1860983AHigh degree of generalizationMeet comfortAC motor controlElectric equipment installationDriver circuitEngineering

A touch induction type speed regulator of cleaner is composed of an operation knob arranged on the casing of cleaner and consisting of an acceleration piece and a deceleration piece and a speed regulating circuit connected to said two pieces for regulating the speed of motor and consisting of input buffer, phase lock ring, state and phase angle memory, digital comparator, driver and SCR.

Owner:LG ELECTRONICS (TIANJIN) APPLIANCES CO LTD

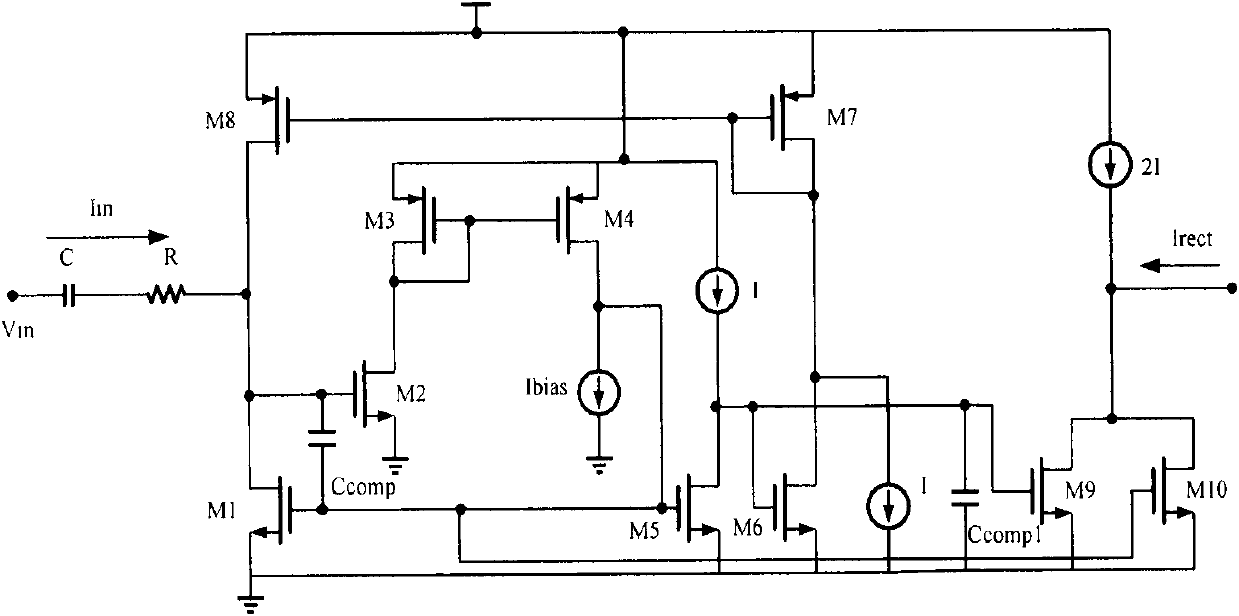

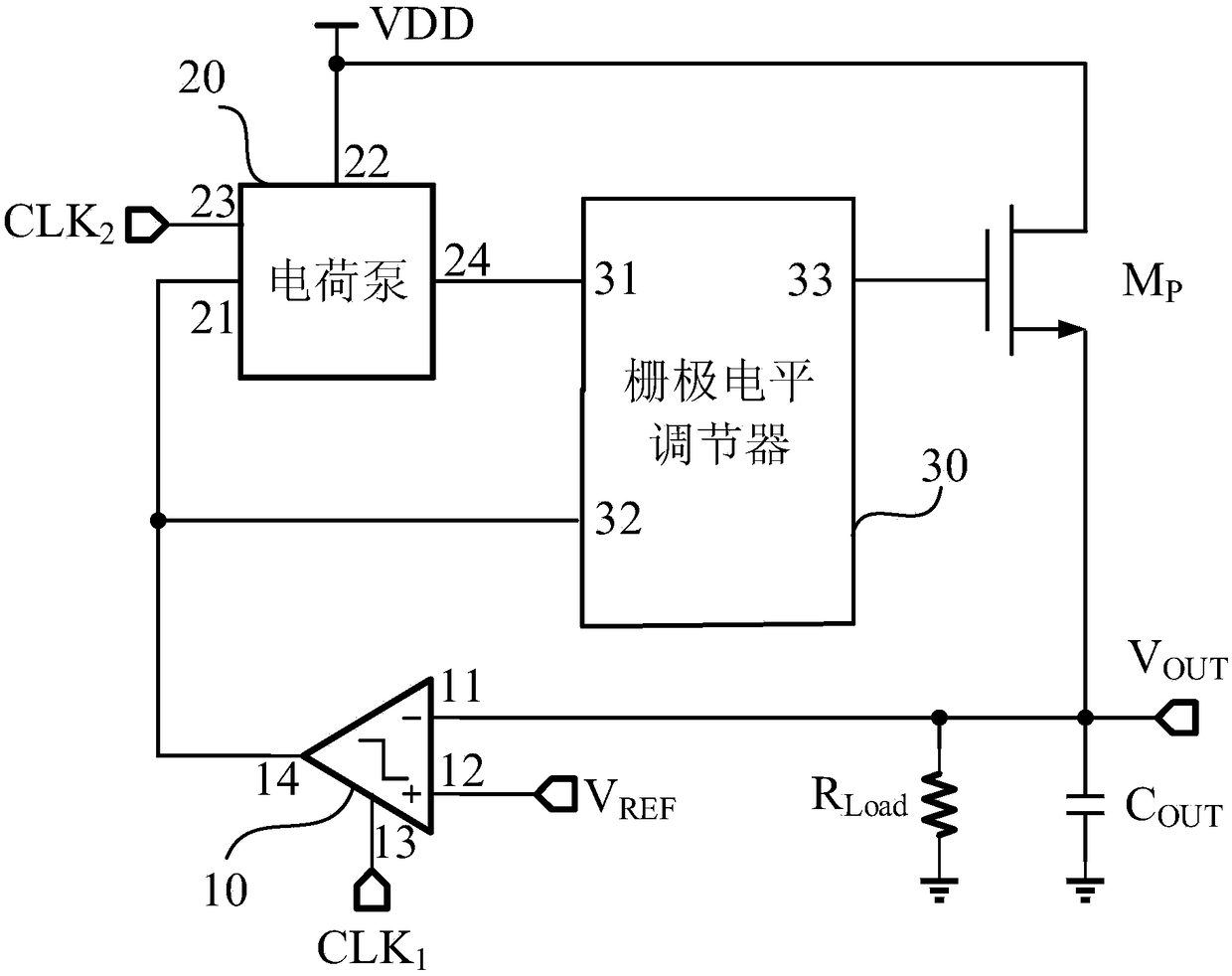

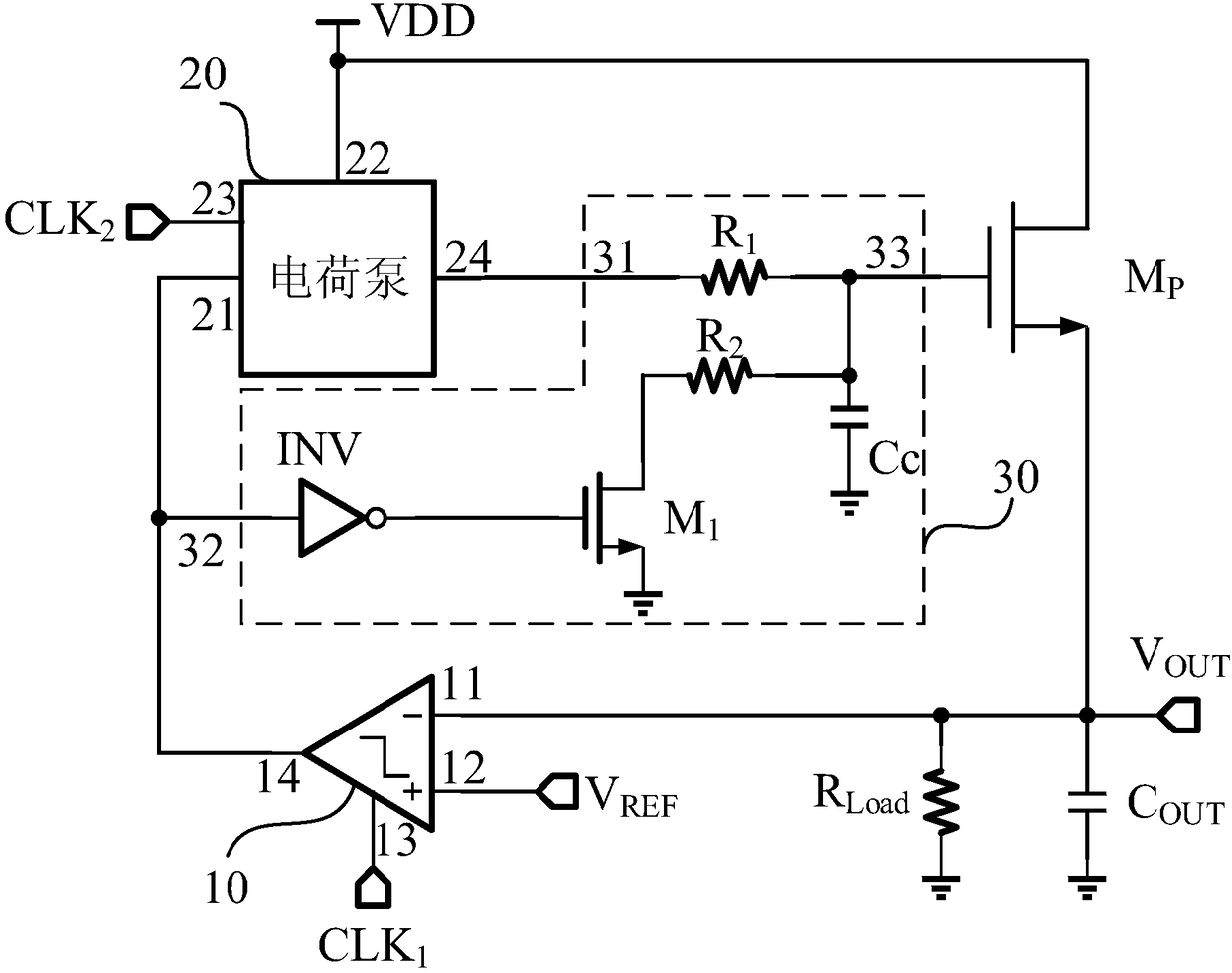

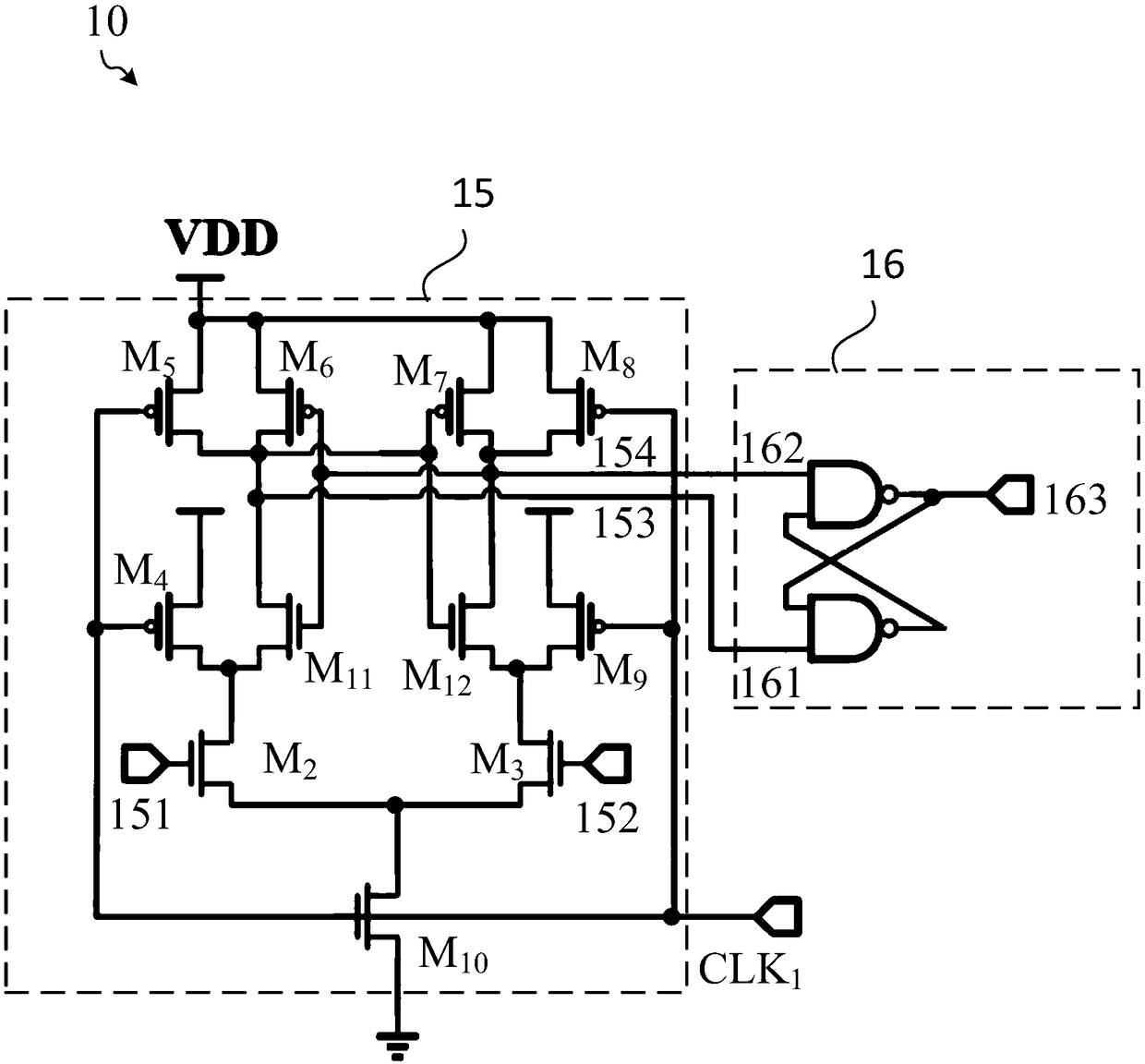

Pseudo digital low-pressure-difference linear voltage stabilizer and power management chip

ActiveCN108508958ARaise the gate voltageAvoid it happening againElectric variable regulationElectricityVoltage reference

The invention discloses a pseudo digital low-pressure-difference linear voltage stabilizer and a power management chip. The pseudo digital low-pressure-difference linear voltage stabilizer comprises an NMOS transistor, a digital comparator, a charge pump and a grid level adjuster. A first input end of the digital comparator is electrically connected with an output end of the pseudo digital low-pressure-difference linear voltage stabilizer. A second input end of the digital comparator is electrically connected with a reference voltage signal line. A first gating end of the charge pump is electrically connected with an output end of the digital comparator. A power input end of the charge pump is electrically connected with a power voltage signal line. An input end of the grid level adjusteris electrically connected with an output end of the charge pump. A control end of the grid level adjuster is electrically connected with an output end of the digital comparator. An output end of the grid level adjuster is electrically connected with a grid of the NMOS transistor. The transient response performance and the working performance under low power voltages of the pseudo digital low-pressure-difference linear voltage stabilizer are improved, the circuit structure is simplified, and the chip area is reduced.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

LDO/HDO architecture using supplementary current source to improve effective system bandwidth

An LDO / HDO circuit adds a supplementary current source to supply the output node. The current boosting section includes a digital comparator with a first input connected to the LDO's feedback loop and a second input connected to a reference level. The comparator then generates a digital output used to control the supplementary current source. This approach also can be used in a far-side implementation, where the local supply level for the load is boosted by the current source based a comparison of this local level and the output of the LDO. Miller capacitive compensation is also considered. Current in shunted to ground from a node in the Miller loop, where the level is controlled by the output of a digital comparator base on a comparison of the circuit's output voltage and a reference level.

Owner:SANDISK TECH LLC

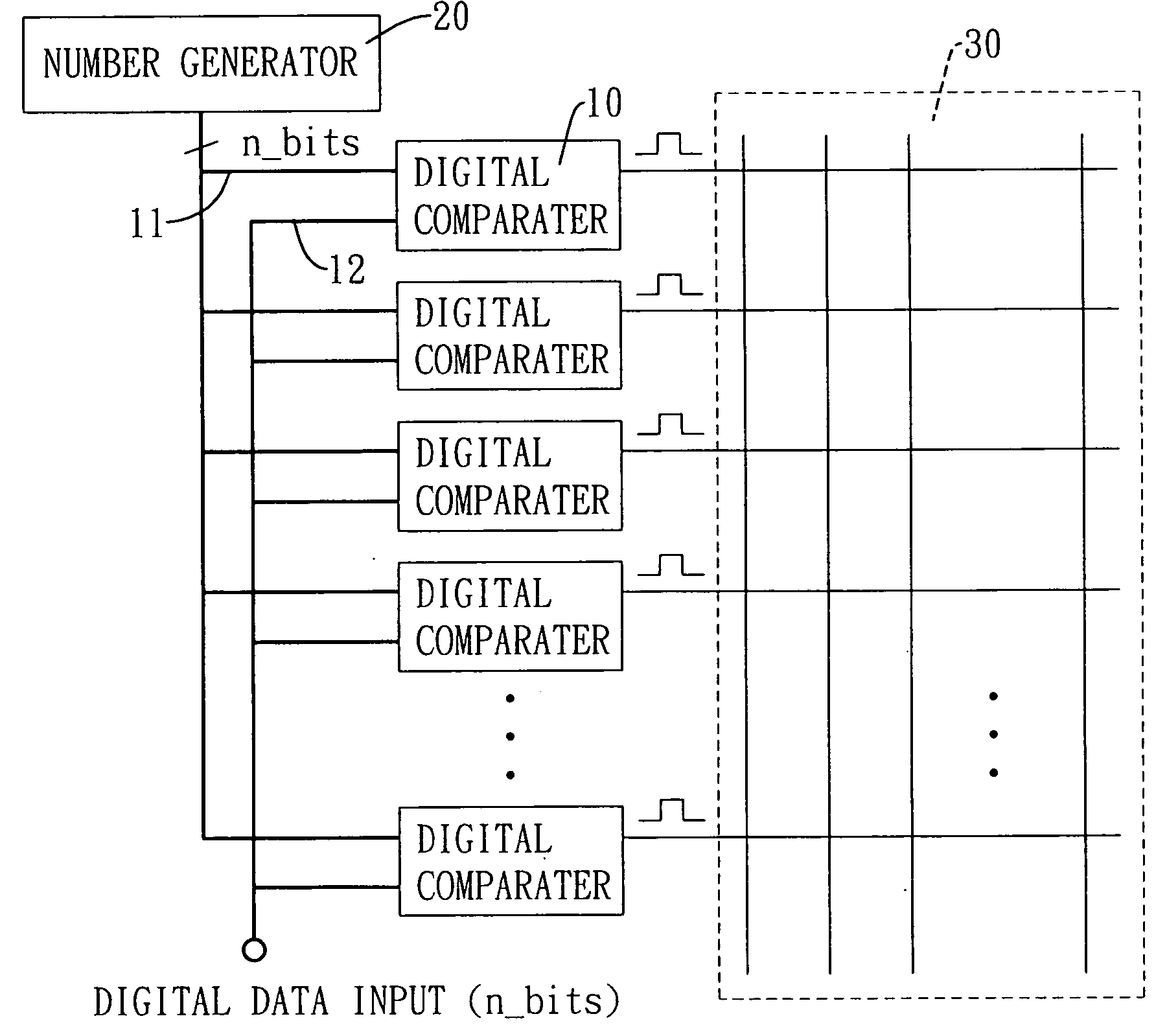

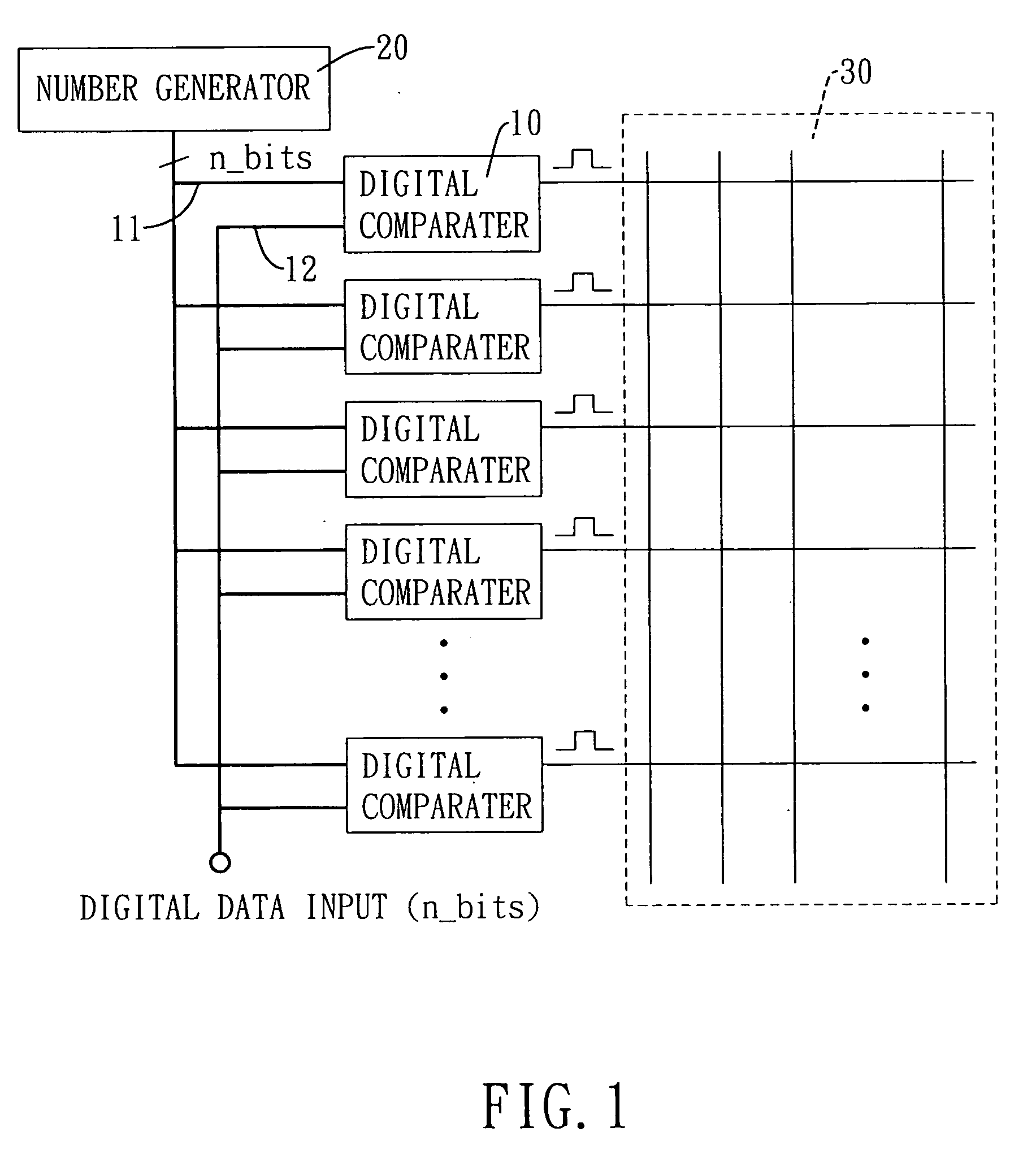

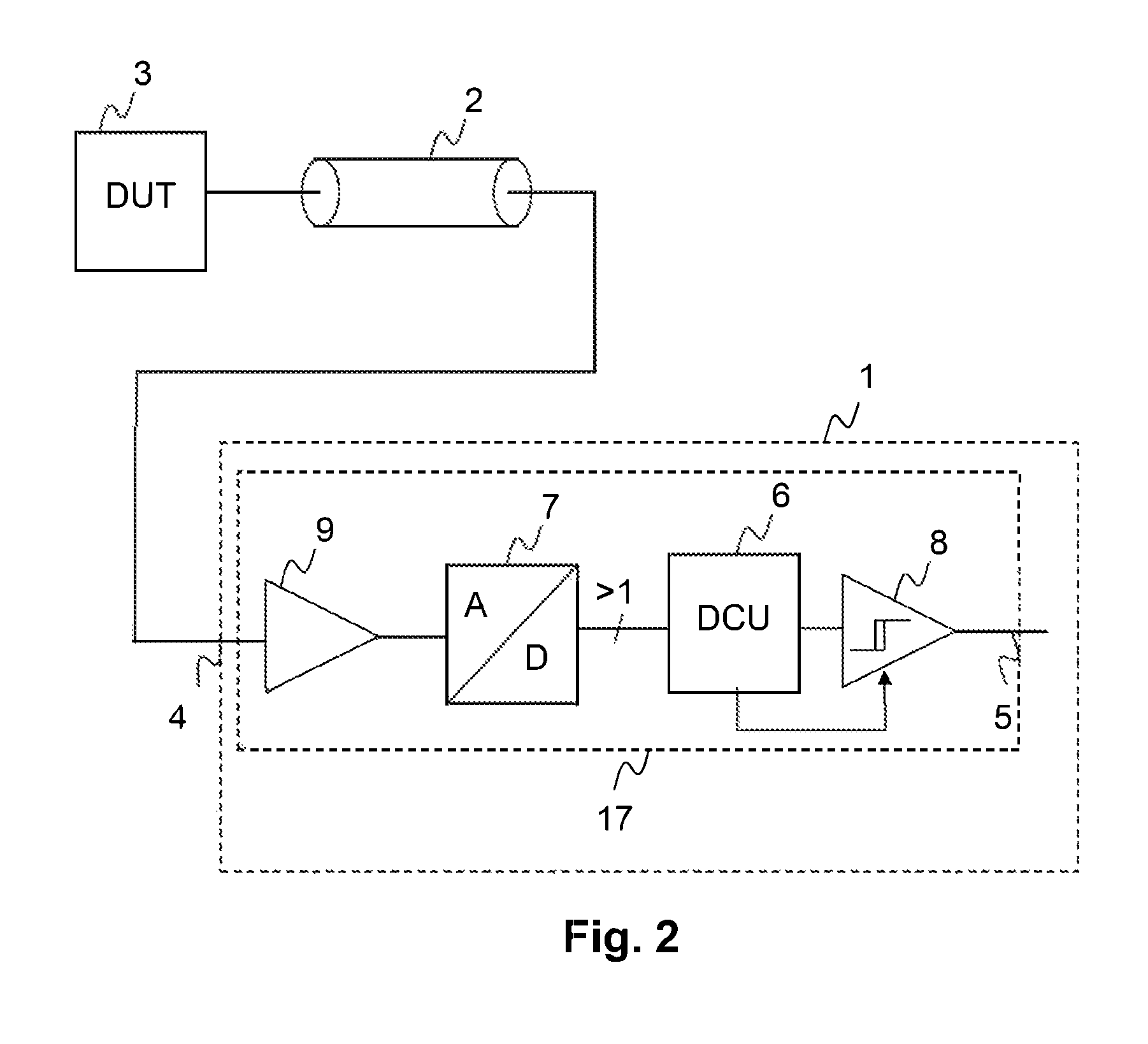

Multi-channel display driver circuit incorporating modified D/A converters

ActiveUS20050156918A1Reduce chanceSimple structureElectric signal transmission systemsCathode-ray tube indicatorsDigital dataElectromagnetic interference

A multi-channel display driver circuit incorporating modified D / A converters has a plurality of digital comparators connected to a number generator. Each digital comparator has an output, a digital data input and a reference input. The reference inputs of all digital comparators are connected to the number generator and the outputs are respectively connected to corresponding data channels of a display. By the proposed technique, each digital comparator obtains a unique non-sequence reference signal, and then compares it with the input digital data signal. Since the non-sequential signals are input to the reference input of the digital comparator, the overshoot distortion, the harmonic distortion and the electromagnetic interference problems are prevented. Therefore, the precise imaging can be obtained with this signal modulation technique in small circuit size.

Owner:SILICON TOUCH TECH INC

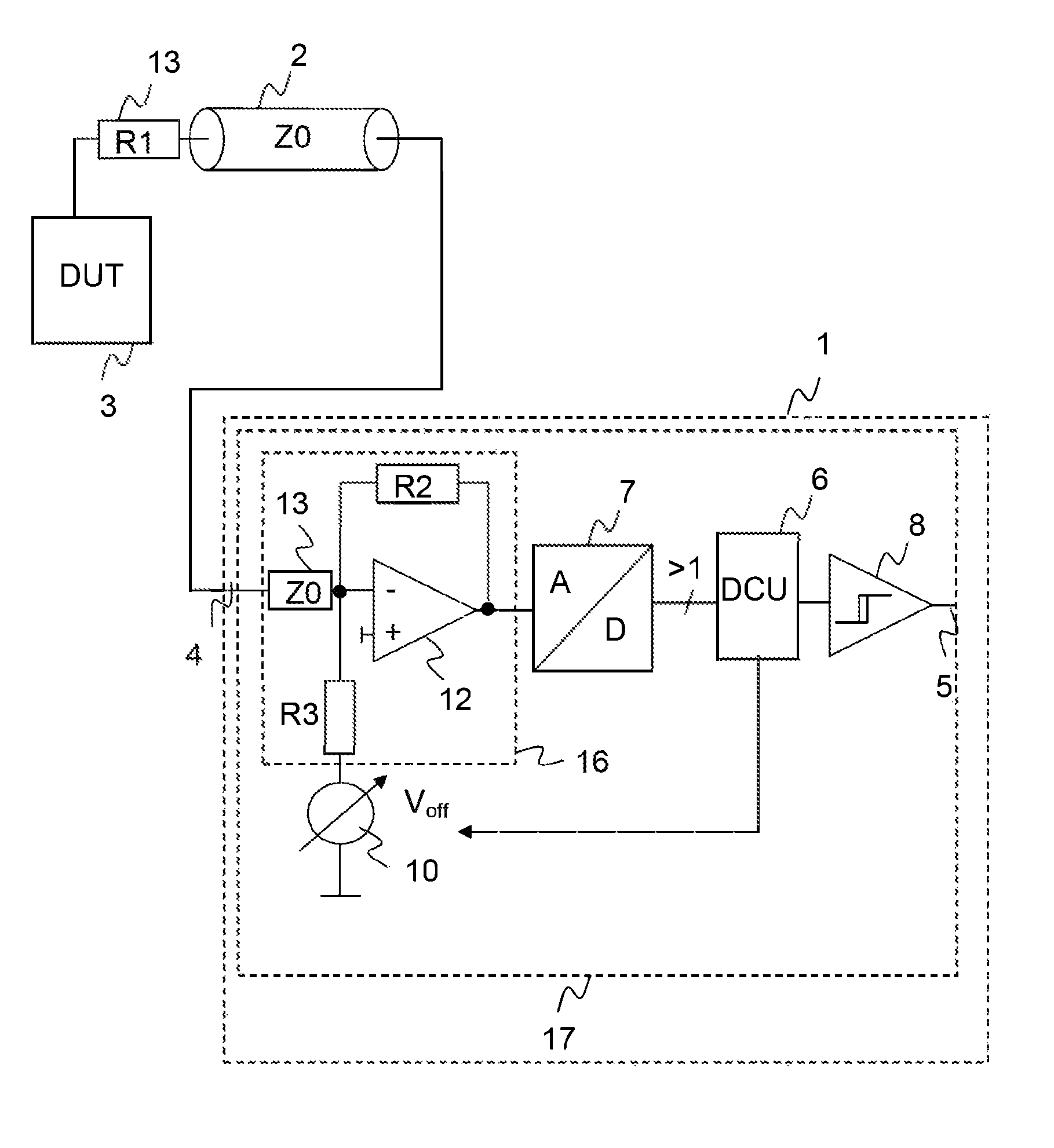

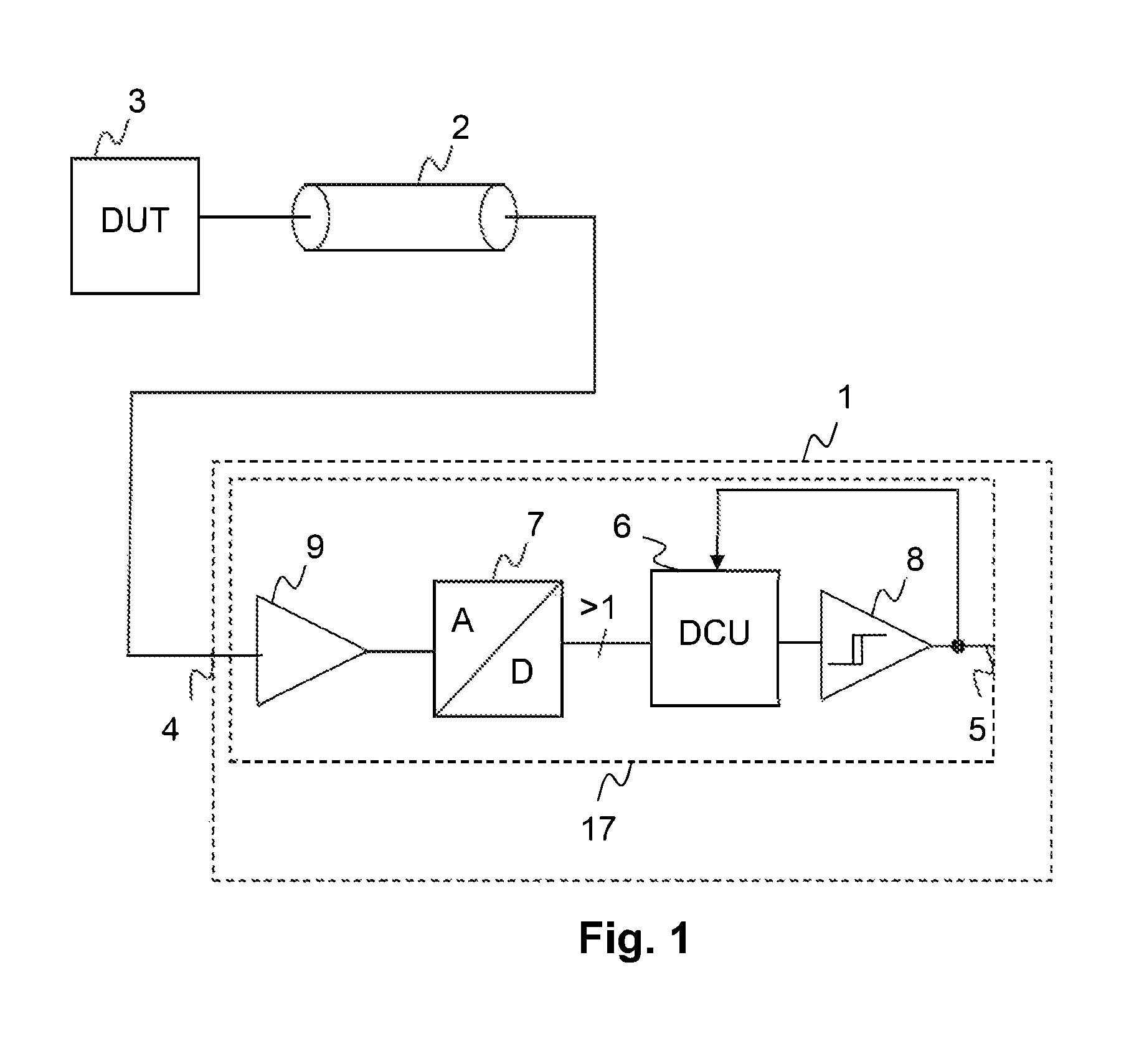

Oscilloscope with logic analyzer frontend

ActiveUS9484942B1Improve test throughputLow costDigital variable/waveform displayAnalogue-digital convertersDigital down converterDecision threshold

An electronic test apparatus, such as an oscilloscope, comprising a logic analyzer frontend, wherein the logic analyzer frontend comprises a digital input port configured to receive a digital signal from a device under test. The logic analyzer frontend further comprises at least one analog-to-digital converter that is arranged downstream of the digital input port, and a digital comparator that is arranged downstream of the analog-to-digital converter. The digital comparator is configured to generate an adjusted digital signal and to provide the adjusted digital signal to further components of the electronic test apparatus. The logic analyzer frontend further comprises a digital correction unit configured to adjust a digital decision threshold value of the comparator.

Owner:ROHDE & SCHWARZ GMBH & CO KG +1

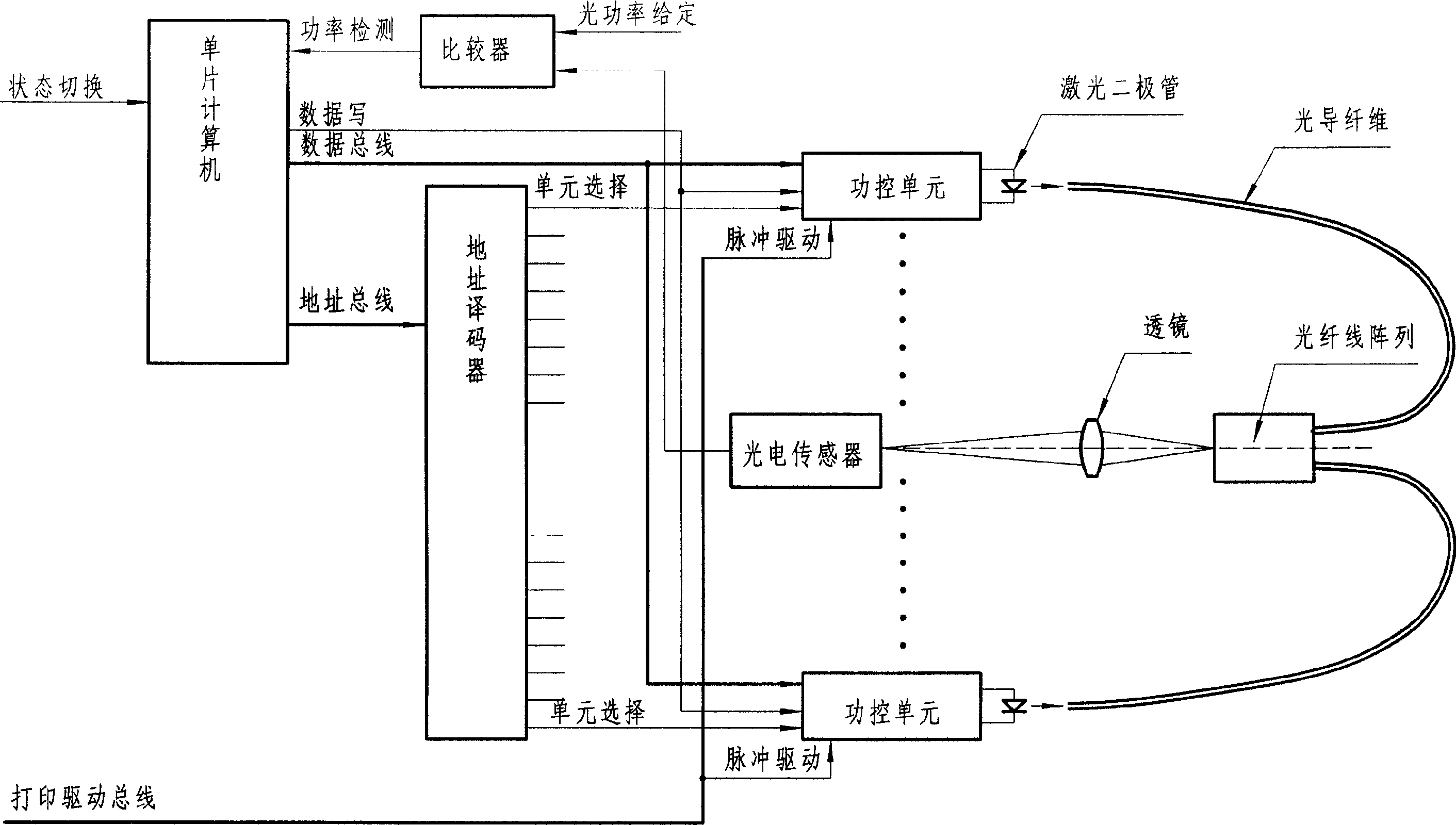

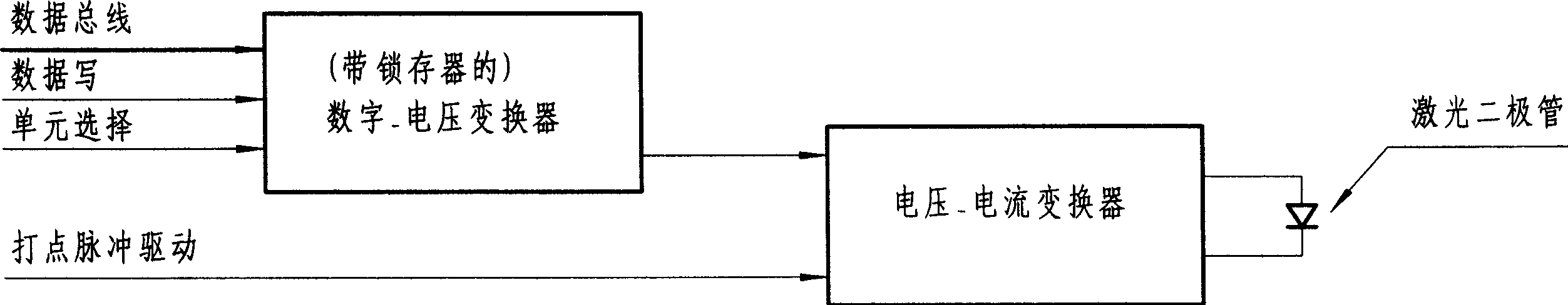

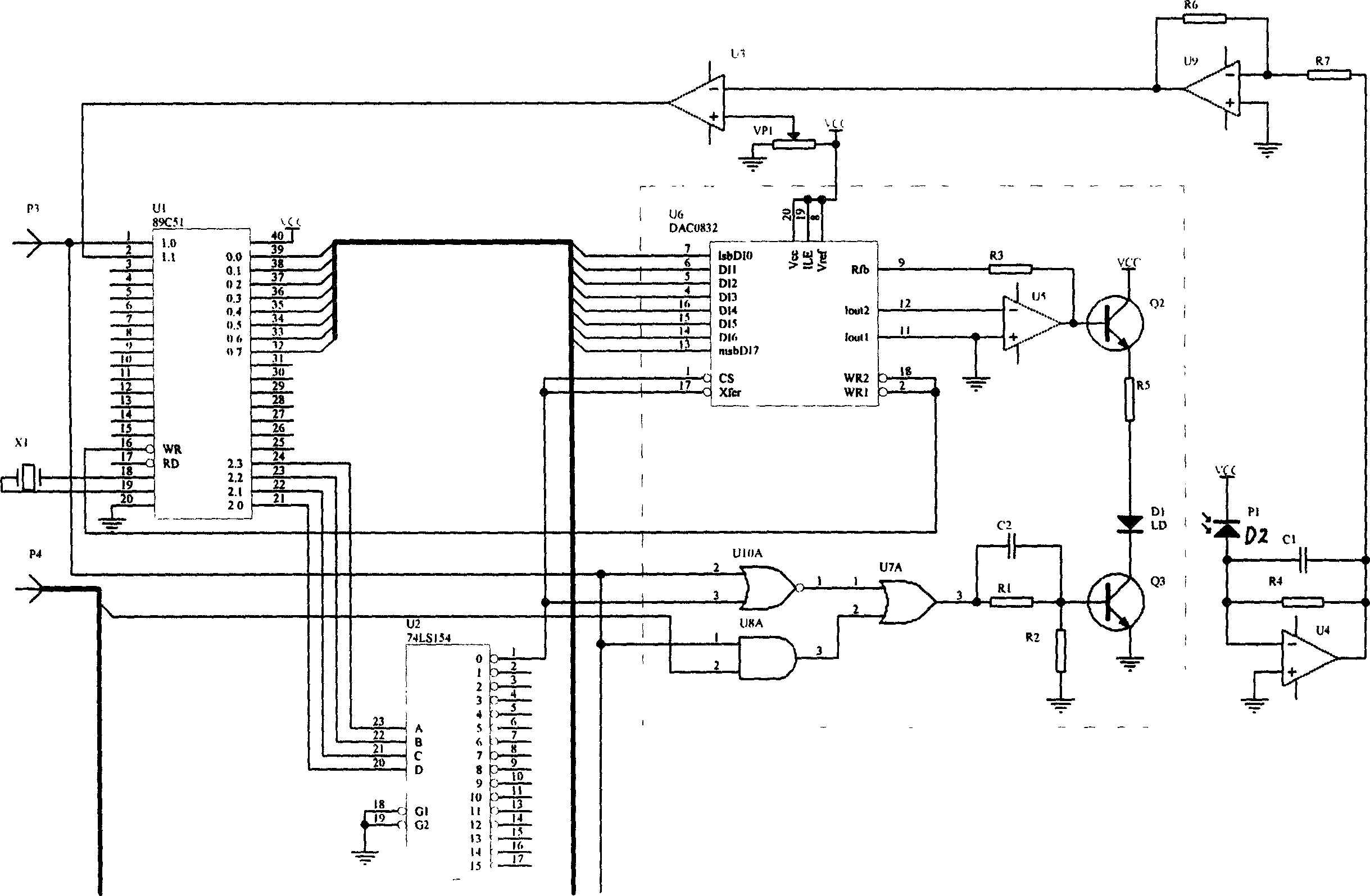

Method and device for realiznig multiple light path automatic balance regulation in laser phototypesetting

InactiveCN1586887AAddressing Power ImbalancesOvercoming the Moiré phenomenonPhotometryPhotoelectric composing devicesFiberFiber array

The method and device for realizing automatic balance regulation of several light paths is mainly used in multiple light path scanning imaging system in laser phototypesetting. The method includes setting each of the light power control unit in either calibration state or scanning state; setting switching circuit for switching between the two states; and performing automatic real-time detection and regulation of the light power control units in calibration state circularly with computer. The device for the said method includes monochip computer, address decoder, digital comparator, photoelectric sensor, lens, linear fiber array, light conducting fiber, power control unit and print drive bus. The present invention balances power of the light paths, eliminates moire fringe, and raises the scanning imaging precision of laser phototypesetting system.

Owner:深圳市东方宇之光科技股份有限公司

Method and apparatus for dithering in multi-bit sigma-delta digital-to-analog converters

A multi-bit (M-bit, M>1 ) Sigma-Delta digital-lo-analog converter (DAC) with a variable resolution multi-bit quantizer that has its digital value inputs that are truncated or rounded to a resolution that follows a random or pseudo-random sequence to provide automatic dynamic dithering for removing undesired idle tones in the analog output of the Sigma-Delta DAC. Random numbers N(n) between 1 and M are provided, and M-N(n) least significant bits in each M-bit digital value at the output of the quantizer are forced to zero with a digital trunealor or rounder. The random numbers N(n) may be provided by a random or pseudo-random sequence generator, e.g., Galois linear feedback shift register in combination with digital comparators and an adder.

Owner:MICROCHIP TECH INC

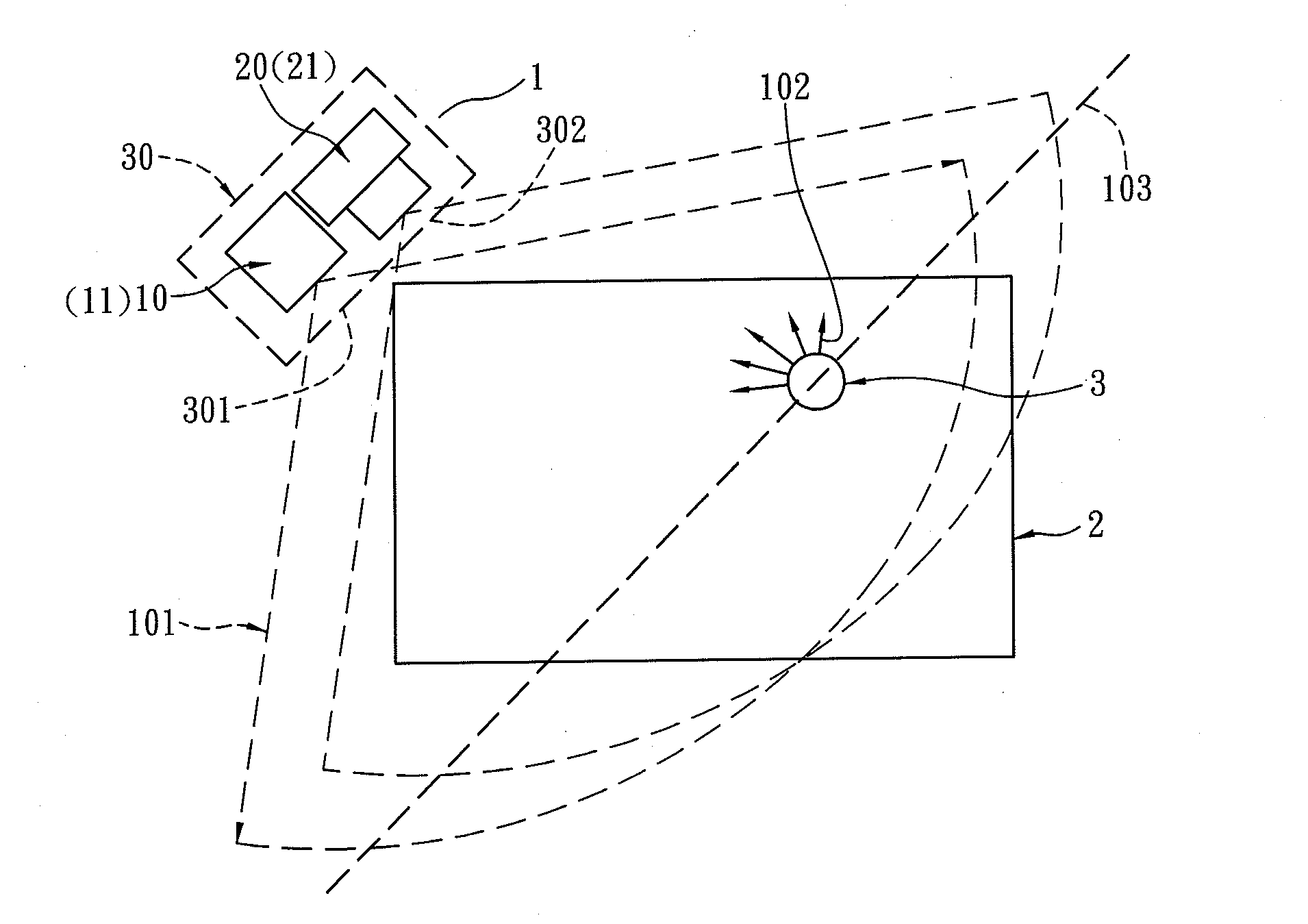

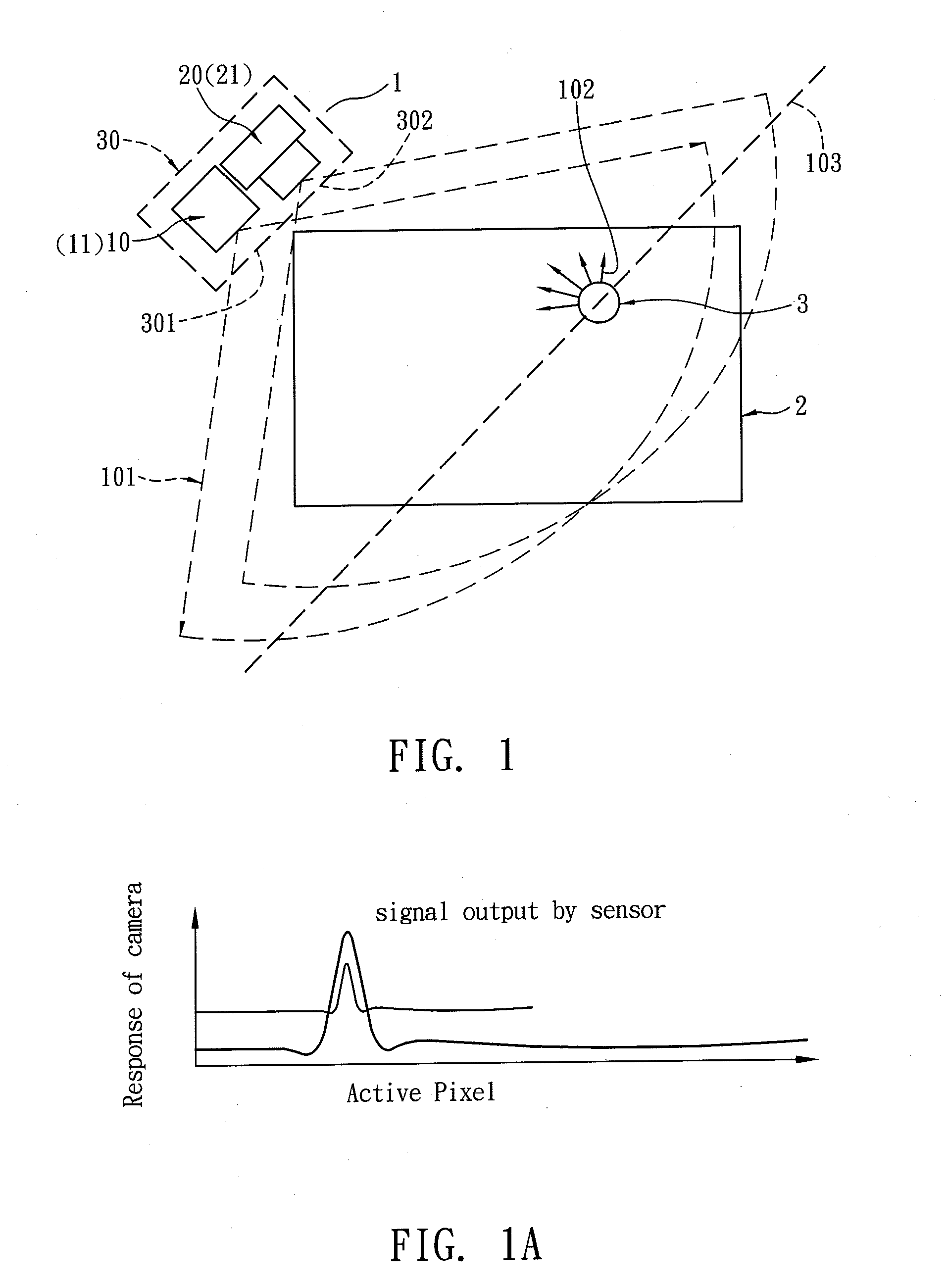

Laser optical touch control module analog-to-digital conversion system and method of the same

InactiveUS20130147766A1Simple structureImprove fluencyAnalogue/digital conversionElectric signal transmission systemsLight beamComputer module

A laser optical touch control module includes a light emitting part with a laser light source and a light receiving part with a position sensor. A laser beam is emitted from the laser light source and reflected by a wide angle optical element. Thus a light fan of the reflected light is larger than 90 degrees to form a wide angle linear light beam. The position of a touch control widget is obtained by a sensor of the light receiving part that detects the linear light beam blocked and reflected by the touch control widget. An analog-to-digital conversion system includes a variable reference level generator that calculates to generate a variable reference level according to different variances. Then the sensor output data is converted into a digital signal based on the reference voltage level by a digital comparator and the digital signal is output to a processor.

Owner:SERAFIM TECH

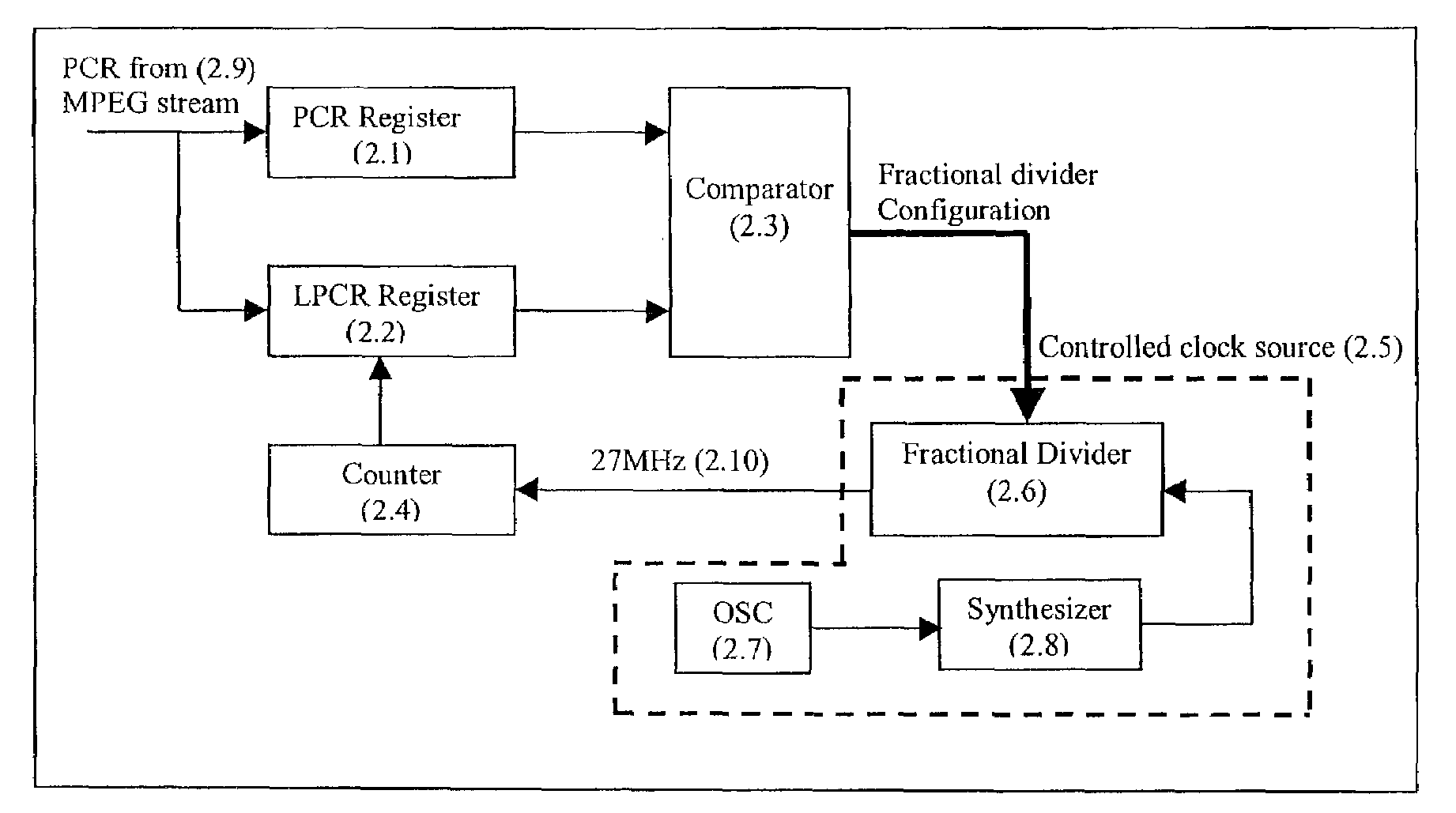

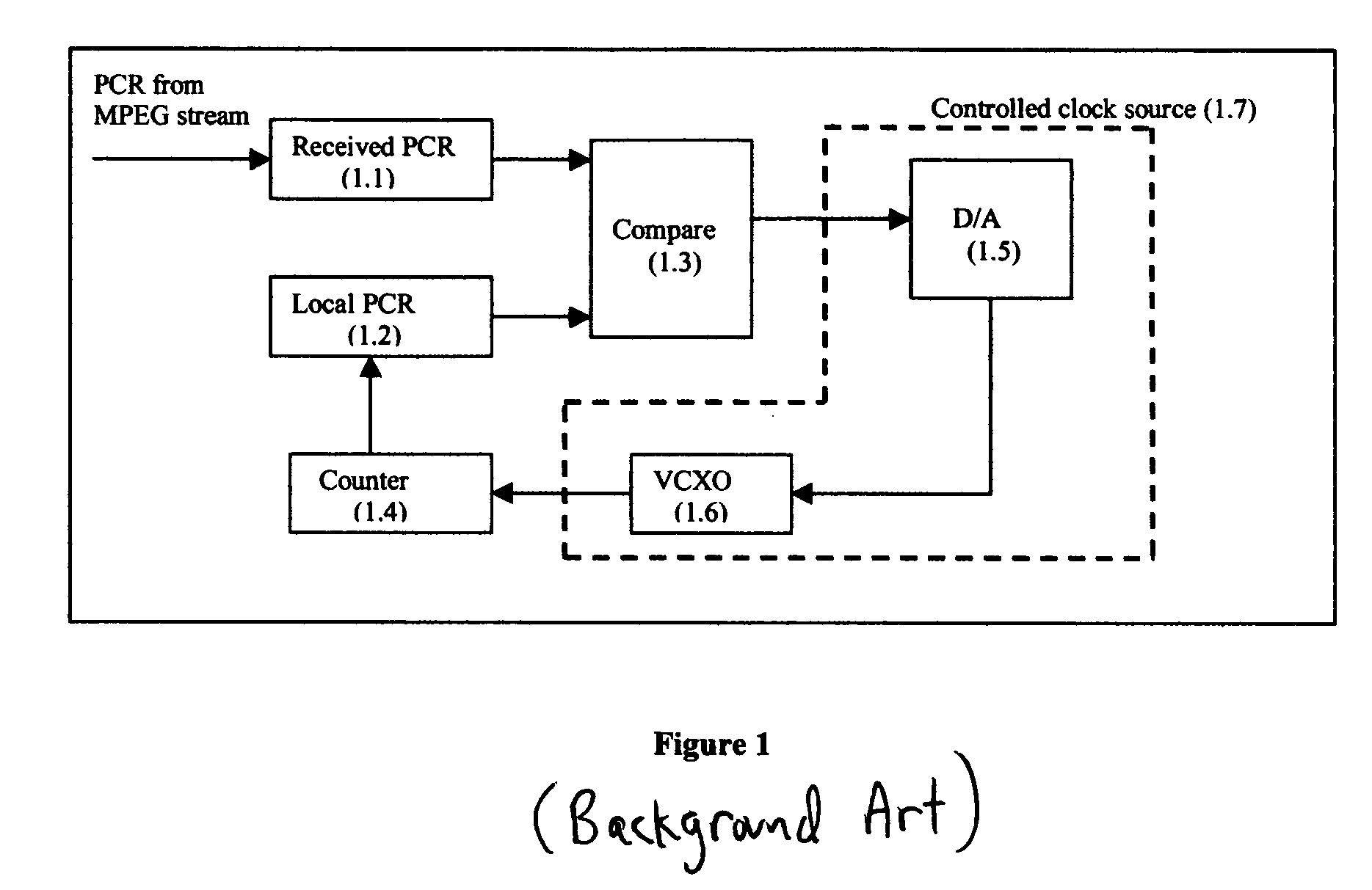

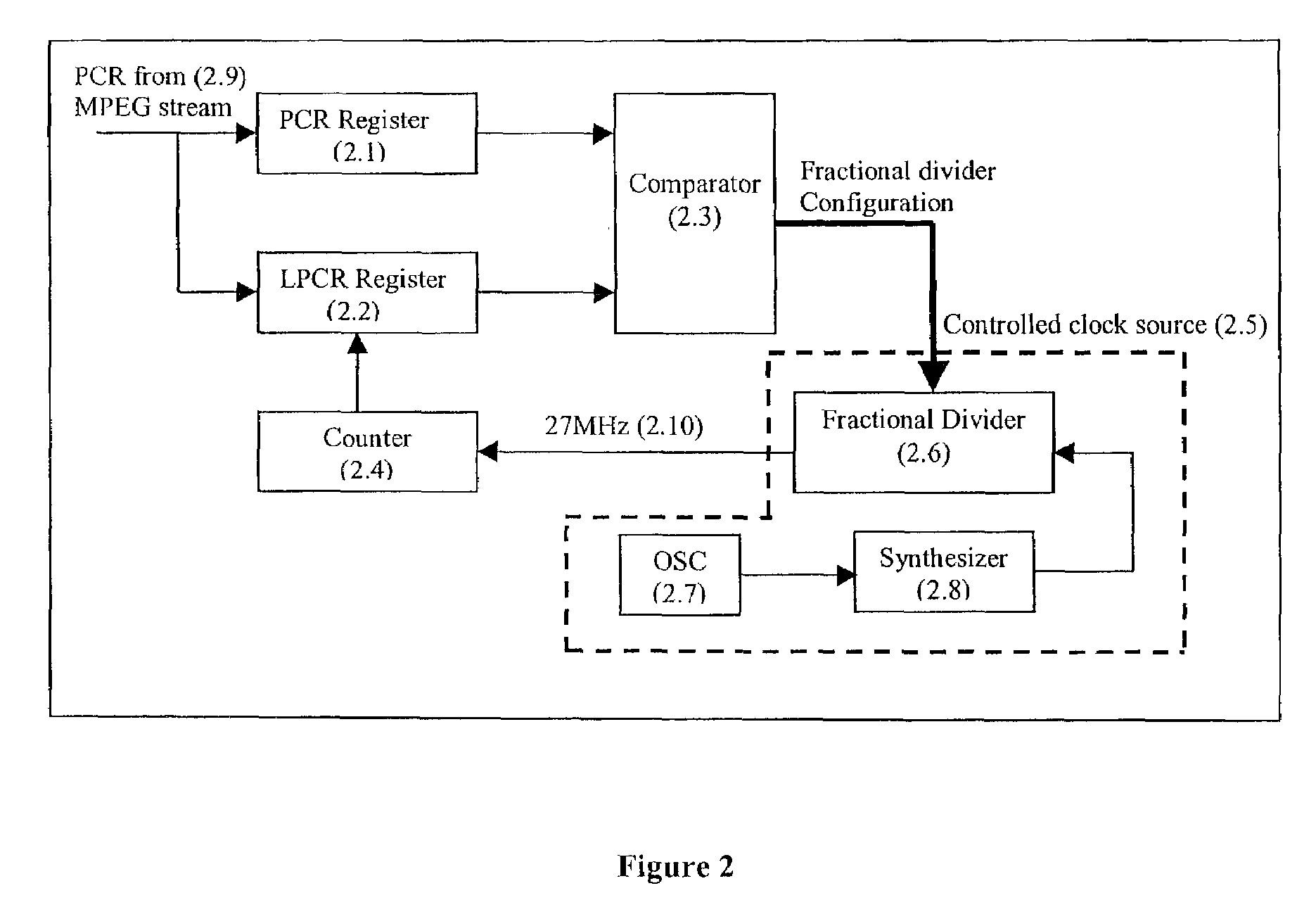

Clock recovery from data streams containing embedded reference clock values

InactiveUS7801261B2Reduce severityEliminates and reduces severityPulse automatic controlSelective content distributionData streamDigital clock

A method and an improved apparatus for clock recovery from data streams containing embedded reference clock values controlled clock source includes of a controllable digital fractional divider receiving a control value from digital comparator and a clock input from a digital clock synthesizer driven by a fixed oscillator.

Owner:STMICROELECTRONICS PVT LTD

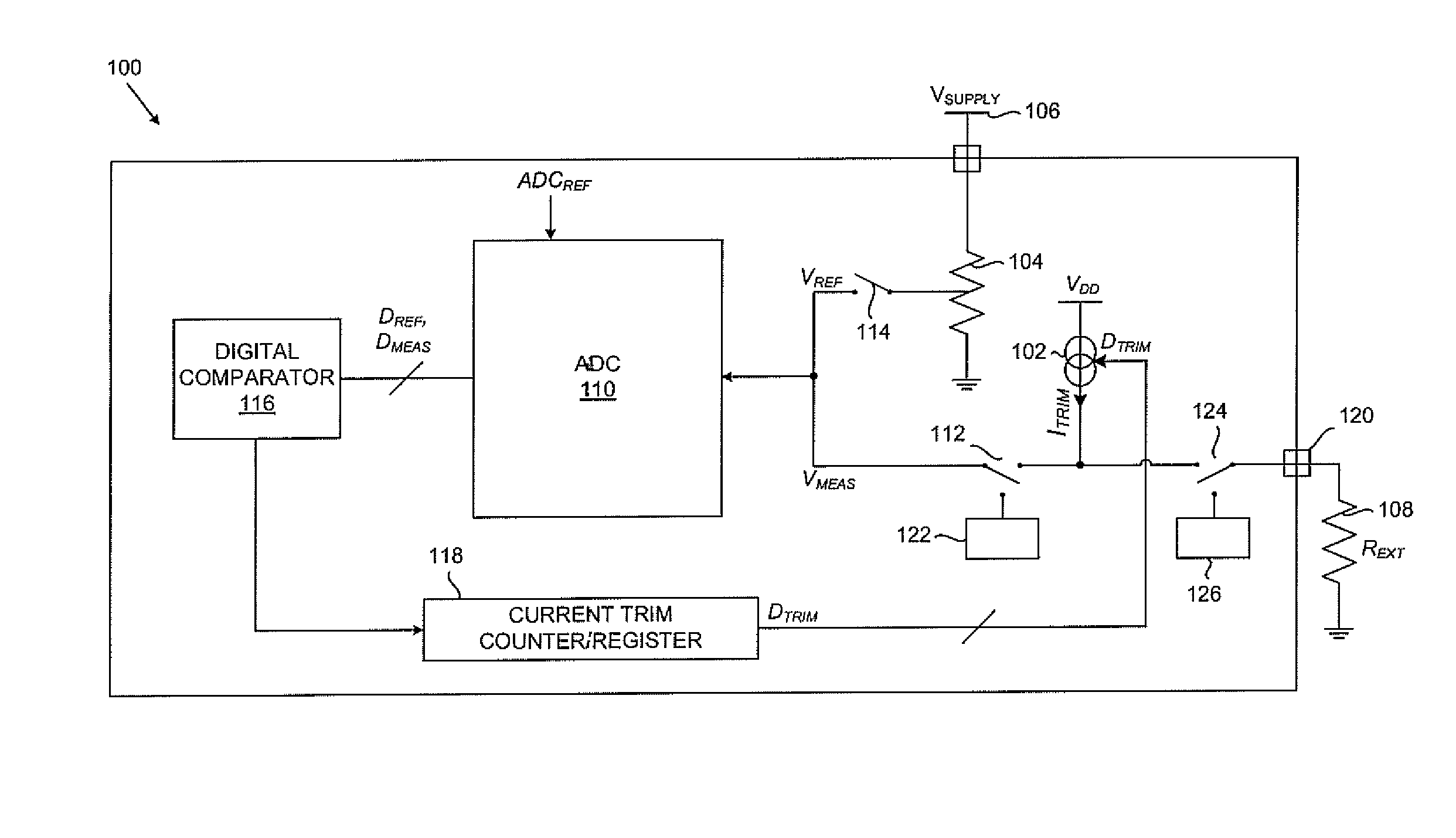

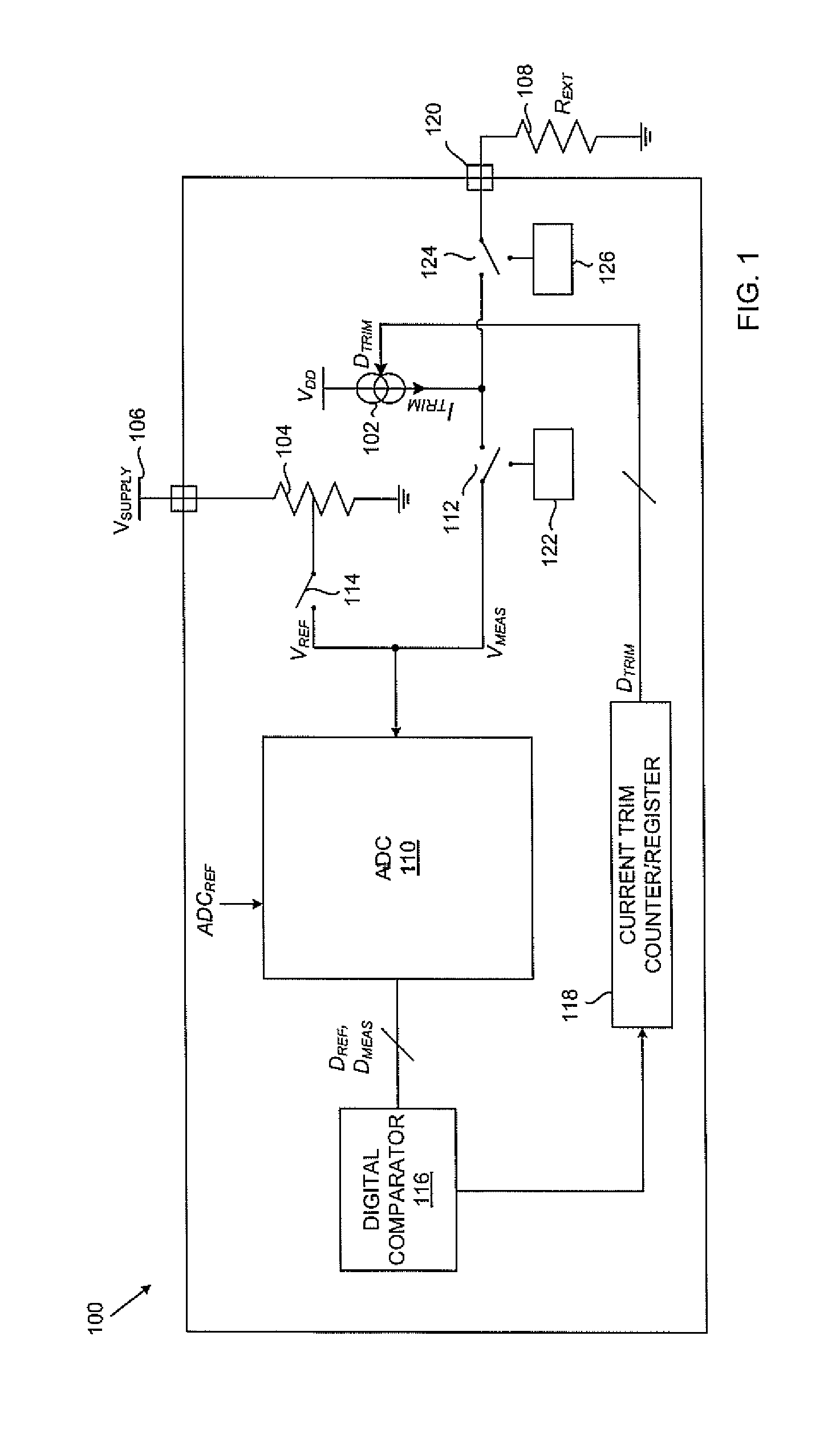

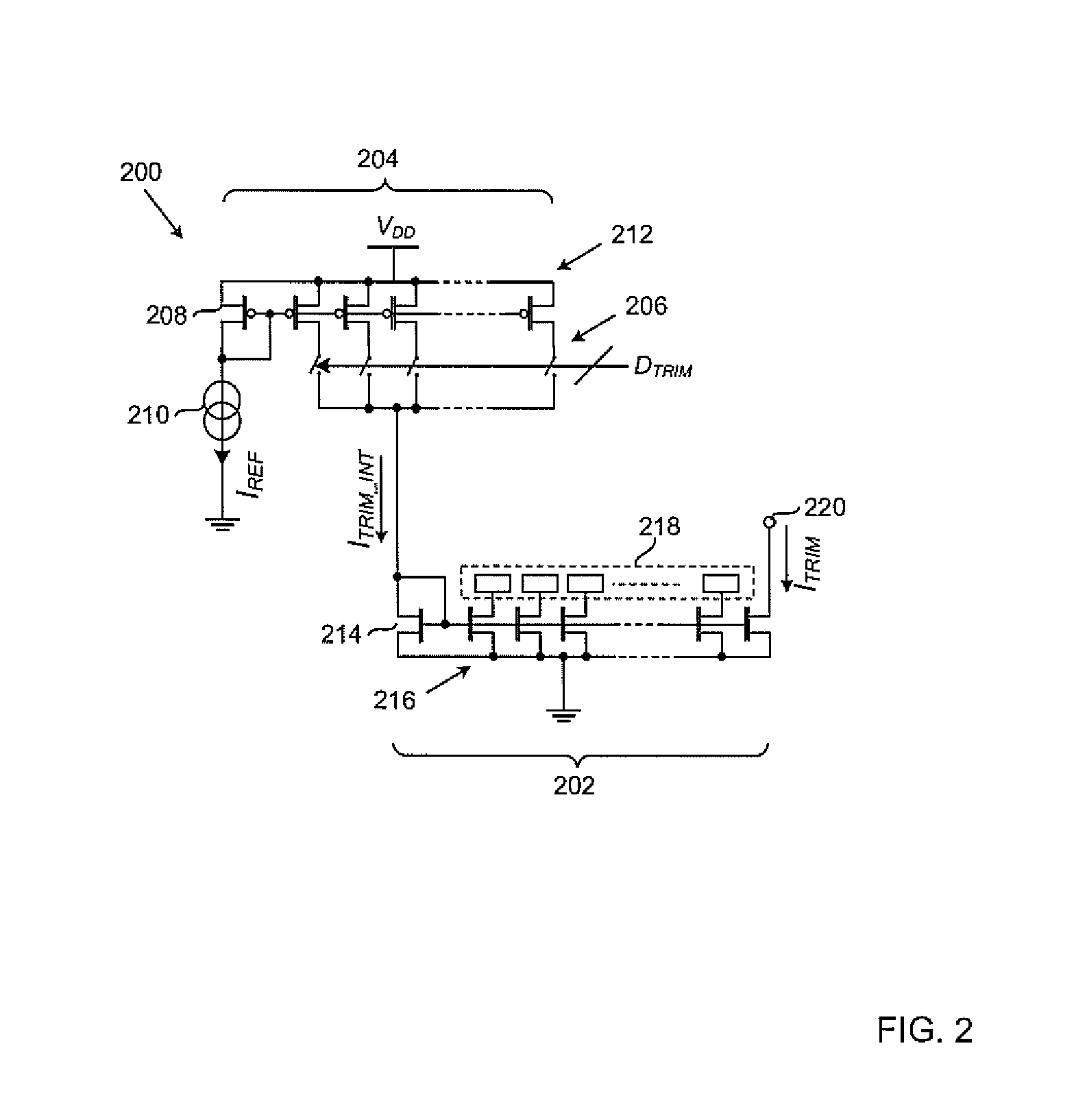

Method of trimming current source using on-chip ADC

A method of trimming a current source in an IC includes deriving a reference voltage from an external supply, and developing a measurement voltage across an external reference resistance receiving the current to be trimmed. An on-chip ADC is used to provide corresponding digital reference and digital measurement signals. A digital comparator compares the digital signals and provides a digital trim signal, which is used to adjust the current to be trimmed until the digital measurement signal is equal to the digital reference signal within an acceptable tolerance. Gain and offset errors in the ADC cancel and do not affect the calibration of the trim operation.

Owner:NXP USA INC