Phase-locked loop with correction and correction method thereof

A phase-locked loop and correction loop technology, applied in the field of microelectronics, can solve problems such as difficulty in obtaining high-speed and stable clocks, and impact on clock system performance, and achieve the effects of low power consumption, simple and clear structure, and improved stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

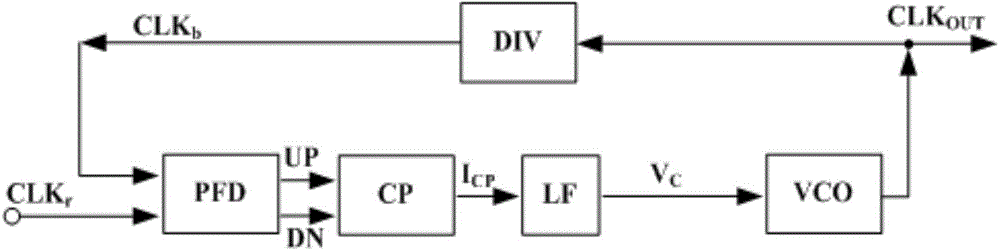

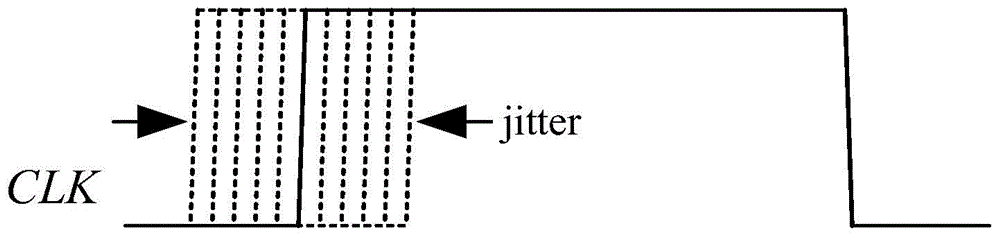

[0031] Such as Figure 5 Shown is a phase-locked loop with correction. After the circuit is powered on, the PLL main loop works normally and tracks the reference clock CLK r The frequency and phase of the lock detector (LD) output signal V LD is low, the correction loop is not started; when the PLL loop is locked, the feedback clock CLK b The frequency and phase of the reference clock CLK r Consistent, but due to different levels of noise in each unit circuit in the PLL loop, the feedback clock CLK b Will exhibit random jitter (such as Figure 6 shown), so after the main loop locks, the lock detector (LD) outputs a signal V LD Change to high level, the correction loop starts to work.

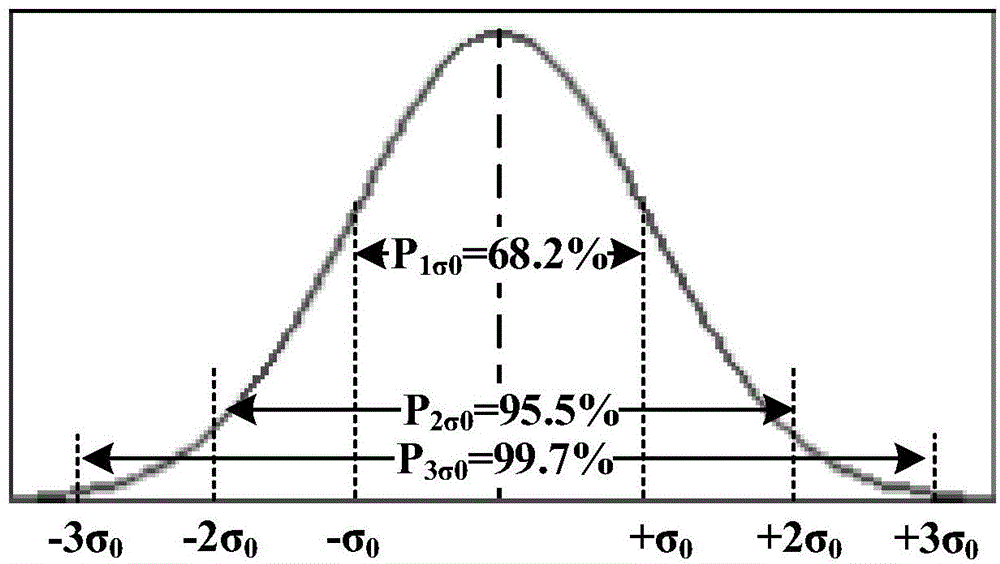

[0032] 2-bit time-to-digital converter (TDC) comparison feedback clock CLK b with reference clock CLK r offset and generate a digital output code. Such as Figure 6 shown, if CLK b Occurs at -σ 0 On the left side, the output code is 00; if CLK b in [-σ 0 ,+σ 0 ] range, the output c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More