Digital triggering system of oscilloscope

A digital oscilloscope and digital comparison technology, applied in the direction of digital variable display, etc., can solve the problems of large correlation of hardware circuits, limitation of sensitivity of analog trigger system, and offset of displayed waveform relative to trigger point, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

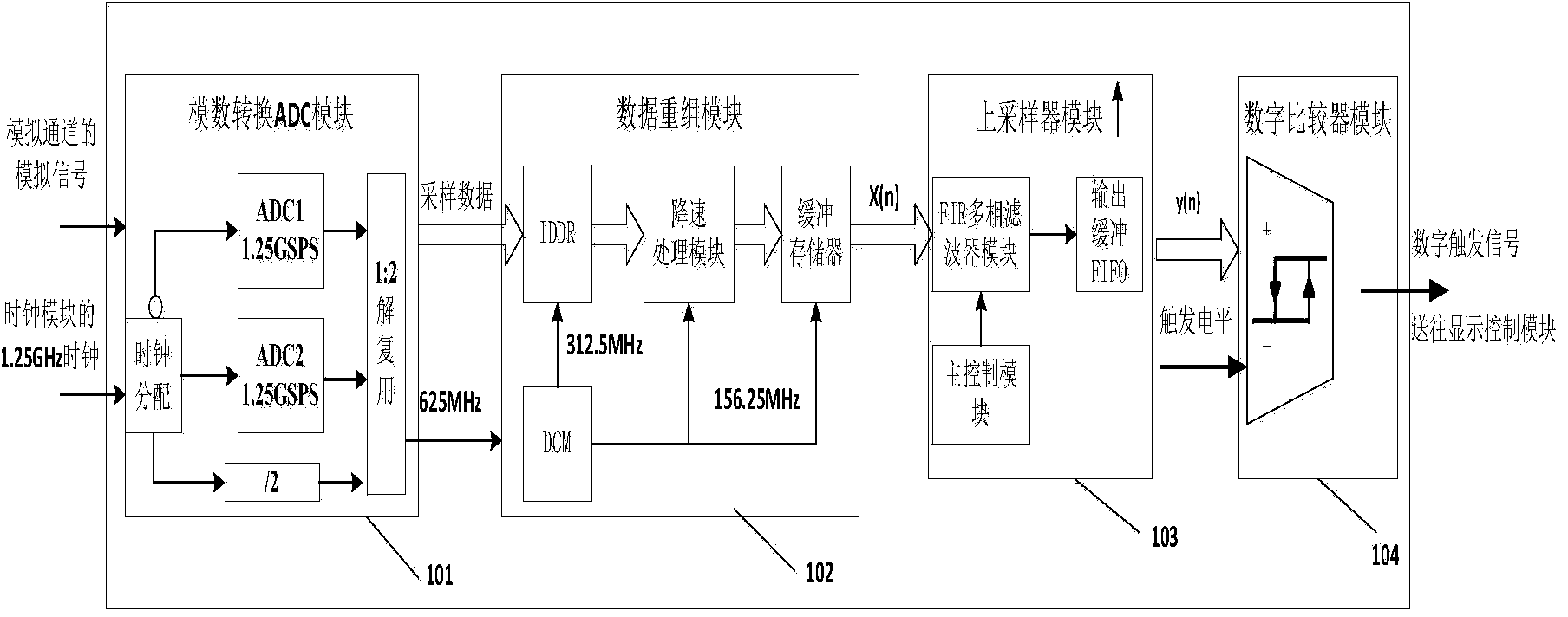

[0023] The invention provides a digital oscilloscope trigger system, which uses digital trigger technology and a digital signal processing method to measure trigger points, and detects effective trigger events with precise algorithms. Unlike analog triggering, digital triggering systems work directly on the samples from the A / D converter. The measurement signal is not split into two paths. Therefore, digital triggering processes the same signal that is acquired and displayed. The digital trigger system is mainly realized in FPGA (XC5VLX110-1FFG676).

[0024] The digital trigger system of the digital oscilloscope proposed by the present invention can be applied in the hand-held digital oscilloscope with 200MHz bandwidth and 2.5GSa / s sampling rate. The digital trigger system of the present invention mainly includes an analog-to-digital conversion ADC module, a data reorganization module, an upsampler, The digital comparator consists of four parts.

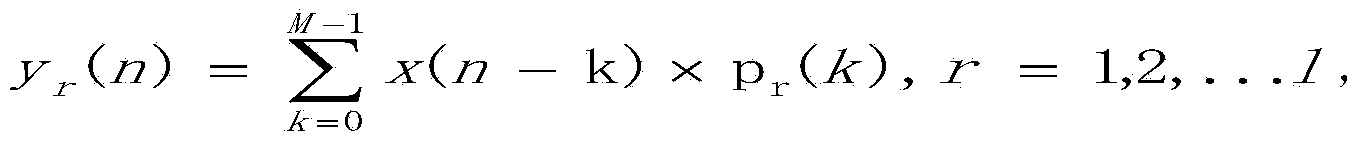

[0025] The analog-to-digit...

Embodiment 2

[0030] On the basis of the above examples, if figure 1 As shown, the present invention provides a digital oscilloscope trigger system, wherein, it is composed of an analog-to-digital conversion ADC module 101, a data recombination module 102, an upsampler module 103, and a digital comparator module 104 and is connected in sequence; the analog-to-digital conversion ADC Module 101 is used to convert the analog signal transmitted by the analog channel of the oscilloscope into a digital signal to generate sampling data with a sampling rate of 2.5GSa / s. The clock generation module outside the system is used to provide a 1.25GHz synchronous clock for the trigger system of the digital oscilloscope , the 1.25GHz clock signal is sent to the clock distribution module in the analog-to-digital conversion ADC module 101, and the 0° and 180° phase difference clock signals of 1.25GHz are sent to two 1.25GSa / s sampling rate modulus respectively Cross-sampling is performed in the conversion AD...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More