Method and apparatus for dithering in multi-bit sigma-delta digital-to-analog converters

A technology of analog-to-analog converter, equipment, applied in the field of digital/analog converter

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] Reference is now made to the drawings, which schematically illustrate details of specific example embodiments. In the drawings, the same elements will be represented by the same numerals, and similar elements will be represented by the same numerals with different lowercase letter suffixes.

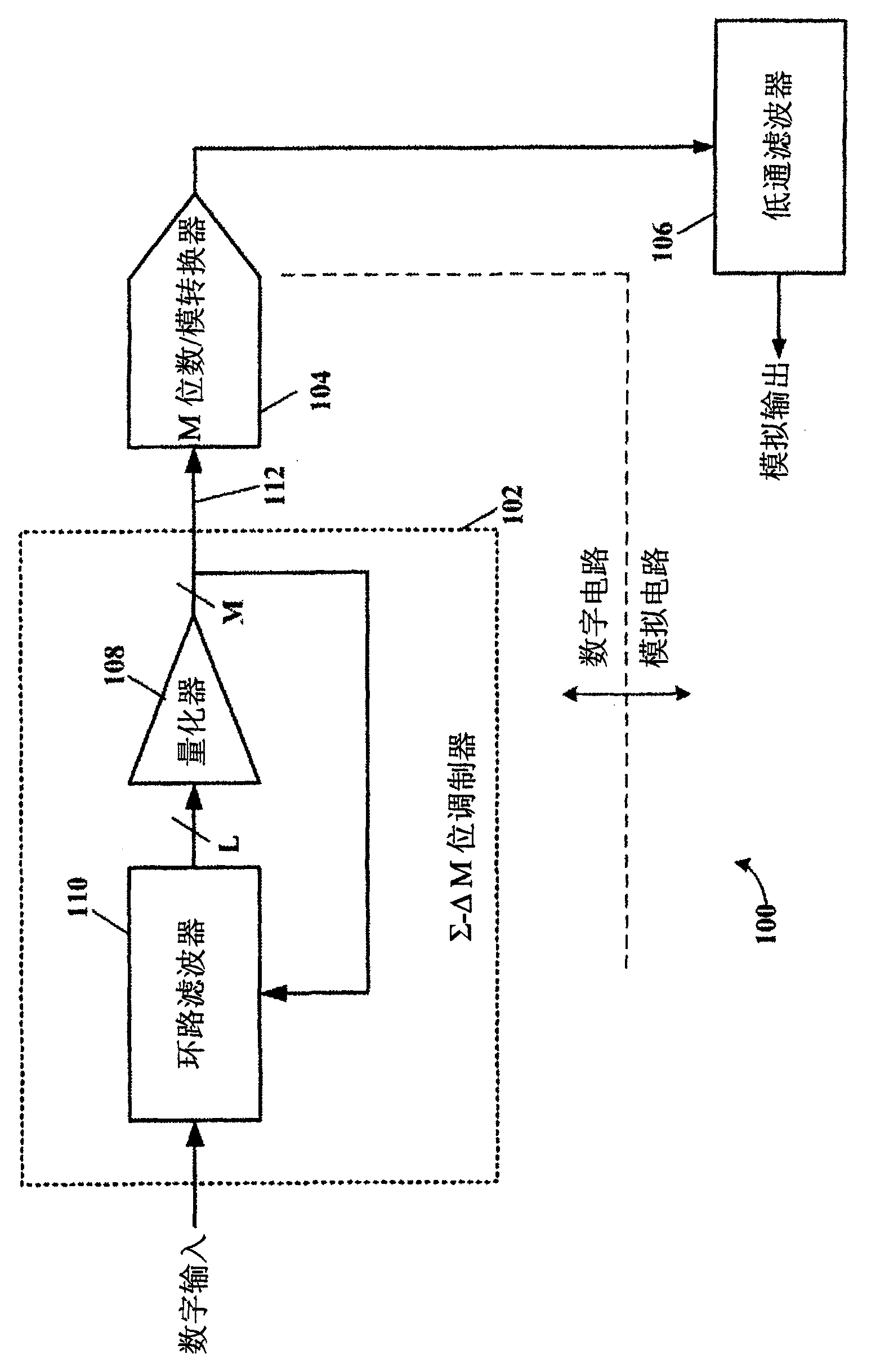

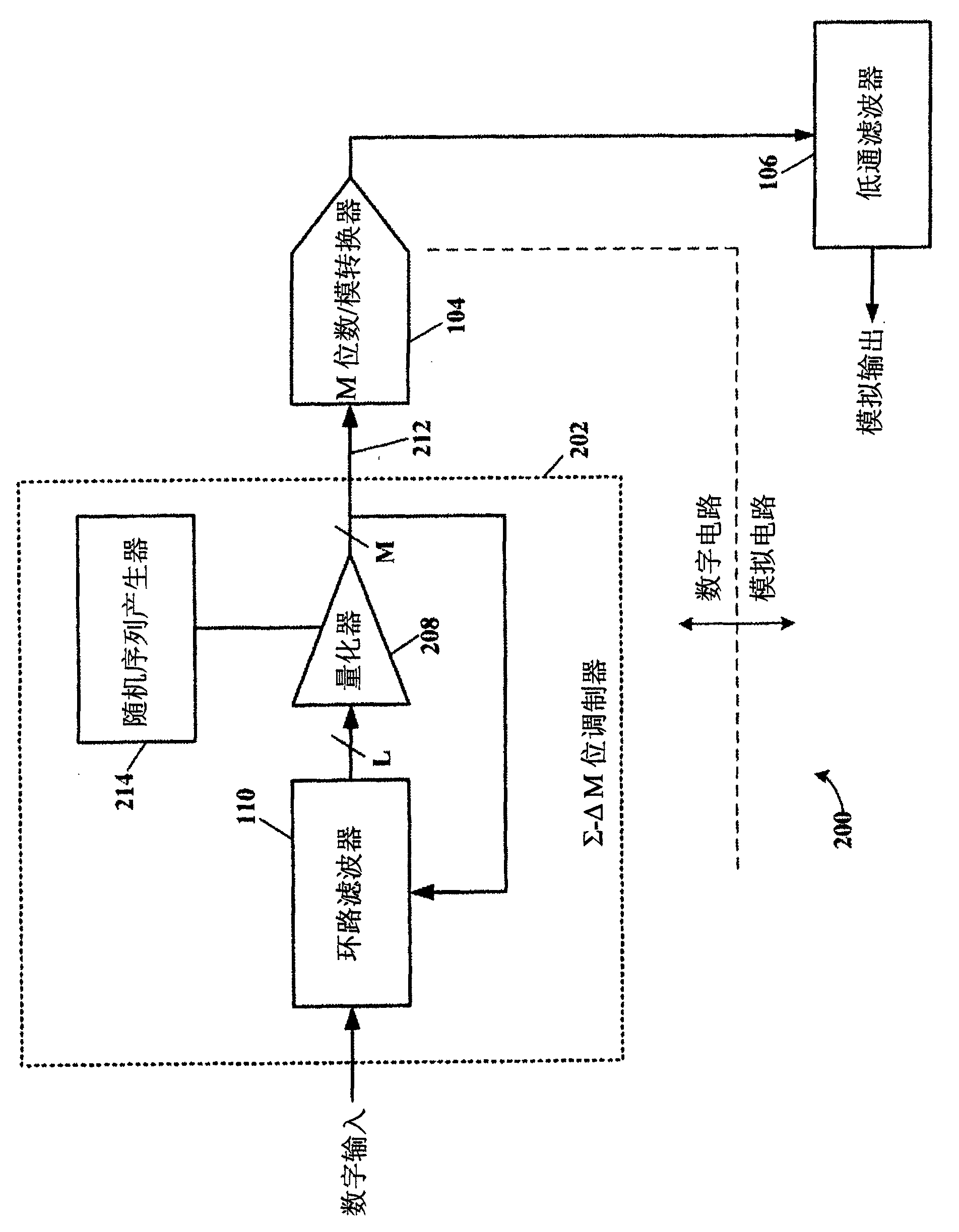

[0021] refer to figure 1 , which depicts a schematic block diagram of a single-loop sigma-delta digital-to-analog converter (DAC) with a multi-bit quantizer. A sigma-delta DAC generally indicated by numeral 100 includes a single-loop sigma-delta M-bit modulator 102 , an M-bit-to-analog converter 104 and an analog low-pass filter 106 . The sigma-delta modulator 102 includes a digital loop filter 110 and a fixed resolution quantizer 108 . Sigma-delta modulator 102 may also use multiple feedback loops in its design.

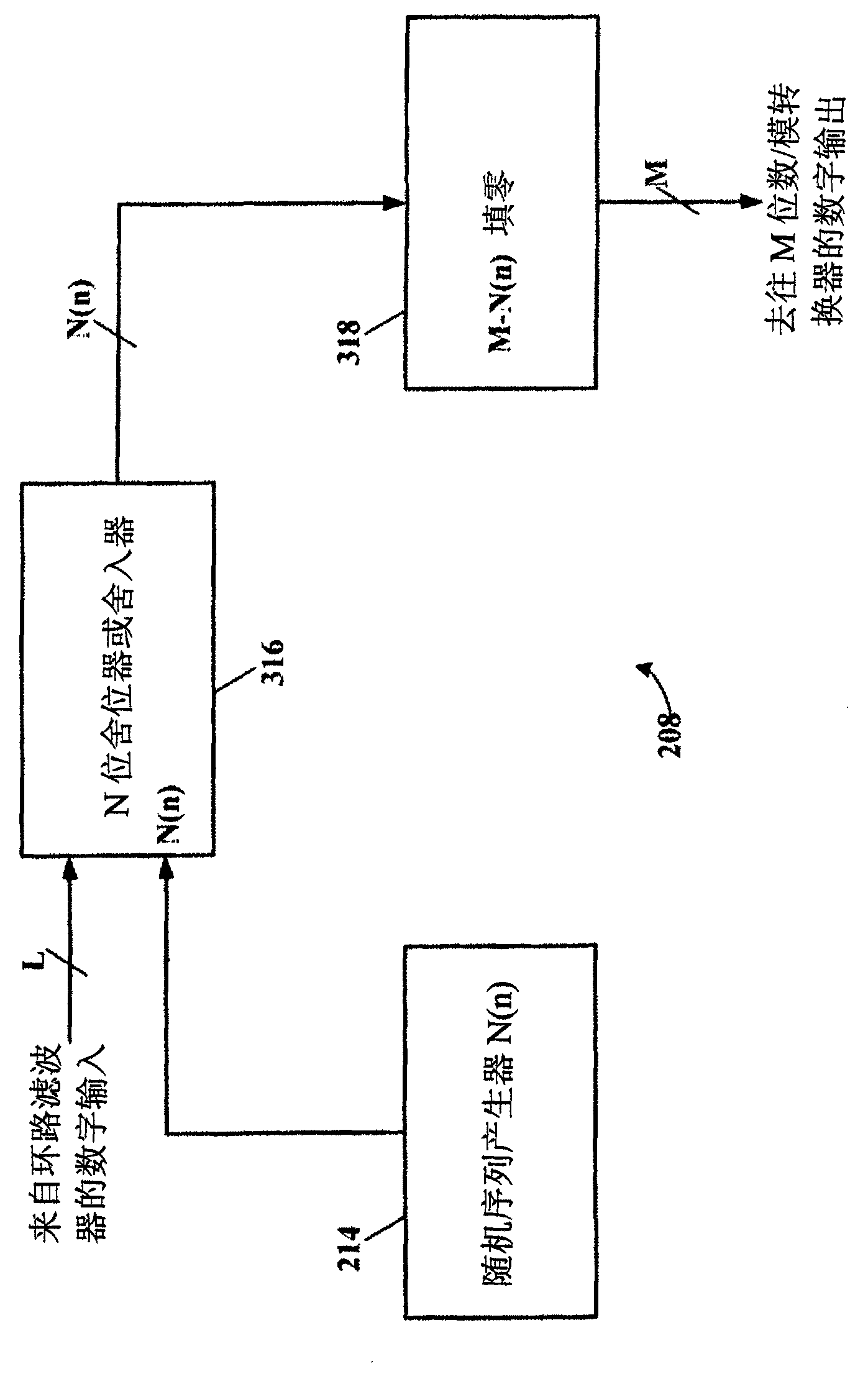

[0022] Fixed-resolution quantizer 108 processes L-bit words at its input and provides M-bit words at its output (where L>=M). Fixed-resolution quantizer 108 typical...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More