Method and apparatus for dithering in multi-bit sigma-delta analog-to-digital converters

A digital converter and equipment technology, applied in the field of automatic dynamic jitter, to achieve the effect of high-efficiency pitch scrambling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] Reference is now made to the drawings, which schematically illustrate details of specific example embodiments. In the drawings, the same elements will be represented by the same numerals, and similar elements will be represented by the same numerals with different lowercase letter suffixes.

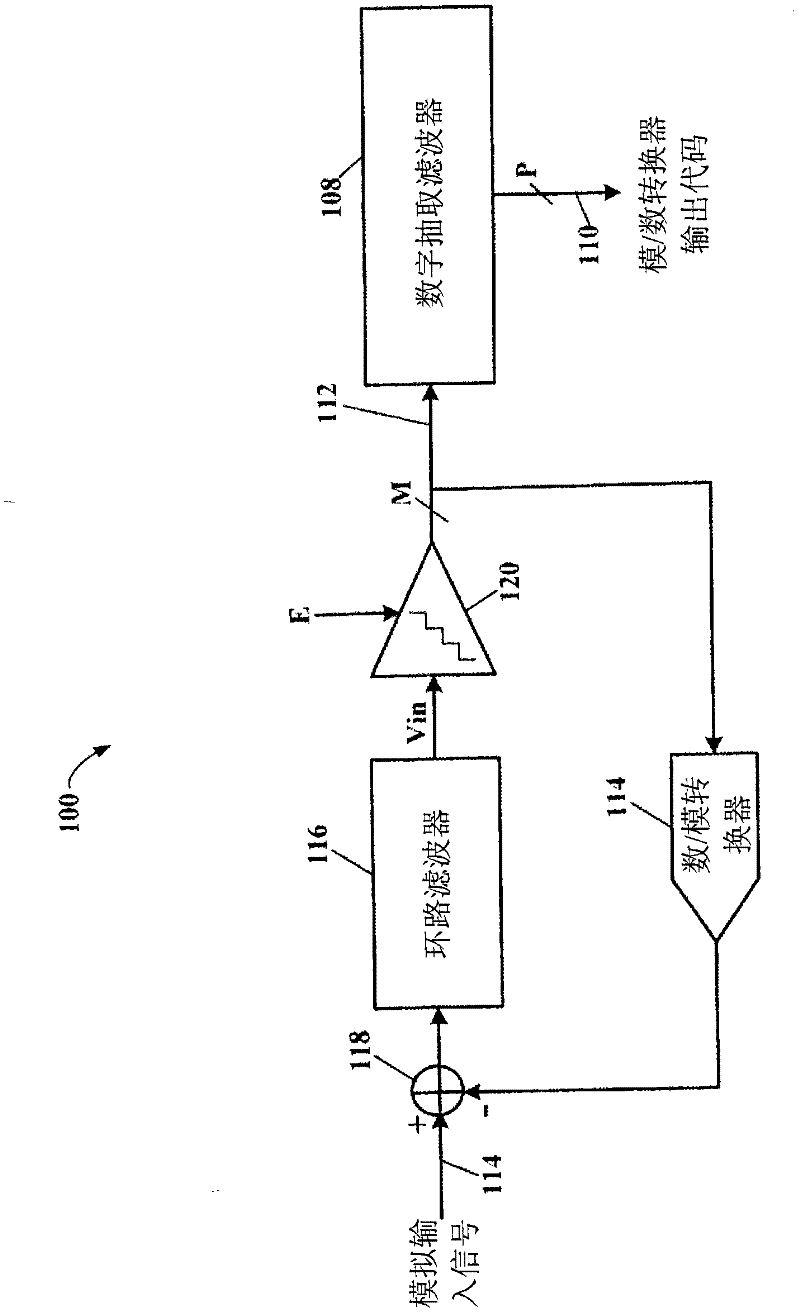

[0040] refer to figure 1 , which depicts a multi-bit or multi-level (nlev levels, nlev>2, M bits, M=Floor(log2(nlev)), M>1) single-loop sigma-delta analog / digital with a fixed quantizer Schematic block diagram of a converter (ADC). A multi-level (nlev) sigma-delta ADC (also called multi-bit, since encoding the levels requires more than 1 bit, M > 1) with a fixed quantizer, generally indicated by numeral 100, includes an input voltage summing node 118 , a loop filter 116 , a fixed multi-bit quantizer 120 , a multi-digit-to-analog converter (DAC) 114 and a digital decimation filter 108 .

[0041] Digital filter 108 receives sampled digital bitstream 112 and decimates digital bits...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More