Development board of network multi-core processor on test board based on four field programmable gate arrays (FPGA)

A multi-core processor, network-on-chip technology, applied in the direction of instruments, simulators, computer control, etc., can solve the problem that a single-chip FPGA development board cannot meet the requirements of hardware resources required for VLSI design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The development board designed by the present invention has two innovative points: one is that the imitation storage bandwidth is much larger than other multi-FPGA development boards, and the other is that the inter-chip communication throughput rate is super large.

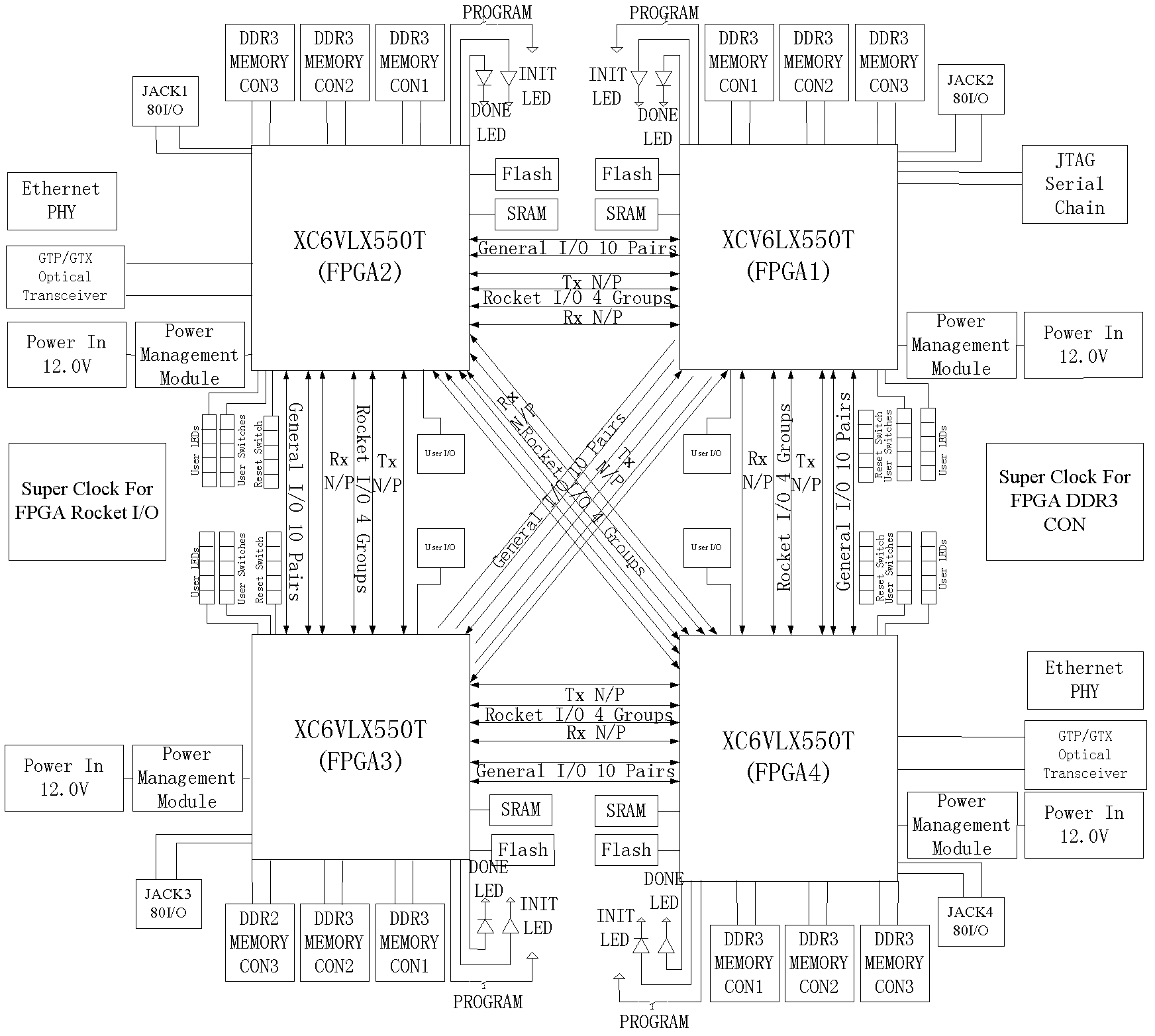

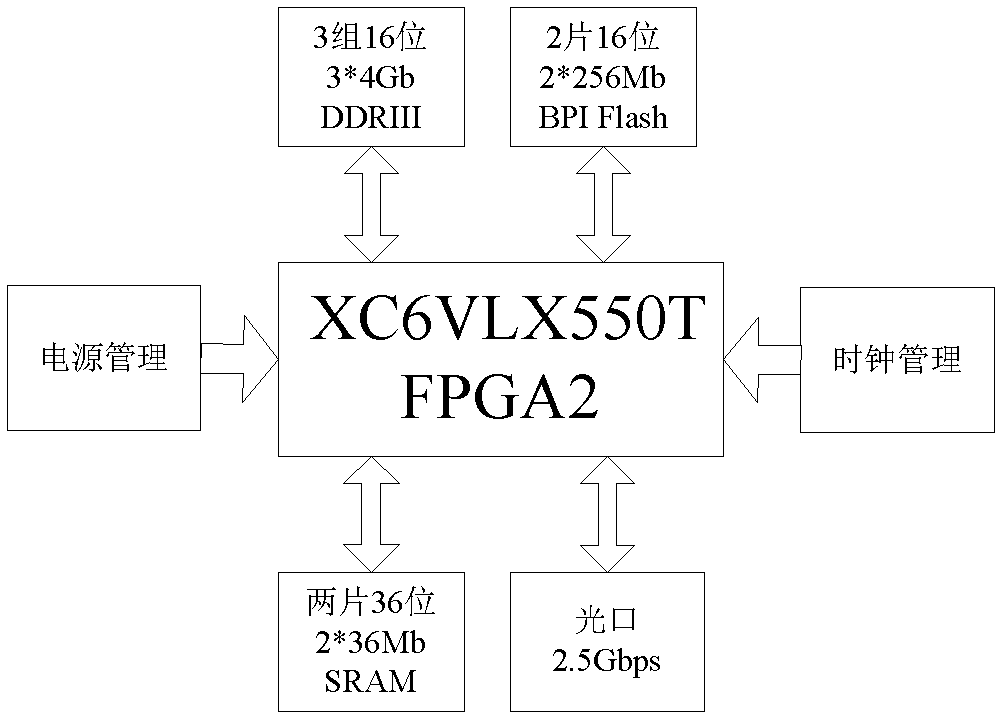

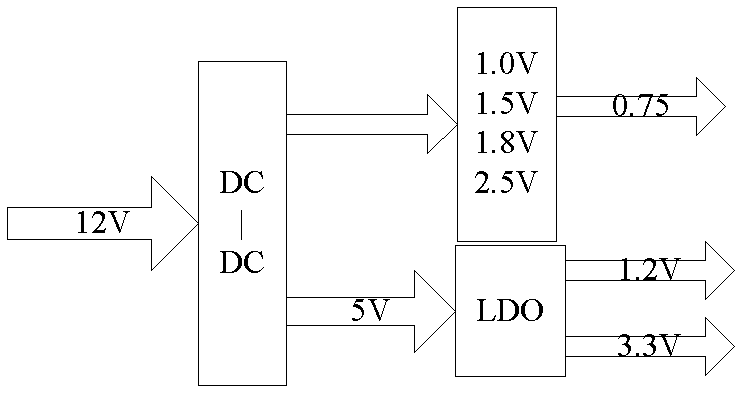

[0028] like figure 1 , there are 4 Xilinx XC6VLX550T chips (FF1759) on the motherboard of the present invention, and high-speed GTX input and output interfaces and common I / O are used to realize full interconnection between the chips, so as to realize the pipeline parallelism of NoC multi-core processor processing data. The name of the serial transceiver is different, the V4 period is called MGT, the early V5LXT / SXT is GTP, and the later V5FXT is called GTX. For the future versatility of the FPGA mainboard, the present invention adopts a fully interconnected structure, and each FPGA chip is provided with three large groups of GTX IO interfaces that are respectively connected to the corresponding GTX IO int...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More