Traversal test method of configurable logic block (CLB) of field programmable gate array (FPGA) based on look-up table structure

A technology of traversal testing and programming logic, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., to achieve the effects of reducing occupation, reducing configuration times, and good portability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

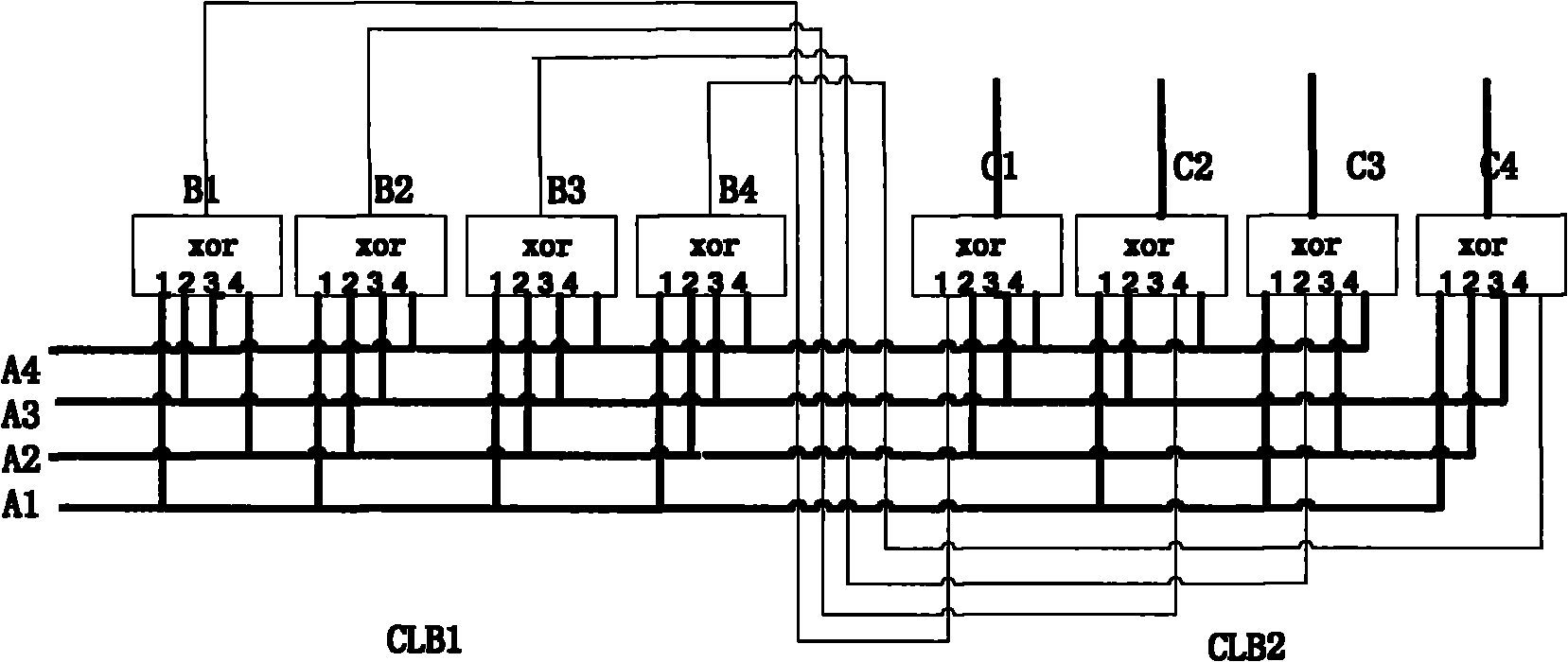

[0035] LUT single point fault traversal test scheme such as image 3 shown. Here, two CLBs are regarded as a repeatable cell, and A1, A2, A3, and A4 come from the IO port or the output of the previous cell. Each LUT is configured as XOR, so that B1, B2, B3, and B4 are all equal to A1@A2@A3@A4; C1=B1@A2@A3@A4=A1, C2=A2, C3=A3, C4= A4. It can be seen that the output of each cell is equal to the input. In this way, as long as the 8 LUTs in a cell are fully tested, the entire row of CLBs can be fully tested. We can achieve the purpose of traversing each memory cell of each LUT in the first CLB by adding a pseudo-depletion test stimulus (0000 to 1111) to the 4 input terminals of the first CLB. For the second CLB, though, the input is no longer {A1, A2, A3, A4}, but three of these four and A1@A2@A3@A4. But obviously it is also traversed from 0000 to 1111, but the order has changed. In the second configuration, replace the XOR with the same OR. At the same time, due to the two...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More