Security RAM block with multiple partitions

An area, memory block technology used in instrumentation, preventing unauthorized use of memory, computing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

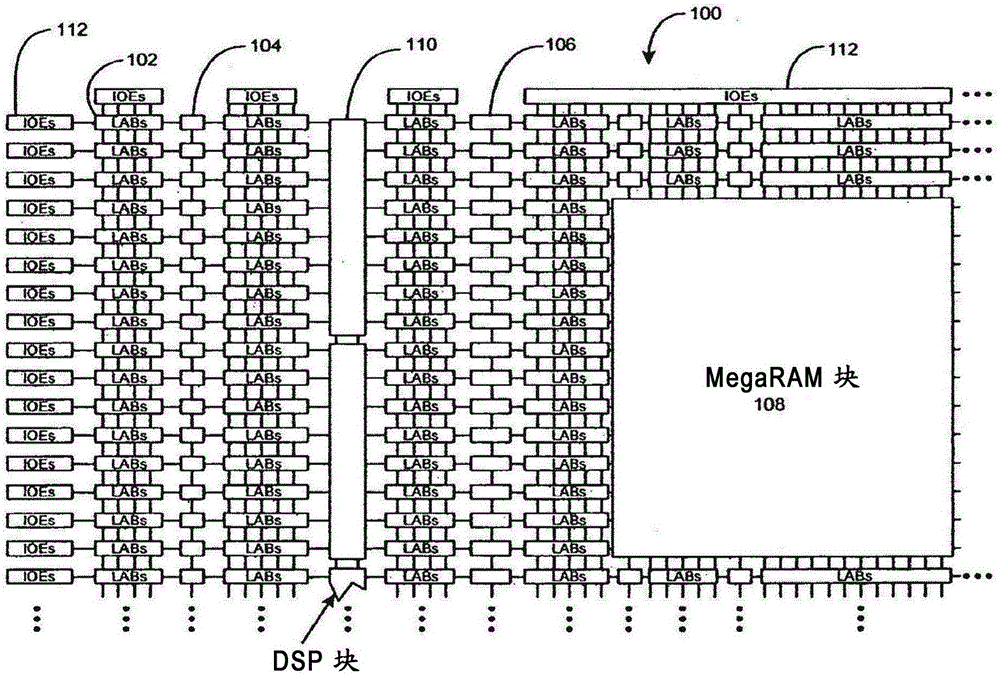

[0041] figure 1 is a simplified partial block diagram of an exemplary high density programmable logic device 100 in which techniques according to the present invention may be used. PLD 100 includes a two-dimensional array of programmable logic array blocks (LABs) 102 interconnected by a network of variable length and speed row and column interconnects. LAB 102 includes a number (eg, 10) of logic elements (LEs), which are small logic units that provide efficient implementation of user-defined logic functions.

[0042] PLD 100 also includes a distributed memory structure that includes variable sized RAM blocks provided throughout the array. The RAM blocks include, for example, a 512-bit block 104, a 4K block 106, and an M-block 108 providing 512K bits of RAM. These memory blocks may also include shift registers and FIFO buffers. The PLD 100 also includes a digital signal processing (DPS) block 110 that may implement, for example, a multiplier with addition and subtraction fe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More