Method using FPGA (field programmable gate array) for controlling DSP (digital signal processor) program load running

A program loading and program technology, applied in program loading/starting, program control in sequence/logic controllers, program control devices, etc., can solve problems such as troublesome, inflexible, and system reliability reduction in volume-sensitive occasions, and achieve The effect of simple circuit design and debugging, high flexibility and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

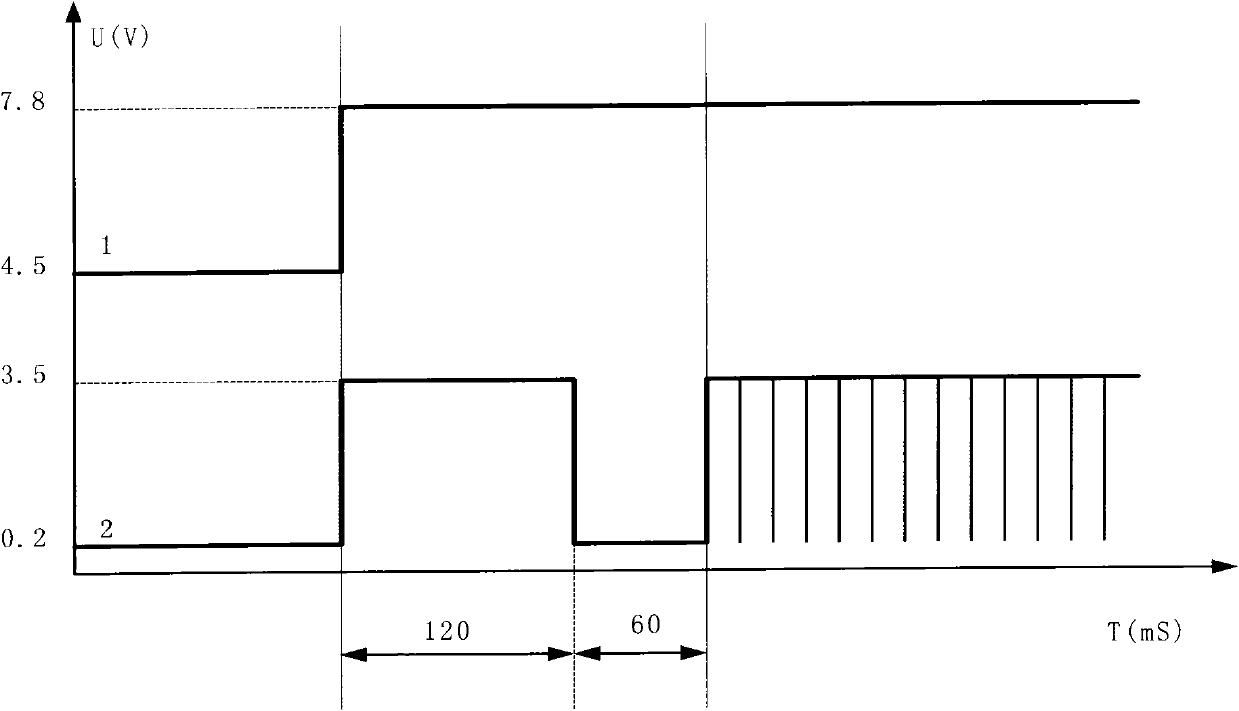

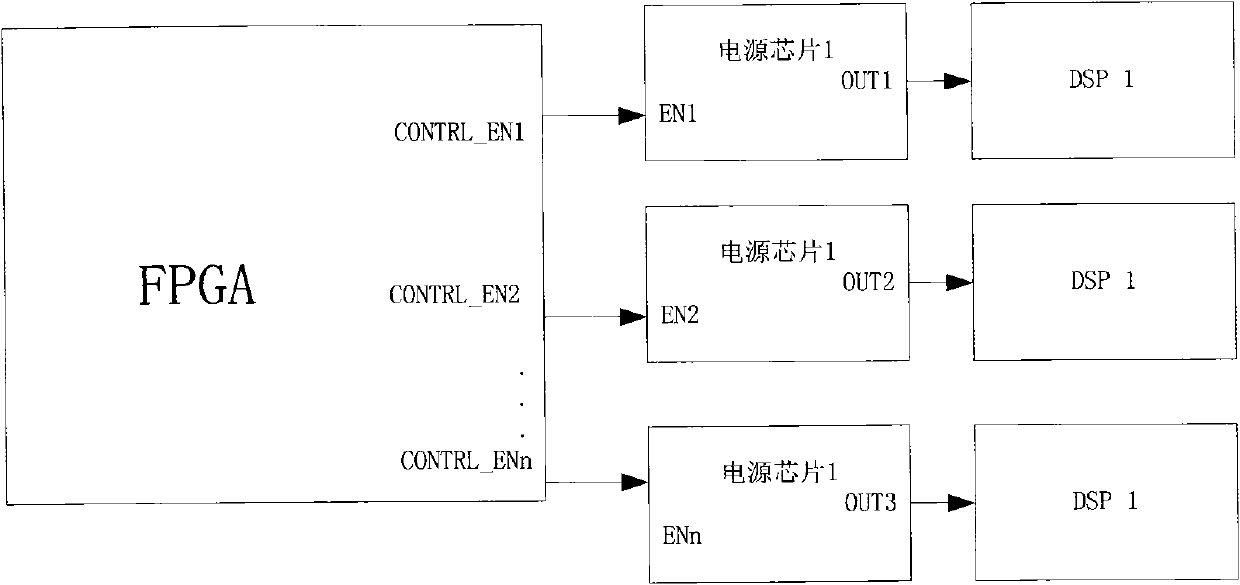

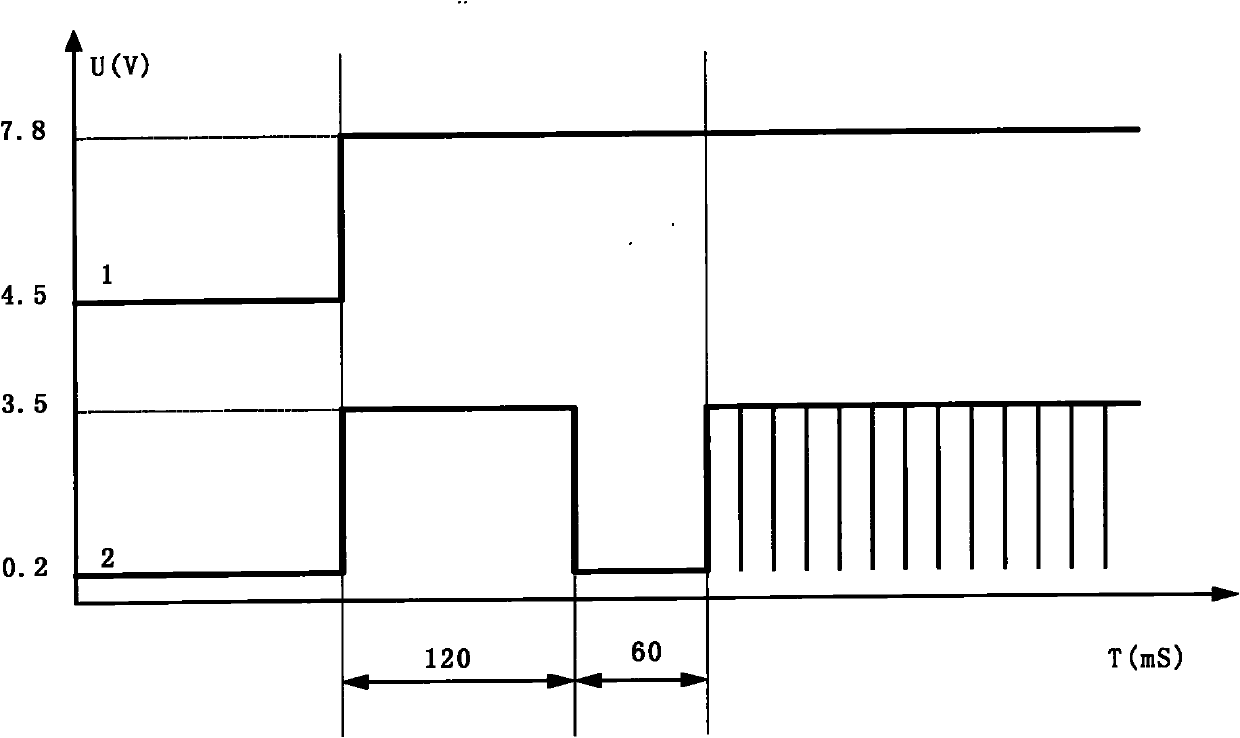

[0022] The invention is as follows: a certain IO pin of FPGA is connected to the control terminal of the power chip of DSP, and is used for controlling the output of the power chip. The control terminal of the power chip can only output current when it is at a high level, and is prohibited from outputting at a low level.

[0023] see figure 1 As shown in the curve 1 in the middle, the IO pin output of the FPGA is fixed at a high level when the device is powered on, which is its inherent characteristic and is not affected by other factors. Only after the FPGA is loaded, the low level can be output through program control. Only at this time can the power supply chip of the DSP output current, and then the DSP can start program loading. At this time, the FPGA has already been loaded and is in a standby state, and the DSP cannot affect its loading. See details figure 1 Shown in curve 2.

[0024] Concrete process of the present invention is:

[0025] 1] When designing the cir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More