BLOCK RAM (Random Access Memory) cascade structure of field programmable gate array FPGA

A cascade structure, SRAM18K technology, applied in the direction of instrumentation, electrical digital data processing, etc., can solve the problem of occupying programmable logic device wiring and logic resources, etc., to save peripheral wiring resources, small sequence loss, and improve the routing rate Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The embodiments listed in the present invention are only used to help understand the present invention, and should not be interpreted as limiting the protection scope of the present invention. For those of ordinary skill in the art, they can also Improvements and modifications are made to the present invention, and these improvements and modifications also fall within the protection scope of the claims of the present invention.

[0033] In order to realize the memory unit RAM with the required address depth and data width, the software algorithm is simplified and the peripheral wiring resources are saved. The invention proposes a BLOCKRAM cascade structure of field programmable device FPGA.

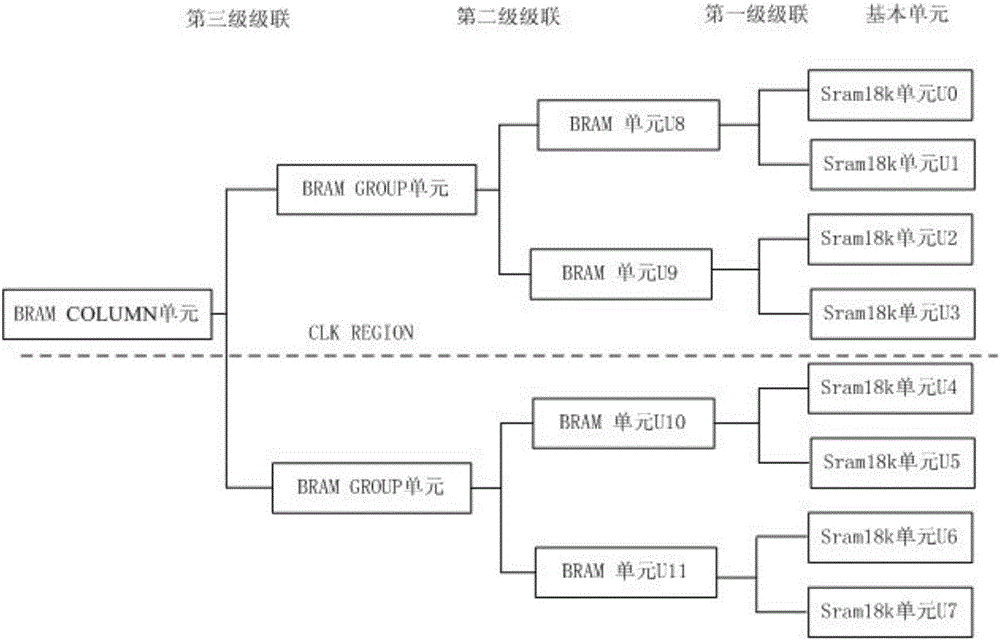

[0034] like figure 1As shown, it is the cascade structure supported by the 144KBLOCKRAM inside the field programmable device FPGA. It is described with 4 BLOCKRAM units U8, U9, U10, and U11 as an example, that is, there are 8 SRAM18K units U0, U1, U2, U3, U4, U5, U6, U7. The cas...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More