User register state capture circuit adopting single-event hardened FPGA (field programmable gate array)

A single-particle reinforcement and register technology, applied in static memory, digital memory information, instruments, etc., can solve problems such as short circuit or open circuit of interconnection lines, inability to know the user's logic state, and partial circuit function errors, achieving wide applicability, reducing The effect of the cumulative effect of single-event flipping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

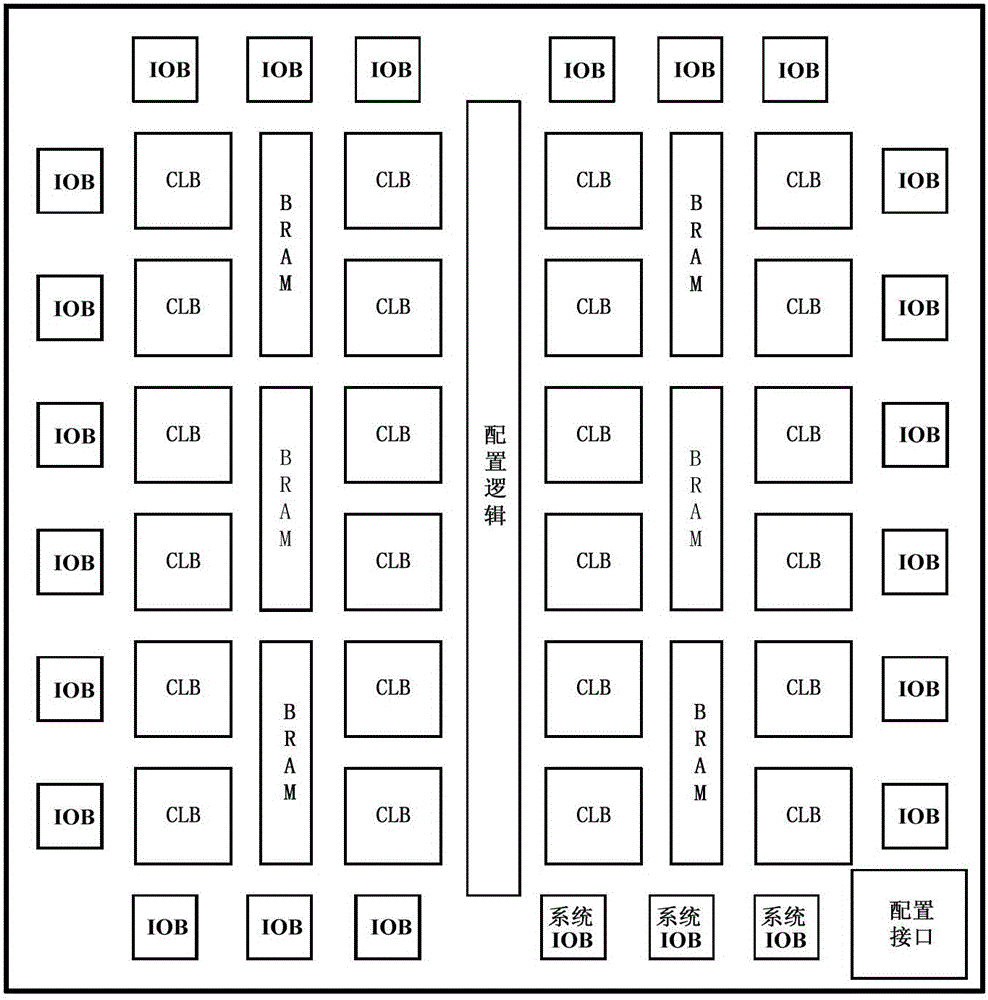

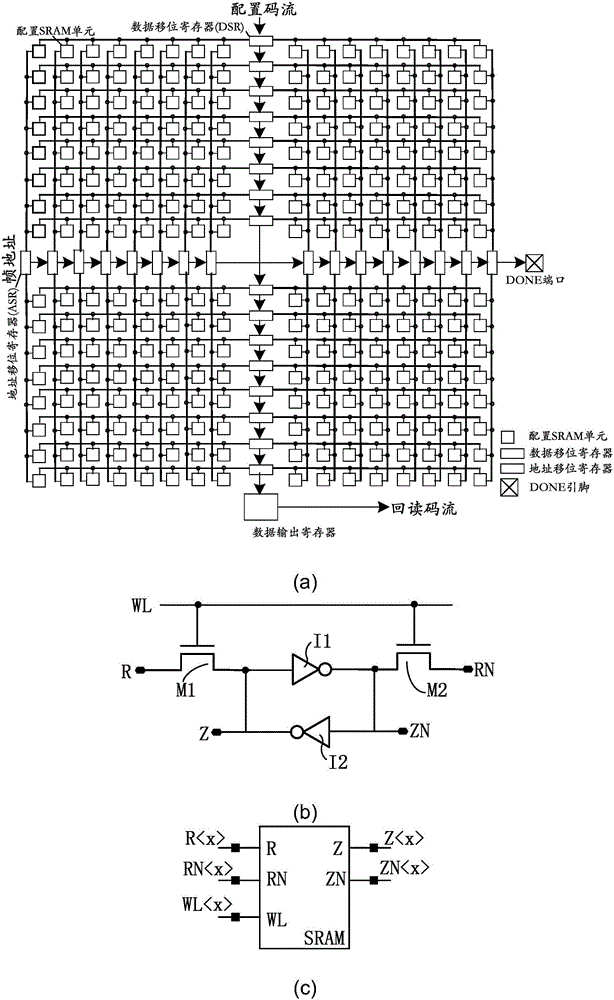

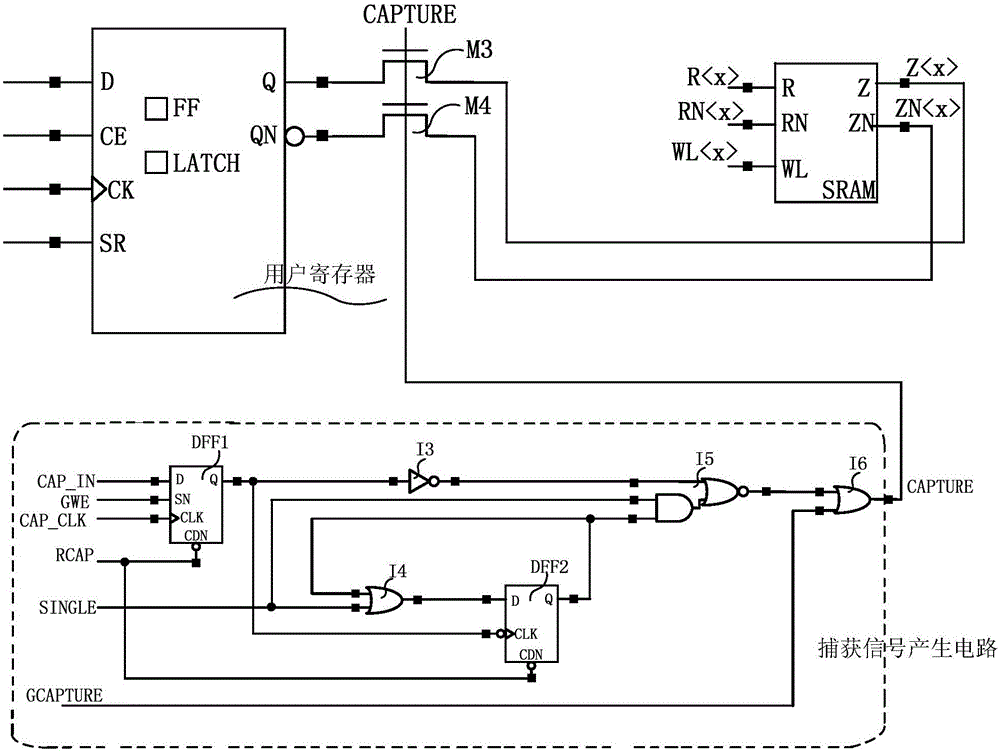

[0031] The SRAM FPGA chip completes the configuration by loading the specified configuration data into the internal configuration memory array (CSRAM), which contains a large number of SRAM storage cells. Such as figure 2 (b) shows the SRAM memory cell circuit, which includes two inverters I1, I2 and two transistors M1 and M2. The output of each inverter is connected to the input of the other inverter to form an interlock Structure, the source terminal of the transistor M1 is connected to the configuration data input signal R, the drain terminal is connected to the input terminal of the inverter I1, the gate terminal is controlled by the address decoding signal WL, and the source terminal of the transistor M2 is opposite to the configuration data input signal R The phase signal RN is connected, the drain terminal is connected to the input terminal of the inverter I2, the gate terminal is controlled by the address decoding signal WL, the output terminal of the inverter I2 is Z, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More