System and method for collaborative power management of FPGA (field programmable gata array) chip and BMC (baseboard management controller) chip used on ATCA (advanced telecom computing architecture) blade

A power management system and BMC chip technology, applied in the computer field, can solve problems such as chip damage and achieve simple troubleshooting

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be described in further detail below in conjunction with the accompanying drawings.

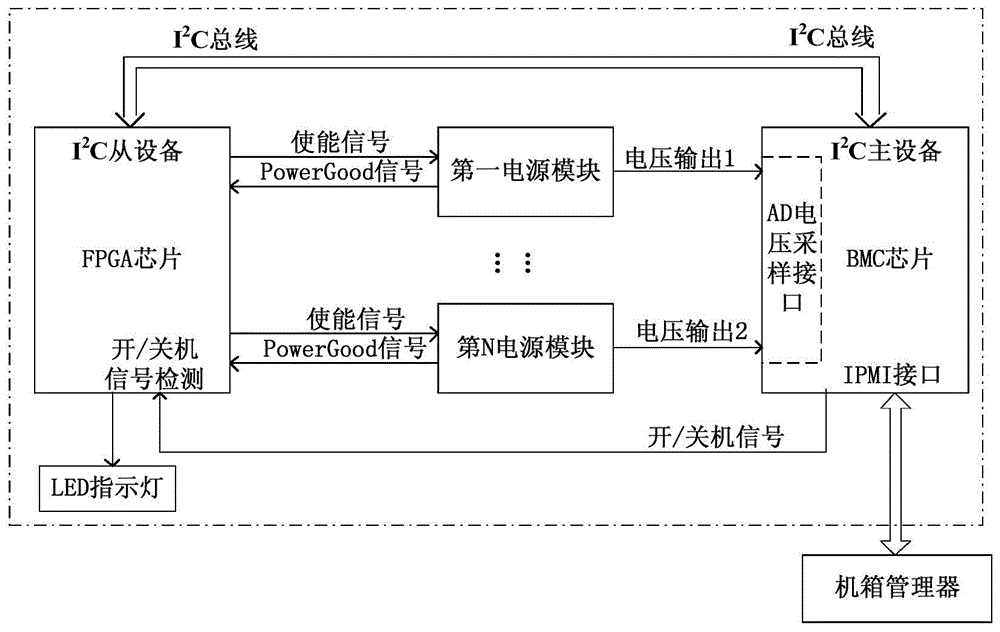

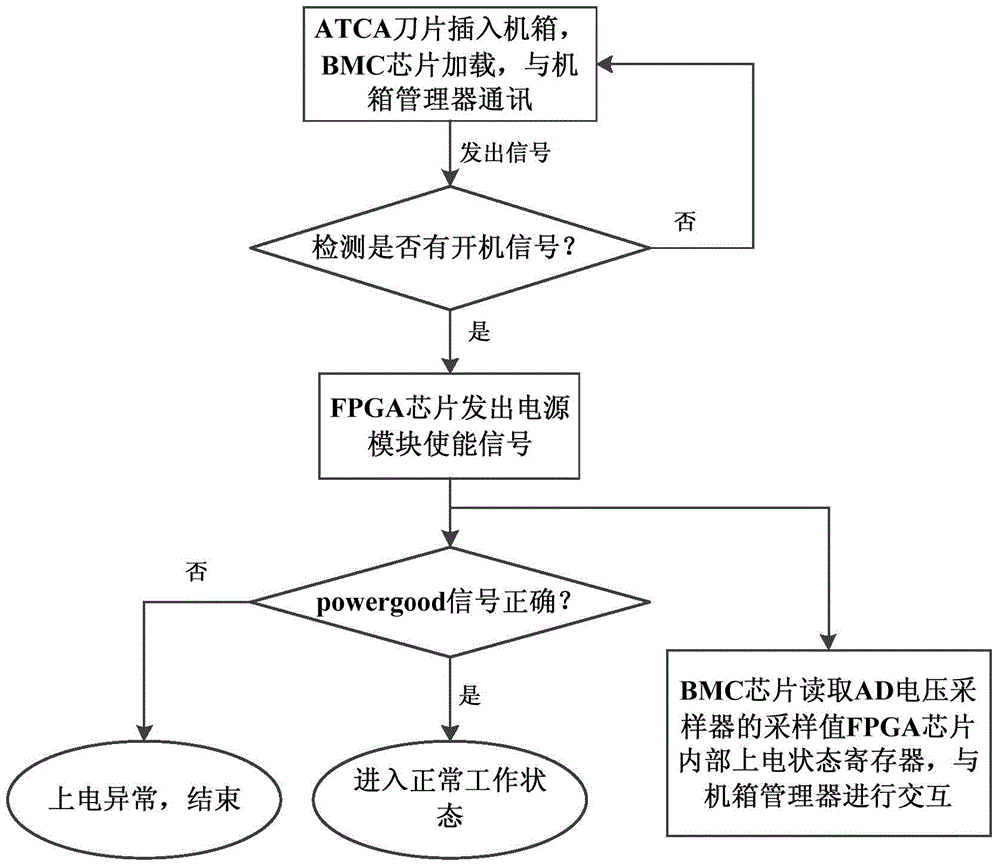

[0028] Such as figure 1 , the present invention provides a cooperative power management system for an FPGA chip on an ATCA (Advanced Telecom Computing Architecture) blade and a BMC (Baseboard Management Controller) chip, the system includes an FPGA chip, a BMC chip, N power modules and chassis management device; the enabling pins and Power Good pins of N power supply modules are respectively connected to the IO pins of the FPGA chip, and the output ends of the N power supply modules are all connected to the AD sampling interface of the BMC chip, and the FPGA The chip communicates with the BMC chip through the I2C bus; the chassis manager is bidirectionally connected with the BMC chip.

[0029] The BMC chip and the FPGA chip are respectively an I2C master device and an I2C slave device, and the BMC chip accesses a power-on state register inside the FPGA chip ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More