System and method for coordinating power management of fpga chip and bmc chip on atca blade

A power management system, BMC chip technology, applied in the computer field, can solve problems such as chip damage, and achieve the effect of simple troubleshooting

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be described in further detail below in conjunction with the accompanying drawings.

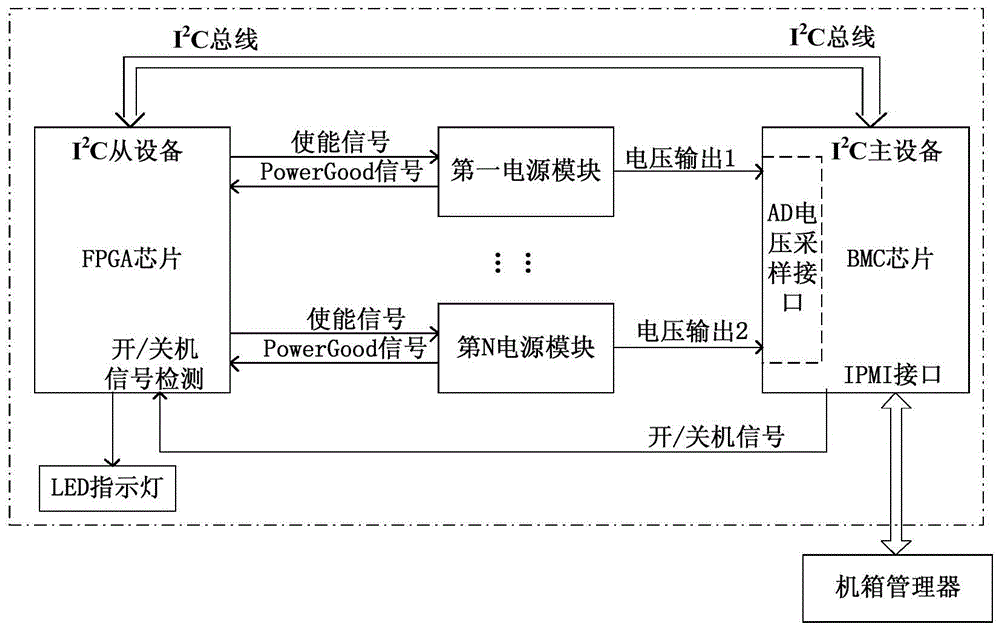

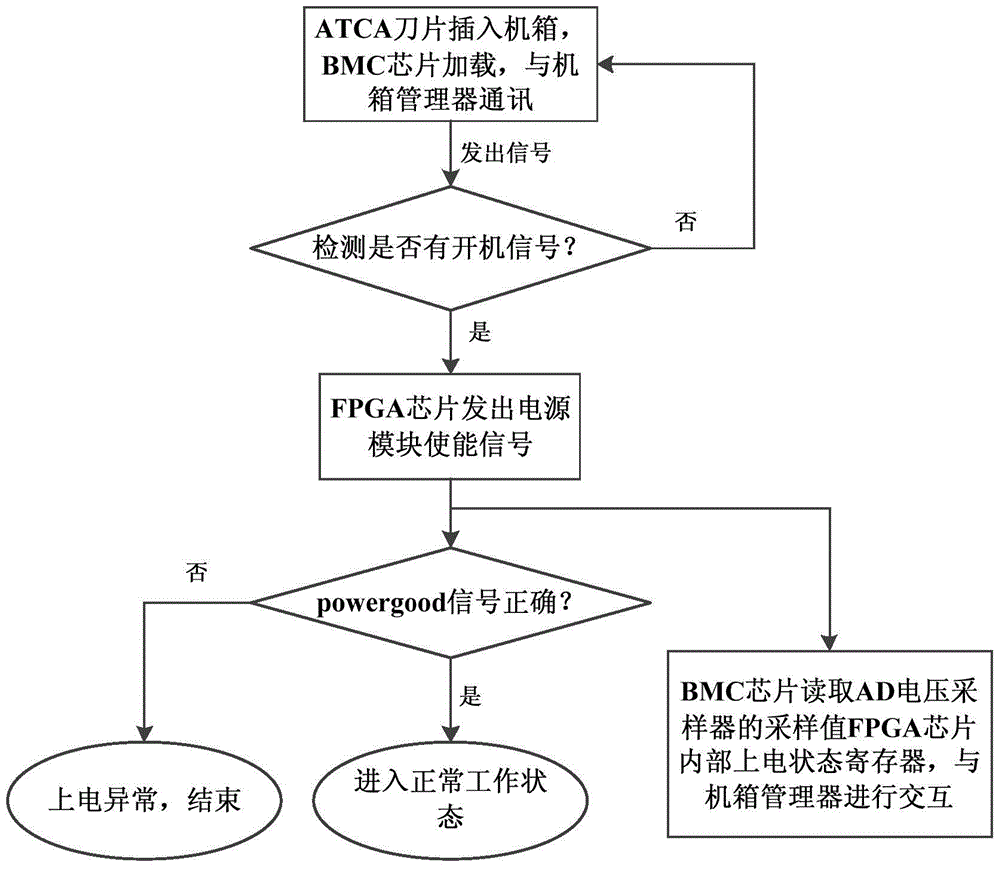

[0028] like figure 1 , the present invention provides a cooperative power management system for an FPGA chip on an ATCA (Advanced Telecom Computing Architecture) blade and a BMC (Baseboard Management Controller) chip, the system includes an FPGA chip, a BMC chip, N power modules and chassis management device; the enabling pins and PowerGood pins of N power modules are respectively connected to the IO pins of the FPGA chip, and the output ends of the N power modules are all connected to the AD sampling interface of the BMC chip, and the FPGA chip Communicate with the BMC chip through the I2C bus; the chassis manager is bidirectionally connected with the BMC chip.

[0029] The BMC chip and the FPGA chip are respectively an I2C master device and an I2C slave device, and the BMC chip accesses a power-on state register inside the FPGA chip through the I2C bus.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More