Chip testing system and method based on field programmable gata array (fpga)

A chip testing and chip technology, applied in printed circuit testing, electronic circuit testing, etc., can solve the problems of increasing chip testability, expensive experimental equipment, and unrealistic testing, and achieve the effect of meeting chip testing requirements and short compilation time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

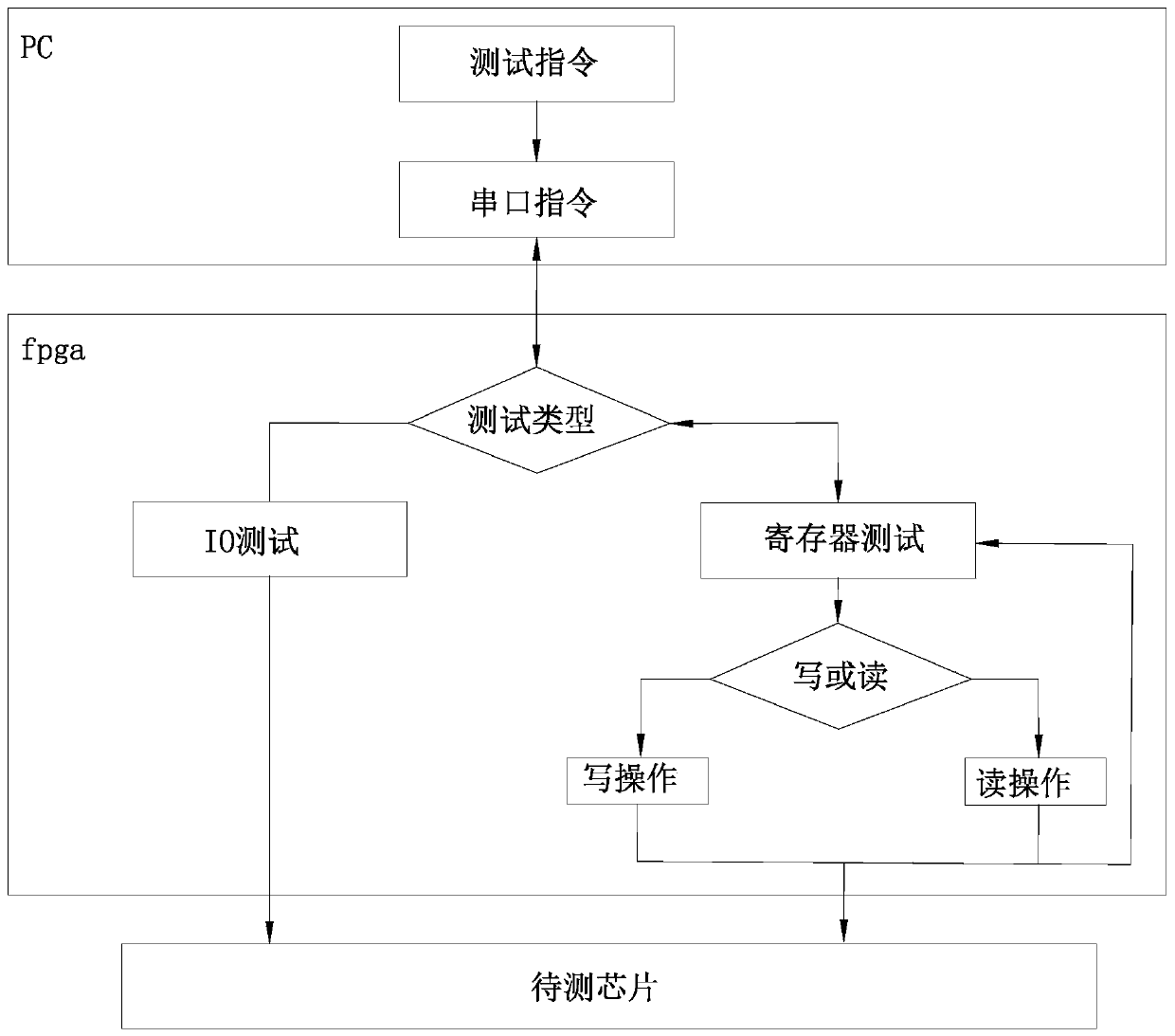

[0033] see figure 1 As shown, a fpga-based chip testing system is disclosed.

[0034] The system includes a PC terminal and an FPGA connected by communication.

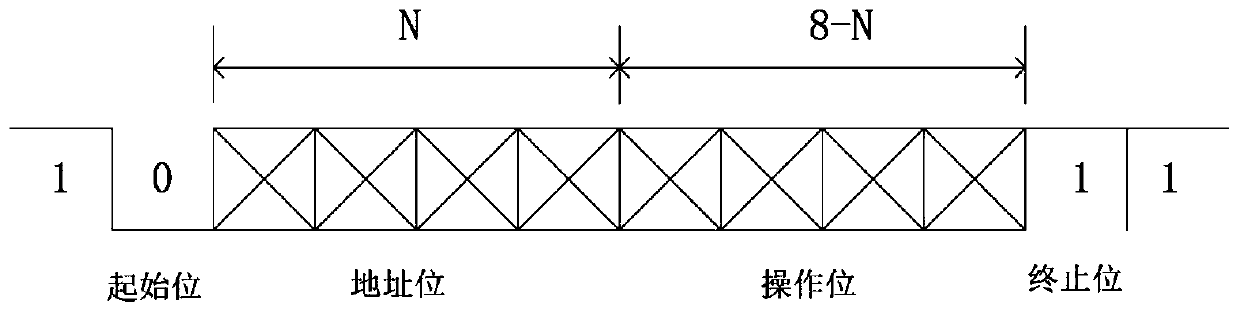

[0035] The PC end is used for applying test stimulus instructions, and sending the test stimulus instructions to the fpga through a serial port tool. The test stimulus may include pull-up and pull-down operations on the chip IO, register read and write operations.

[0036] The fpga is used to receive the test stimulus instruction sent by the serial port tool, analyze the test stimulus instruction and send it to the chip to be tested, collect the test response information of the chip to be tested, and send the test response information to the PC.

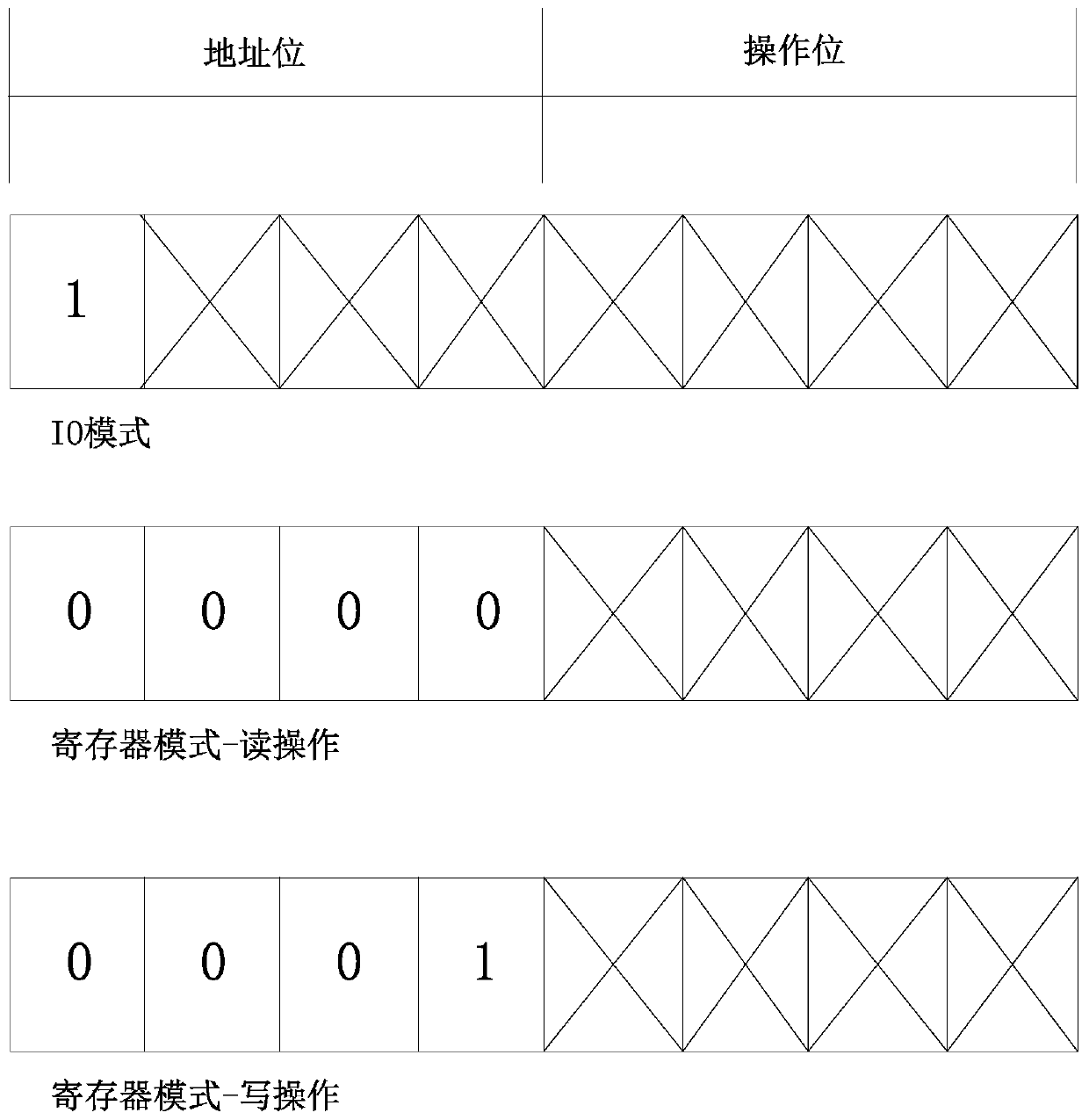

[0037] The fpga, when parsing the test incentive instructions, can determine whether the test type is an IO test or a register test, the IO test includes the configuration of the chip test mode and the pull-up and pull-down operations of the chip IO, and the register test ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More