Loading method and device for FPGA (field programmable gate array) logic editions

A version and logic technology, applied in the field of FPGA logic version loading, to achieve the effect of improving forwarding performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

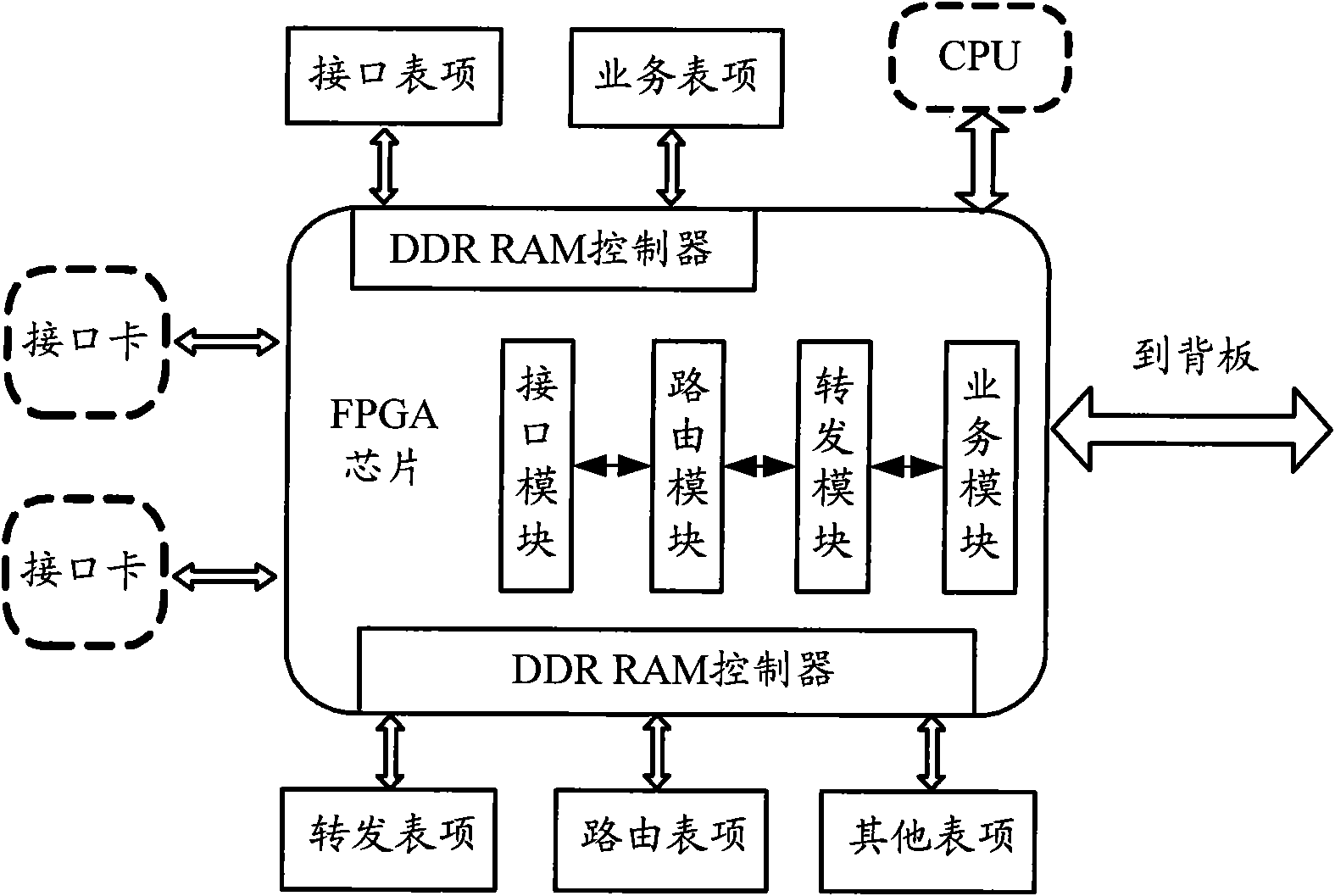

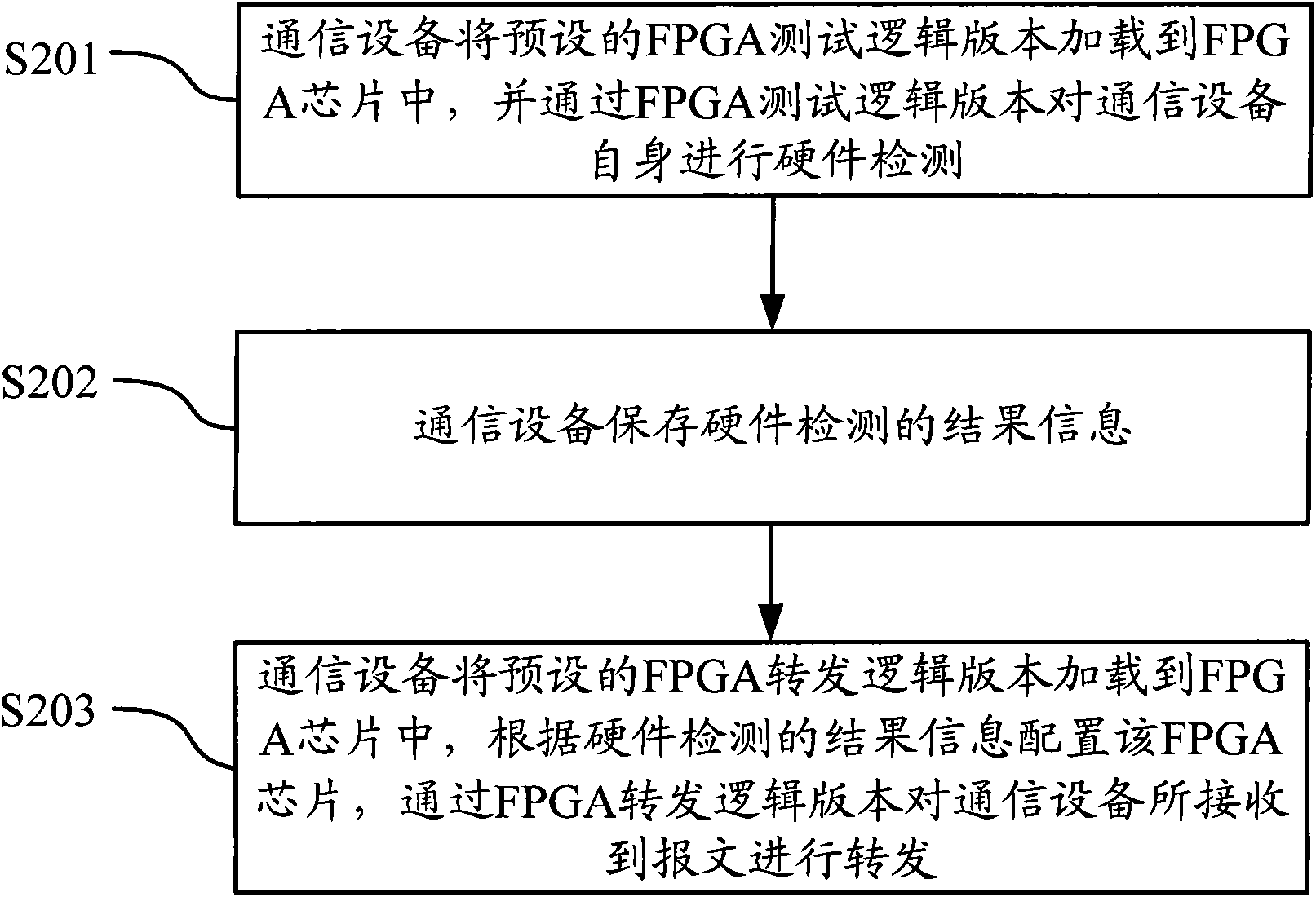

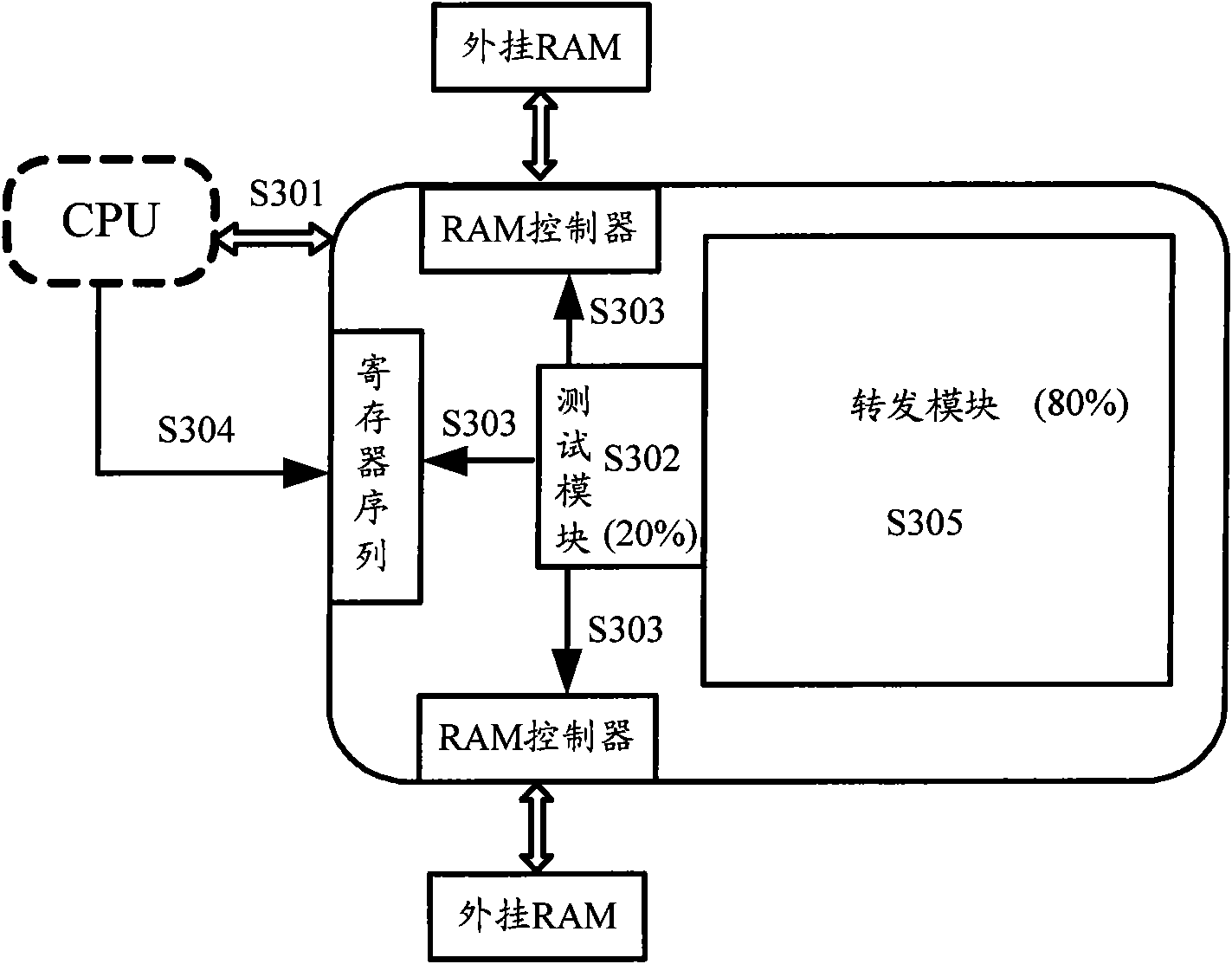

[0059] As described in the background technology, in the loading strategy of the FPGA logic version of the FPGA chip in the existing communication equipment, it is necessary to load all the FPGA logic versions into the FPGA chip at one time, but in fact, in the FPGA logic version, except for forwarding In addition to the content corresponding to the necessary functions such as business, it also includes a part of the content corresponding to the functions that must exist in the logic but only need to be executed once. Such functions include FPGA chip self-test, DDR (Double Data Rate, double Speed) RAM (Random Access Memory, random access memory) self-test, DDR Training (training), etc., these functions will not be executed after the system is started once, but the corresponding content is fixed in the FPGA chip Occupying a part of space resources undoubtedly causes a waste of limited space resources of the FPGA chip.

[0060] For the convenience of description, in the followin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More