Field-programmable gate array (FPGA) configuration device and configuration method

A configuration device and configuration method technology, applied in the direction of program control devices, CAD circuit design, special data processing applications, etc., can solve the problems of limited capacity, high price, slow speed, etc., and achieve the effect of saving costs and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

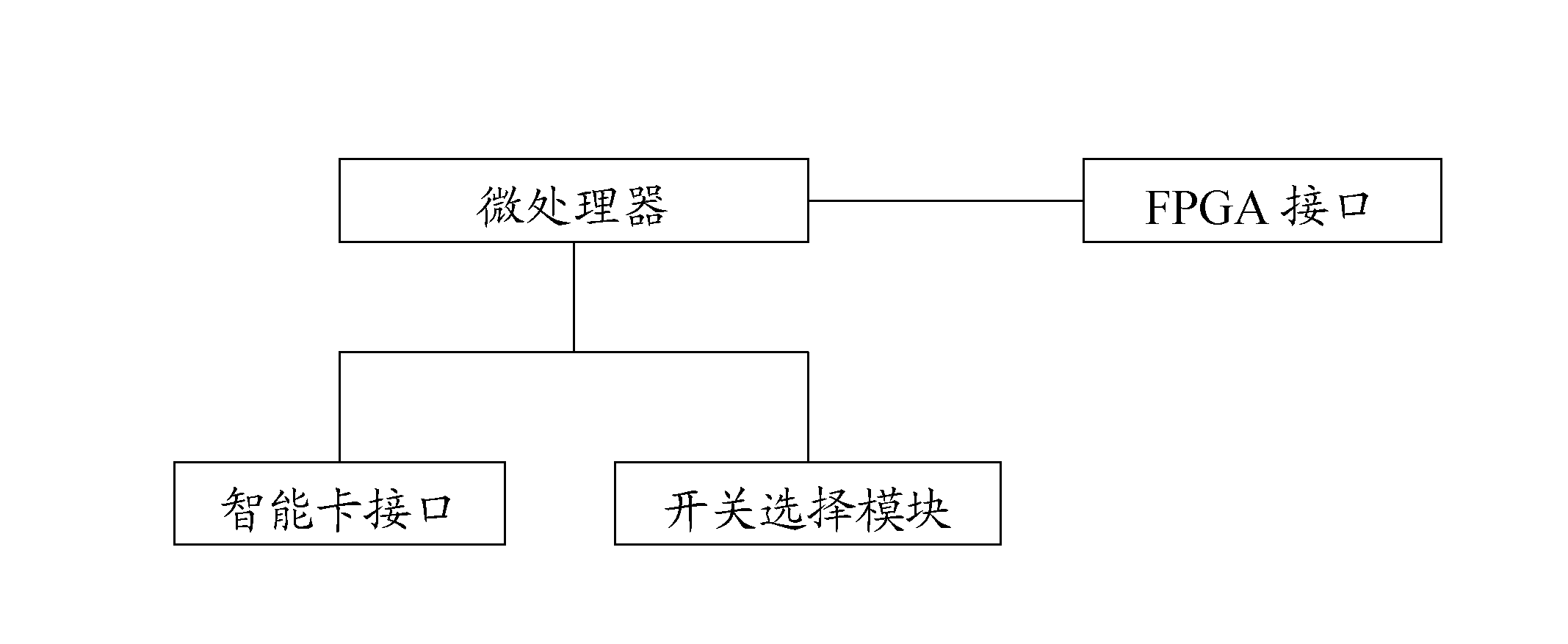

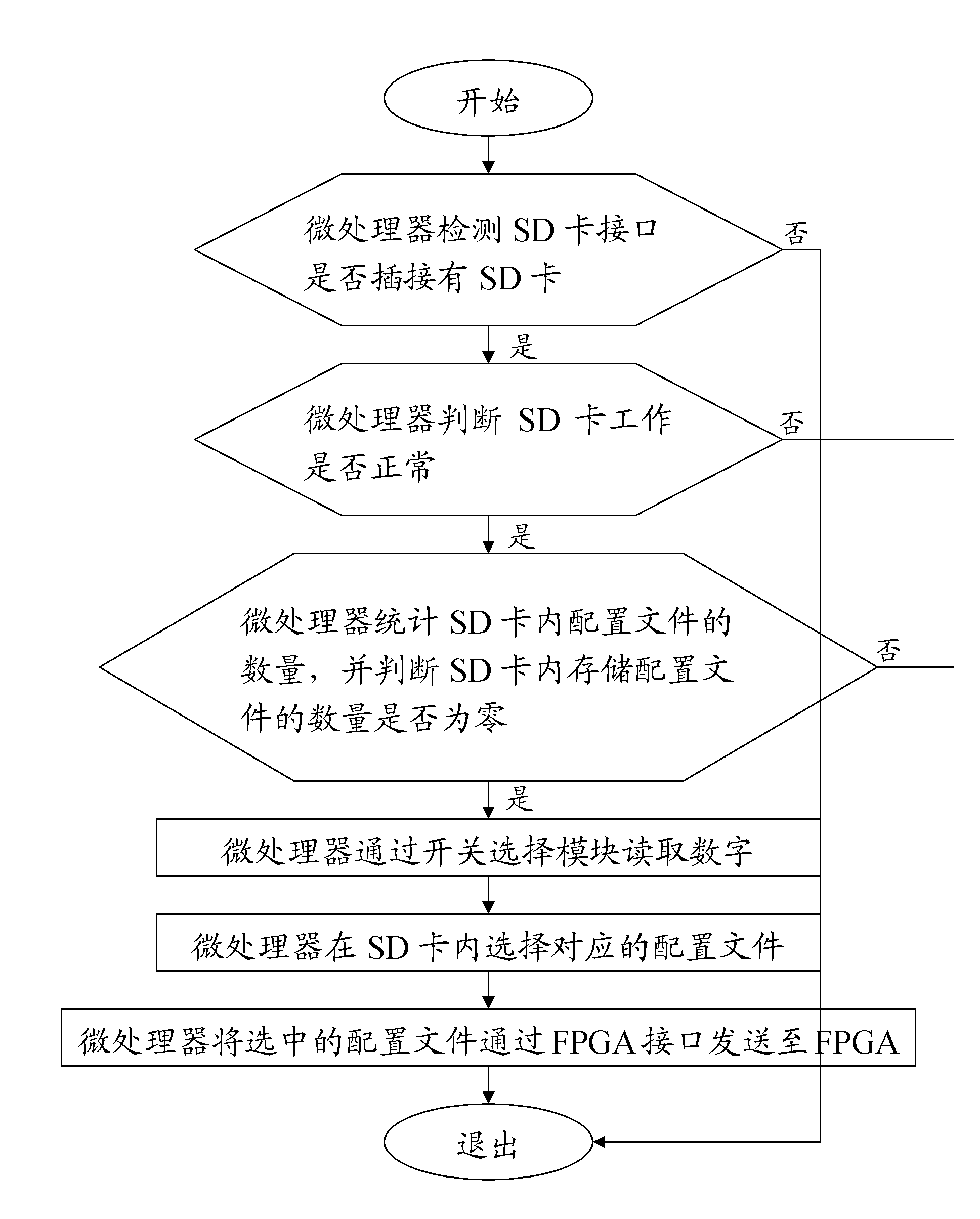

[0016] see figure 1 A preferred embodiment of the FPGA configuration device of the present invention includes a microprocessor, an FPGA interface connected to the microprocessor, a smart card interface connected to the microprocessor, and a switch selection module connected to the microprocessor. In this embodiment, the smart card interface is an SD card (Secure Digital Memory Card, secure digital card) interface.

[0017] The SD card interface is used to insert an SD card, and the microprocessor uses the SPI (Serial Peripheral Interface, Serial Peripheral Interface) bus system mode to transmit data with the SD card through the SD card interface. Compatible with a full range of SD cards, and compatible with standard SD card readers, that is, standard SD card readers can be used to copy in configuration files; the switch selection module is used to read the number input by the user, the microprocessor According to the number read by the switch selection module, the configurati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More