Field programmable gate array loading method

A gate array and programming logic technology, applied in program control devices, instruments, electrical digital data processing, etc., can solve the problems affecting the system startup speed, long chip selection effective time, long loading time, etc., to reduce fault recovery time, Reduce startup time, improve product performance and metrics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

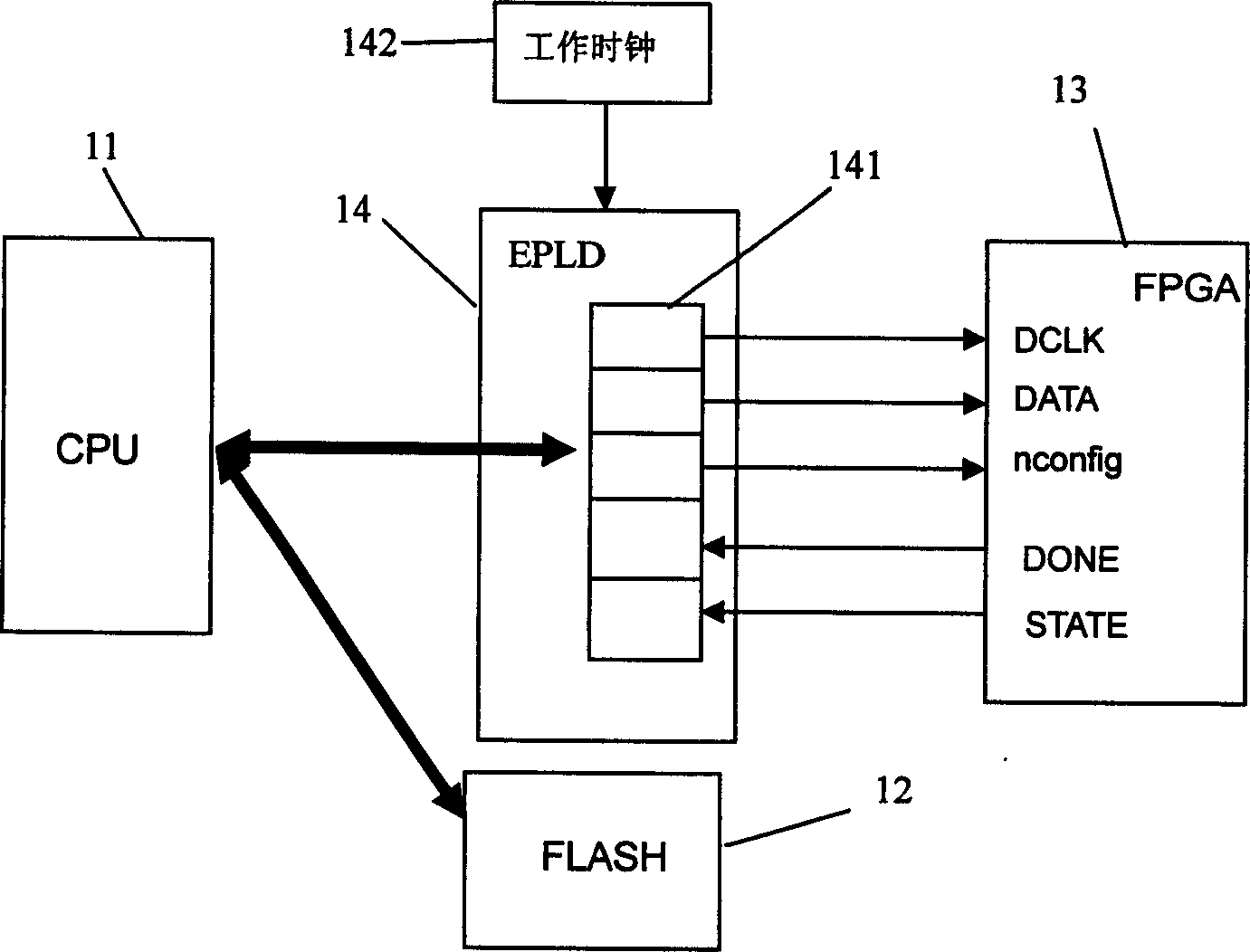

[0031] see Figure 4 to Figure 6 , is a preferred embodiment of the loading method of the field programmable gate array of the present invention, first as follows Figure 4 An erasable programmable logic device EPLD14 is provided between the CPU 11 and the field programmable array FPGA 13 . The CPU 11 is connected to the EPLD 14 and the FLASH 12 through a bus, so that the files to be loaded stored in the FLASH 12 can be quickly loaded into the FPGA 13 through the EPLD 14. The EPLD 14 is provided with a control register 31 , an 8-bit load data register 32 and a clock output logic 33 , and an external operating clock 142 is added to the EPLD 14 . The control register 31 is connected with the control signal pins (nCONFIG, DONE, STATE) of the FPGA13, the load data register 32 is connected with the data input pin of the FPGA13, and the clock output logic 33 is connected with the clock input pin of the FPGA13. connect.

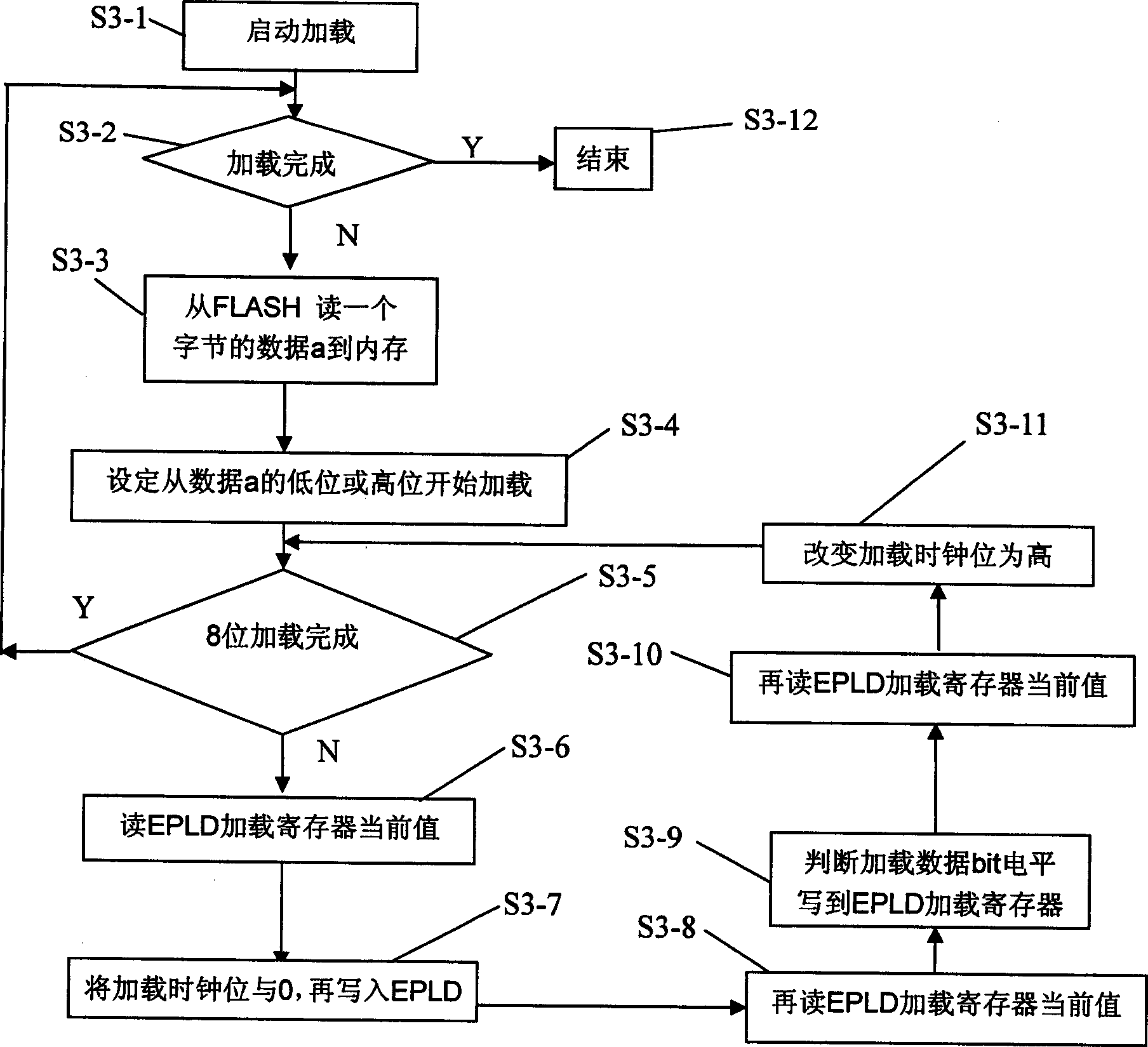

[0032] like Figure 5 As shown, when the loading needs to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More