Patents

Literature

92results about How to "Write less" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System and method for generating Web Service architectures using a Web Services structured methodology

ActiveUS7698398B1SOAP messaging reliableReduce effortMultiple digital computer combinationsOffice automationEnterprise integrationDesign pattern

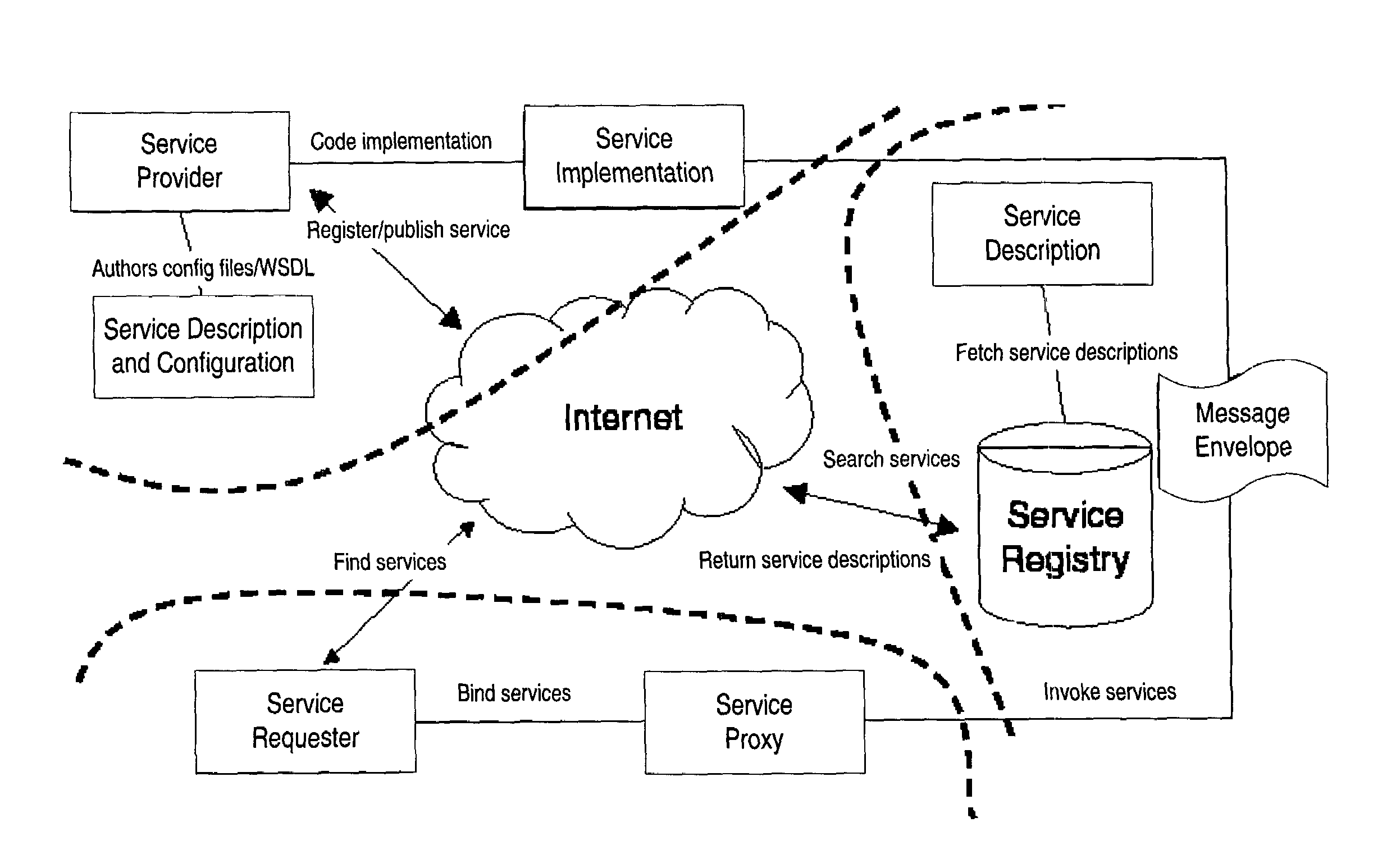

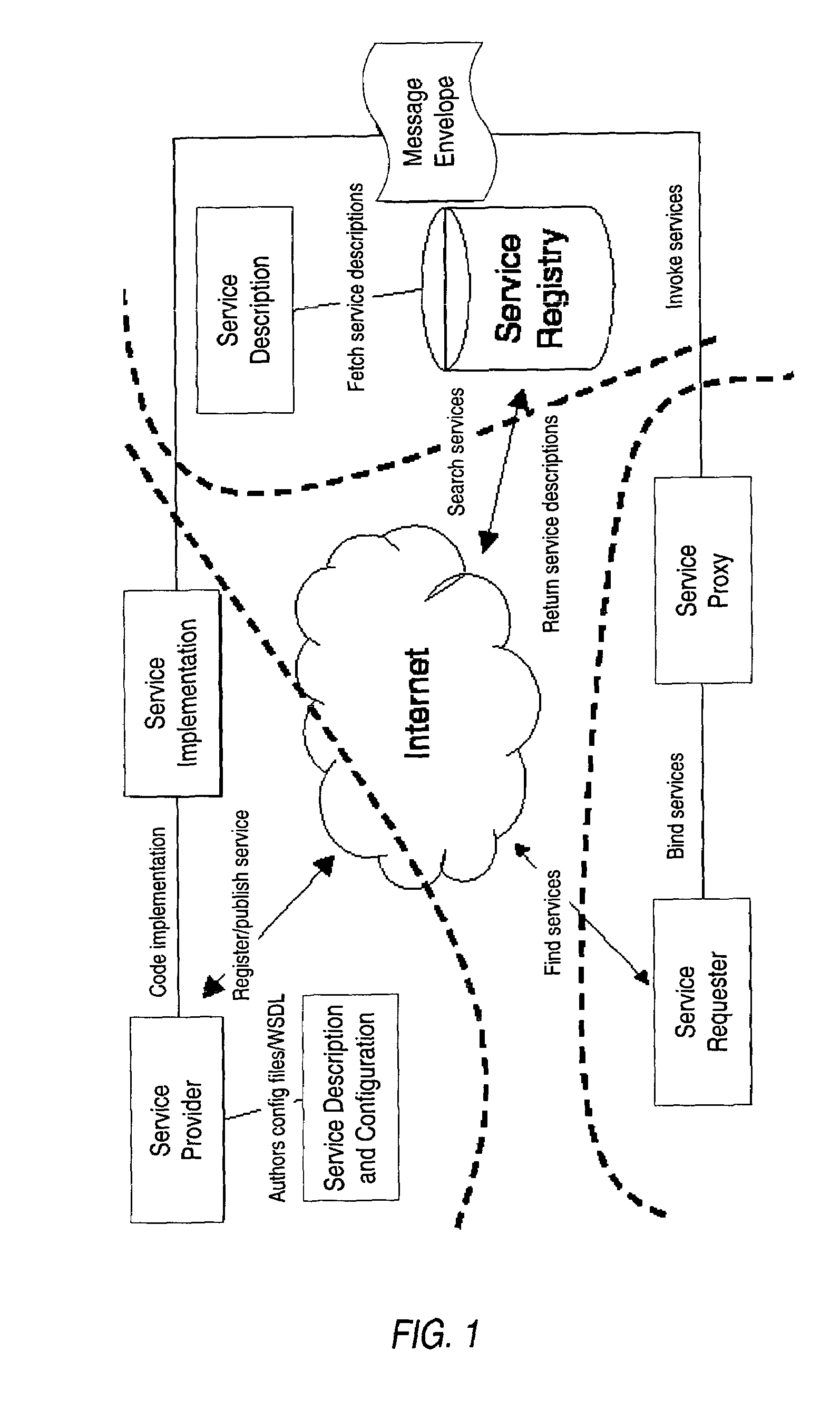

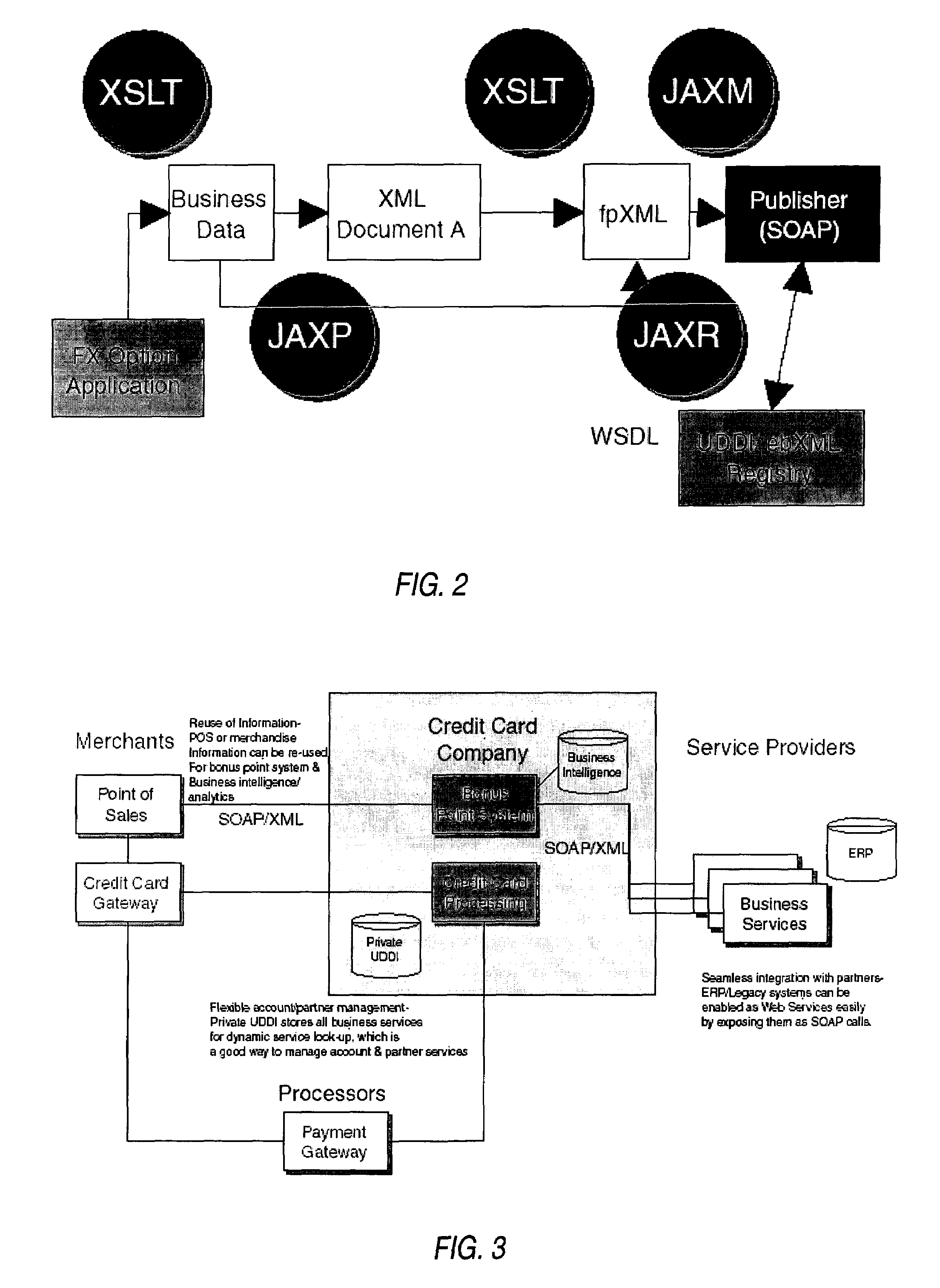

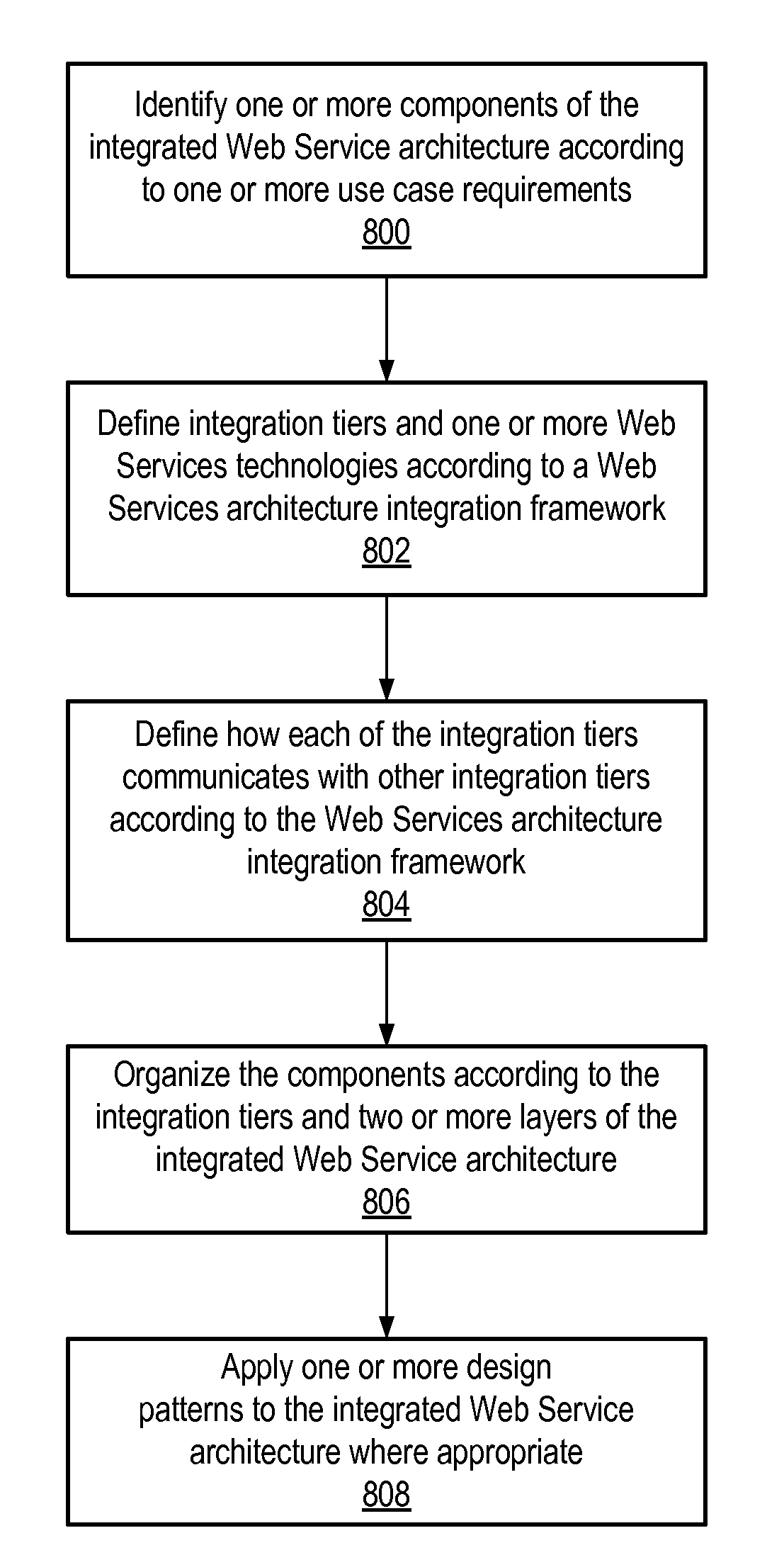

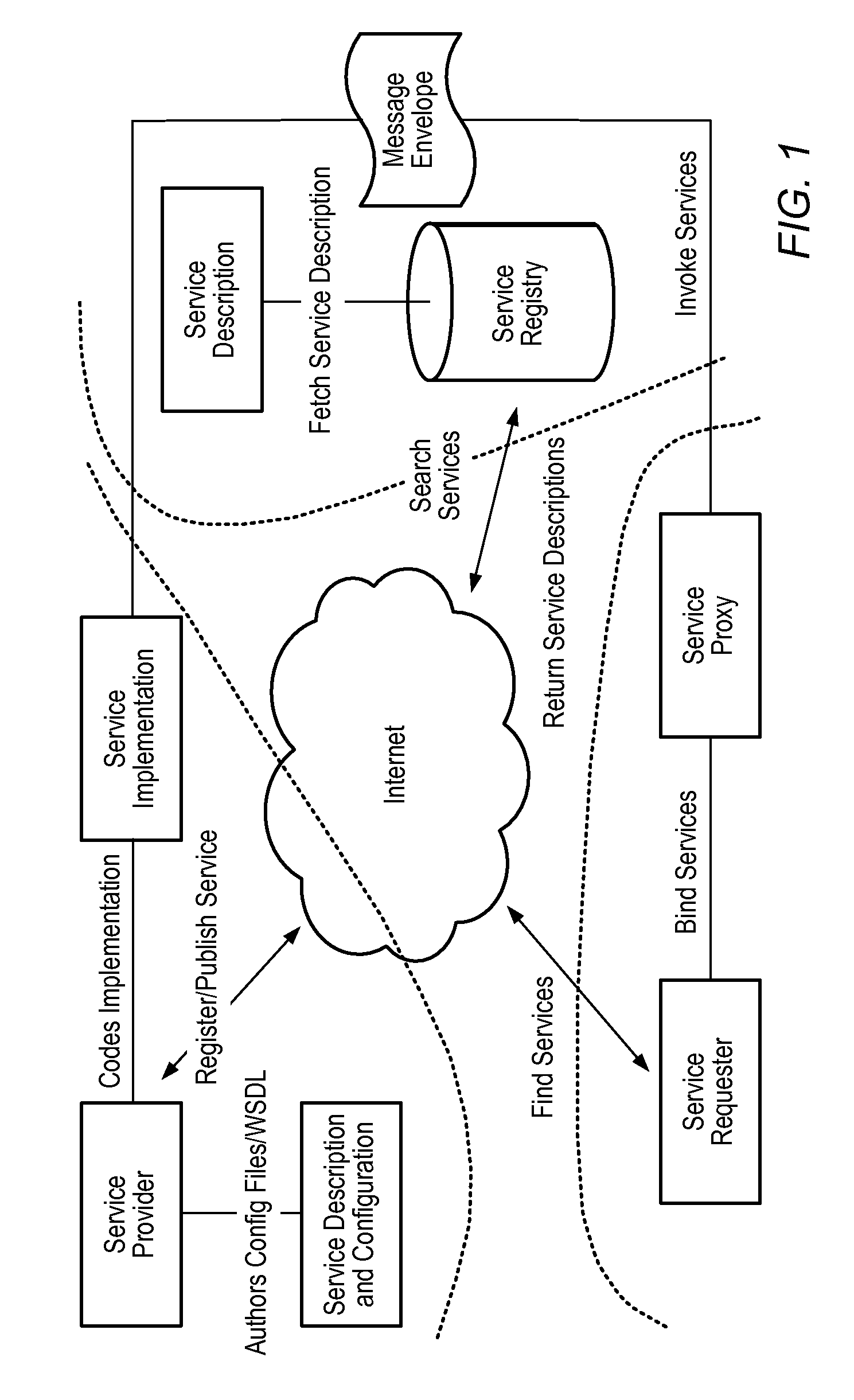

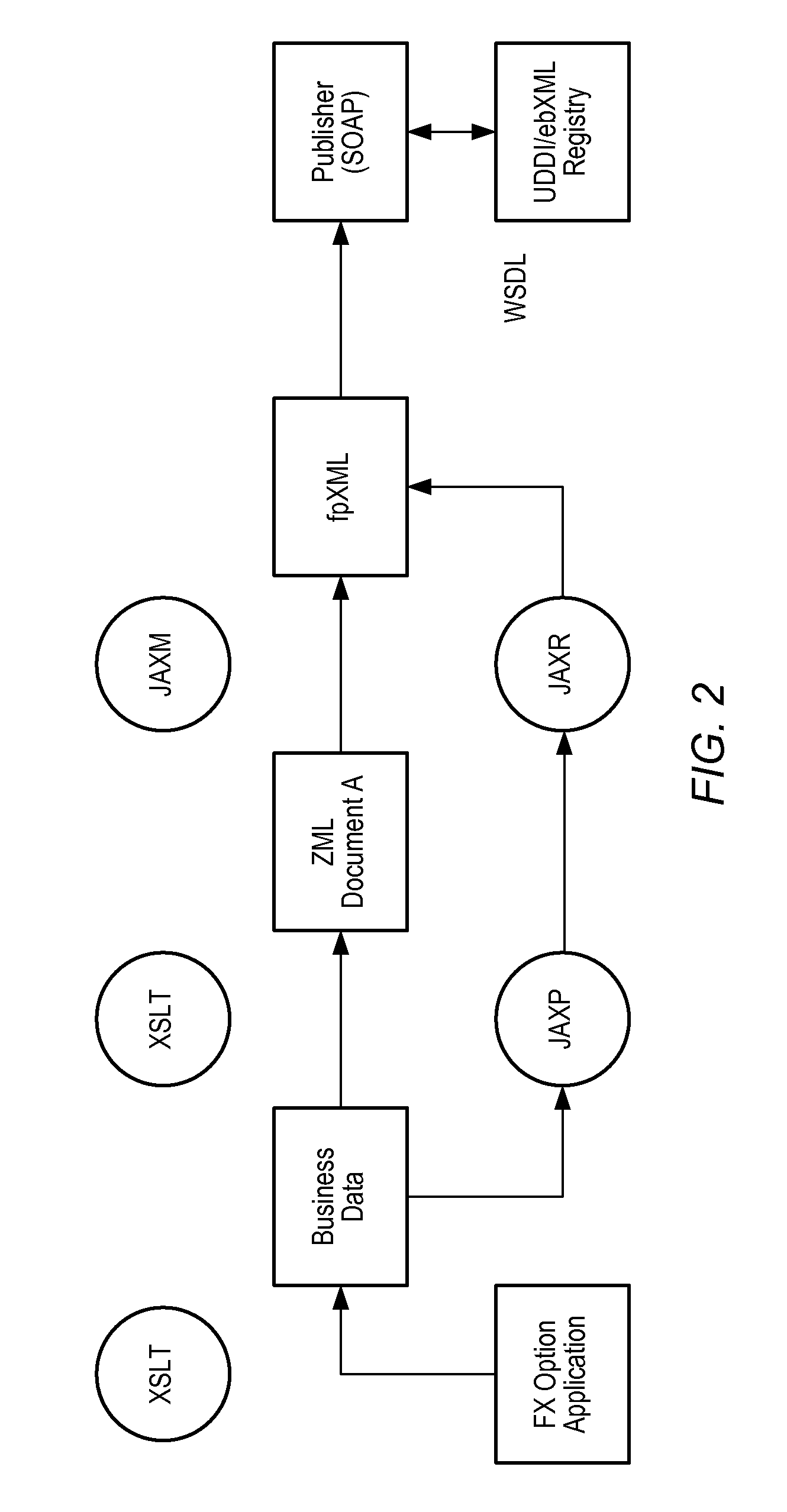

System and method for generating Web Services using a Web Services Structured Methodology. One embodiment may be implemented as a Web Services architecture design mechanism. Lifecycles of the Web Services design process may include vision and strategy, architecture design, development, integration, and deployment. In one embodiment, the Web Services architecture design mechanism may implement a structured methodology design process for Web Services. One embodiment may include a reusable Web Services design pattern catalog and a mechanism for maintaining and updating the catalog and for using the catalog to apply design patterns when designing and implementing Web Services. One embodiment may be used for Enterprise And Cross-Enterprise Integration of Web Services. One embodiment may be used for Legacy Mainframe Integration and Interoperability with Web Services.

Owner:ORACLE INT CORP

System and method for integration of web services

ActiveUS8069435B1SOAP messaging reliableReduce effortOffice automationBuying/selling/leasing transactionsLegacy systemEnterprise integration

System and method for integrating Web Services using a Web Services Structured Methodology are described. Embodiments of a Web Services Structured Methodology may be used to integrate Web Services in Enterprise and Cross-Enterprise business systems, and to integrate legacy systems (e.g. legacy mainframe systems) with Web Services in Enterprise and Cross-Enterprise business systems. Embodiments may provide an integrated Web Services architecture design mechanism that may be used for Enterprise and Cross-Enterprise integration of Web Services. Embodiments may be used for Legacy Mainframe Integration and Interoperability with Web Services.

Owner:ORACLE INT CORP

Method for prolonging service life of solid-state disk

ActiveCN102646069AReduce occupancyLow costMemory adressing/allocation/relocationSoftware engineeringFingerprint

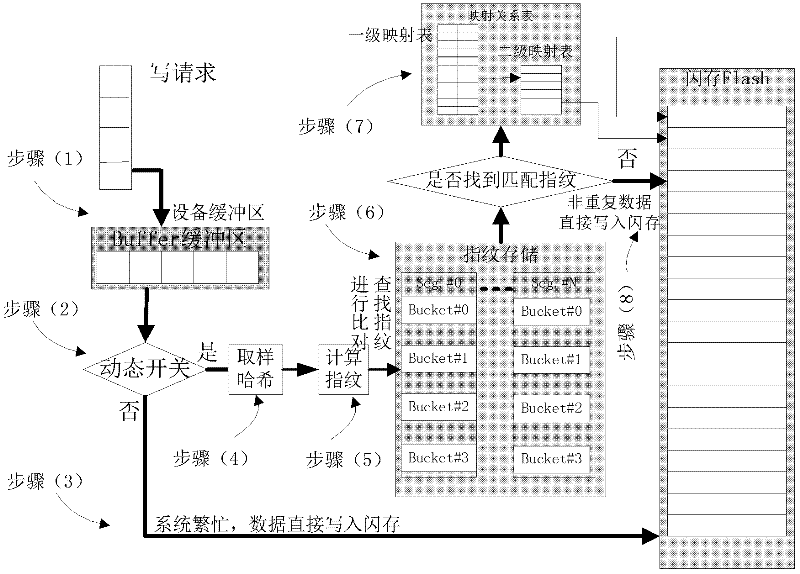

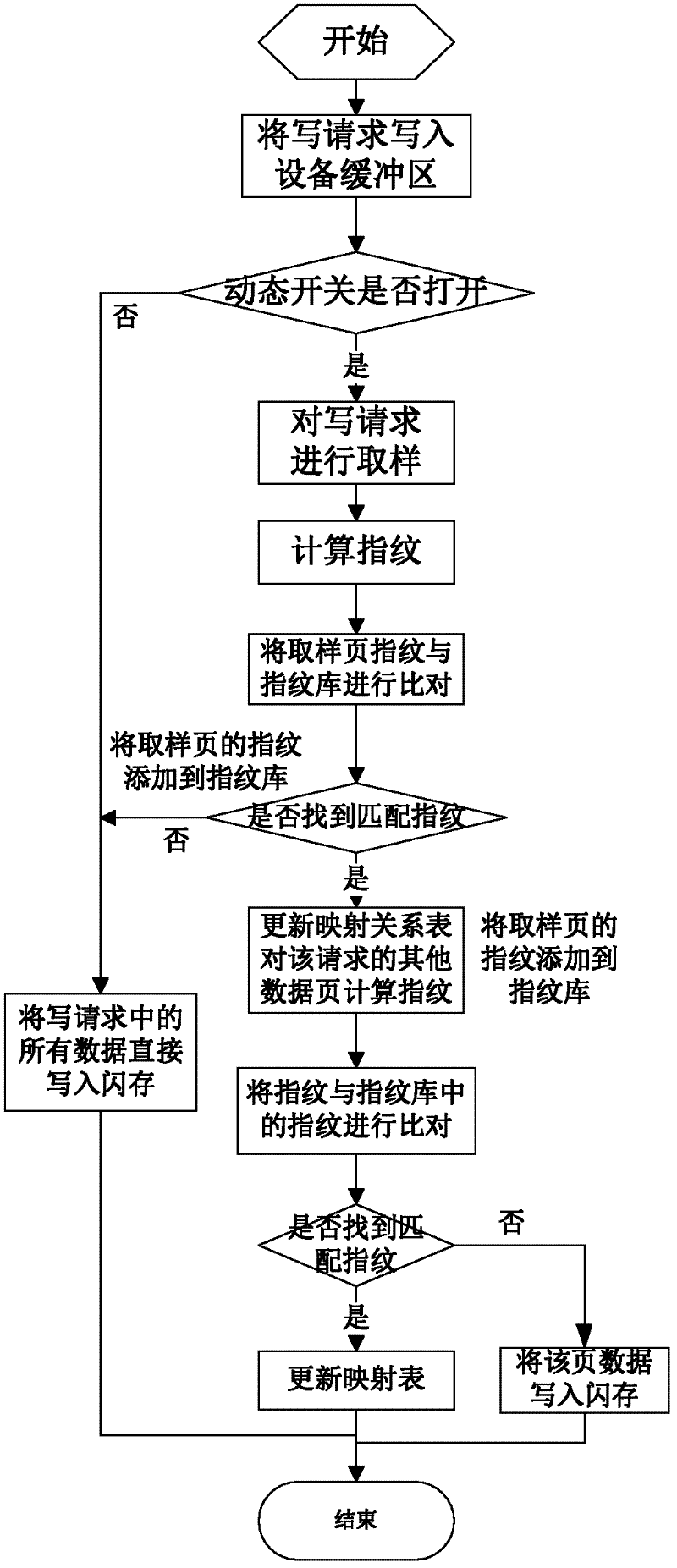

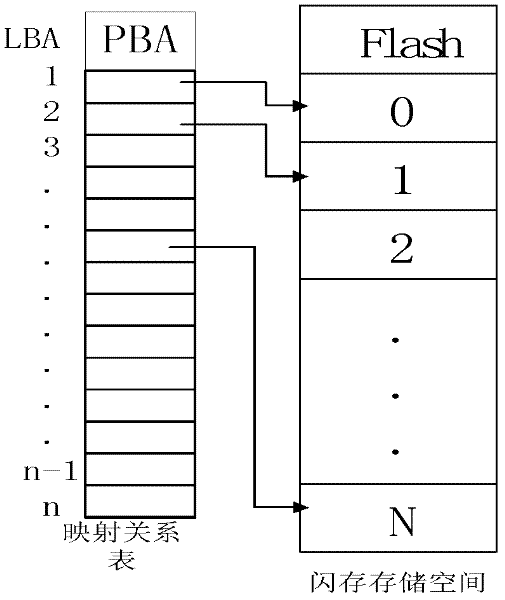

The invention discloses a method for prolonging the service life of a solid-state disk, which comprises the following steps of: (1) adding a write request into a write request queue in a buffer area of a solid-state disk; (2) selecting a data page in the write request as a sampling page; (3) calculating the fingerprint of the sampling page and also comparing with fingerprints in a fingerprint library so as to carry out matching; (4) if no matching fingerprint is found, writing the rest data pages in the sampling page and the request into a flash memory of the solid-state disk directly; and (5) if a matching fingerprint exists, carrying out fingerprint calculation on each of the rest pages respectively and also comparing with the fingerprints in the fingerprint library respectively so as to carry out matching: updating a corresponding mapping table directly for the data page in which the matching fingerprint is found and writing the data page in which the matching fingerprint is found into the solid-state disk. According to the method for prolonging the service life of the solid-state disk, the actual physical occupation of data in the solid-state disk on the flash memory is reduced, the redundant space of a system is indirectly increased, and the frequency of the garbage recovering operation of the system is reduced, so that the service life of the solid-state disk is enhanced.

Owner:HUAZHONG UNIV OF SCI & TECH

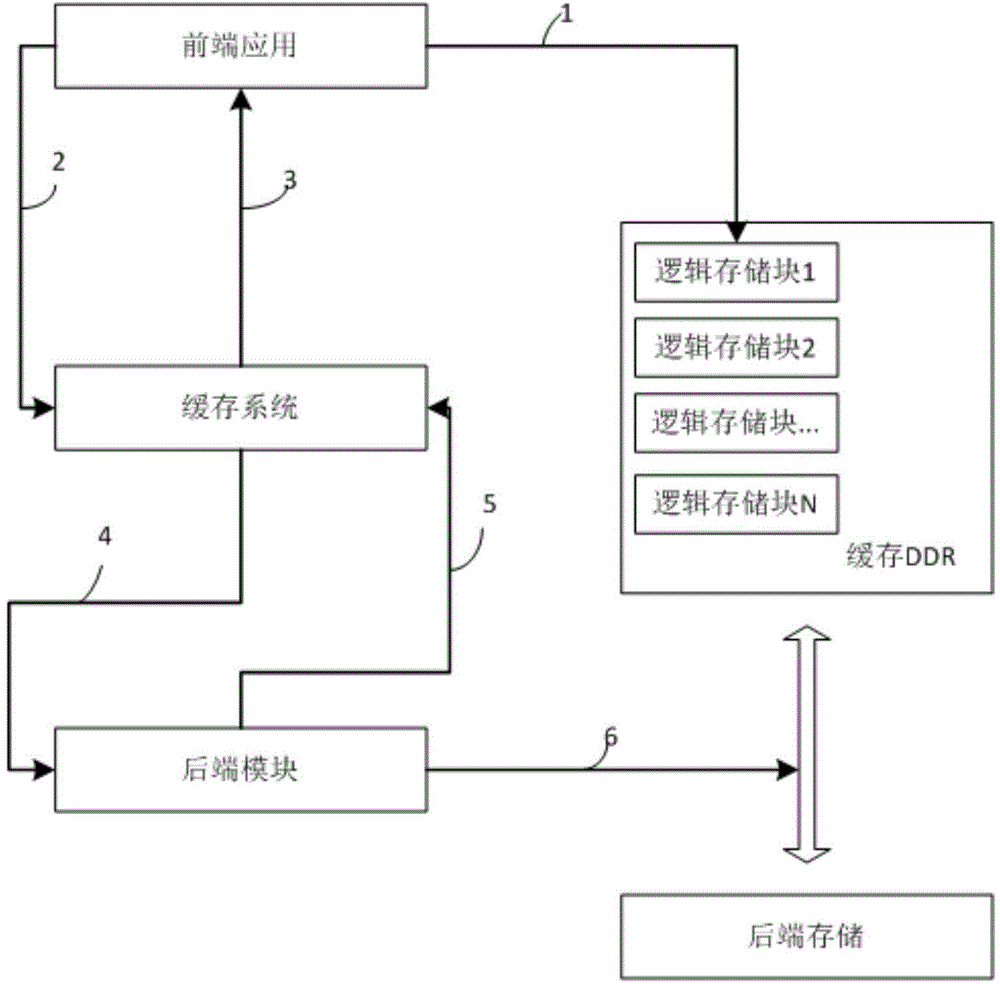

Method and system for data caching of solid state disk

InactiveCN103049394AReduce the number of reads and writesWrite lessMemory adressing/allocation/relocationVisit timeSolid-state drive

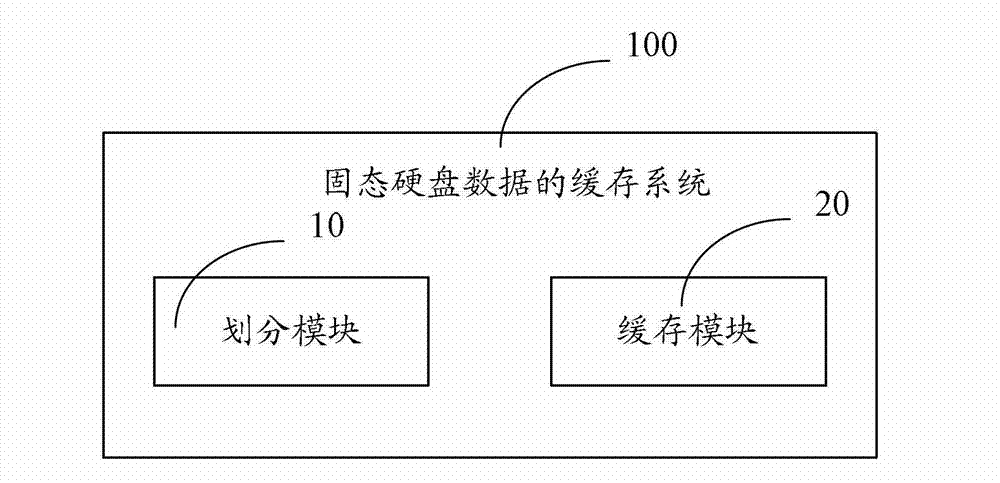

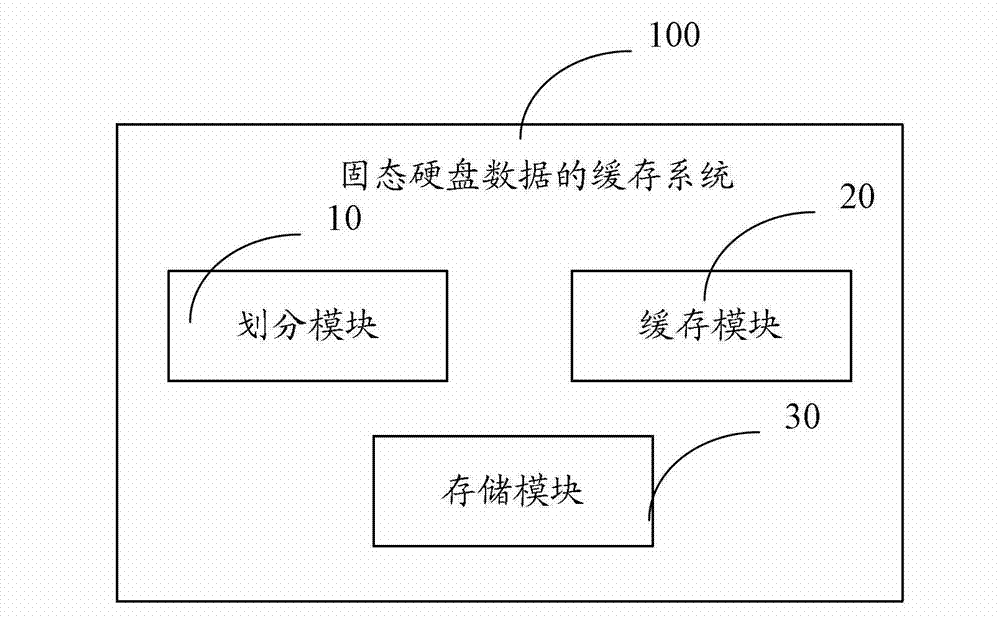

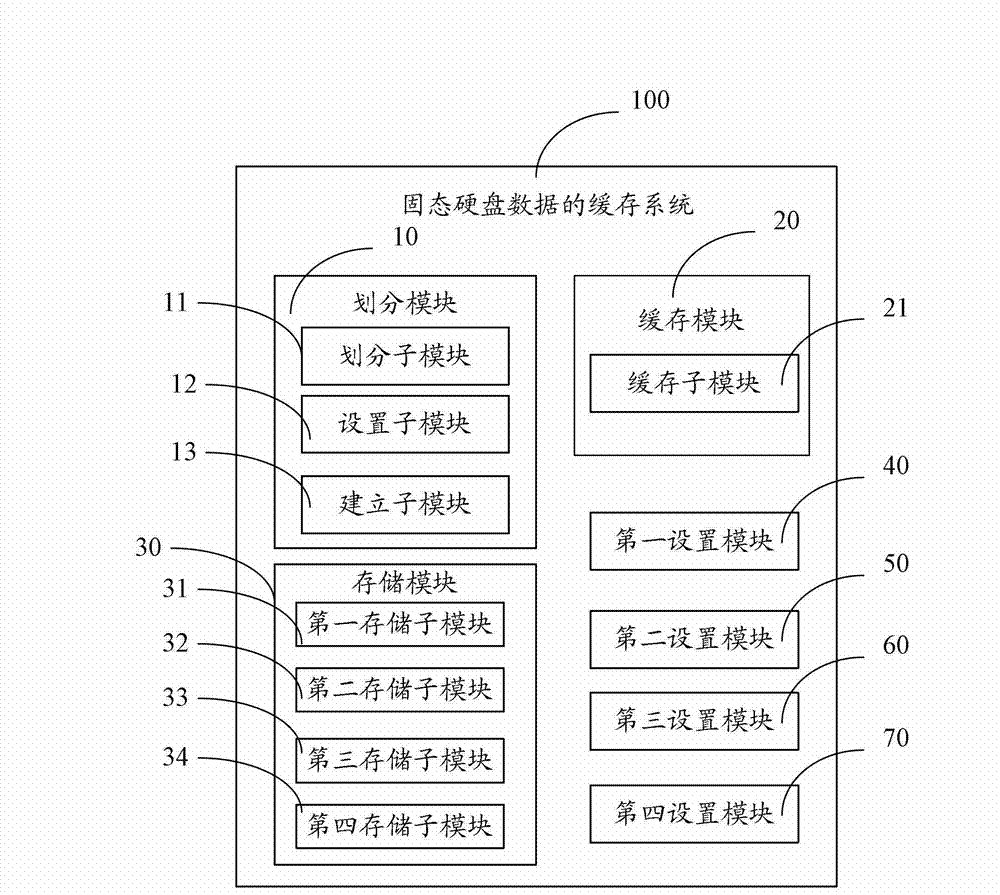

The invention is applied to the technical field of storage, and provides a method and system for data caching of a solid state disk. The method for the data caching of the solid state disk comprises the following steps: setting a part of memory of a system memory as a data buffer cache of the solid state disk; caching read and write data of the solid state disk into the data buffer cache of the solid state disk. Therefore, the method and system of the data caching of the solid state disk reduces the visit times of the solid state disk and lengthens the service life of the solid state disk.

Owner:RAMAXEL TECH SHENZHEN

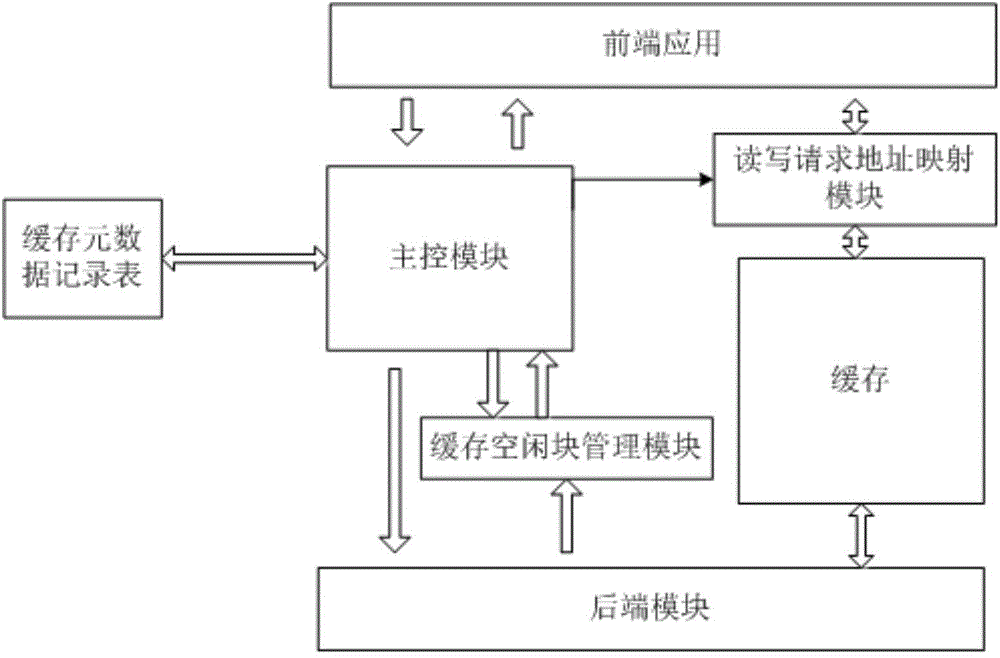

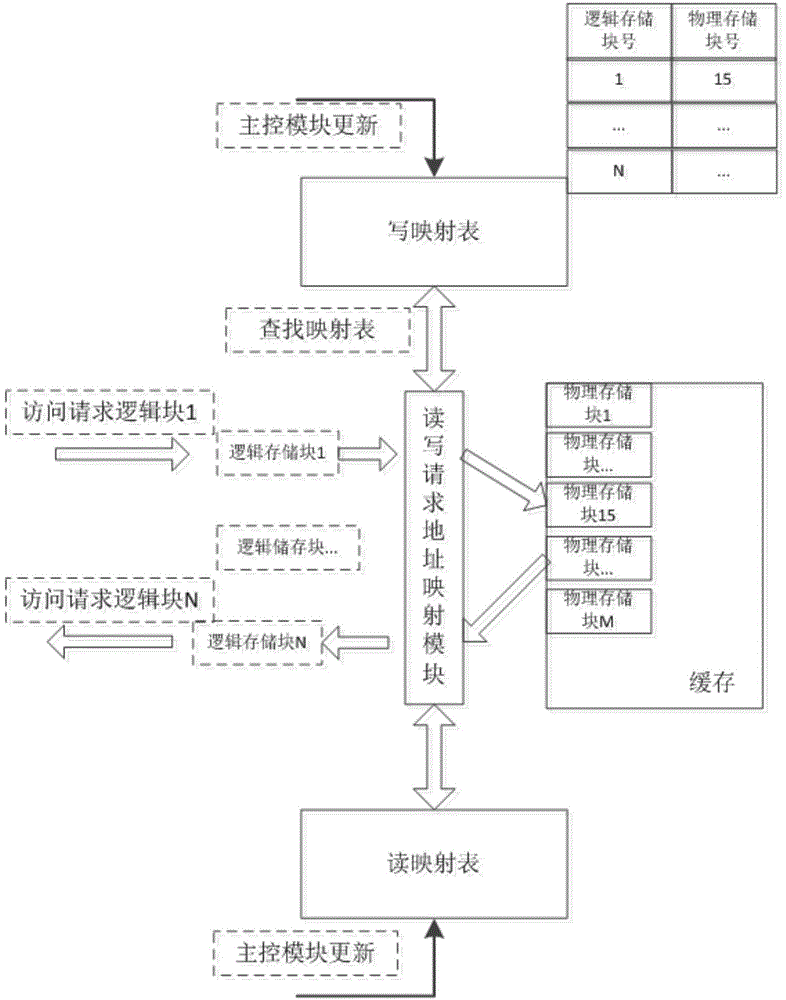

Flash memory storage system and reading, writing and deleting method thereof

ActiveCN104636285AAchieve zero copyWrite lessMemory adressing/allocation/relocationZero-copyMetadata record

The invention discloses a flash memory storage system and a reading, writing and deleting method thereof. The flash memory storage system comprises a cache, a main control module, a cache metadata record sheet, a read mapping table and a write mapping table. The write mapping table is used for being stored in the cache and writing in the correspondence of a logical storage block and a physical storage block. The read mapping table is used for being stored in the cache and reading out the correspondence of the logical storage block and the physical storage block. The cache metadata record sheet is used for storing correspondences of metadata sheet addresses, the physical storage blocks and rear end flash memory addresses. By means of the flash memory storage system, the unnecessary write-in or read-out of a rear end flash memory can be reduced, the zero copy on a read-write data channel is achieved, the unnecessary intermediate copy process is omitted, and therefore the read-write efficiency is improved; the size of the read-write access of a front end application can be matched with the size of the rear end flash memory.

Owner:BEIJING ZETTASTONE TECH CO LTD

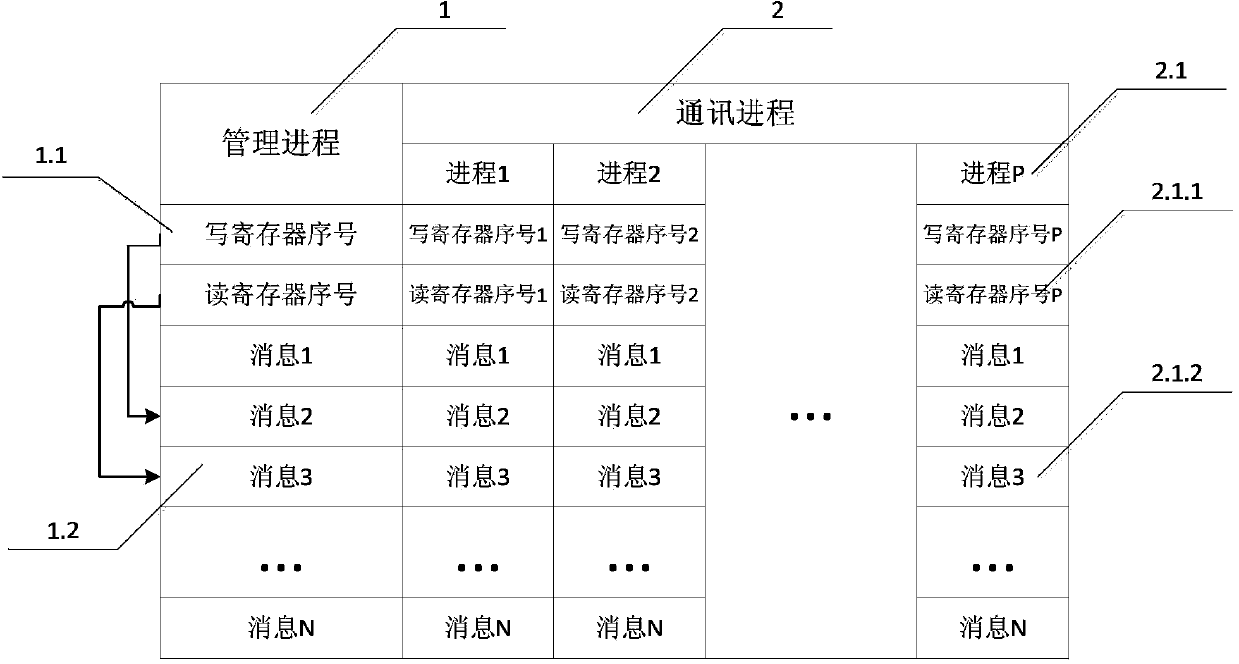

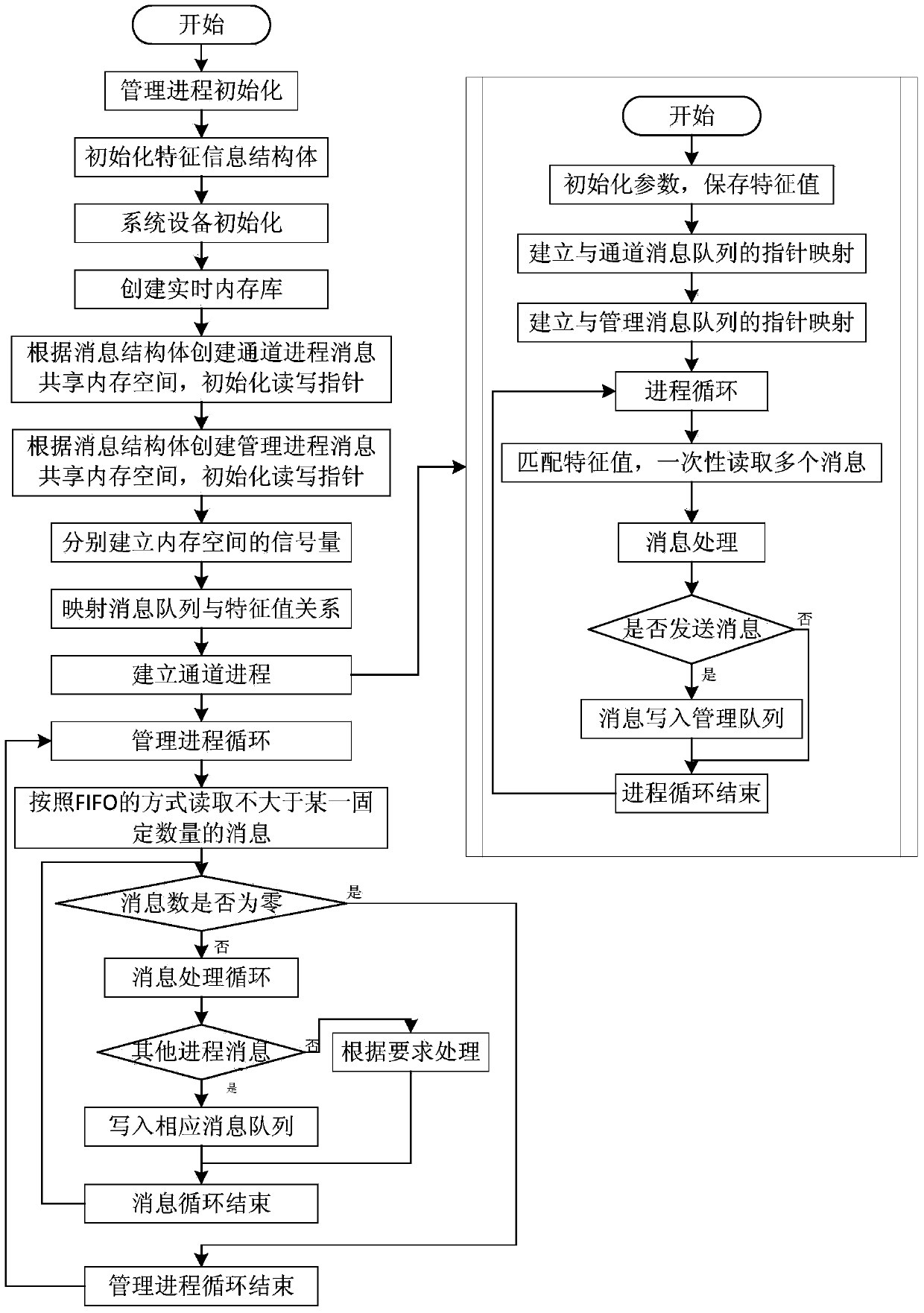

Processing method for optimization of inter-process communication of embedded operating system

ActiveCN104346229AMeet the requirements of communication efficiencyWrite lessInterprogram communicationOperational systemManagement process

The invention discloses a device and a method for optimization of inter-process communication of an embedded operating system. The method comprises the following steps: initializing a management process to determine operation information of system equipment; initializing a characteristic information structural body and the equipment; establishing a real-time memory library; establishing a channel process message sharing memory space, a management process message sharing memory space, the semaphore of the channel process message sharing memory space and the semaphore of the management message sharing memory space; mapping the channel process message sharing memory space and the channel process characteristic information structural body; establishing channel processes according to the operation information and transferring a management message to the corresponding channel process; entering the management process, setting the semaphore of the management message, and reading the management message which is less than or equal to the semaphore of the management message. According to the device and the method, the problems of useless message transfer and low message processing efficiency existing in a message transfer mechanism established by using the sharing memories under the condition of communication among multiple processes of the embedded operation system are solved.

Owner:STATE GRID CORP OF CHINA +3

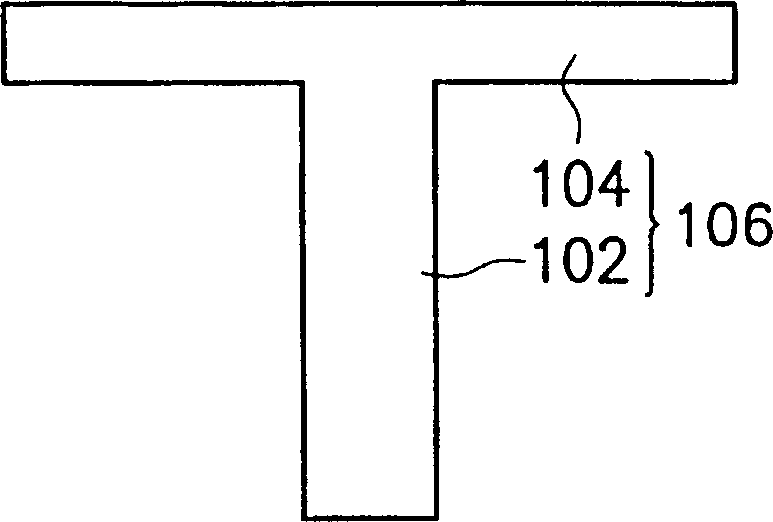

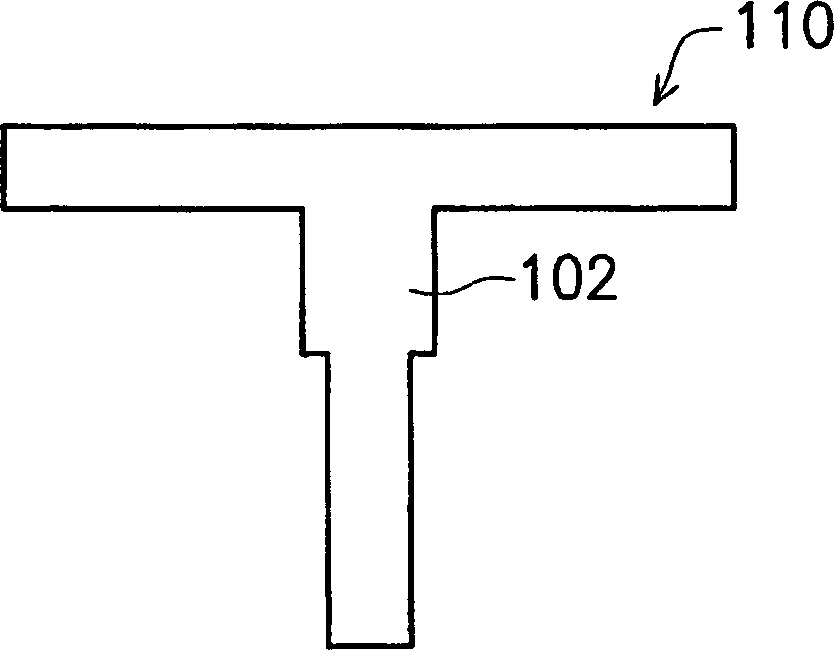

Mask-pattern correction method

InactiveCN1405634AReduce file sizeWrite lessSemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentEngineeringCorrection method

A correction method for mask patterns is first of all to provide a third pattern composed of a first strip pattern and a second pattern in which the first strip pattern is connected between the head and end of the second one, then two sides of the first strip pattern are added by an auxiliary pattern to form a first correction apttern. After that part of the first strip pattern is reduced to form a second correction pattern, the dimension of the reduced first strip pattern is the key on of a main pattern then the second correction pattern is modified by an optical adjacent correction method to form a third modified pattern.

Owner:UNITED MICROELECTRONICS CORP

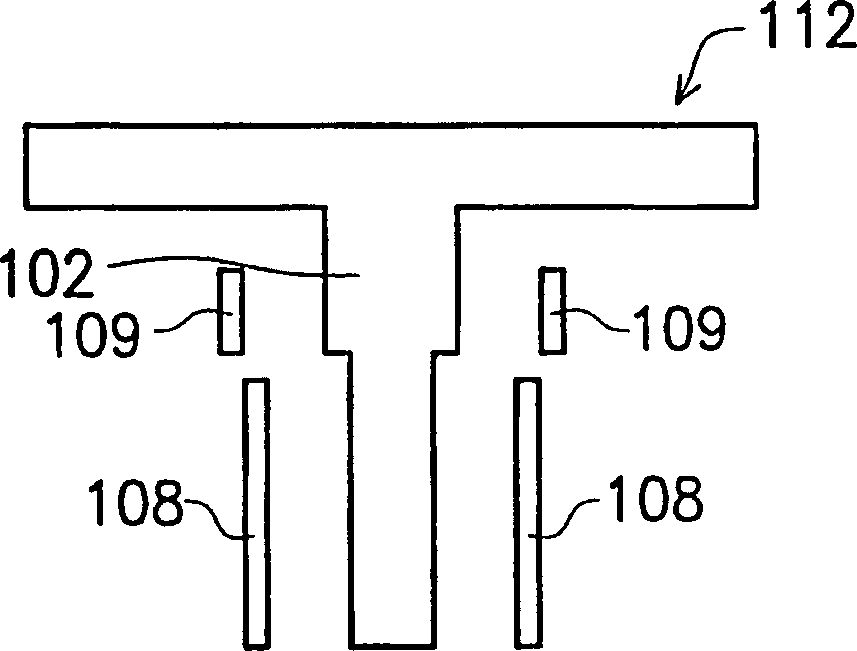

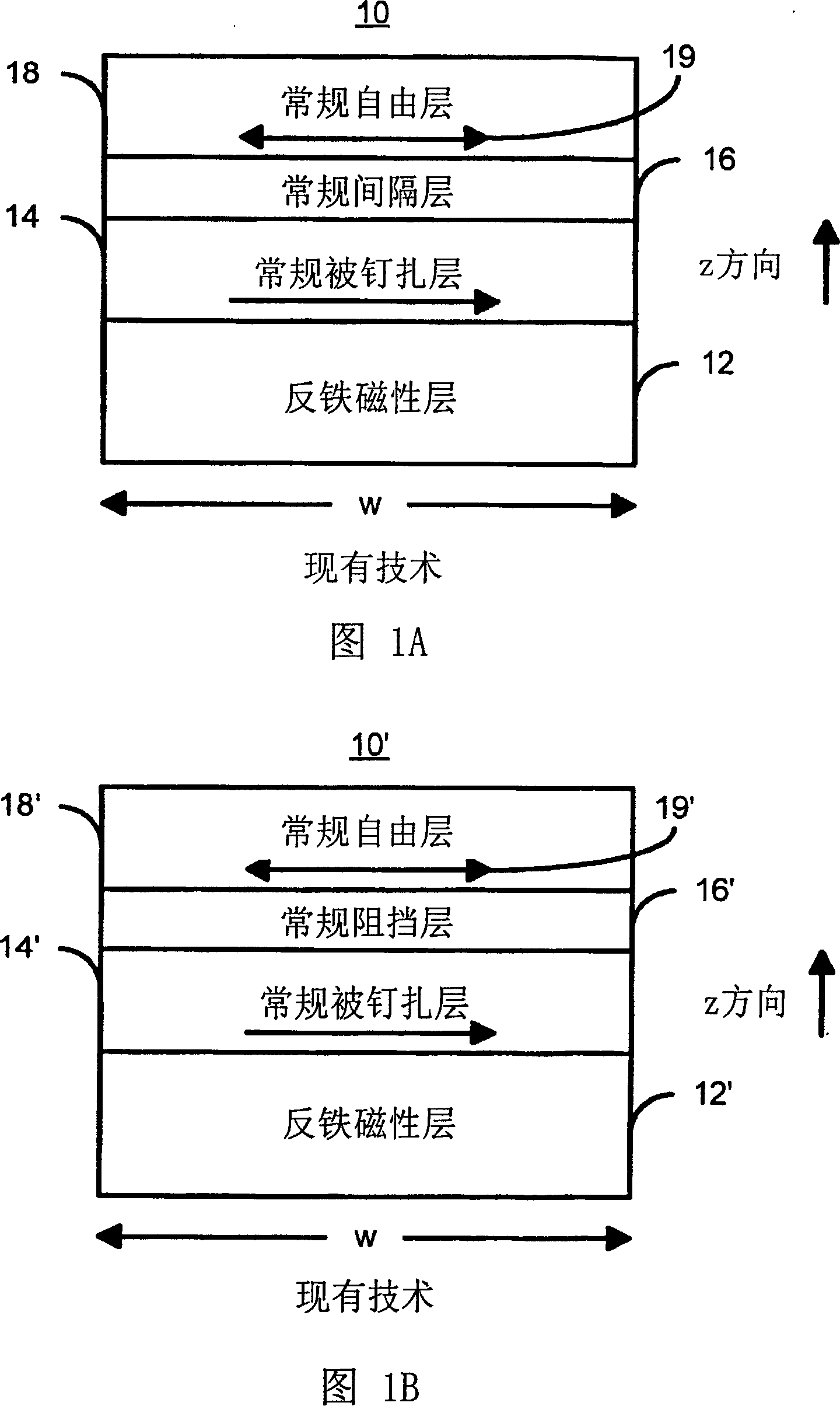

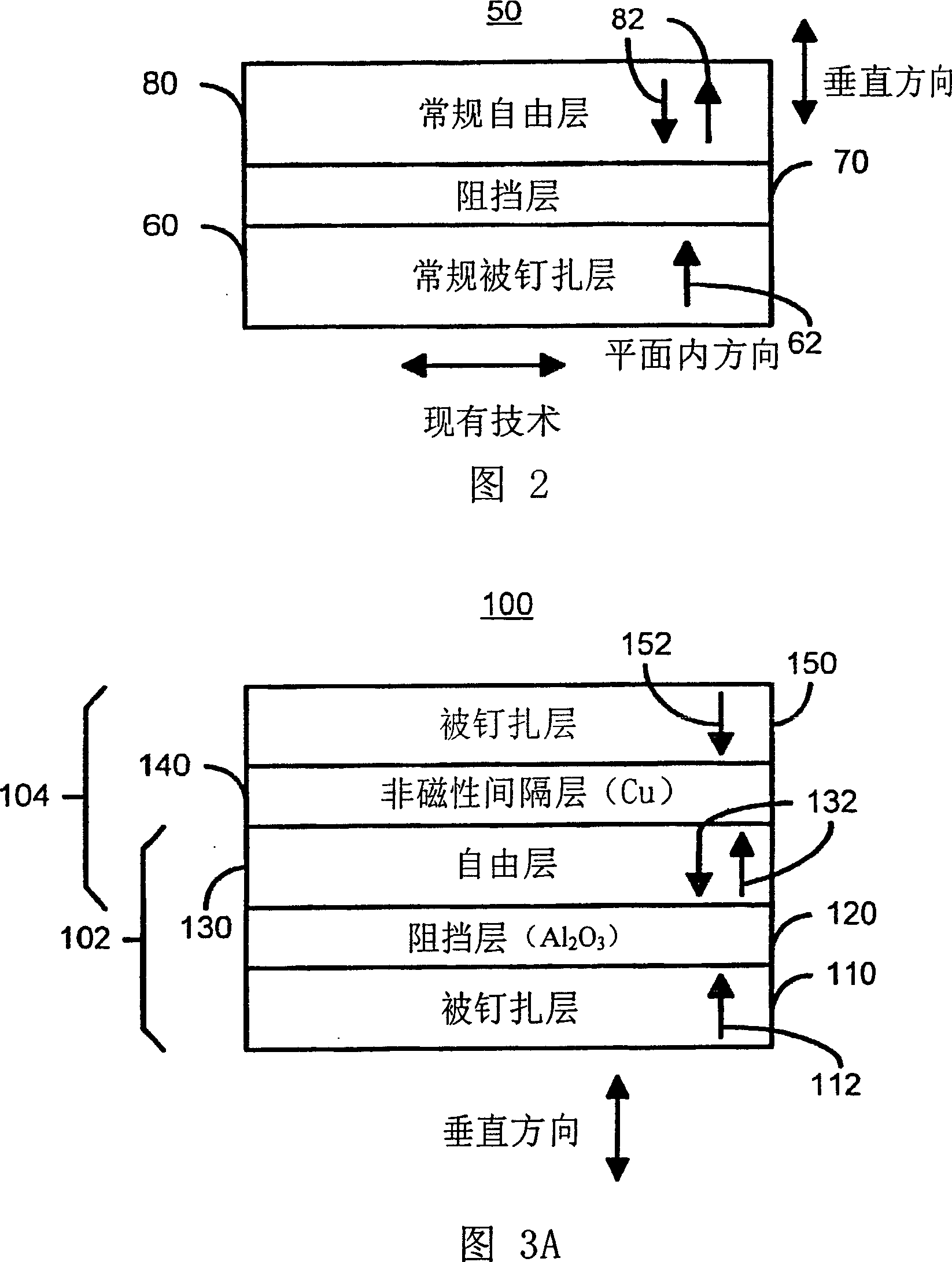

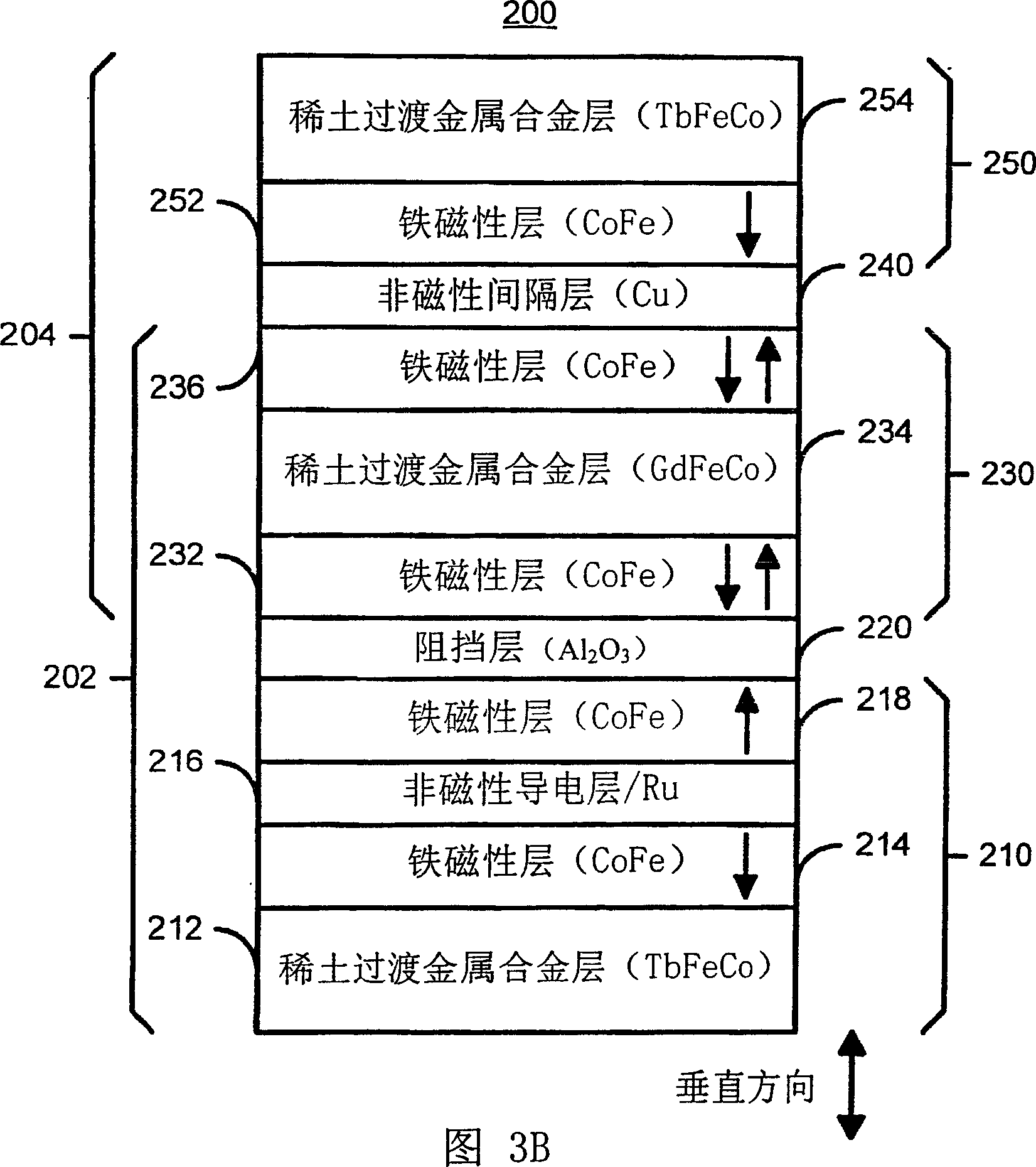

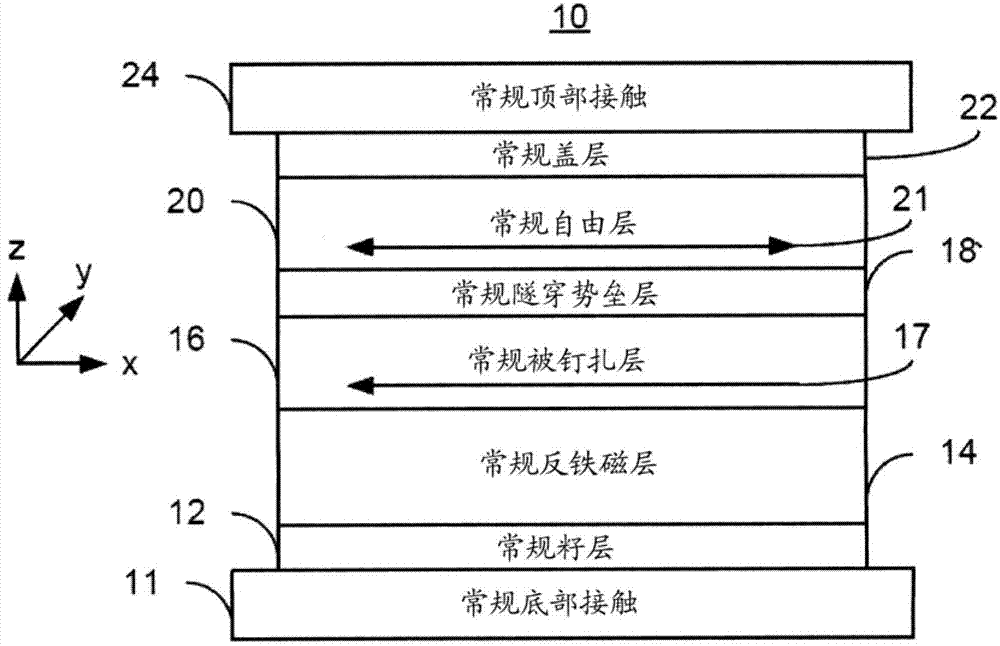

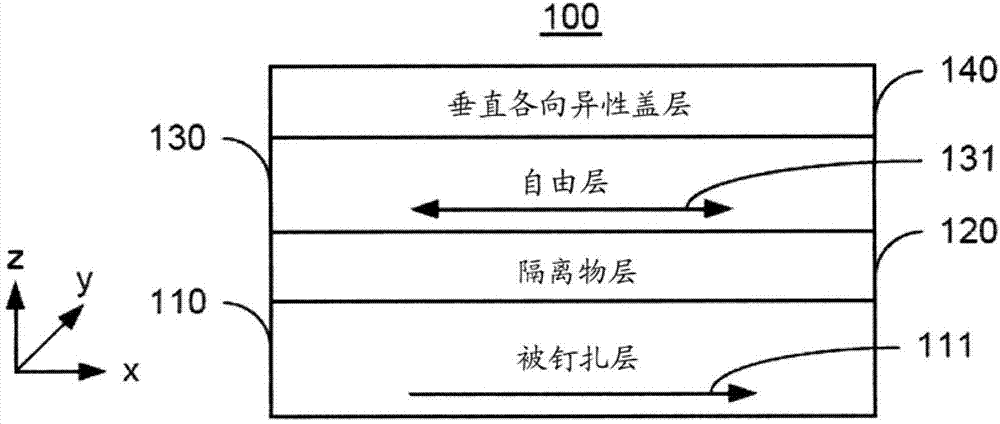

Perpendicular magnetization magnetic element utilizing spin transfer

InactiveCN1938780AWrite lessNanomagnetismMagnetic measurementsPerpendicular magnetizationMagnetic memory

A method and system for providing a magnetic element that can be used in a magnetic memory is disclosed. The method and system include providing a first pinned layer, a barrier layer, a free layer, a conductive nonmagnetic spacer layer, and a second pinned layer. Each pinned layer has a pinned layer easy axis. At least a portion of the pinned layer easy axis is in a perpendicular direction. The barrier layer resides between the first pinned layer and the free layer. The spacer layer is between the free layer and the second pinned layer. The free layer has a free layer easy axis, at least a portion of which is in the perpendicular direction. The magnetic element is also configured to allow the free layer to be switched due to spin transfer effect when a write current is passed through the magnetic element. Because of the perpendicular magnetization(s), the writing current for spin transfer may be significantly reduced.

Owner:GRANDIS

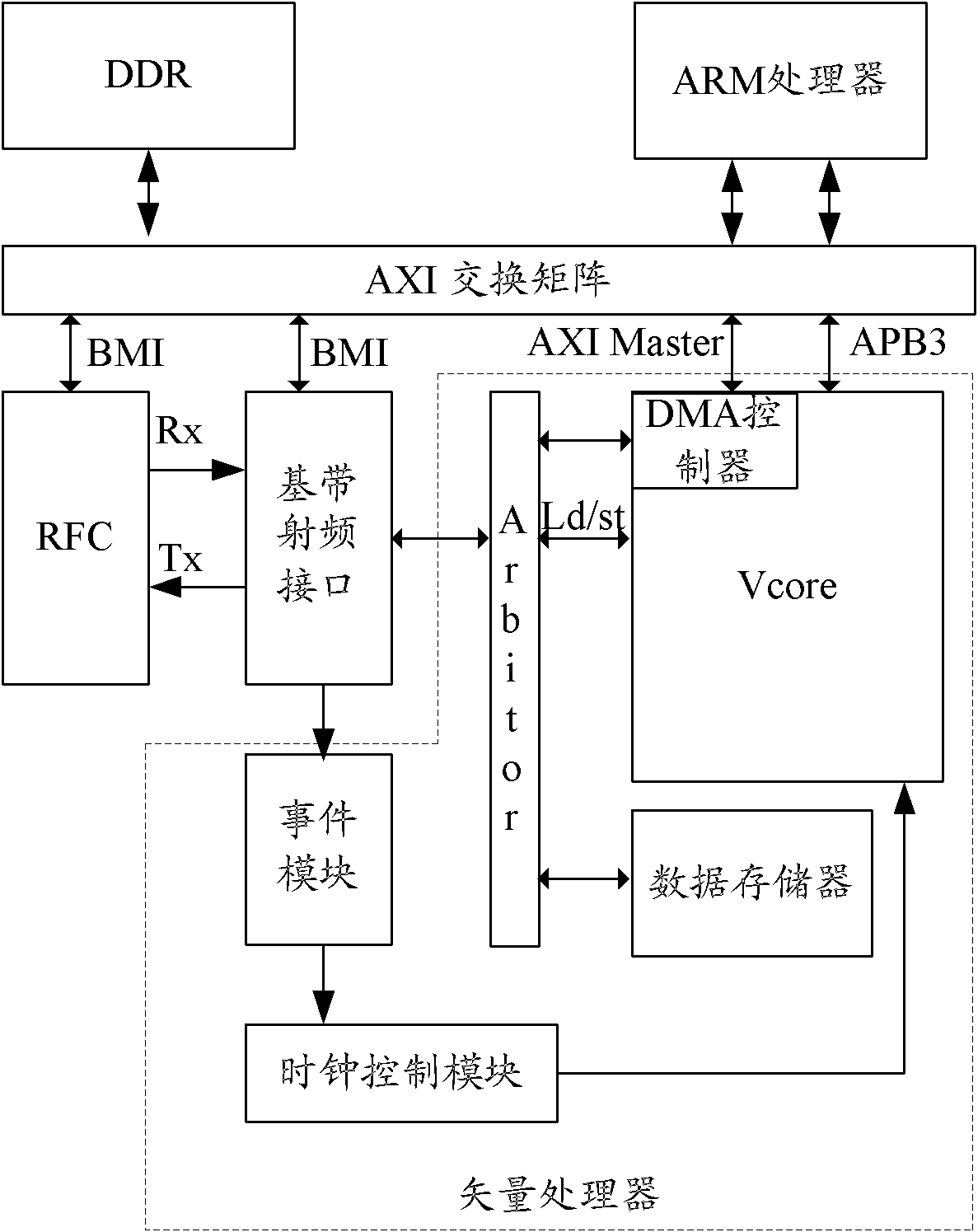

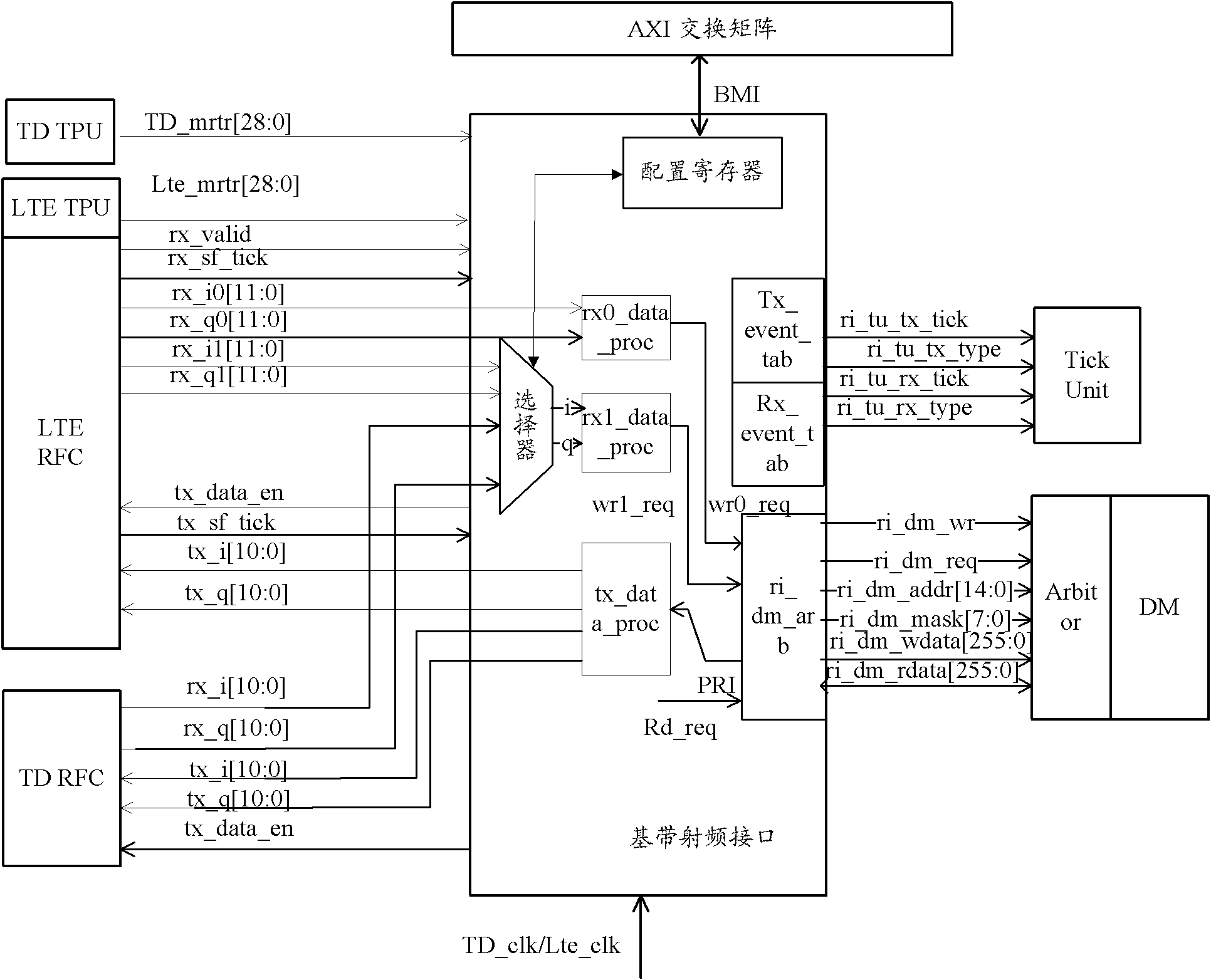

Baseband radio frequency interface based on software defined radio (SDR) and application method thereof

ActiveCN102740511AWrite lessIncrease flexibilityTransmissionWireless communicationSoftware define radioProcessor register

The invention discloses a baseband radio frequency interface based on a software defined radio (SDR). The baseband radio frequency interface based on the SDR comprises an uplink data processing module, a downlink data processing module corresponding to different communication modes, an uplink event list module, a downlink event list module, a configuration register, a selector and a communication module. The invention also discloses an application method of the baseband radio frequency interface based on the SDR. Through using the baseband radio frequency interface and the application method, the baseband radio frequency interface can be guaranteed to possess versatility and simultaneously possess advantages of a simple circuit and low power consumption. Scheduling to a vector processor or a multi-core DSP can be simply realized.

Owner:SANECHIPS TECH CO LTD

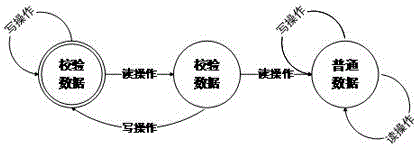

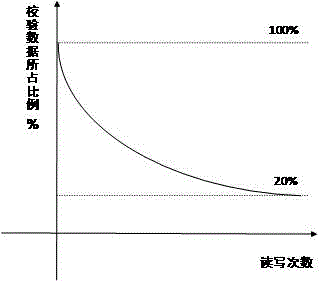

Flash translation layer capable of perceiving RAID (Redundant Array of Independent Disks) and implementation method thereof

ActiveCN105718206AAchieve separationRealize the effect of perception RAIDInput/output to record carriersMemory adressing/allocation/relocationRAIDComputer architecture

The invention relates to a flash translation layer capable of perceiving a RAID (Redundant Array of Independent Disks) and an implementation method thereof. An operation identifier which shows the access type of the last-time access on a page and a logic page type identifier which shows whether the page is common data or calibration data are added into each logic page of a flash memory; a block type identifier which shows whether data stored in a block is the common data or the calibration data is added into each physical block of the flash memory; when a certain logic page is accessed, the access type of the last-time access and the access type of current access are compared, and if the access types are both read operation, an indication result shows that the data corresponding to the logic page is the common data; and when the certain logic page is subjected to a write operation, according to the type identification of the page, the page is written into a newly-distributed idle block, the type of the idle block is set to be the same with the type of the page, or the page is directly written into a physical block which is the same as the page in type. The flash translation layer is low in expenditure, reduces a data size migrated in a garbage collection process, and reduces writing to the flash memory so as to prolong the service life of the flash memory.

Owner:NAT UNIV OF DEFENSE TECH

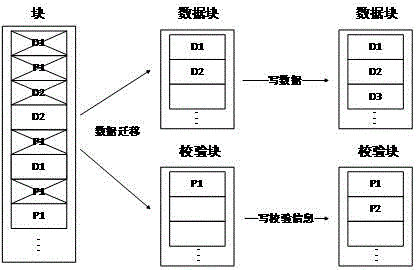

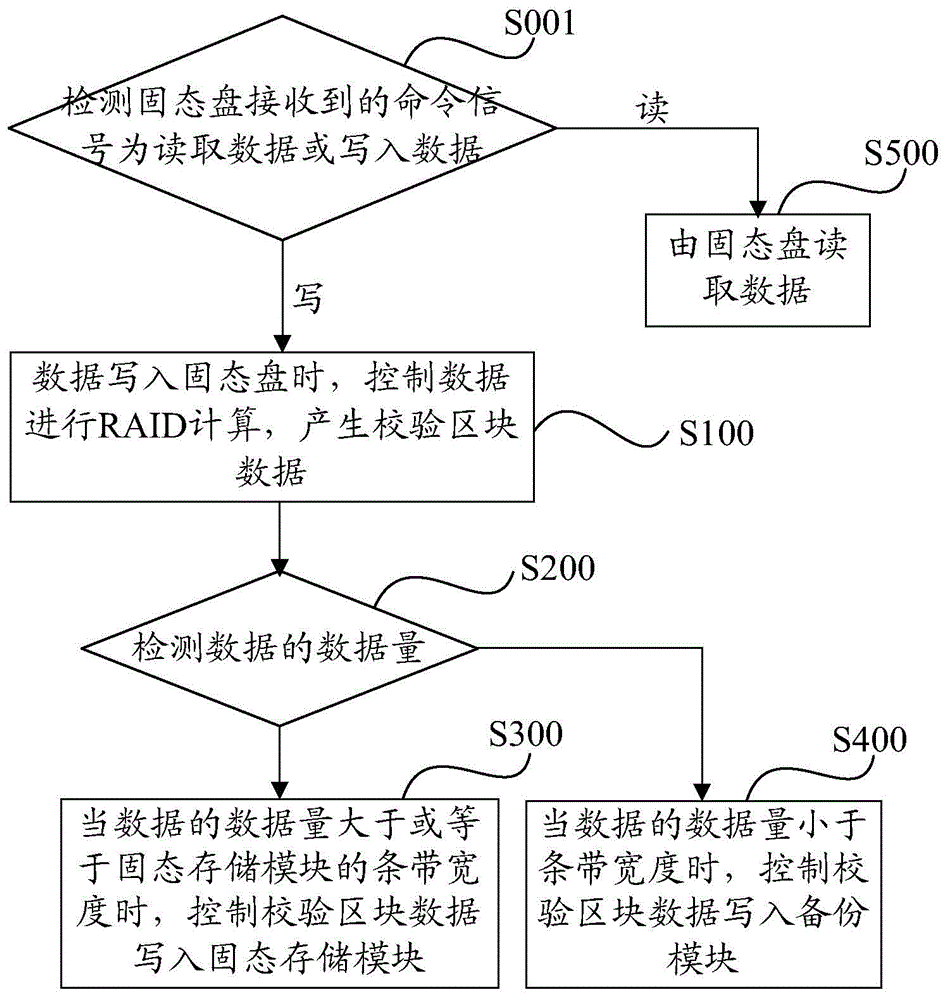

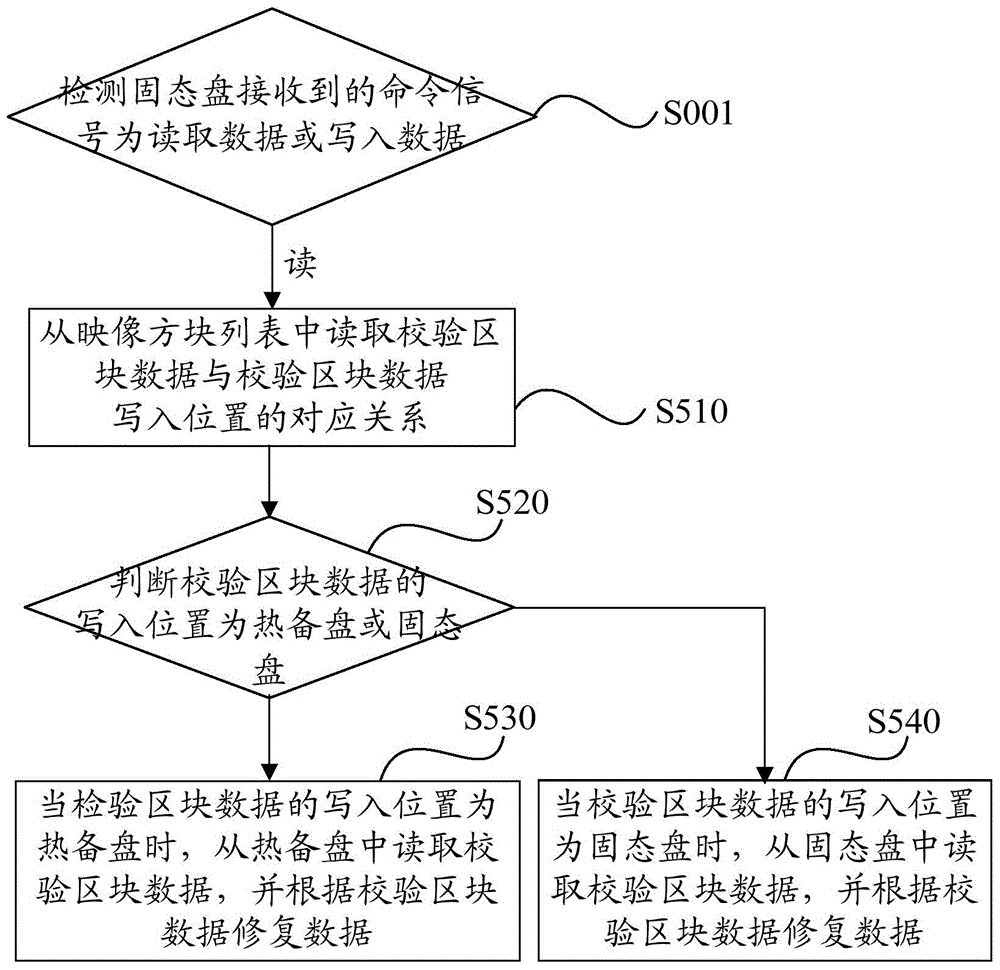

Storage system and data protection method thereof

ActiveCN104881244AWrite lessReduce lossInput/output to record carriersRedundant operation error correctionSolid-state storageControl unit

The invention discloses a storage system and a data protection method thereof. The storage system comprises a plurality of solid-state storage modules, a detection module, a control module and a backup module. The solid-state storage modules form an RAID (redundant array of independent disks), used for subjecting data to RAID calculation to generate check area block data when data are written into the solid-state storage modules. The detection module is used for detecting quantity of the data. The control module comprises a first control unit and a second control unit; the first control unit is used for controlling the check area block data to be written into the solid-state storage modules when the quantity of the data is higher than or equal to stripe width of the solid-state storage modules; the second control unit is used for controlling the check area block data to be written into the backup module when the quantity of the data is lower than the stripe bandwidth. By adding the backup module to integrate frequent writing of the check area block data, unnecessary loss of the solid-state storage modules is reduced, and the lives of the solid-state storage modules are prolonged.

Owner:BEIJING FORTUNET INFORMATION & TECH

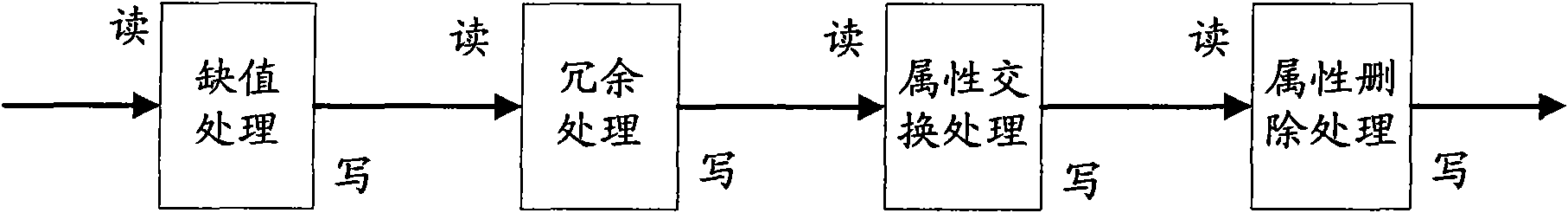

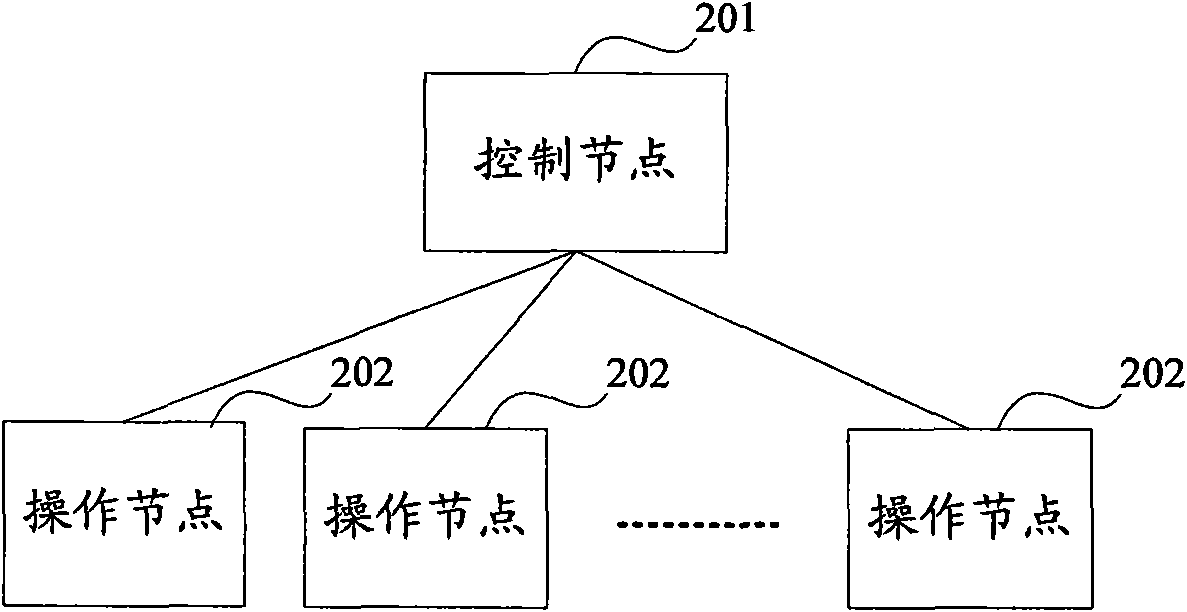

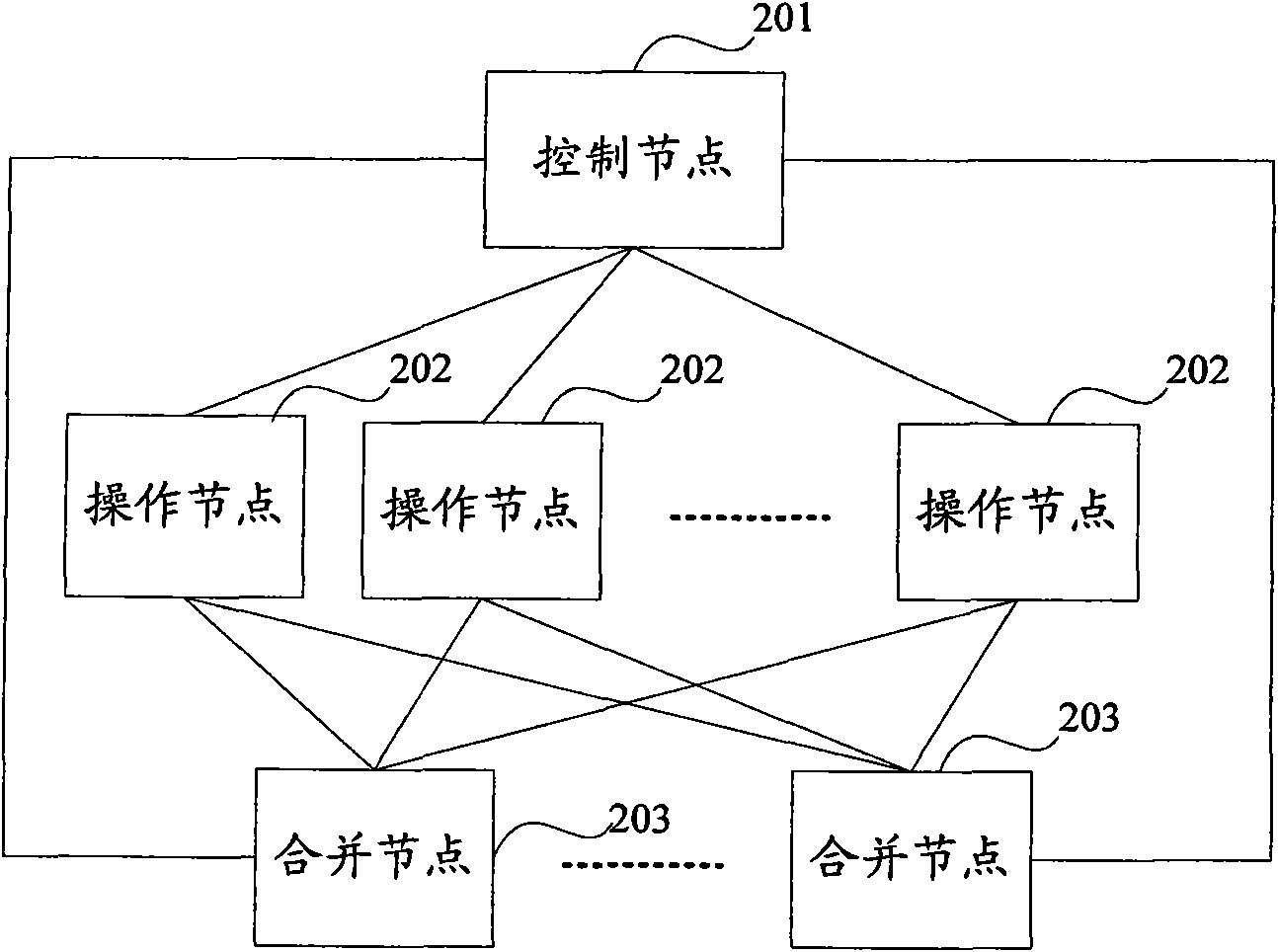

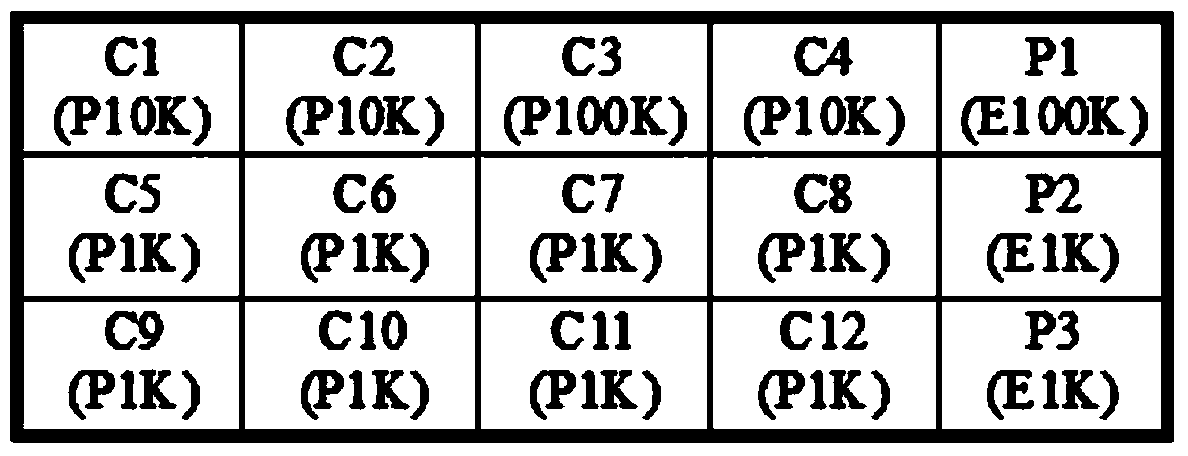

Data preprocessing method, system and device in data mining system

ActiveCN102054001AImprove preprocessing efficiencyWrite lessSpecial data processing applicationsData dredgingTransfer procedure

The invention discloses a data preprocessing method, a data preprocessing system and a data preprocessing device in a data mining system. The data preprocessing correspondingly has a plurality of preprocessing modes in which the execution sequence is set. The invention adopts a main technical scheme which comprises: determining a current preprocessing mode corresponding to the data preprocessing; and when determining that the processing results obtained according to the current preprocessing mode do not need to be combined and the current preprocessing mode is not the last preprocessing mode of the data preprocessing, processing the data to be processed in the current preprocessing mode at the operating nodes, and controlling the operating nodes to process the processing results in a preprocessing mode next to the current preprocessing mode. According to the technical scheme, the transmission process between different nodes for reading the data to be processed and writing the processing results to be written is not used, the data preprocessing efficiency in the data mining system is improved, and the performance of the entire data mining system is improved.

Owner:CHINA MOBILE COMM GRP CO LTD

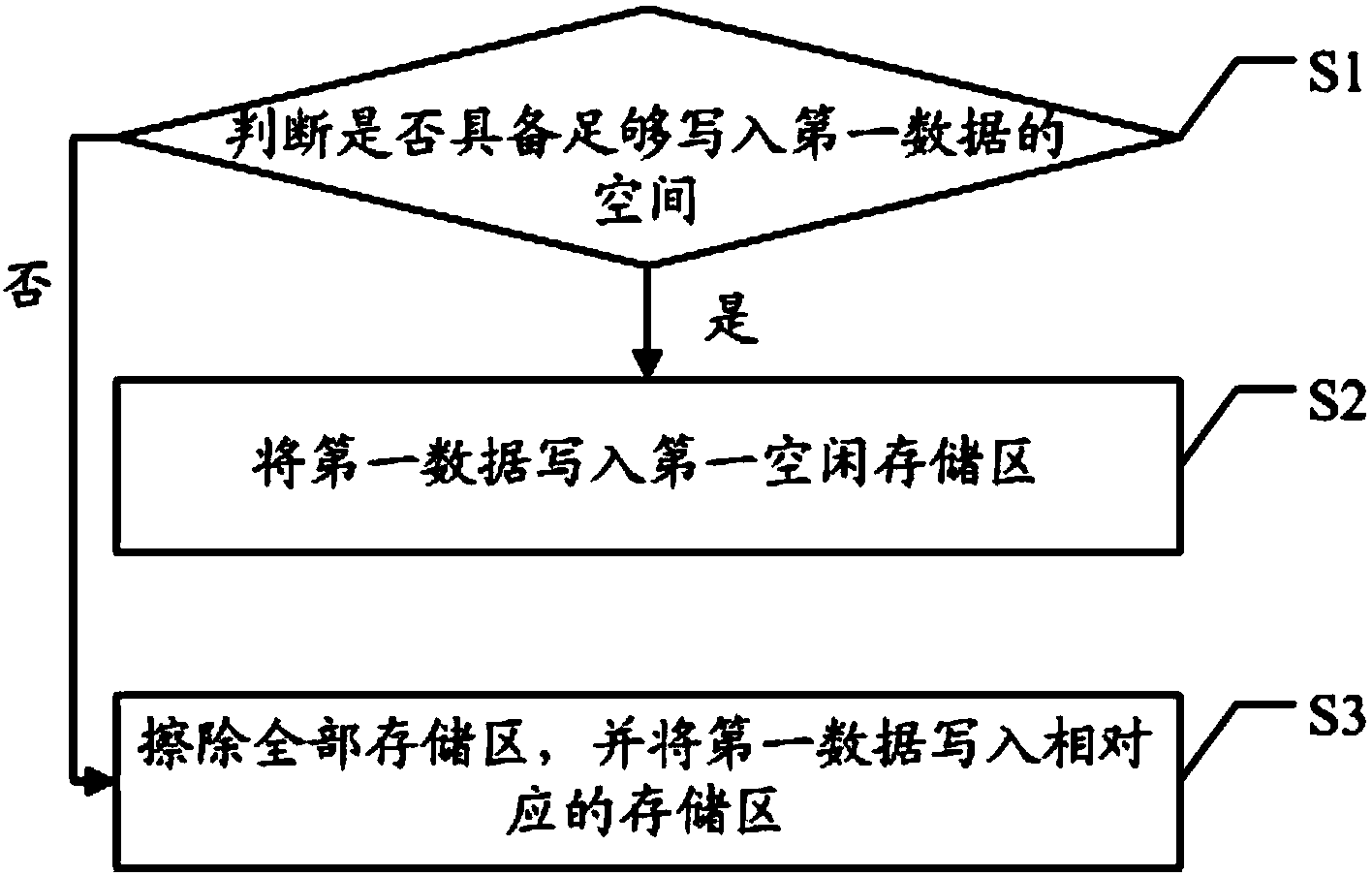

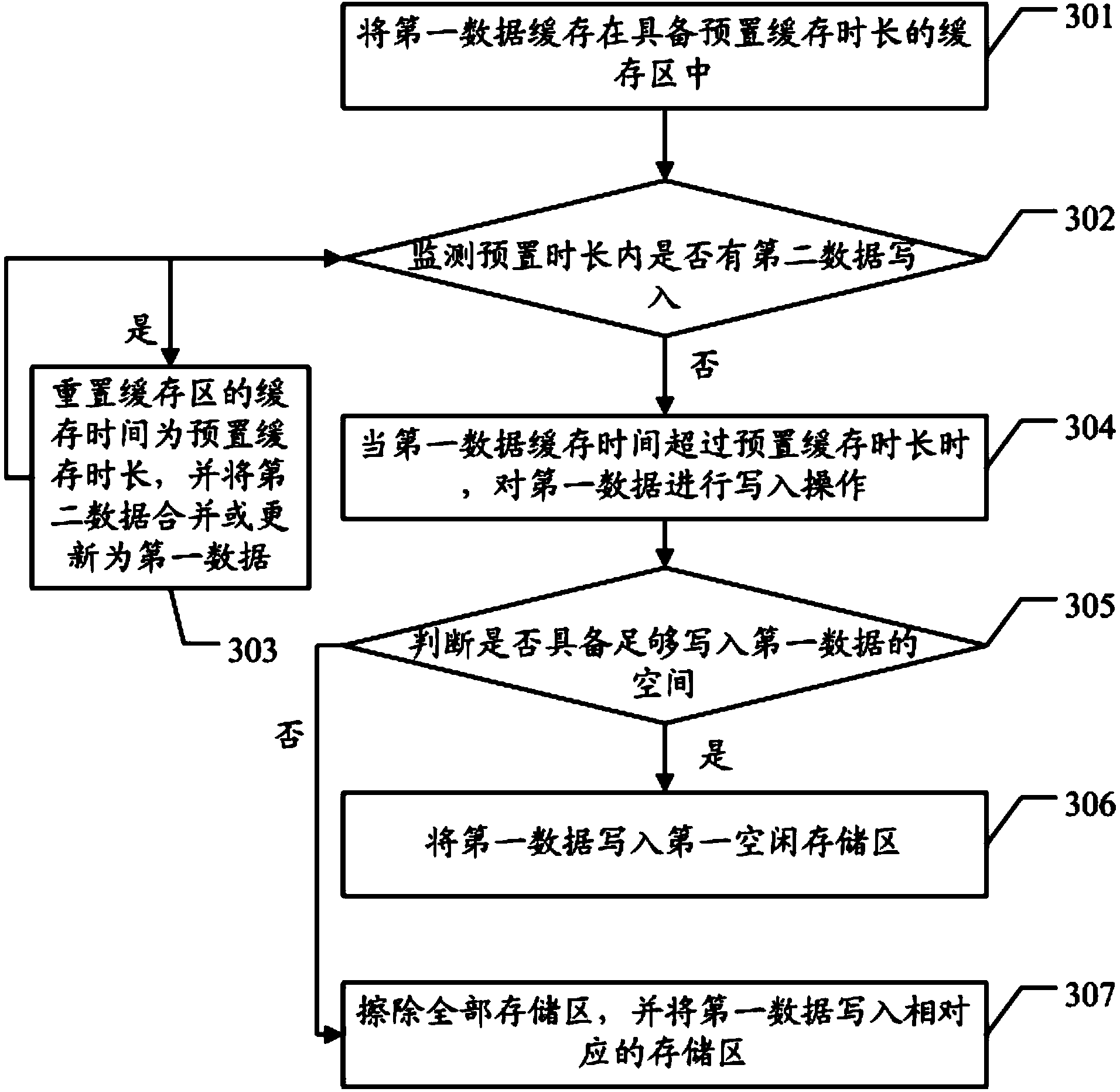

Method and device for writing data in memory chip

ActiveCN103838526AReduce the number of writes and erasesExtend working lifeInput/output to record carriersMemory chipFlash memory

The embodiment of the invention discloses a method and device for writing data in a memory chip. According to the method and device, whether enough space for writing of new data exists or not is judged, if yes, the new data are directly written in, and if not, an erasing operation is carried out. Therefore, the frequency of writing operations and the frequency of erasing operations in the Flash memory chip are further reduced, and the service life of the Flash memory chip is greatly prolonged. The method comprises the steps of (1) judging whether enough space for writing of first data exists or not , if yes, executing the step (2), if not, executing the step (3), (2) writing the first data in a first idle memory area, and (3) erasing all the memory areas, and writing the first data in the corresponding memory area.

Owner:GUANGZHOU HUAXIN ELECTRONICS TECH

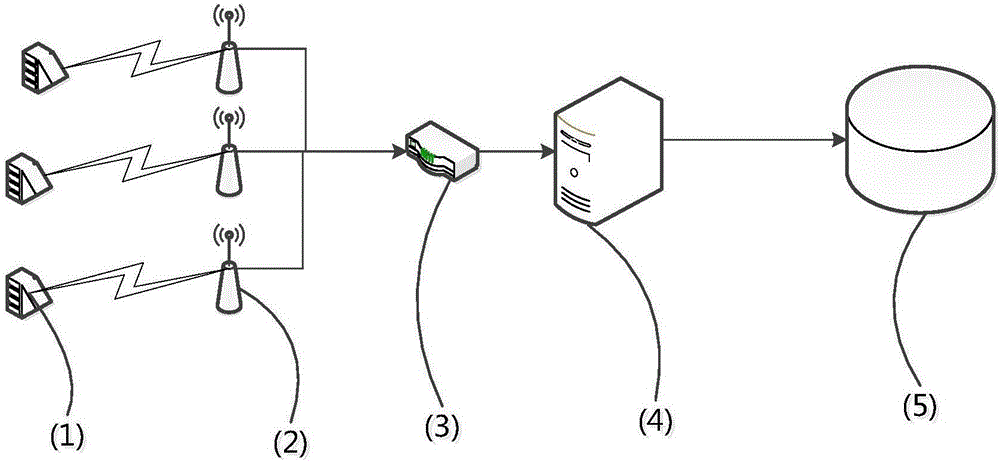

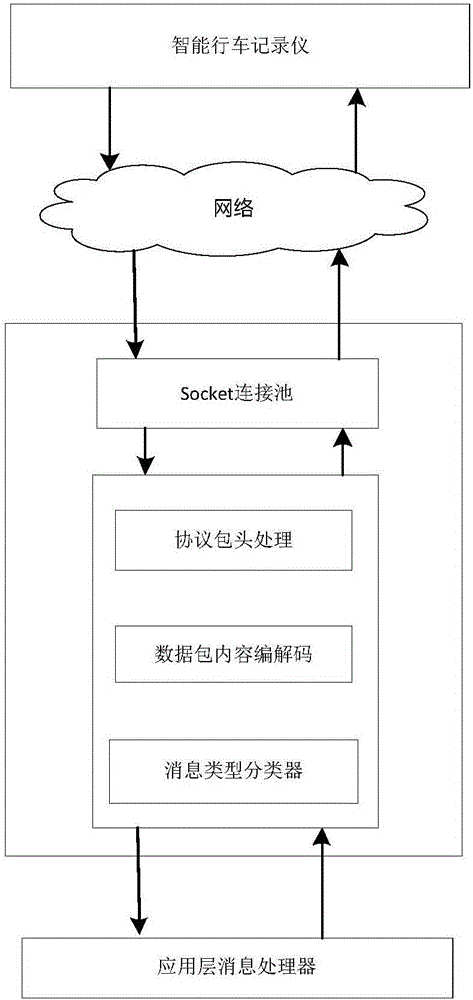

Massive and real-time tachograph data collection method and system

ActiveCN106530438AWrite lessReduce frequencyRegistering/indicating working of vehiclesAnalysis dataData acquisition

The invention discloses a massive and real-time tachograph data collection method. The method comprises the steps that a data collection server terminal receives the wireless connection emitted from bicycle tachograph terminal through a preset quantity of socket connection ponds; each complete data packet is decoded, the content, length and the concrete load of the message are analyzed; all types of tachograph data packets which have been received are transmitted to an upper layer application protocol to be processed; the application protocol sets different priority queries based on the data message types. Through the use of non-blocking data collection channel, and the reasonable processing of the collected data packets, the data collection capability of a single node server is tremendously elevated, and the data collection efficiency is elevated. Moreover through the data slicing and decoding, the data read-in and read-out frequency is reduced.

Owner:NINGBO INST OF TECH ZHEJIANG UNIV ZHEJIANG

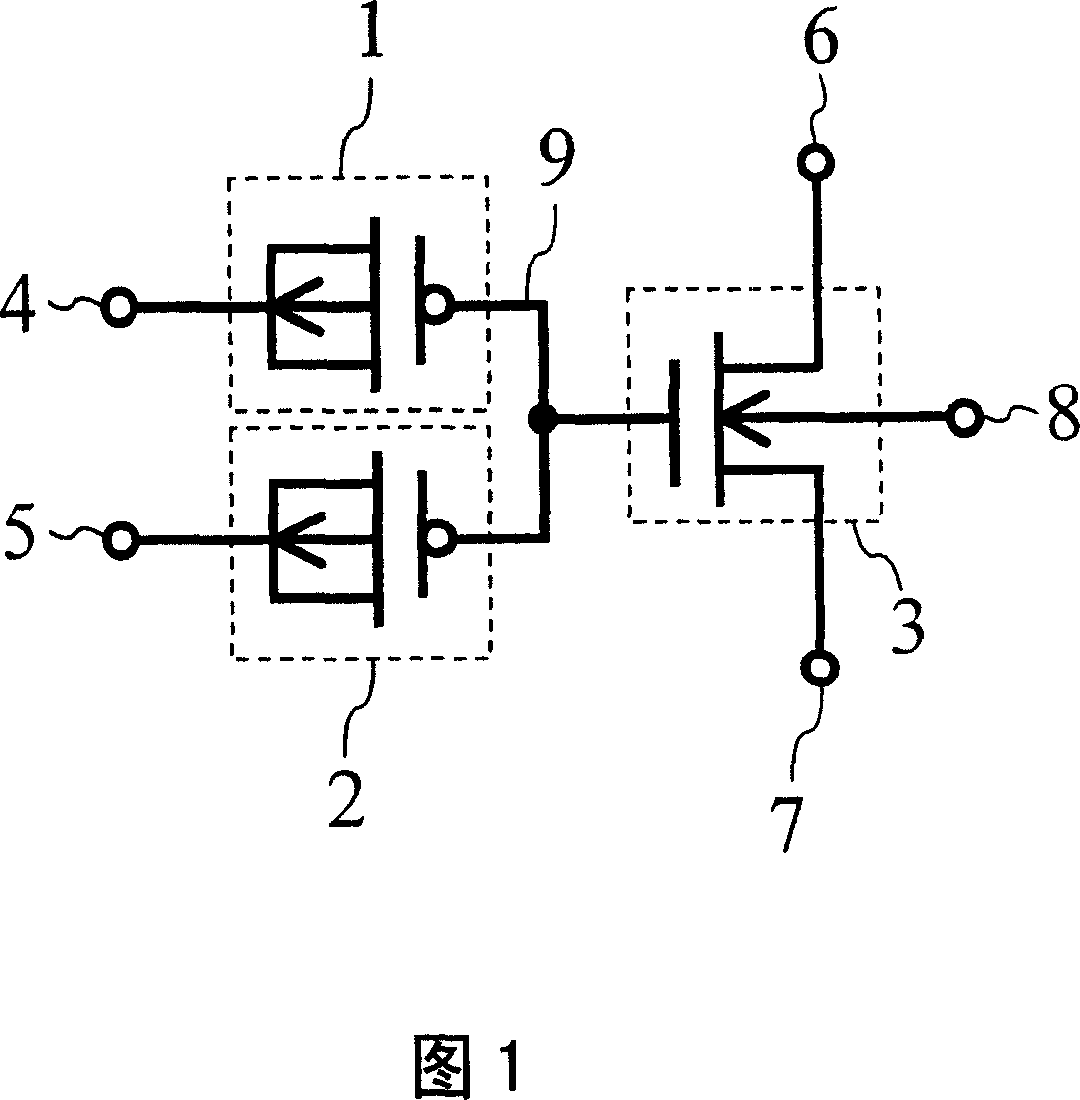

Nonvolatile semiconductor memory device

InactiveCN1941203AReduce areaIncrease the number of rewritesSolid-state devicesRead-only memoriesCapacitanceCoupling

A nonvolatile semiconductor memory device for storing data by accumulating charge in a floating gate (32) includes: a plurality of MOS transistors (24, 25, 26) sharing the floating gate (32). In the device, a PMOS (24) is used for coupling during writing and an n-type depletion MOS (DMOS) (25) is used for coupling during erasure. Coupling of channel inversion capacitance by the PMOS (24) is used for writing and coupling of depletion capacitance by the n-type DMOS (25) is used for erasure, thereby increasing the erase speed without increase of area, as compared to a conventional three-transistor nonvolatile memory element.

Owner:PANASONIC CORP

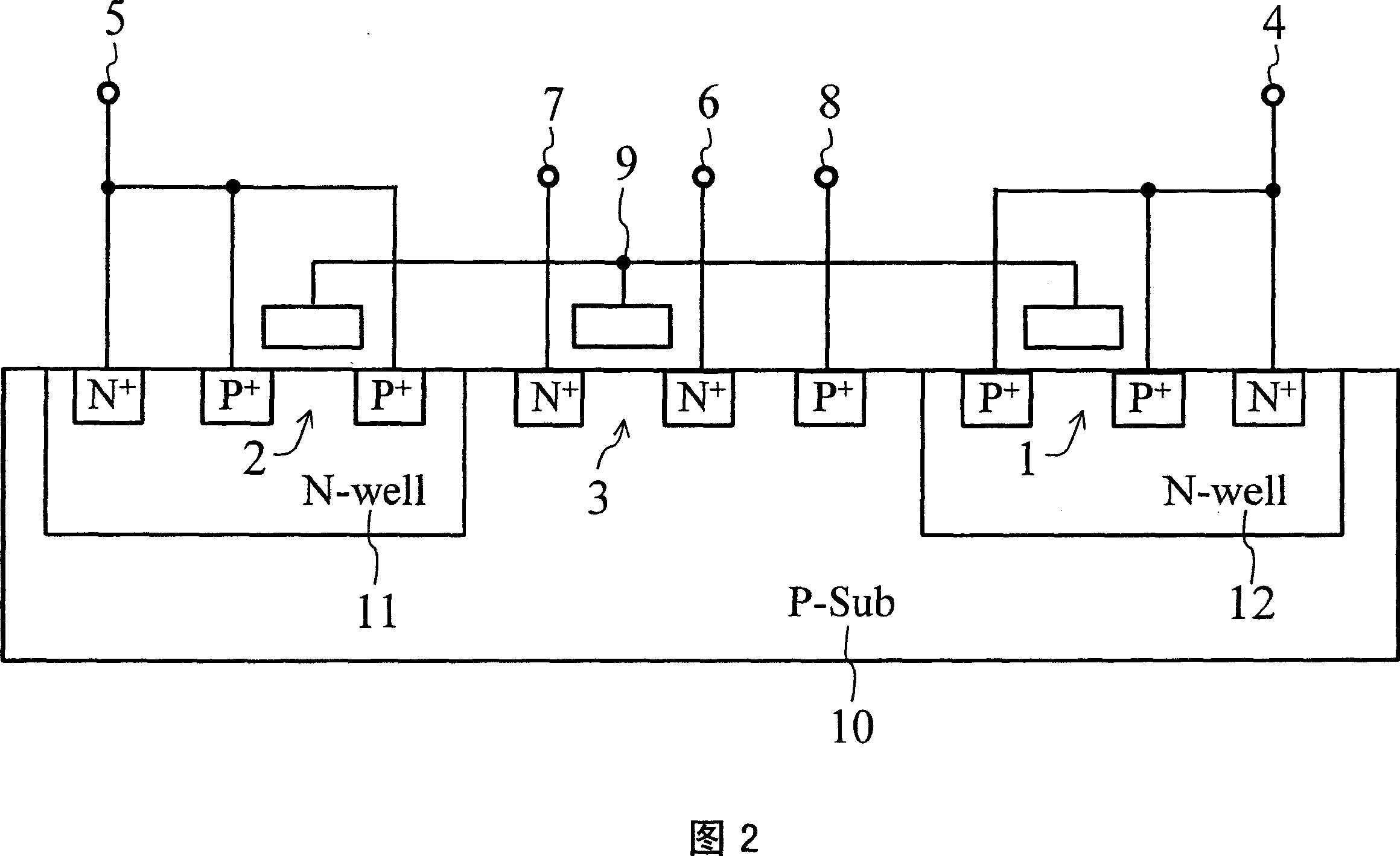

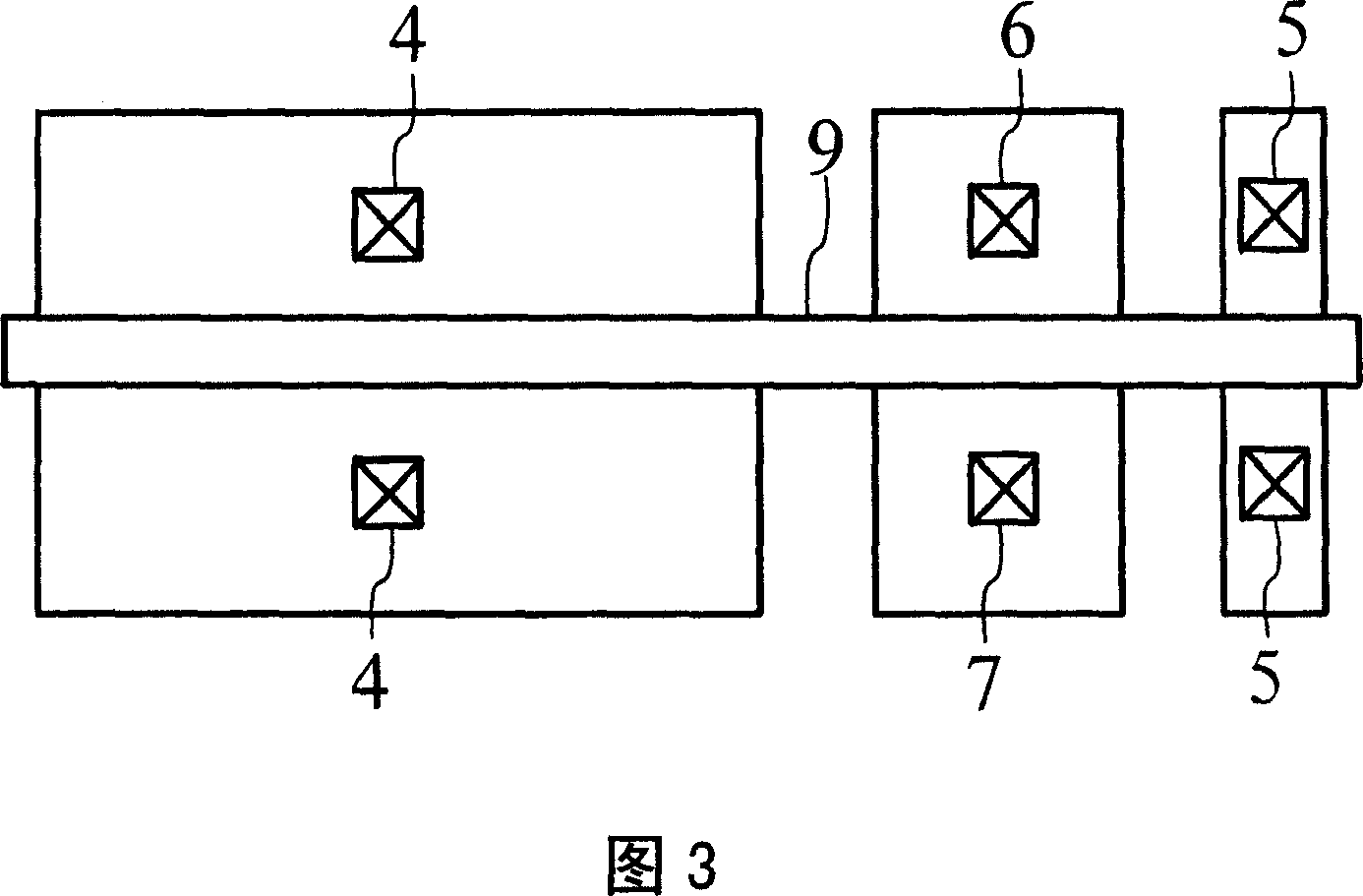

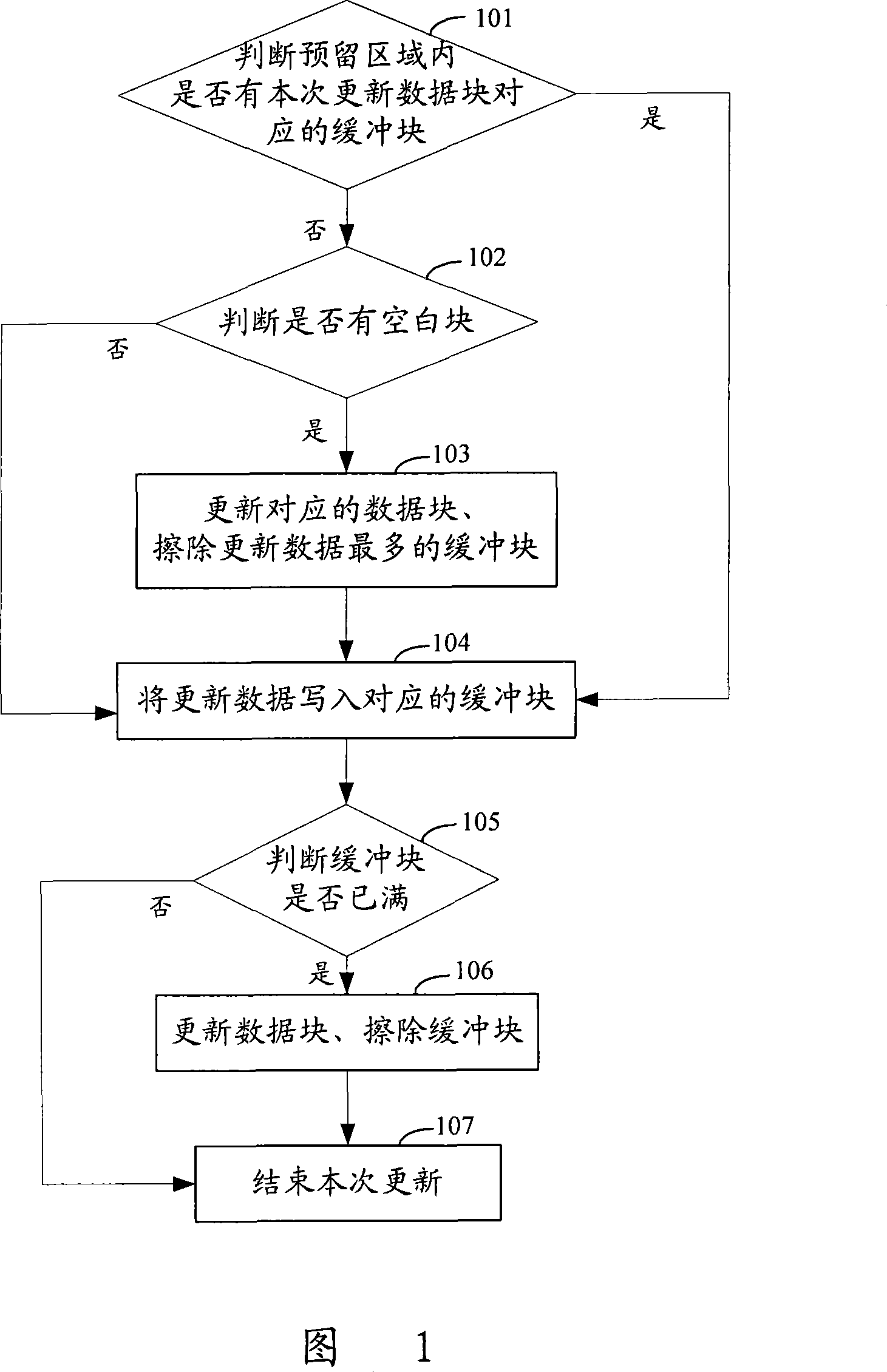

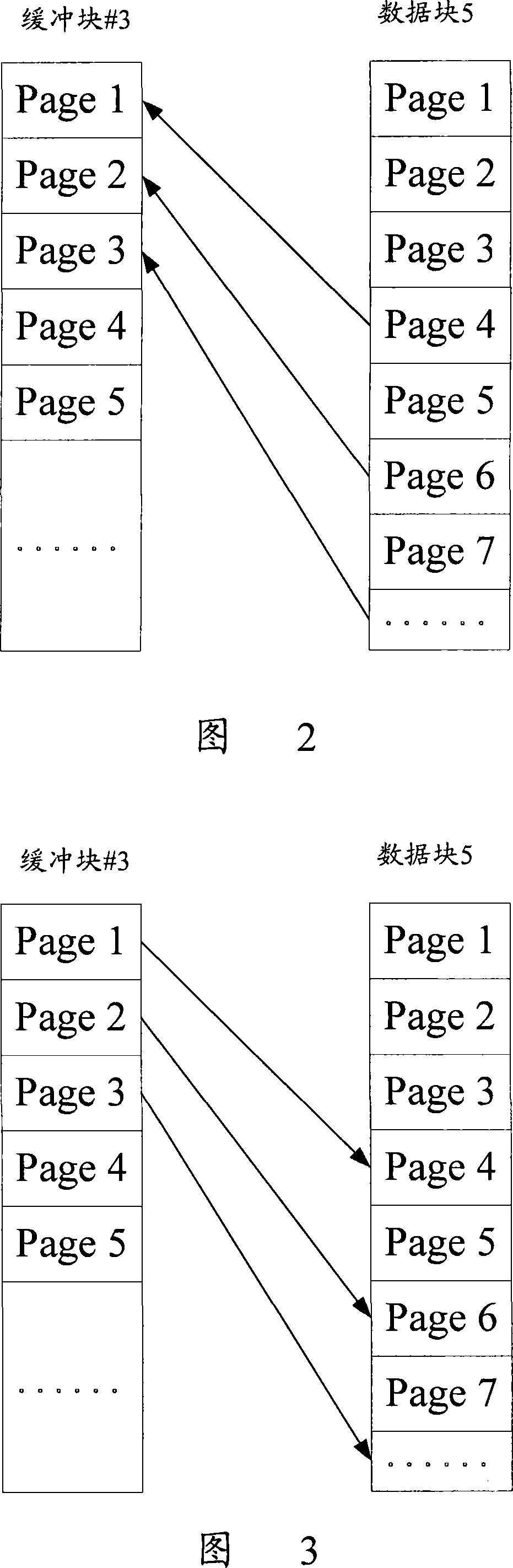

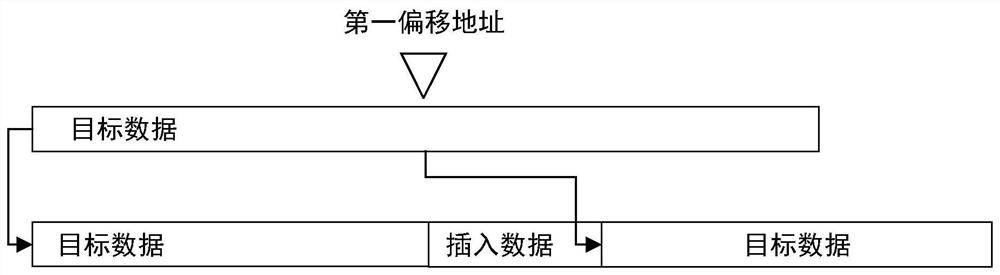

Data updating method and device

InactiveCN101216806AReduce frequent wipingWrite lessMemory adressing/allocation/relocationWeb pageDatabase

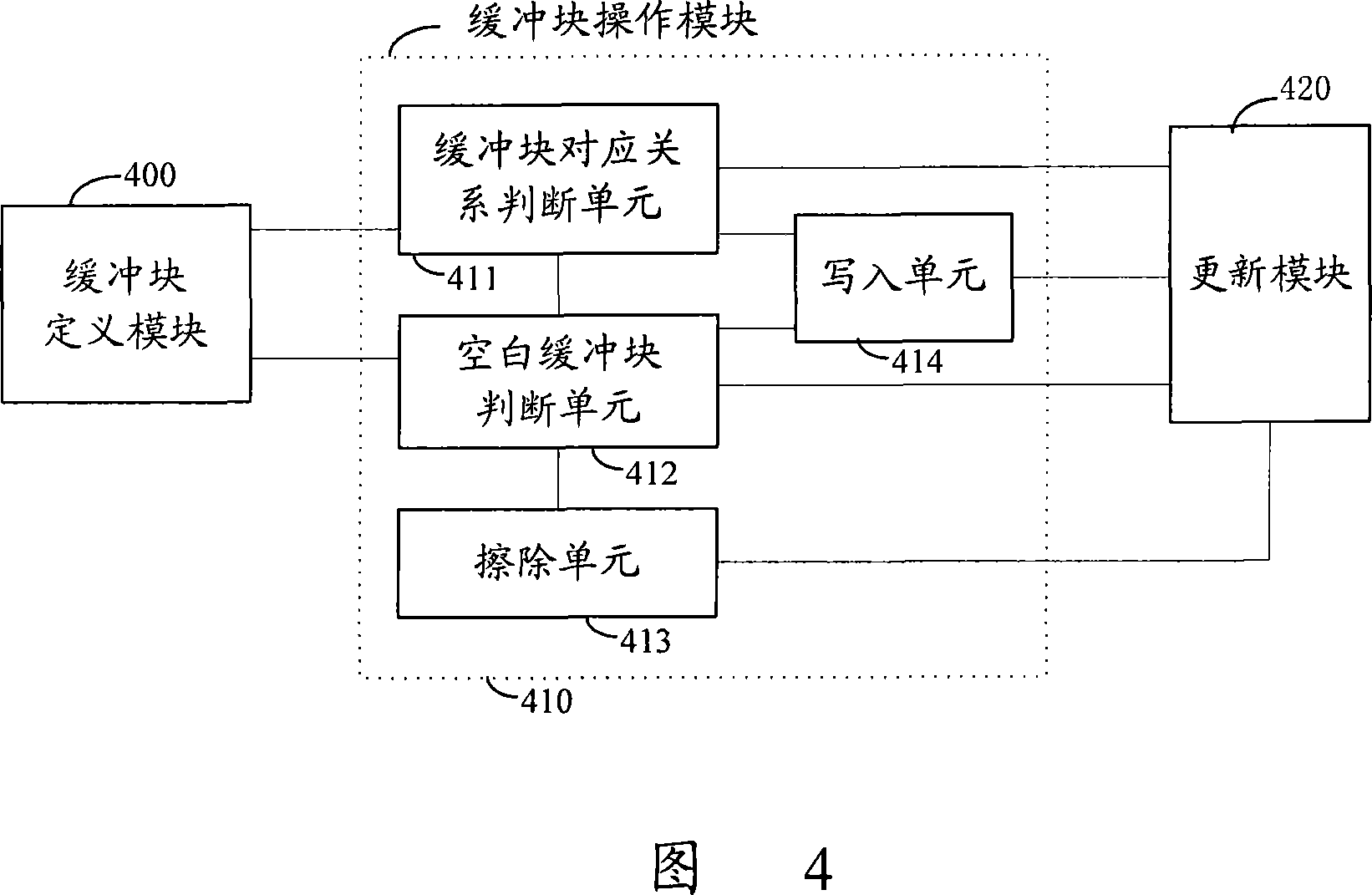

The invention discloses a data updating method, wherein, bumping blocks in preset quantity are arranged. The data updating method includes the following steps: updating data corresponding to any one block data is written to the bumping block corresponding to the block data, and the correlation between the position of the updating data in the bumping block and the position of the data to be updated in the corresponding block data; when any one bumping block is overwritten, the updating data in the bumping block is entirely written to the corresponding block data according to the correlation. The invention also discloses a data updating device at the same time. The data updating device comprises a bumping block definition module, a bumping block operation module and an updating module. The data updating method and the data updating device of the invention avoids the repetitiveness operation caused by rewriting the entire data after a corresponding web page in the block data is updated when updating the date of the web page in the block data, and increases the efficiency of data writing and updating.

Owner:VIMICRO CORP

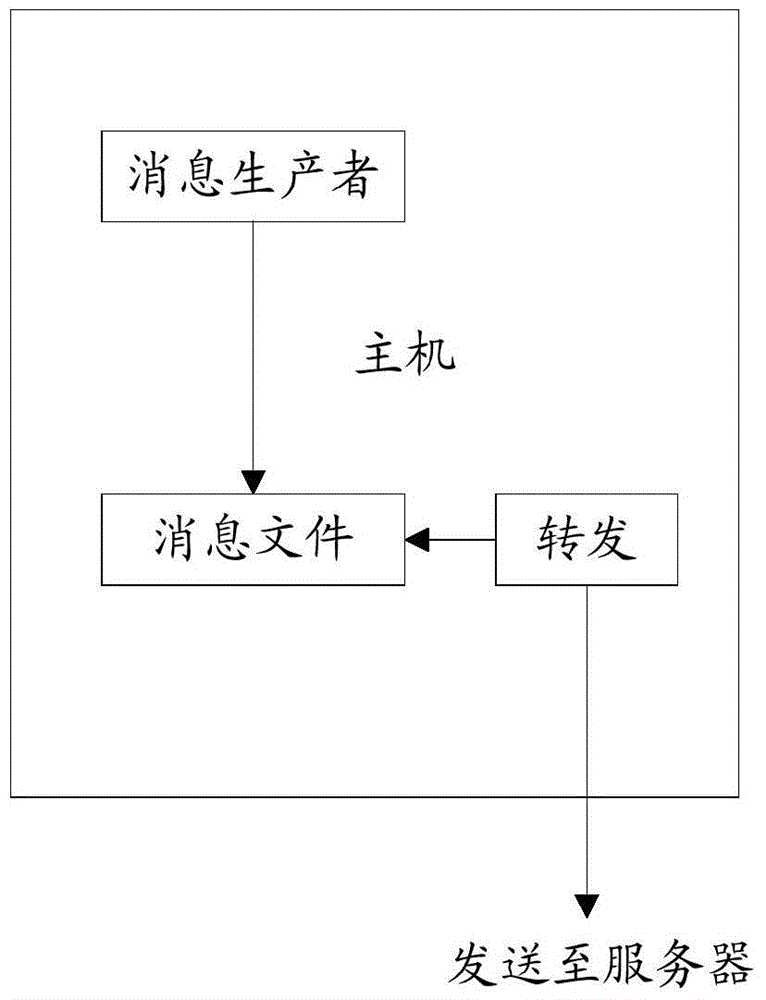

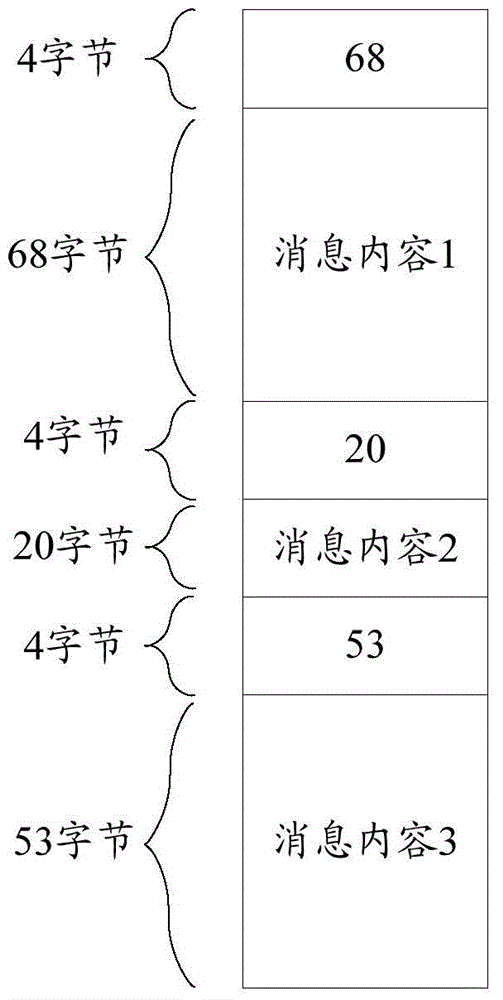

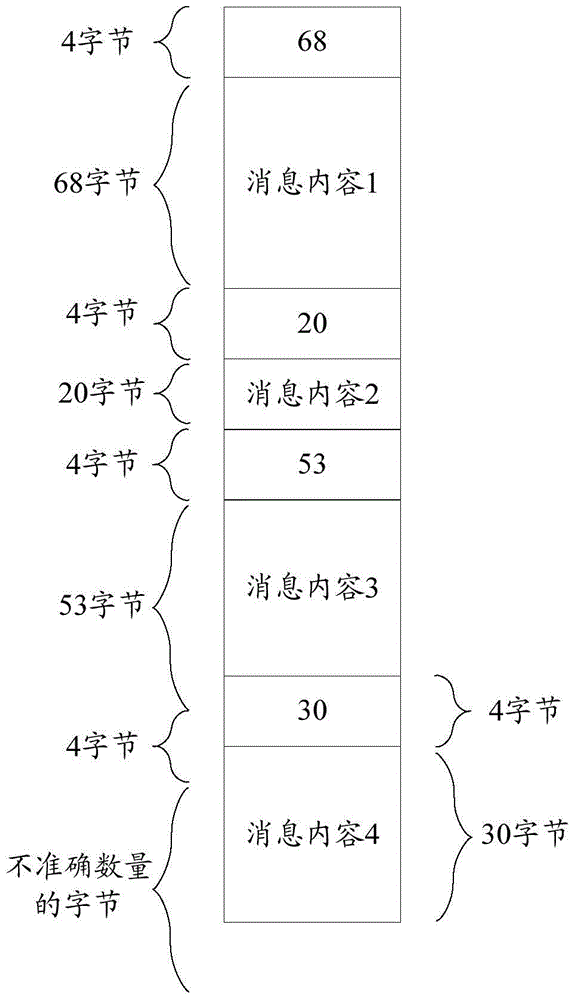

Data file writing method and system and data file reading method and system

ActiveCN103605479ATroubleshoot technical issues with uncorrupted dataWrite lessInput/output to record carriersError detection/correctionData file

The invention discloses a data file writing method and system and a data file reading method and system. The data file writing method is used for writing data to be written into a data file and comprises obtaining one or more than one datum to be written; setting a first character string; utilizing every datum to be written as a unit and adding the first character string into every unit, wherein the first character string is located at the front end of every unit and used for identifying every unit; writing every unit into the data file. According to the data file writing method and system and the data file reading method and system, undamaged data in the data file can still be searched to be read under the condition that a part of data in the data file are damaged.

Owner:BEIJING QIHOO TECH CO LTD

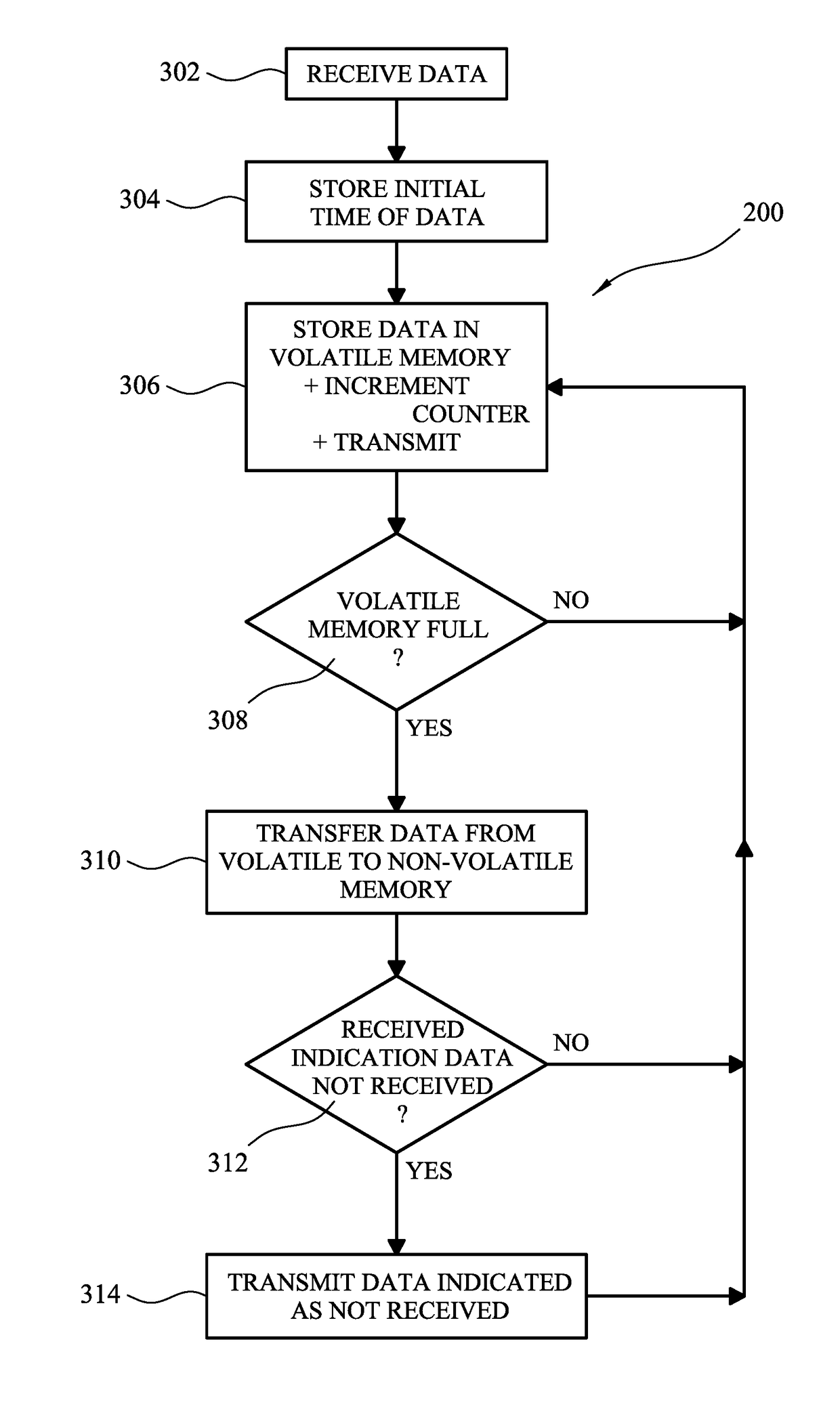

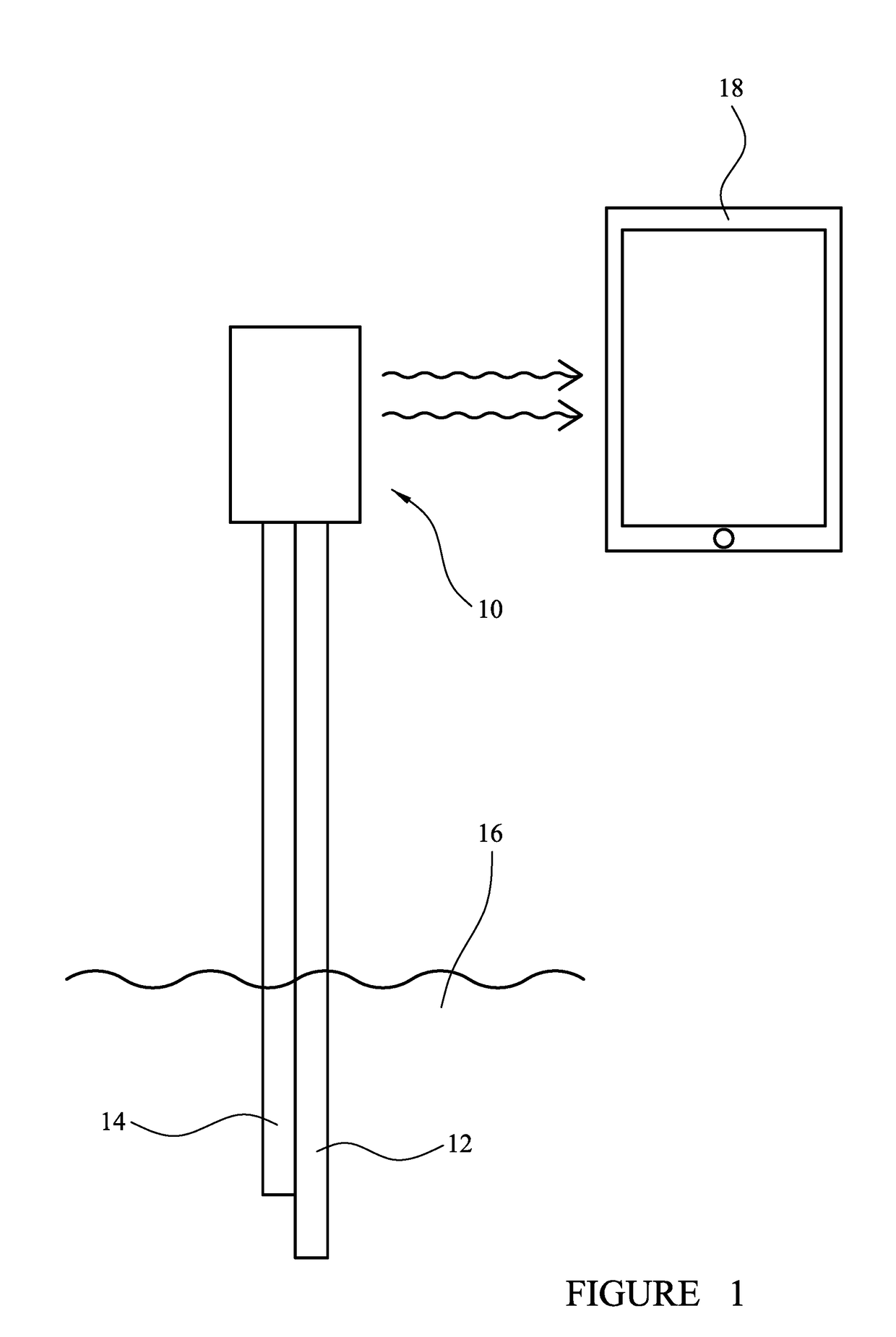

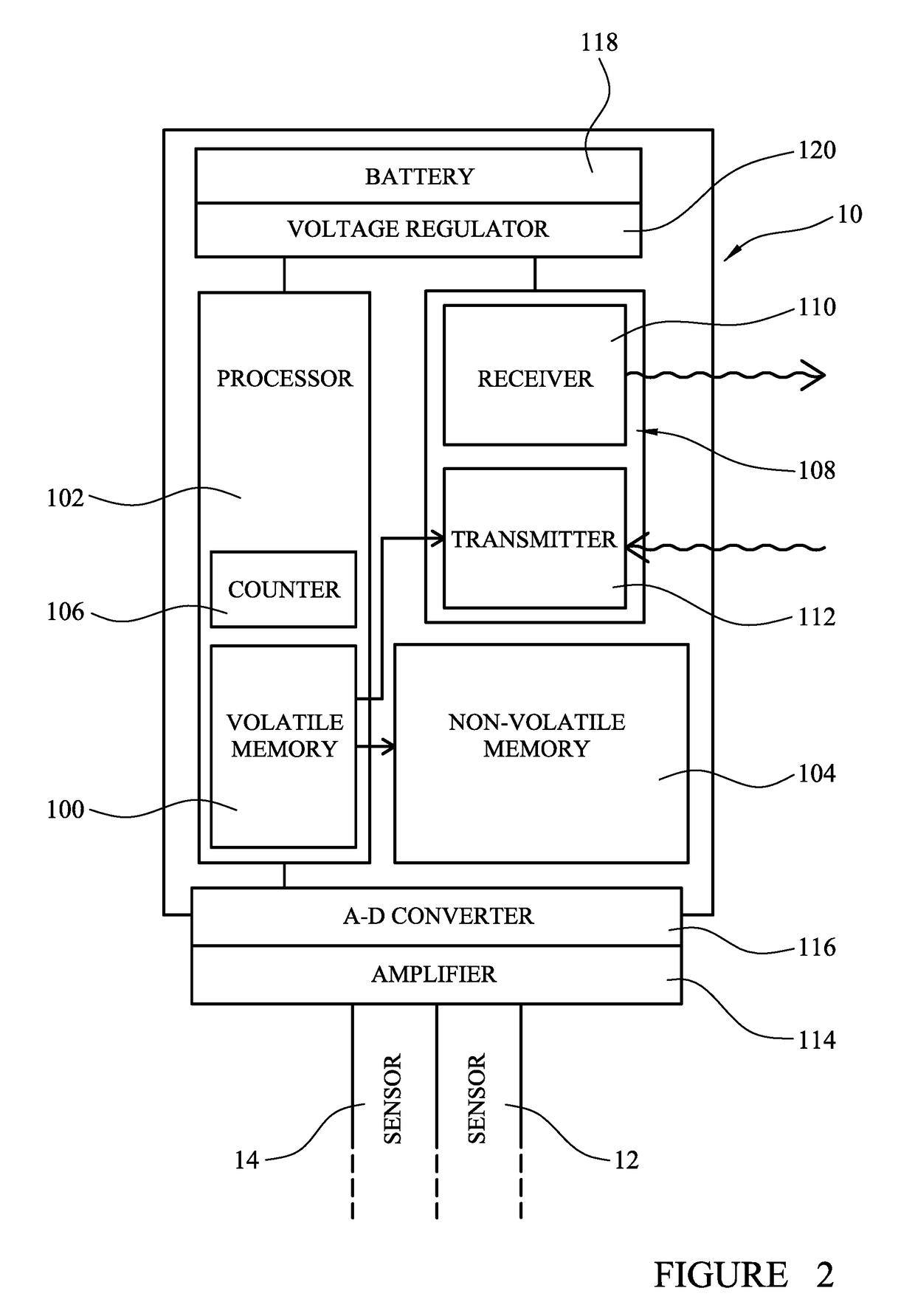

A sensor interface for interfacing with a sensor

ActiveUS20180045666A1Write lessMeet high power requirementsMemory architecture accessing/allocationPower managementData storingData value

A sensor interface for interfacing with a sensor such as an electrochemical sensor, a temperature sensor or the like in which the interface comprises a memory configured to store data received at the interface from a sensor. The sensor interface is configured to assess the difference between data values in the memory, and to transmit advertising packets at a rate dependent on the difference between the values. The sensor interface includes a volatile memory and a non-volatile memory. The volatile memory is configured to store data received at the sensor interface from a sensor. The non-volatile memory is configured to store data stored in the volatile memory. The sensor interface is configured such that: data received at the sensor is stored in the volatile memory forming stored data until the volatile memory is substantially full and then at least some of the stored data is transferred to the non-volatile memory.

Owner:CAMLAB

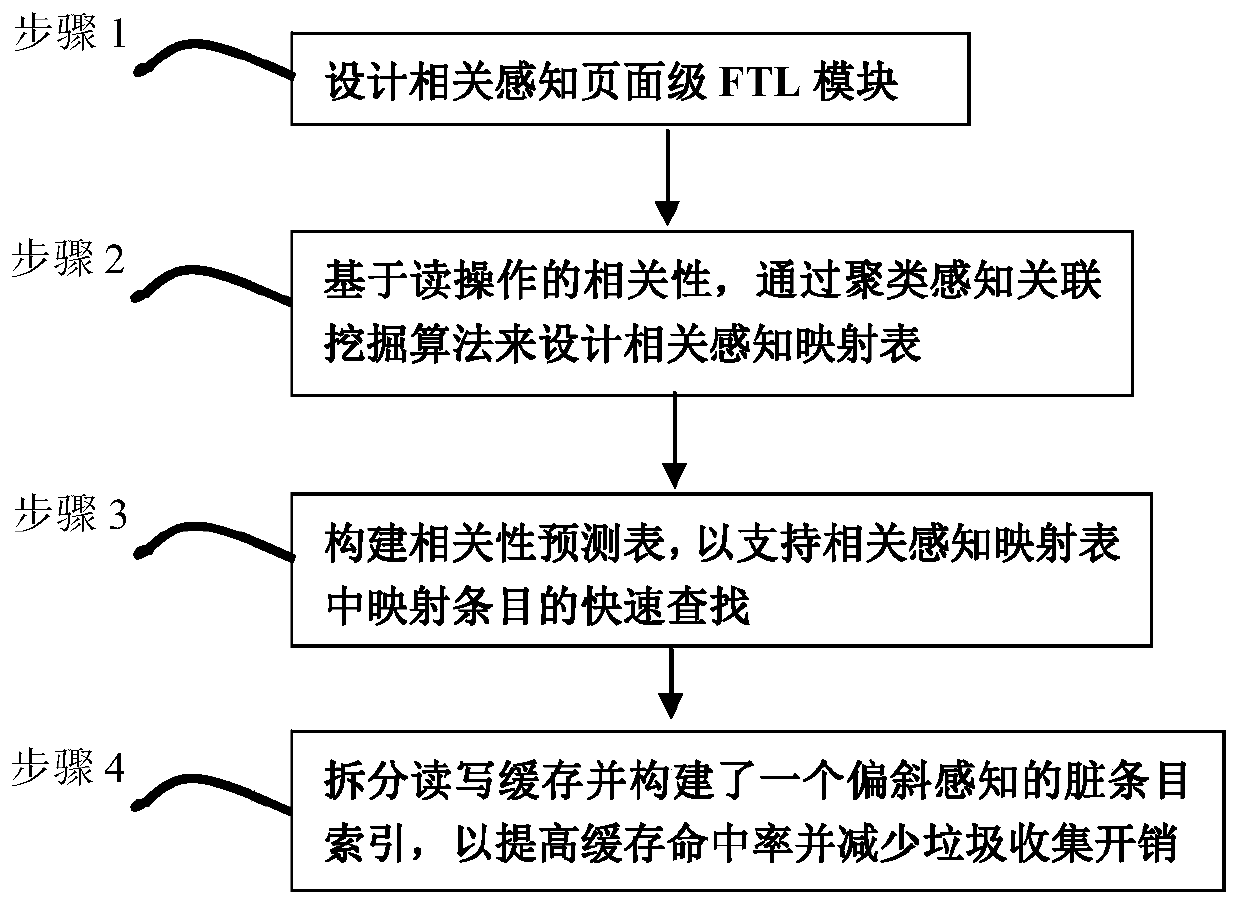

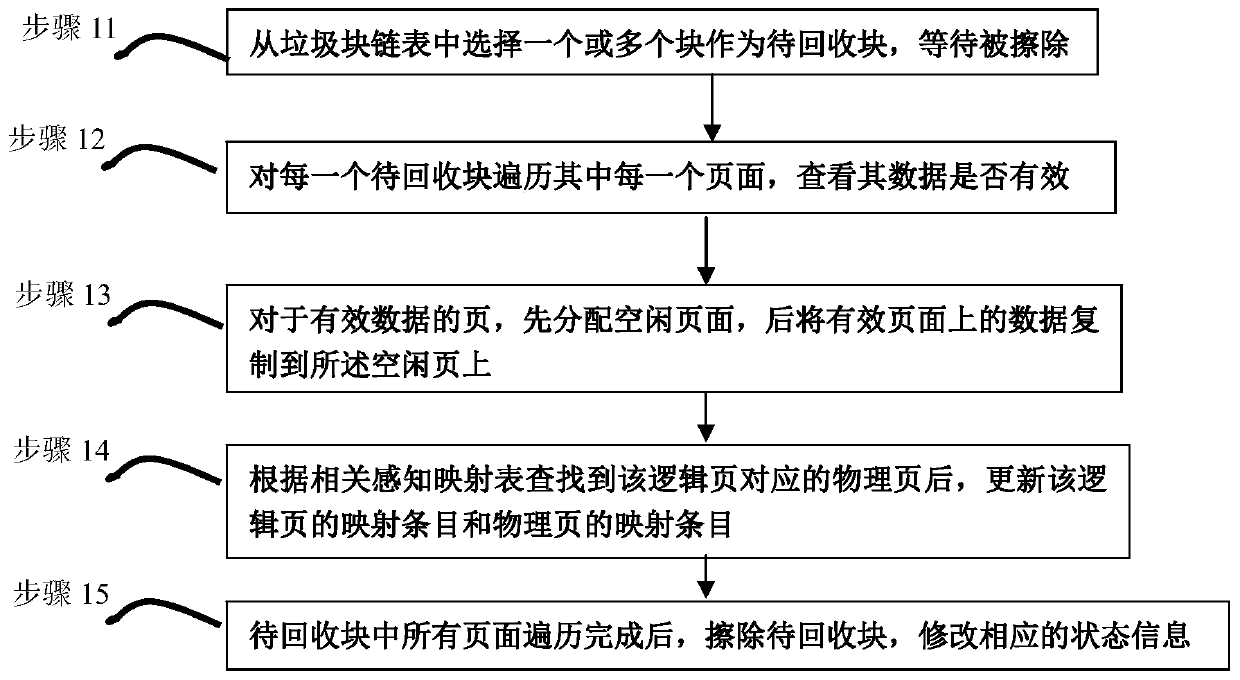

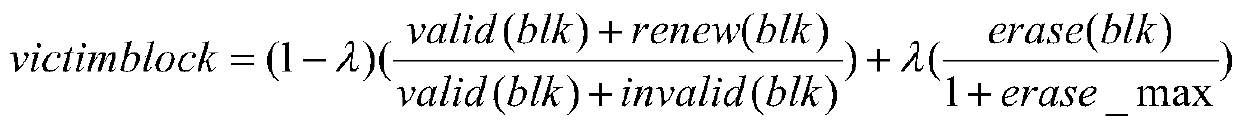

Page-level FTL solid-state hard disk performance optimization method based on correlation perception

ActiveCN109783398AImprove localityImprove performanceMemory adressing/allocation/relocationPhysical addressPattern perception

The invention discloses a page-level FTL solid state disk performance optimization method based on correlation perception. In an SSD based on a flash memory, an FTL is adopted to redirect write content to an idle physical address, and a mapping table from a logic address to the physical address is managed, which seriously affects the performance of the SSD based on the flash memory. In order to improve the performance based on the flash SSD, I / O correlation in workloads is utilized, a related perception page level FTL technology is provided, and a related perception mapping table is designed and a correlation prediction table is constructed based on correlation of reading operation so as to support rapid searching of mapping entries in the related perception mapping table. Moreover, the read-write cache is split, and a skew-perceived dirty item index is constructed, so that the cache hit rate is increased, and the garbage collection overhead is reduced. According to the method, the page mapping efficiency can be remarkably improved, the read-write performance is improved, and the junk collection overhead is reduced by using the semantic link related perception page level FTL method.

Owner:SHANGHAI MARITIME UNIVERSITY

Magnetic cell and method for programming magnetic memory

ActiveCN103490006AReduce the required powerLow conductivityMagnetic-field-controlled resistorsGalvano-magnetic material selectionOxideSemiconductor

In one embodiment, a magnetic cell used for a semiconductor device comprises a reference layer, a free layer and a non-magnetic spacer layer disposed between the reference layer and the free layer. The non-magnetic spacer layer comprises two-component, three-component or multi-component alloy oxide material which comprises MgO containing one or multiple other elements selected from the group formed by Ru, Al, Ta, Tb, Cu, V, Hf, Zr, W, Ag, Au, Fe, Co, Ni, Nb, Cr, Mo and Rh.

Owner:SAMSUNG ELECTRONICS CO LTD

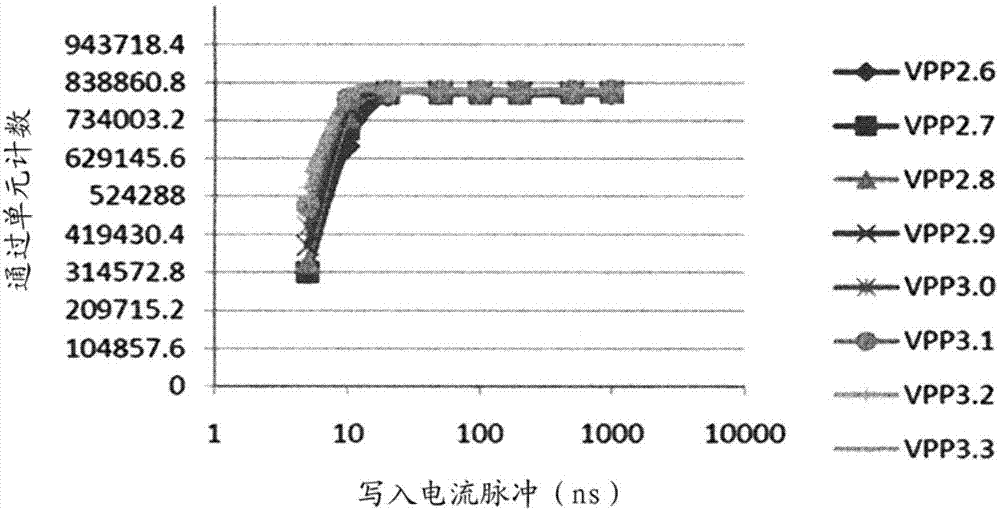

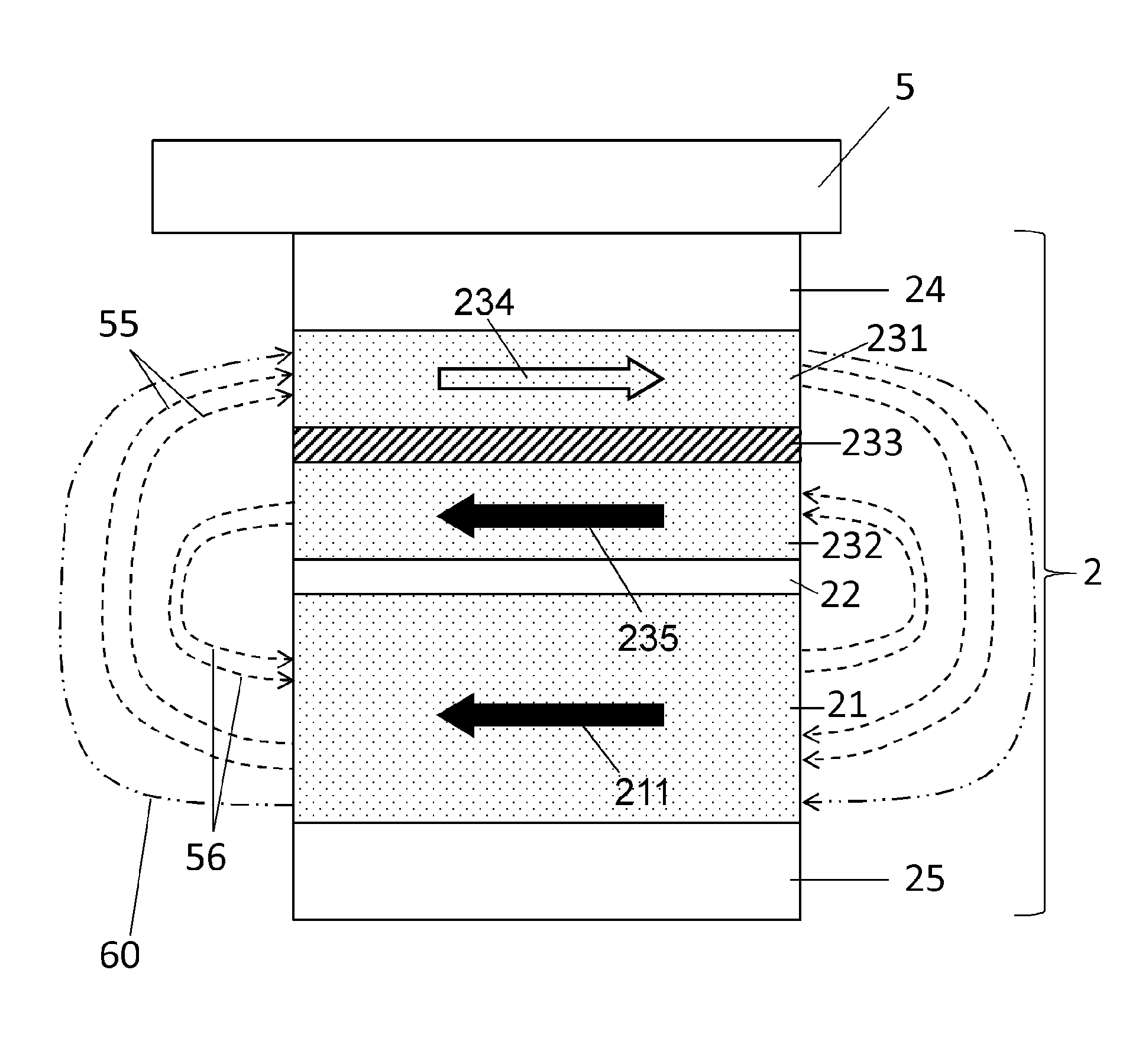

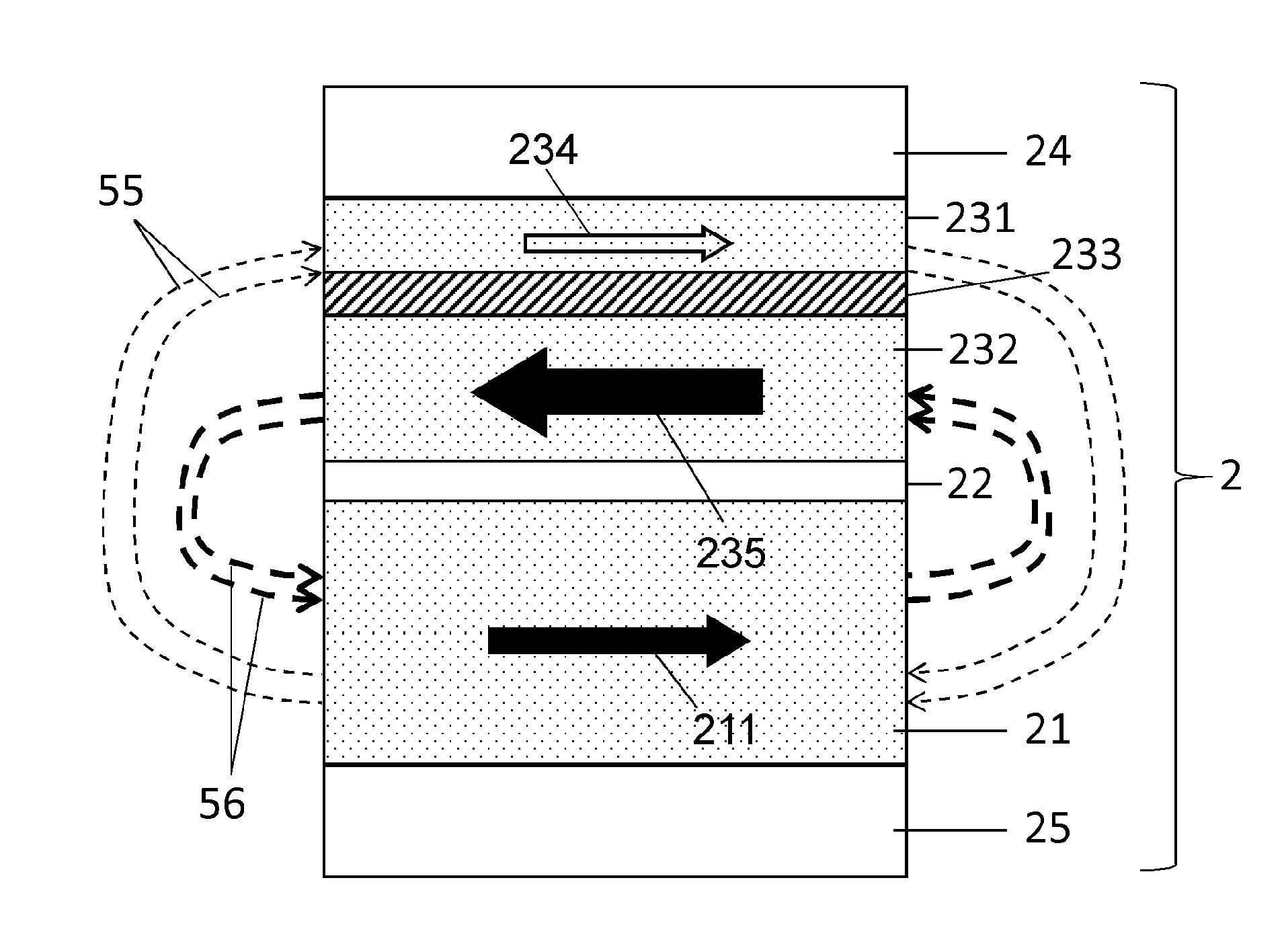

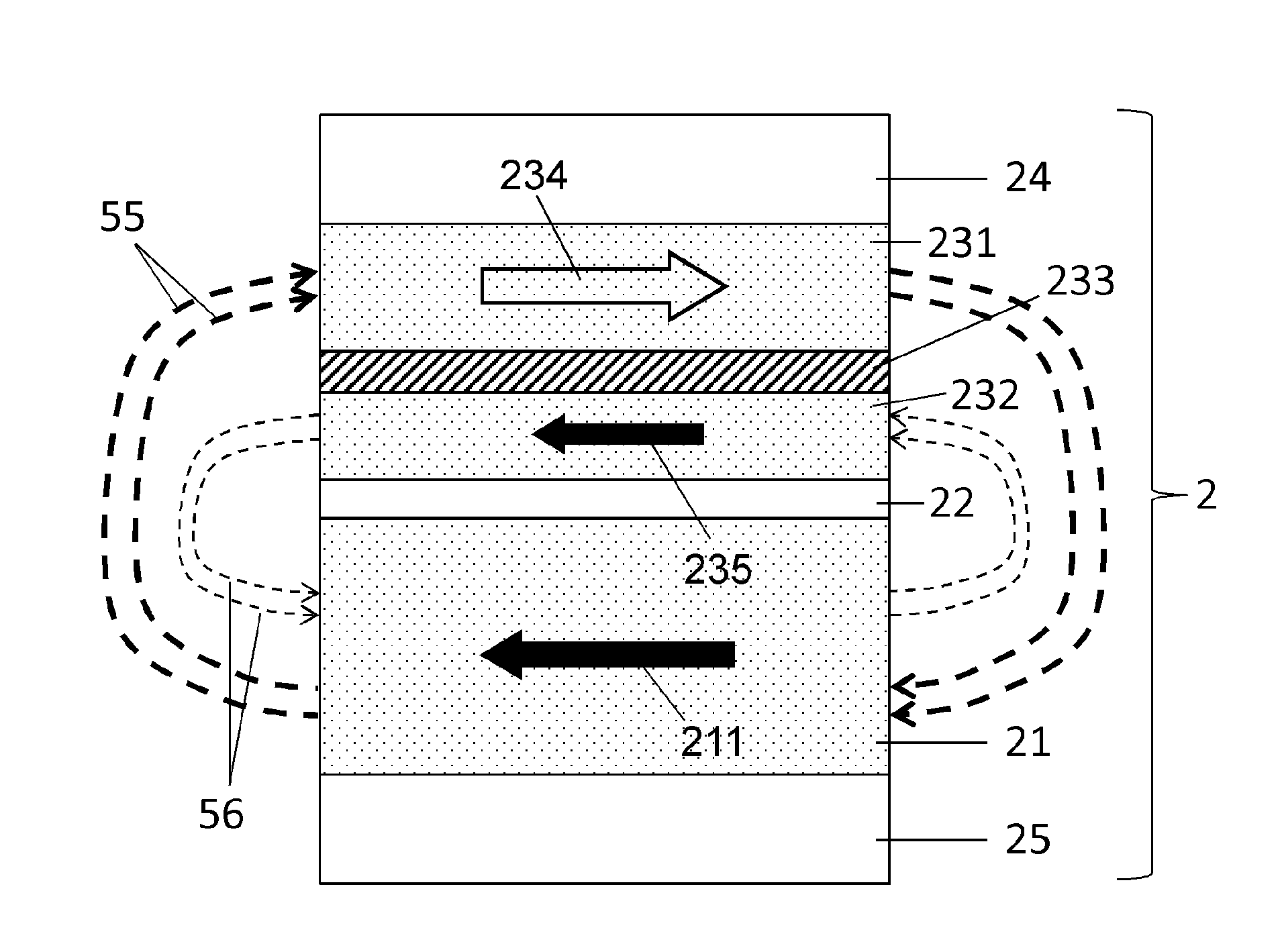

Magnetic random access memory (mram) cell and method for reading the mram cell using a self-referenced read operation

InactiveCN103035280AReduce power consumptionWrite lessDigital storageStatic random-access memoryRandom access memory

The present disclosure concerns a magnetic random access memory (MRAM) cell (1) comprising a magnetic tunnel junction (2) comprising a synthetic storage layer (23); a sense layer (21) having a sense magnetization (211) that is reversible; and a tunnel barrier layer (22) between the sense layer (21) and the storage layer (23); wherein a net local magnetic stray field couples the storage layer (23) with the sense layer (21); and wherein the net local magnetic stray field being such that the net local magnetic stray field coupling the sense layer (21) is below 50 Oe. The disclosure also pertains to a method for writing and reading the MRAM cell (1). The disclosed MRAM cell (1) can be written and read with lower consumption in comparison to conventional MRAM cells.

Owner:CROCUS TECHNOLOGY

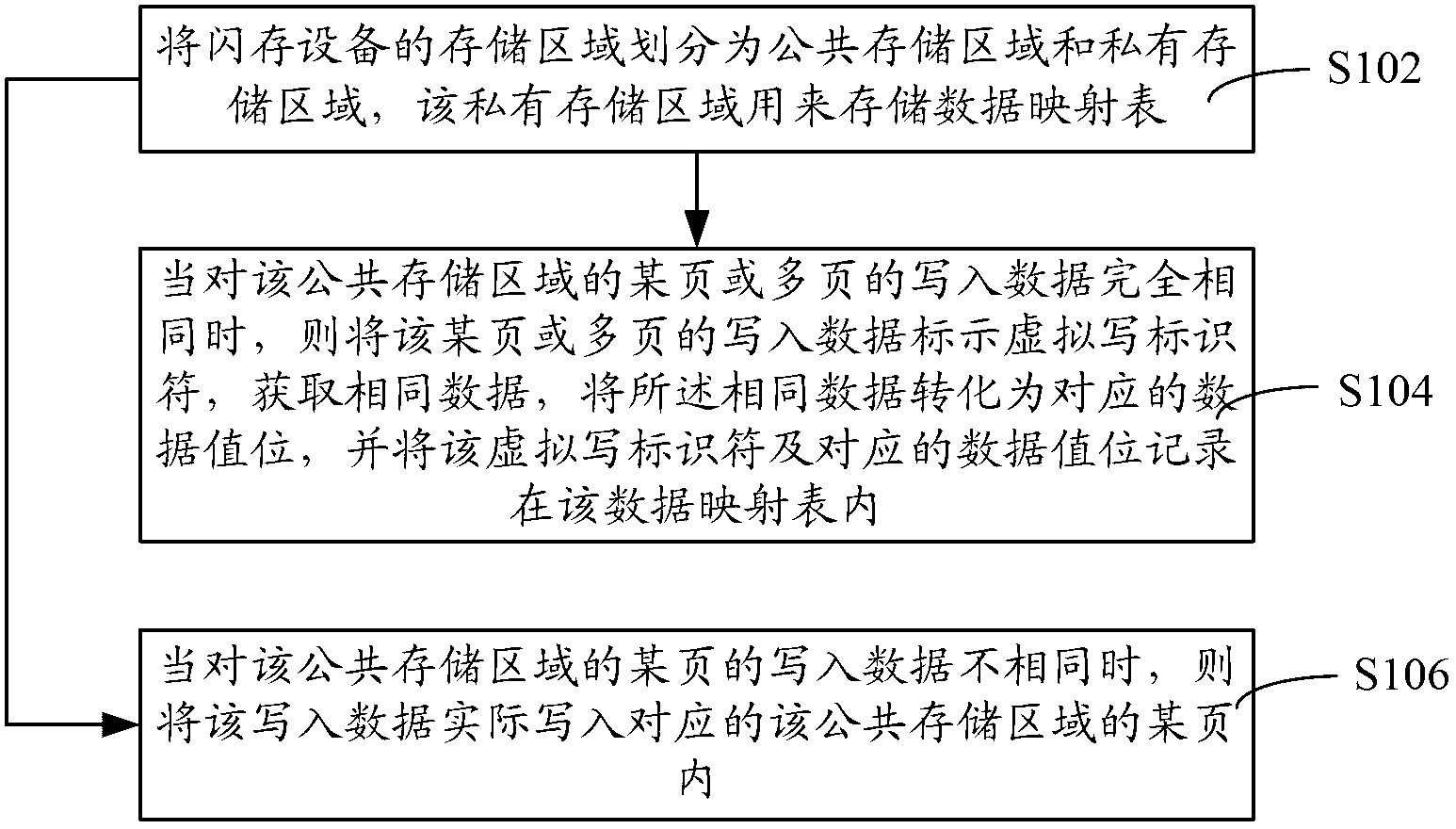

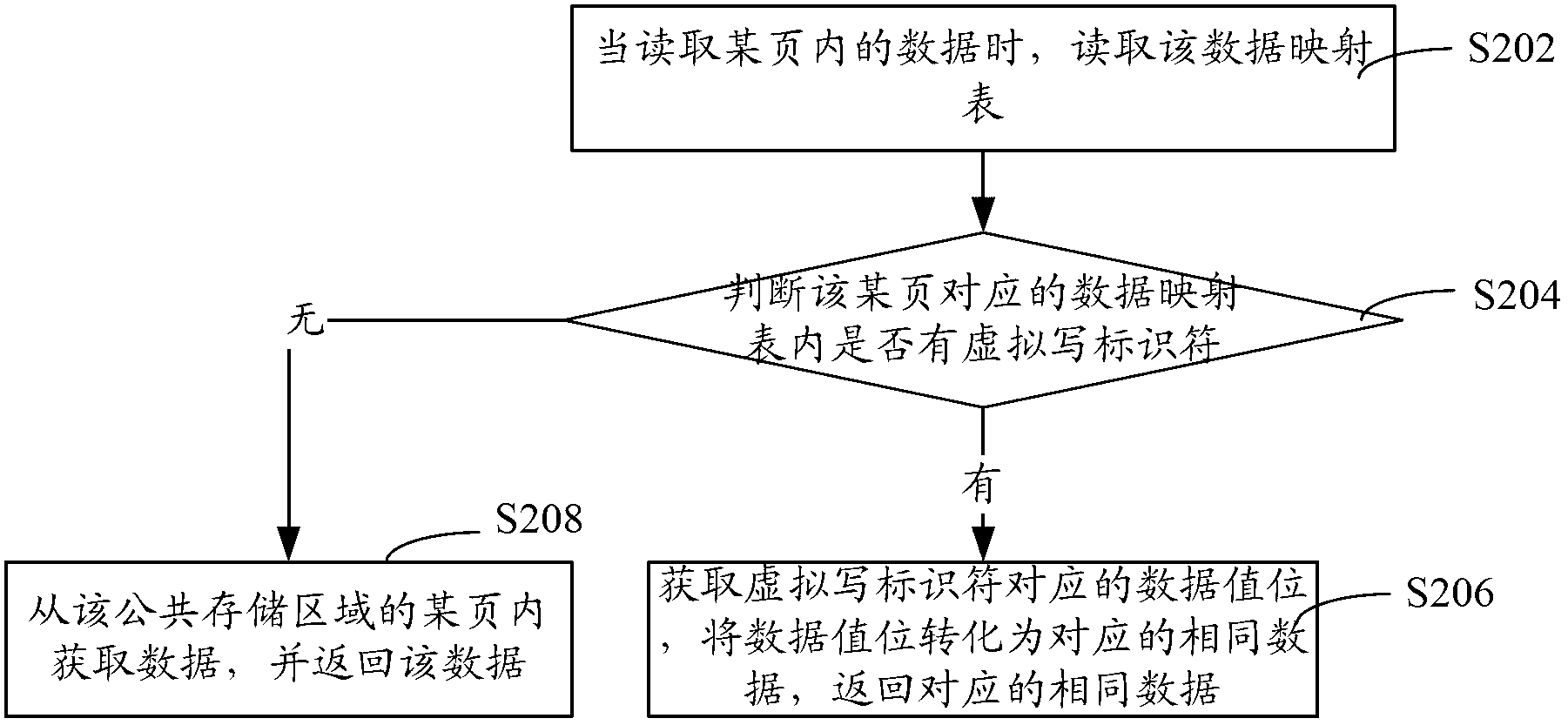

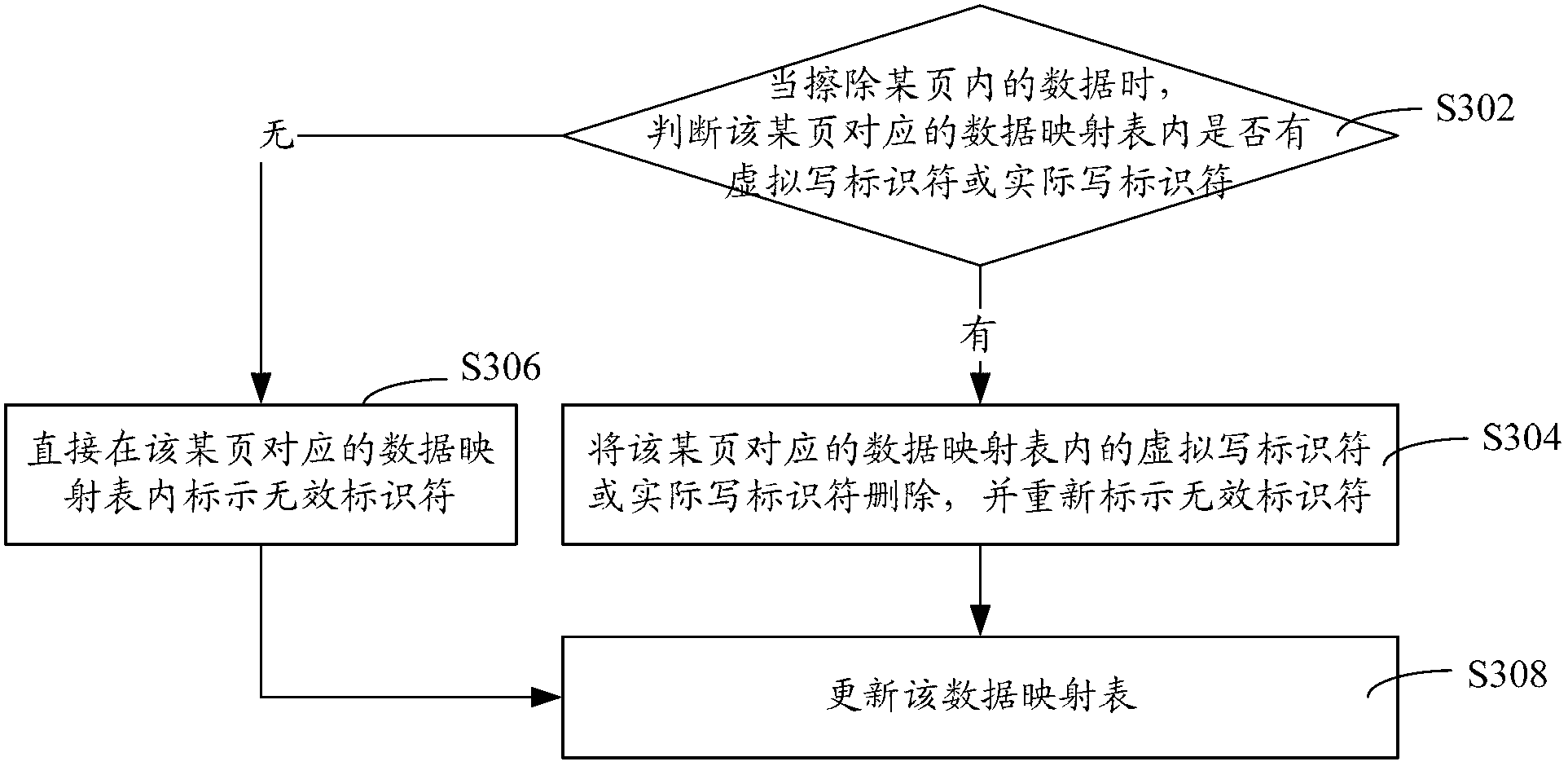

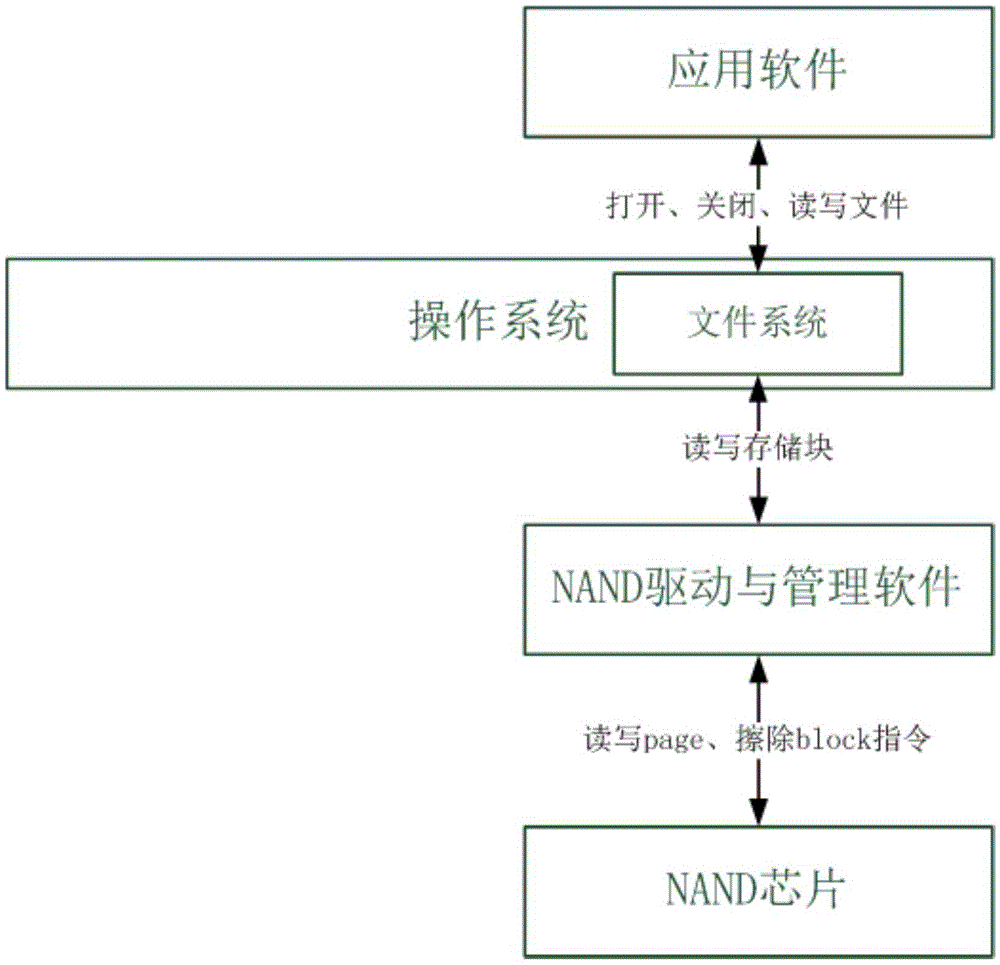

Method and system for data management of flash memory equipment

ActiveCN103257928AWrite lessSave spaceMemory adressing/allocation/relocationData managementData value

Owner:SHENZHEN NETCOM ELECTRONICS CO LTD

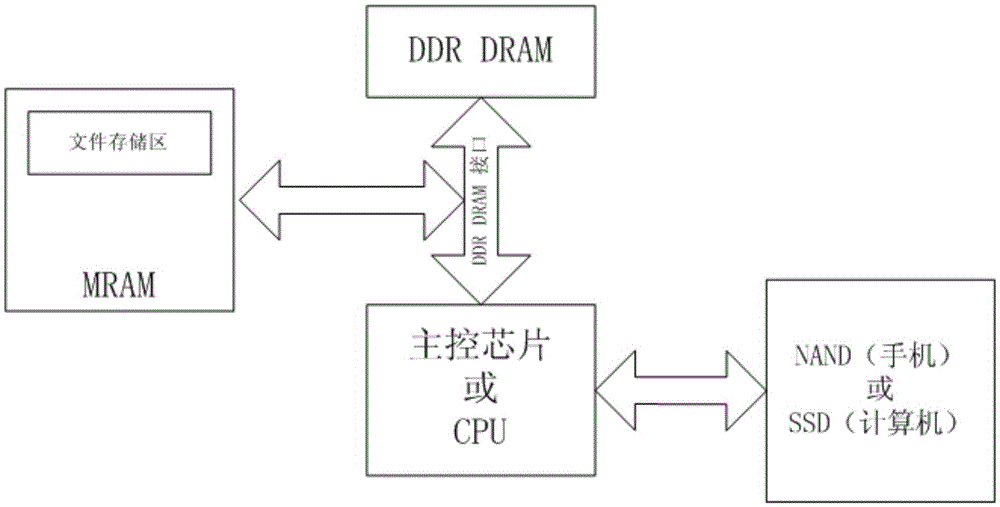

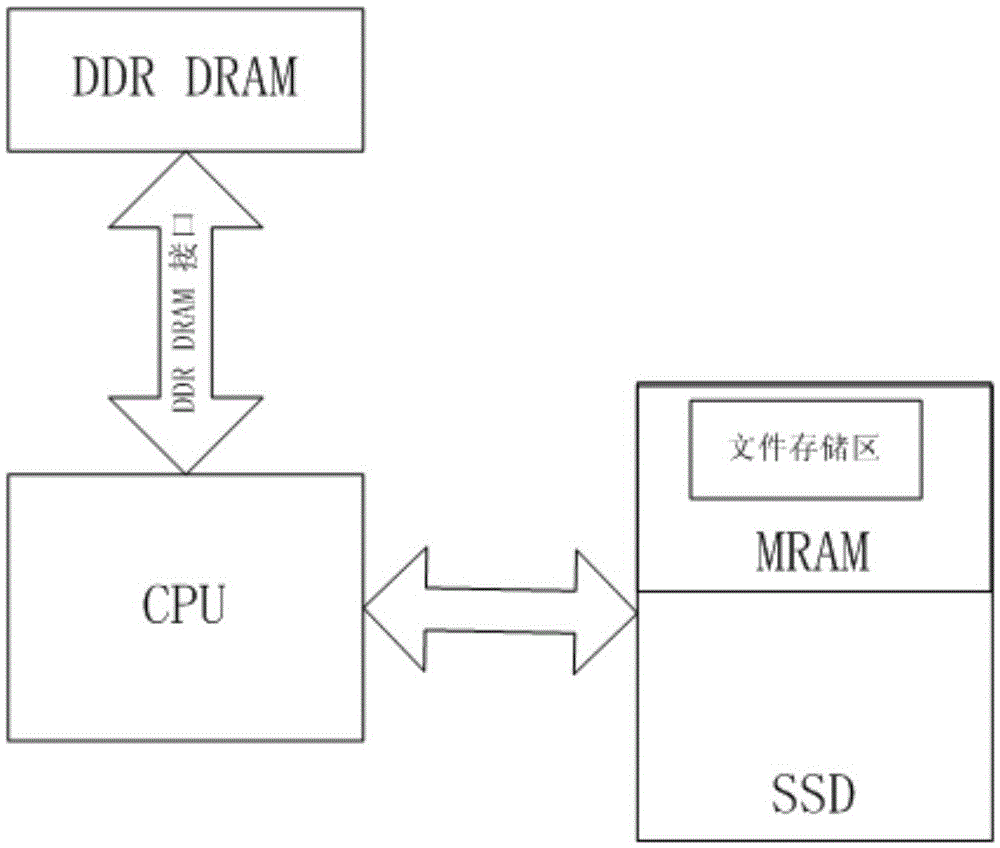

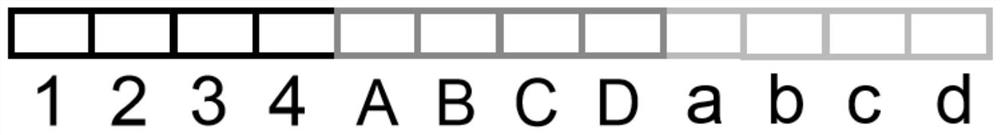

Method for dynamically managing file memory area by nonvolatile random access memory chip

ActiveCN105630410AIncrease profitReduce the burden onInput/output to record carriersRandom access memoryDynamic management

The invention provides a method for dynamically managing a file memory area by a nonvolatile random access memory chip. The file memory area consists of N sub memory areas which have continuous addresses and are connected, a plurality of continuous memory blocks which are adjacent to an ith sub memory in an (i+1)th sub memory area are expropriated, or a plurality of continuous memory blocks which are adjacent to the ith sub storage area in an (i-1) sub storage area are expropriated. The invention also provides a memory structure, which utilizes an MRAM (Magnetic Random Access Memory) to store small files. The method for dynamically managing the file memory area and the memory structure which utilizes the MRAM to storage the small files are characterized in that the adjacent sub memory areas are managed by a dynamic management method; when the blocks of one sub memory area are used up or an amount of idle memory blocks is smaller than a set value, the memory space of the adjacent sub memory area is expropriated; and according to an application environment, the amount of the memory blocks of the sub memory areas can be dynamically regulated so as to improve the use ratio of the memory space.

Owner:SHANGHAI CIYU INFORMATION TECH CO LTD

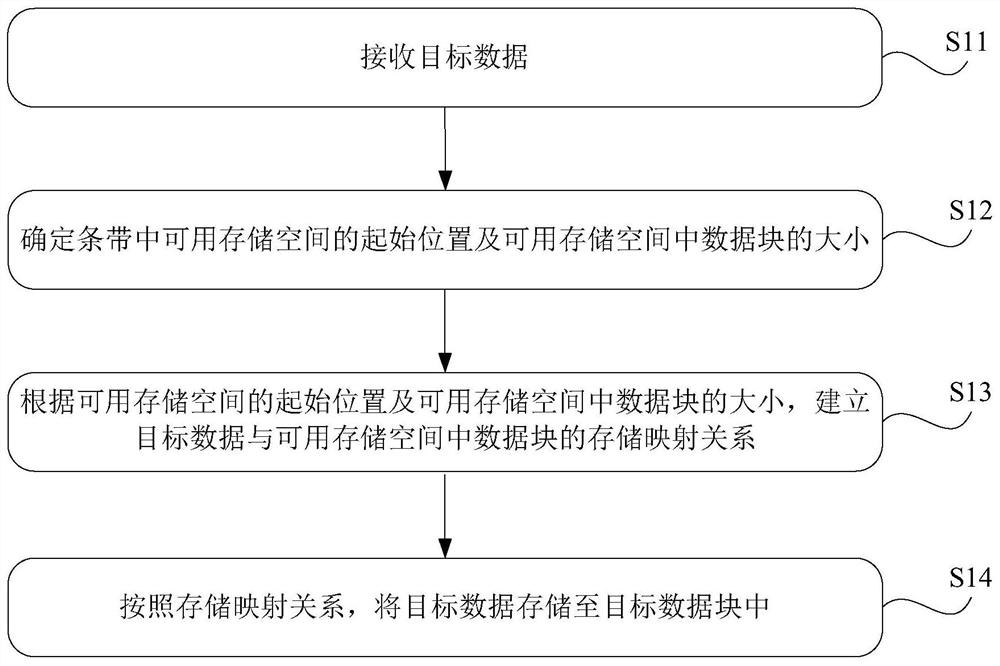

Data storage method and device

PendingCN111752466AWrite lessReduce the number of readsInput/output to record carriersParallel computingTerm memory

Owner:SHENZHEN IPANEL TECH LTD

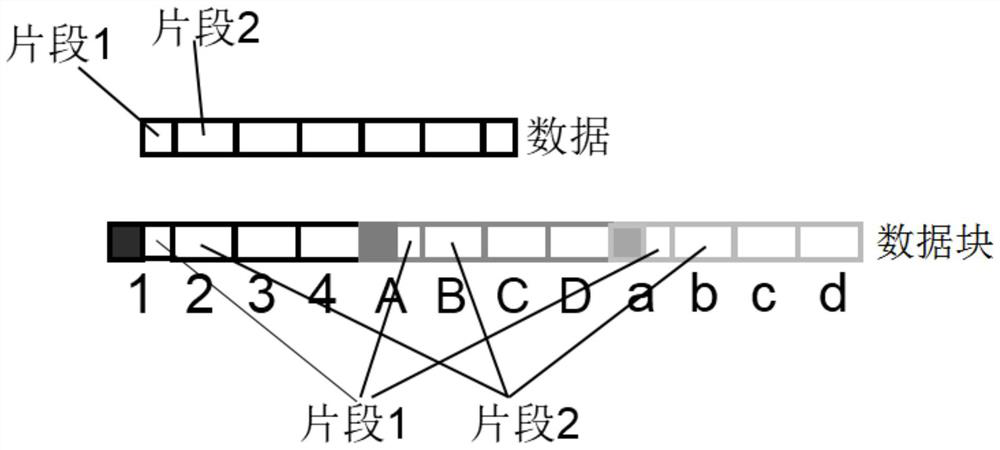

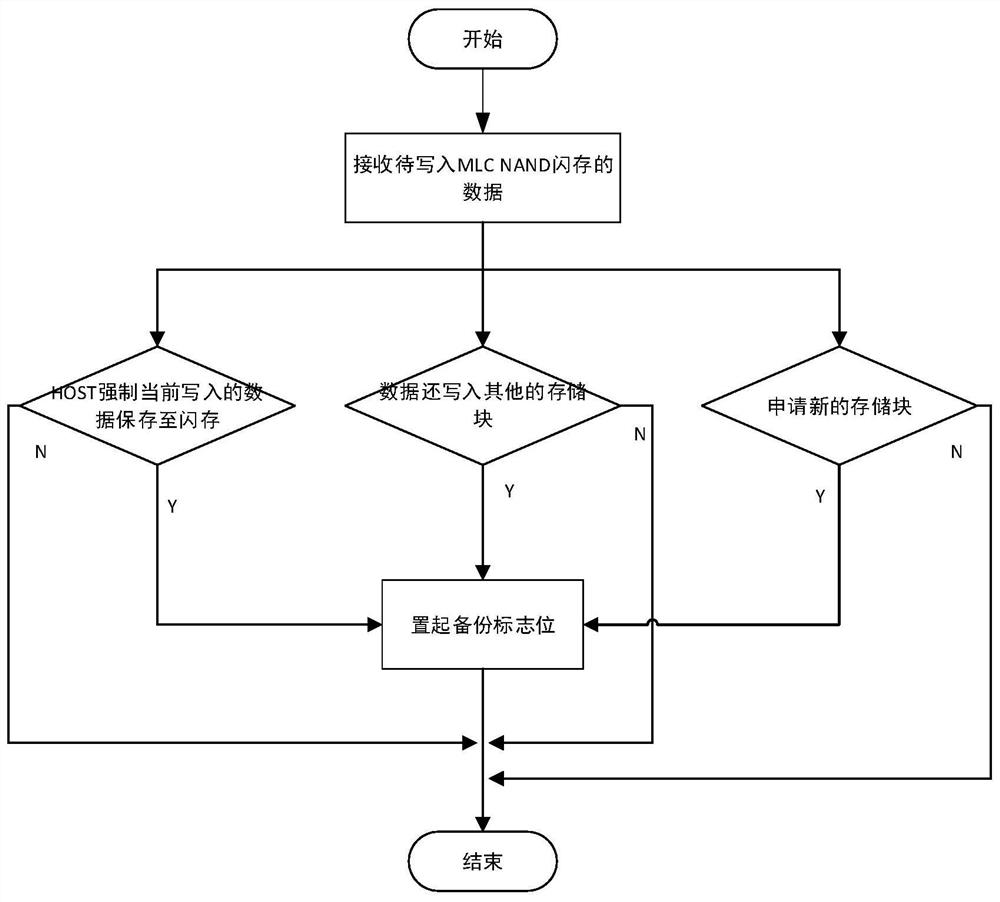

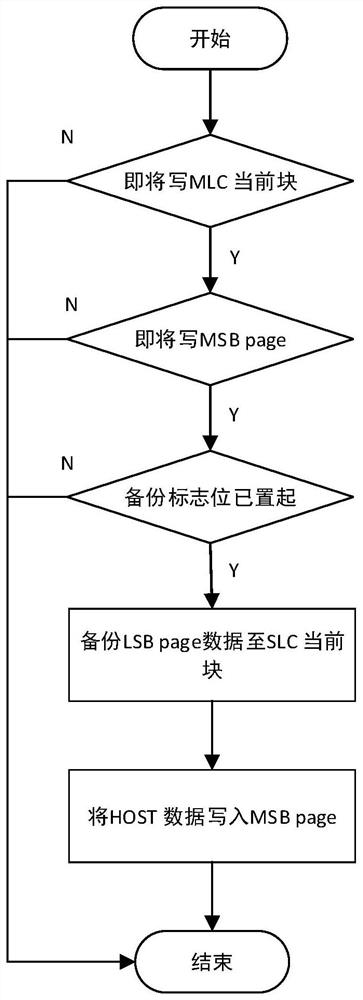

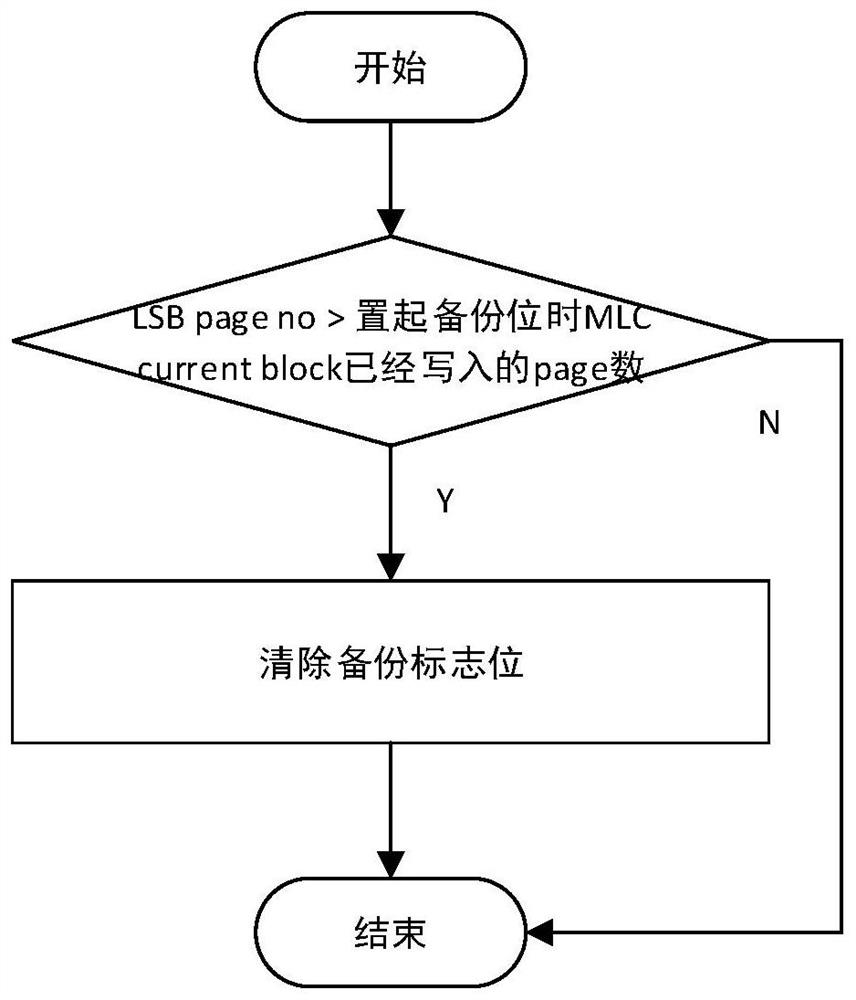

MLC NAND data backup method and device, and flash memory system

ActiveCN112667446AWrite lessGuaranteed reliabilityInput/output to record carriersRedundant operation error correctionEngineeringData storing

The invention relates to the technical field of memories, and discloses an MLC NAND data backup method and device, and a flash memory system. The backup method comprises the steps of receiving data to be written into an MLC NAND flash memory; and if at least one of a first instruction, receiving a second instruction and a third instruction, setting the backup flag bit as a valid bit, the first instruction being an instruction for ensuring data security, the second instruction being an instruction for writing the data into other storage blocks except the current storage block of the MLC, and the third instruction being an instruction for applying for a new storage block. The method at least has the advantages that it can be guaranteed that the data stored in the MLC NAND cannot be lost or inconsistent due to abnormal power failure only by backing up a small amount of LSB page data, and the reliability of the NAND equipment is guaranteed.

Owner:珠海妙存科技有限公司

Method and device for improving hard disk write-in performance of intelligent equipment

ActiveCN106980471AImprove the probability of continuous writing to the hard disk (physical hard disk)Improve write performanceInput/output to record carriersRelevant informationData storing

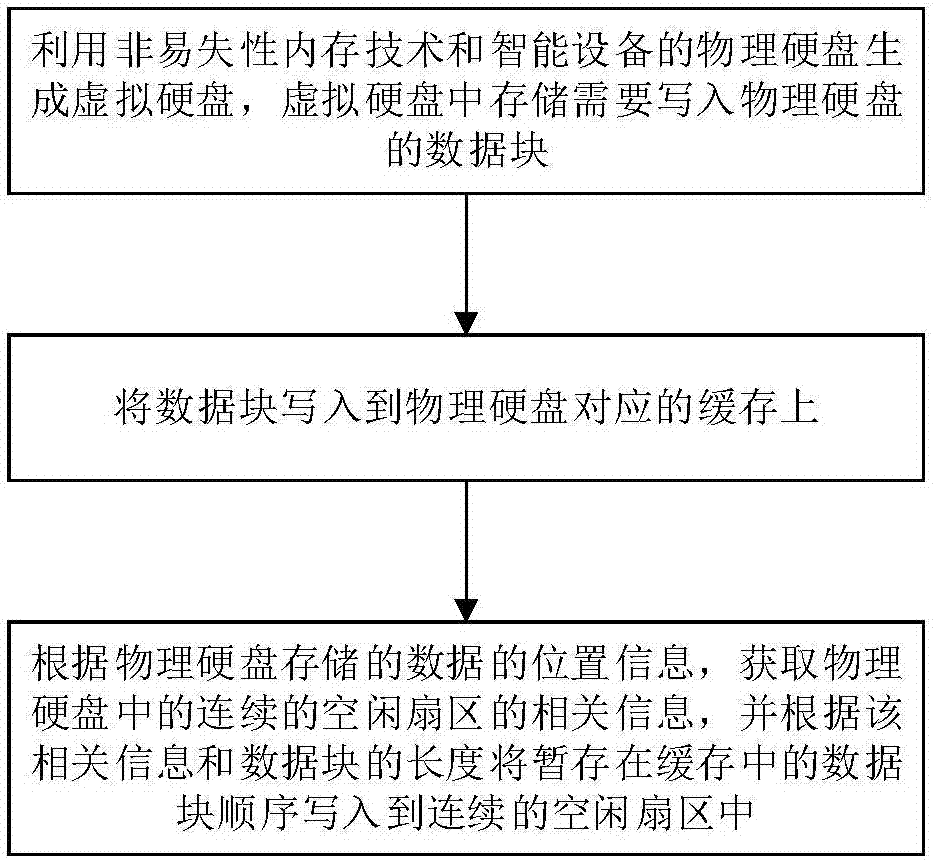

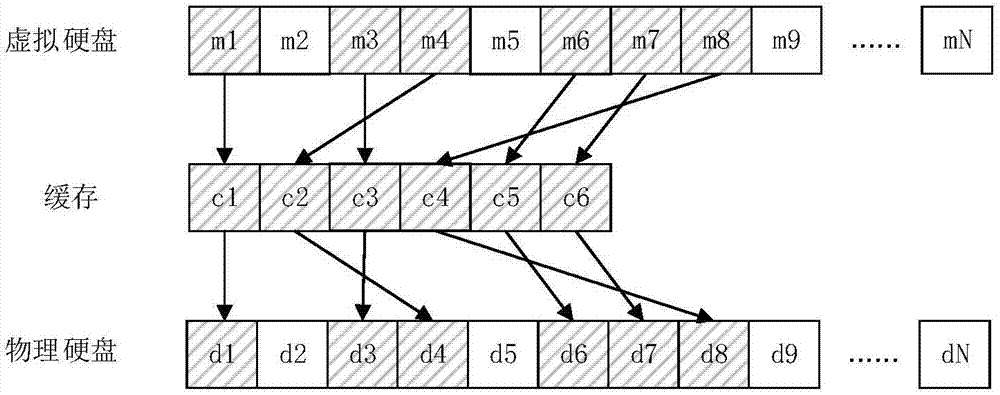

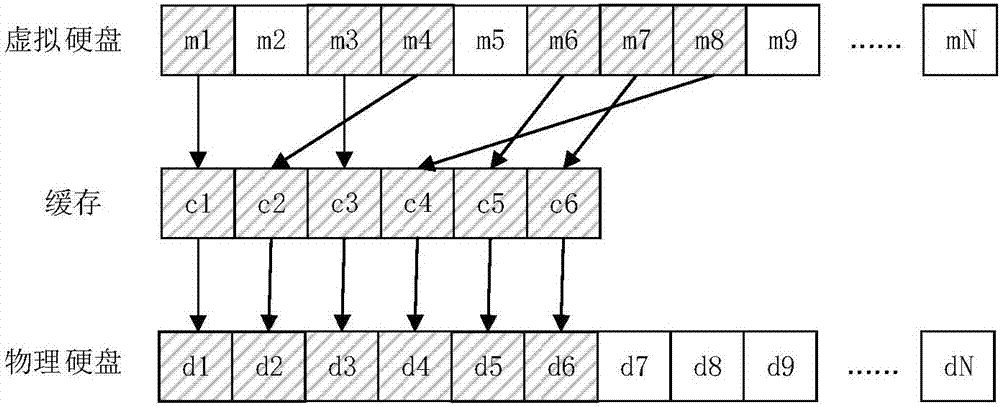

The invention discloses a method for improving hard disk write-in performance of intelligent equipment. The method comprises the following steps of: generating a virtual hard disk by utilizing a non-volatile memory technology and a physical hard disk of the intelligent equipment, wherein the virtual hard disk is internally stored with data blocks to be written in the physical hard disk; writing the data blocks into a cache corresponding to the physical hard disk; and obtaining related information of a continuous leisure sector in the physical hard disk according to position information of data stored in the physical hard disk, and writing the data blocks temporarily stored in the cache into the continuous leisure sector according to the related information and lengths of the data blocks. According to the method and a corresponding device, the probability of continuously writing the data into the hard disk (physical hard disk) can be effectively improved, the probability of randomly writing the data into the hard disk is reduced, the time of writing the data into the hard disk is saved, and the write-in performance of the hard disk is improved.

Owner:LENOVO (BEIJING) CO LTD

Flash memory system and operating method thereof

ActiveCN101739343AImprove access performanceExtend your lifeMemory adressing/allocation/relocationMemory interfaceParallel computing

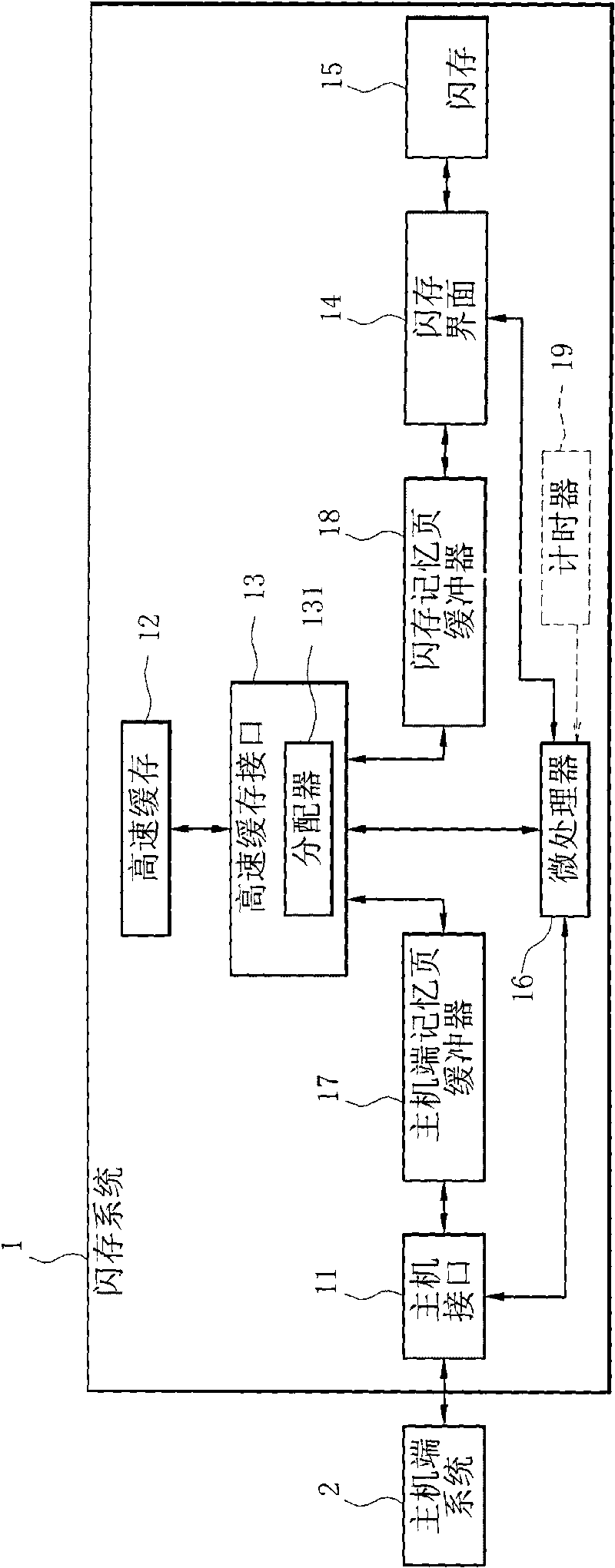

The invention provides a flash memory system, which comprises a high-speed cache memory, a high-speed cache memory interface, a host interface, a flash memory interface and a microprocessor. The high-speed cache memory interface comprises an allocator used to run time sharing processing of a data-bus frequency width so as to allocate and access high-speed cache. The host interface receives data of a host-side system and temporarily stores the date in the high-speed cache memory so as to turn the data into to-be-stored data. The flash memory interface reads the to-be-stored data from the high-speed cache memory and stores the to-be-stored data in at least one flash memory. The microprocessor controls the host interface and the flash memory interface so as to access the high-speed cache. Therefore, the aim of promoting access efficiency and memory lifespan is achieved.

Owner:ADATA

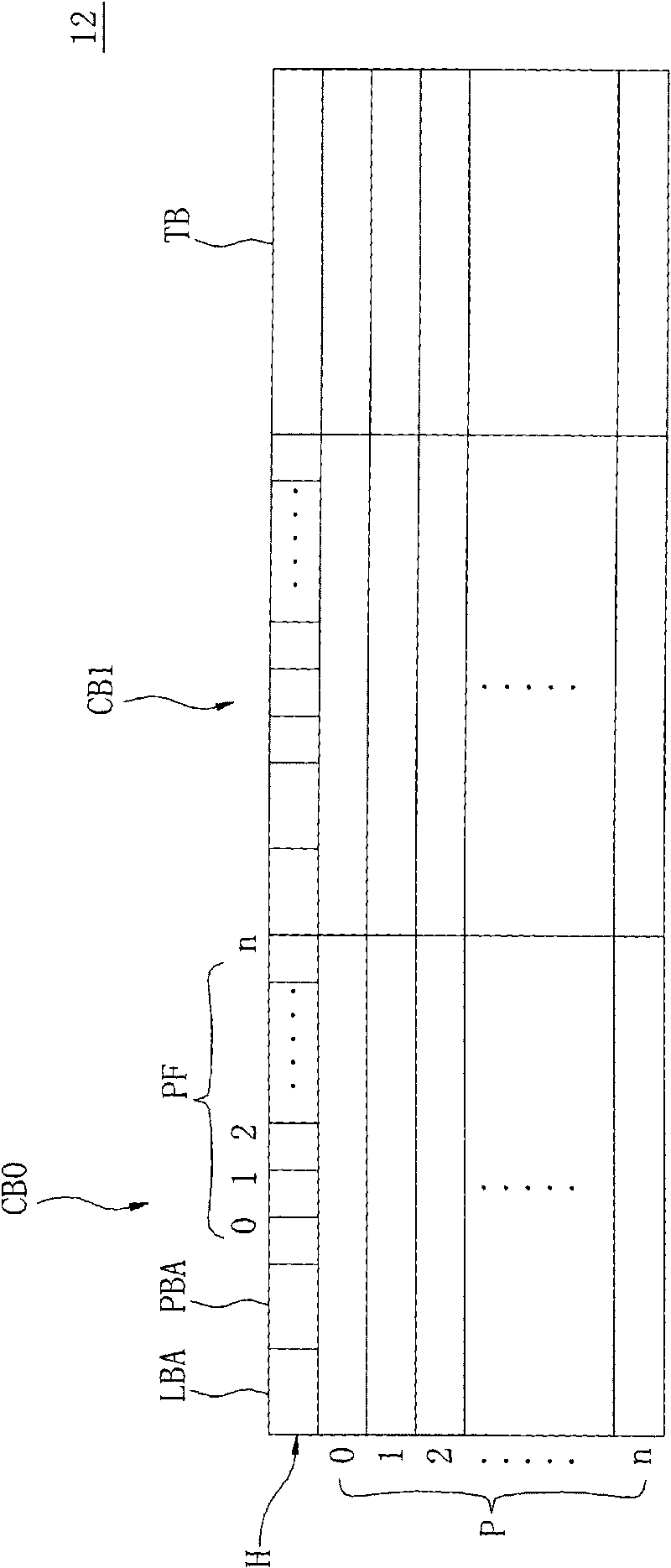

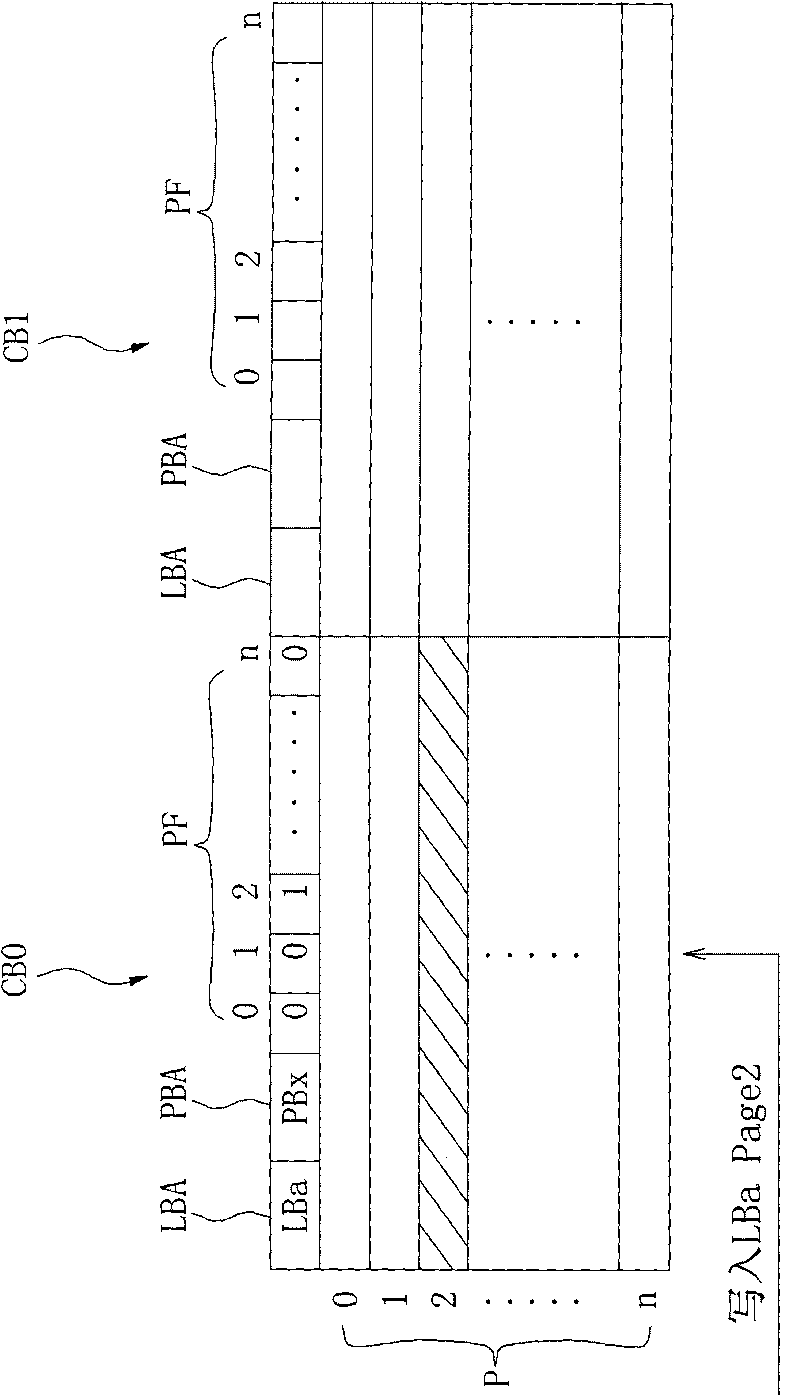

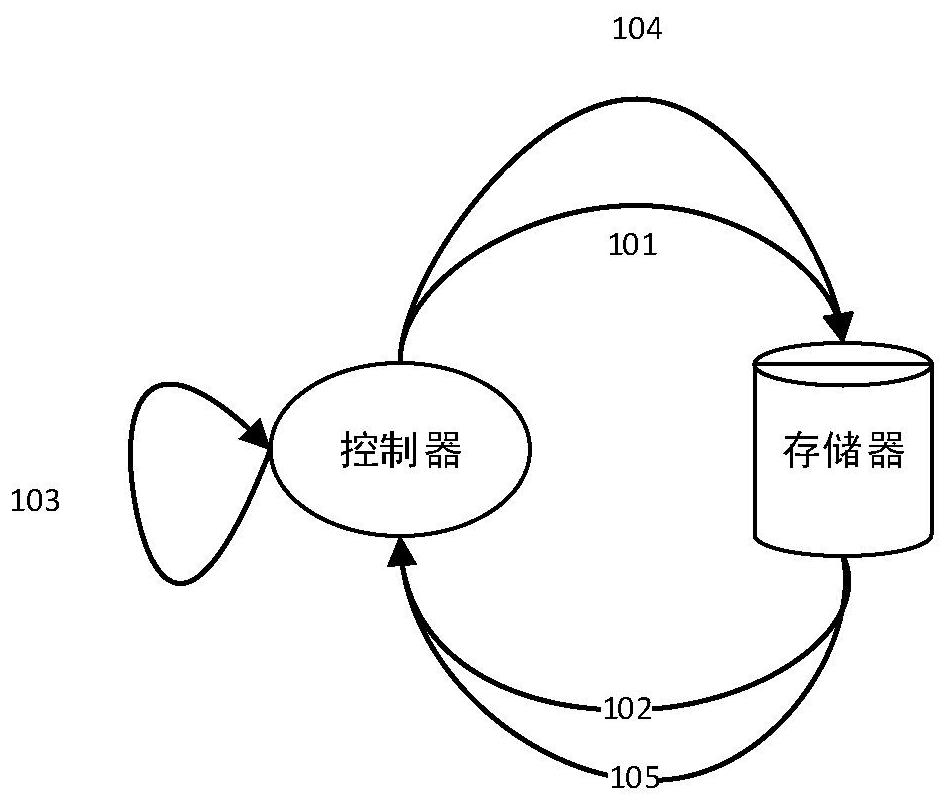

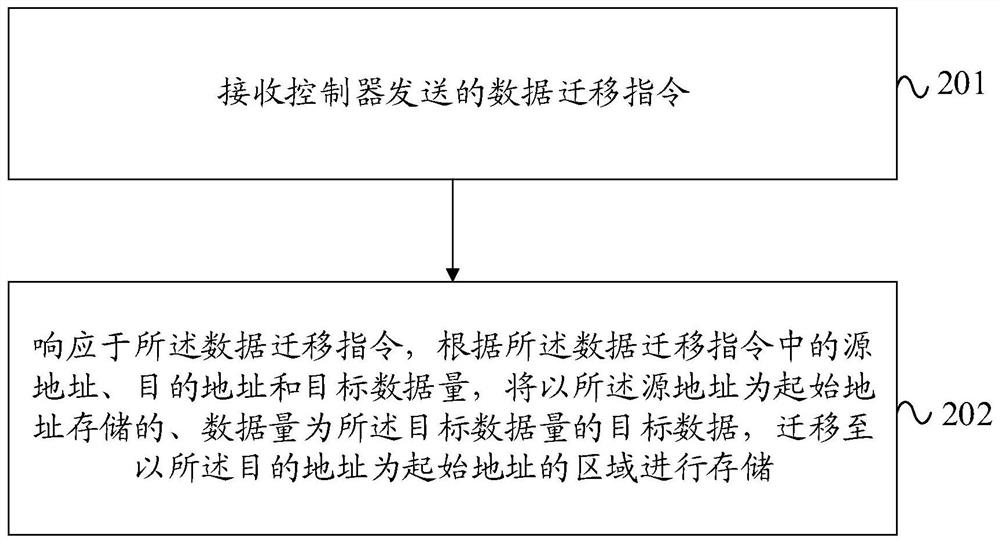

Data migration method, memory and controller

PendingCN113282239AReduce instabilitySmooth transmissionInput/output to record carriersComputer hardwareData migration

The invention discloses a data migration method, a memory and a controller, and belongs to the technical field of computers. The data migration method comprises the following steps: receiving a data migration instruction sent by a controller; and in response to the data migration instruction, according to a source address, a destination address and a target data volume in the data migration instruction, migrating target data which is stored by taking the source address as an initial address and has the data volume of the target data volume to a region which takes the destination address as the initial address for storage.

Owner:VIVO MOBILE COMM CO LTD

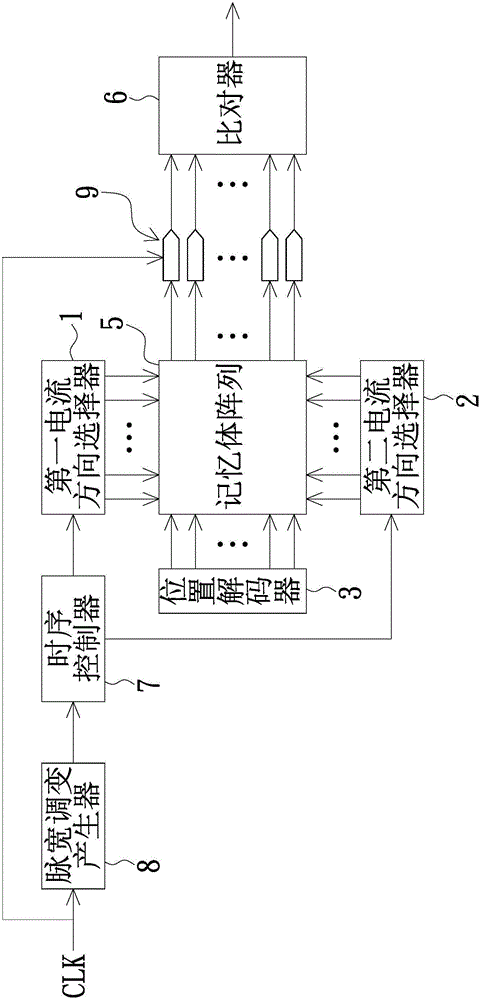

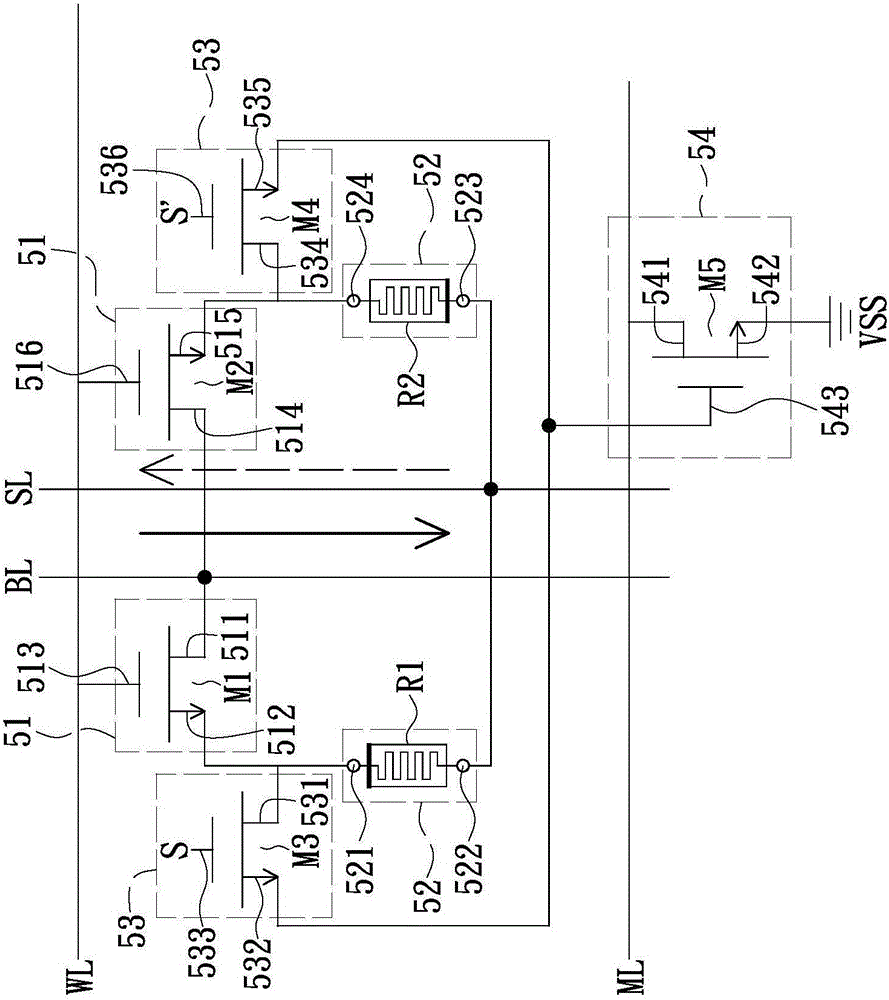

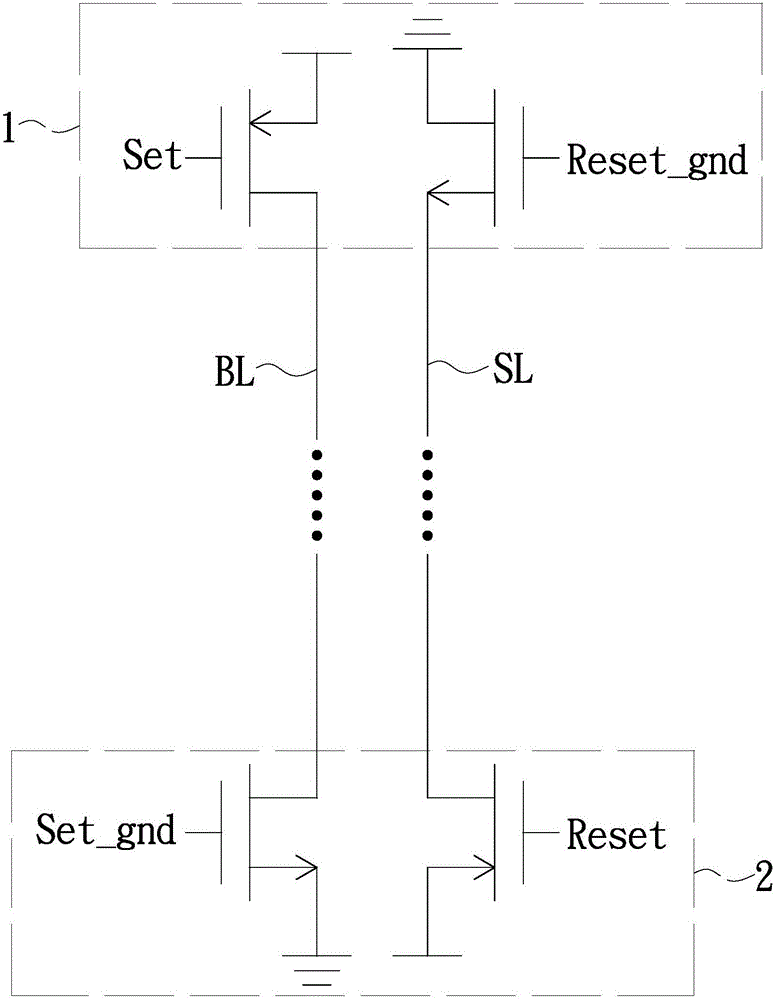

Memory cell and content addressable memory having the same

InactiveCN105989878AReduce the use of areaReduce the number of tracesDigital storageTernary content addressable memoryData storing

The invention discloses a memory cell and a content addresable memory body. A memory cell includes a set of storage switch units, a set of memory units, a set of comparison switch units and a discharge switch unit. The storage switch units are turned on by a turn-on signal transmitted by a word line. The memory units receive and store write data transmitted by a bit line or a source line when the storage switch units are on under a write mode. The comparison switch units are turned on by comparison data transmitted by comparison lines under a search mode. The discharge switch unit is turned on by a detection voltage under the search mode when the comparison data transmitted by the comparison lines is different from the write data stored in the memory units, so that the reference signal transmitted to the comparator is redirected to a reference voltage. A content addressable memory using the memory cell is also provided.

Owner:邱沥毅

Method for improving performance of solid state disk

InactiveCN108241471AReduce the amount of recycled and moved dataReduce data writingInput/output to record carriersHigh probabilityInvalid Data

The invention discloses a method for improving the performance of a solid state disk. The method is characterized by comprising the steps of grouping commands according to logic addresses of writing instructions of a host in the solid state disk; dividing the writing instructions with the continuous logic addresses in the same group; and writing data of the writing instructions in the same group into a NAND flash with continuous physical addresses. After use of a command stream for management, the data of the continuous logic addresses is concentrated in the continuous physical addresses; evenif a user performs deletion and overwriting operations on the data subsequently, the old data is intensively invalid, and the whole block level is invalid with high probability, so that a garbage collection program processes invalid data blocks of the whole block disorderly; and the data can be reused after being directly erased, so that the data migration amount of garbage collection is reducedand unnecessary data writing is reduced.

Owner:SHENZHEN YILIAN INFORMATION SYST CO LTD