Method and system for monitoring single event upset effect of FPGA (field programmable gate array) and correcting reloading

A single-event flipping and reloading technology, which is applied in information storage, static memory, digital memory information, etc., can solve the problems of import restrictions on high-performance devices, affect the normal operation of devices, and limit applications, so as to reduce PCB layout area, Enhance the ability to resist single event effect and ensure the effect of reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] The present invention will be described in detail below in conjunction with the embodiments and accompanying drawings, but the present invention is not limited thereto.

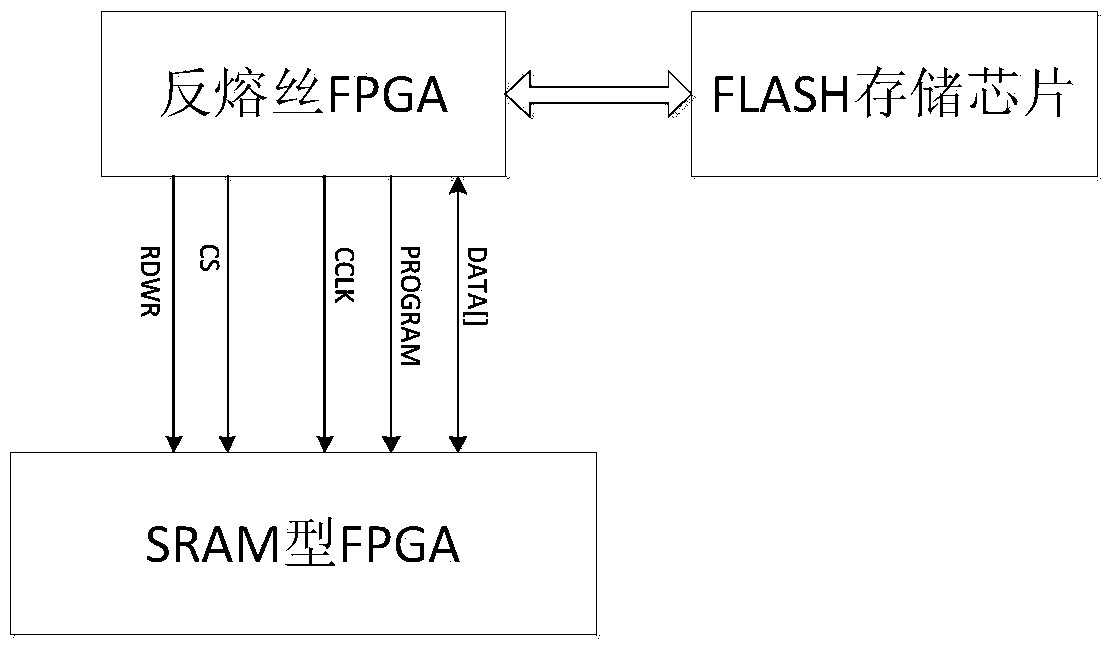

[0047] Such as figure 1 As shown in Fig. 1, a method for monitoring whether the single event flip effect occurs in the SRAM FPGA in space and correcting the reload, the hardware includes an antifuse FPGA, a FLASH memory chip and a SRAM FPGA. Among them, the load-related signal lines of the SRAM FPGA are connected to the antifuse FPGA, including CCLK, RDWR, DATA[0:7], PROGRAM, and CS. At the same time, the SRAM type FPGA should be in slave loading mode, and the CCLK clock is provided by the antifuse FPGA.

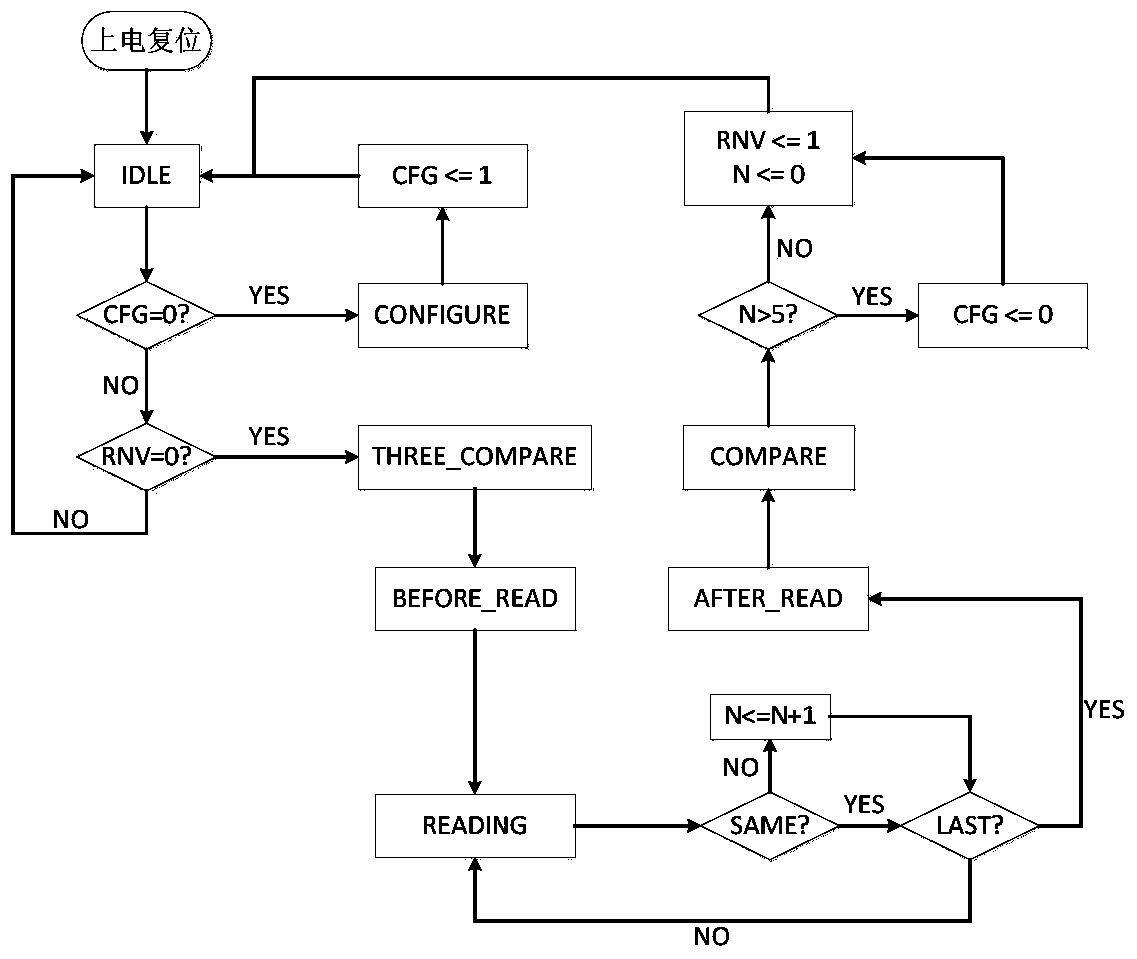

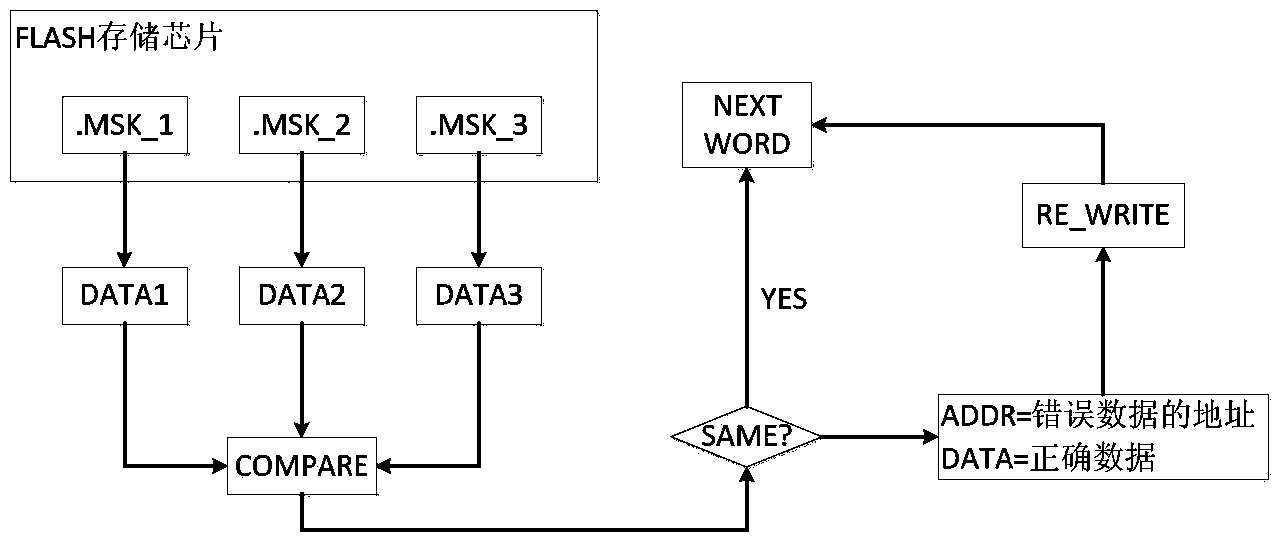

[0048] Such as figure 2 As shown in , the software flow diagram is the main steps of monitoring the SRAM FPGA in the antifuse FPGA. When the power is just turned on, the state machine is in the power-on reset state. In this state, the antifuse FPGA resets the memory chip, and at the same time con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More