On-line upgrading method and device of configuration file of field-programmable gate array (FPGA)

A configuration file and successful configuration technology, applied in the direction of program control device, program loading/starting, etc., can solve the problems of multi-pin, unable to realize logic function, occupying CPLD, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

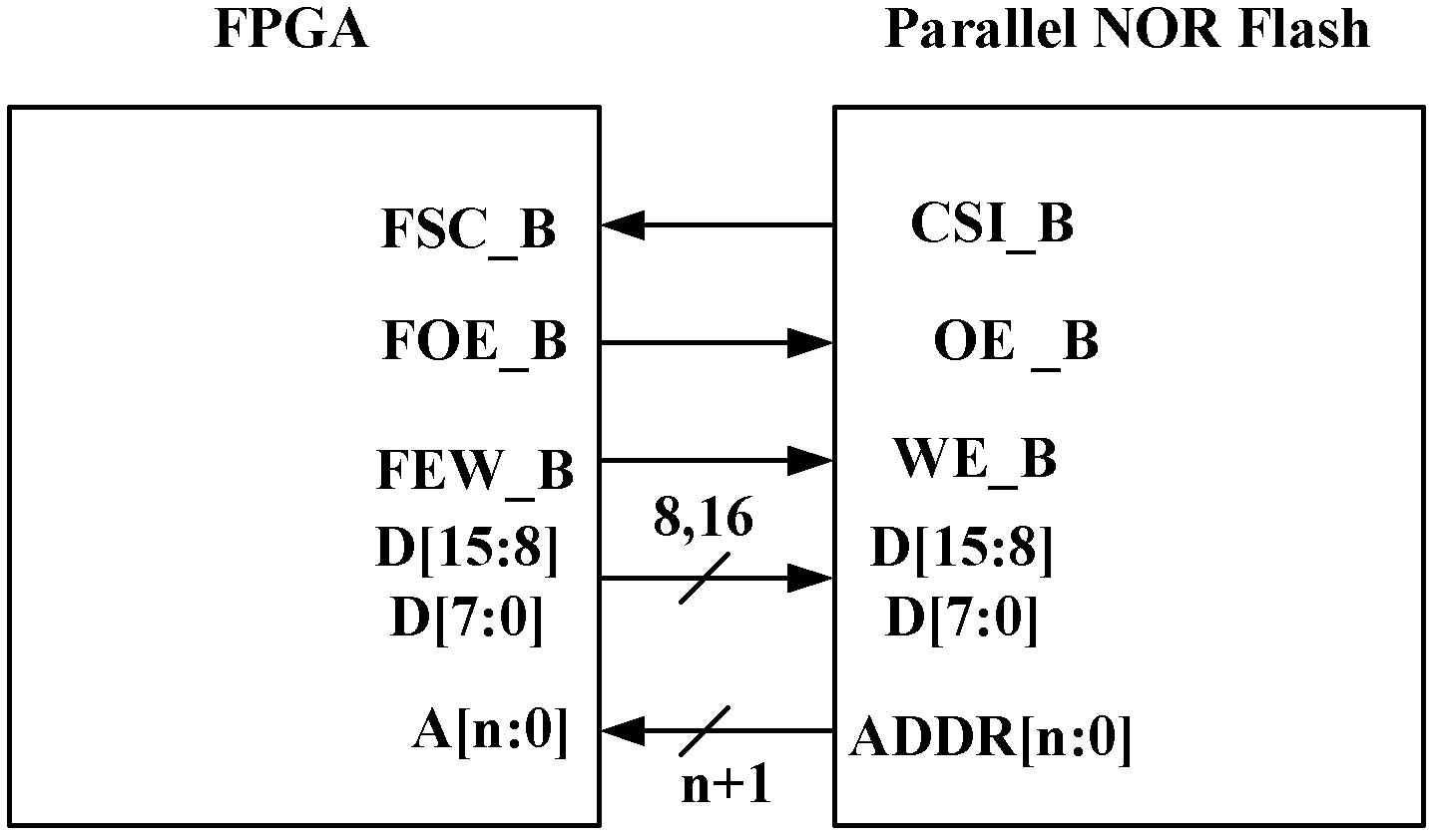

[0033] In order to complete the online upgrade of the FPGA configuration file without adding additional logic devices, and to achieve the purpose that the FPGA can be used after power-on, an embodiment of the present invention provides a method and device for online upgrade of an FPGA file.

[0034] The method and device for online upgrade of FPGA files provided by the embodiments of the present invention enable the FPGA to switch between the normal mode and the upgrade mode. In order to achieve the foregoing objective, in the embodiment of the present invention, the active configuration mode of the FPGA is used to select the data path through the bus switch. Such as image 3 Shown is the structure diagram of the bus switch, image 3 Take the structure of the 3384 bus switch as an example. The 3384 bus switch has a total of 10 data paths, which are controlled by two sets of OE enable keys. When 1OE# is valid (that is, when it is low), the corresponding 1A and 1B side data paths a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More