FPGA emulation device and method

A simulation method and technology of a simulation device, which are applied in the field of FPGA simulation, can solve problems such as the disclosure of FPGA simulators and FPGA simulators, and achieve the effects of solving verification difficulties, saving time, and reducing software and hardware design difficulties.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

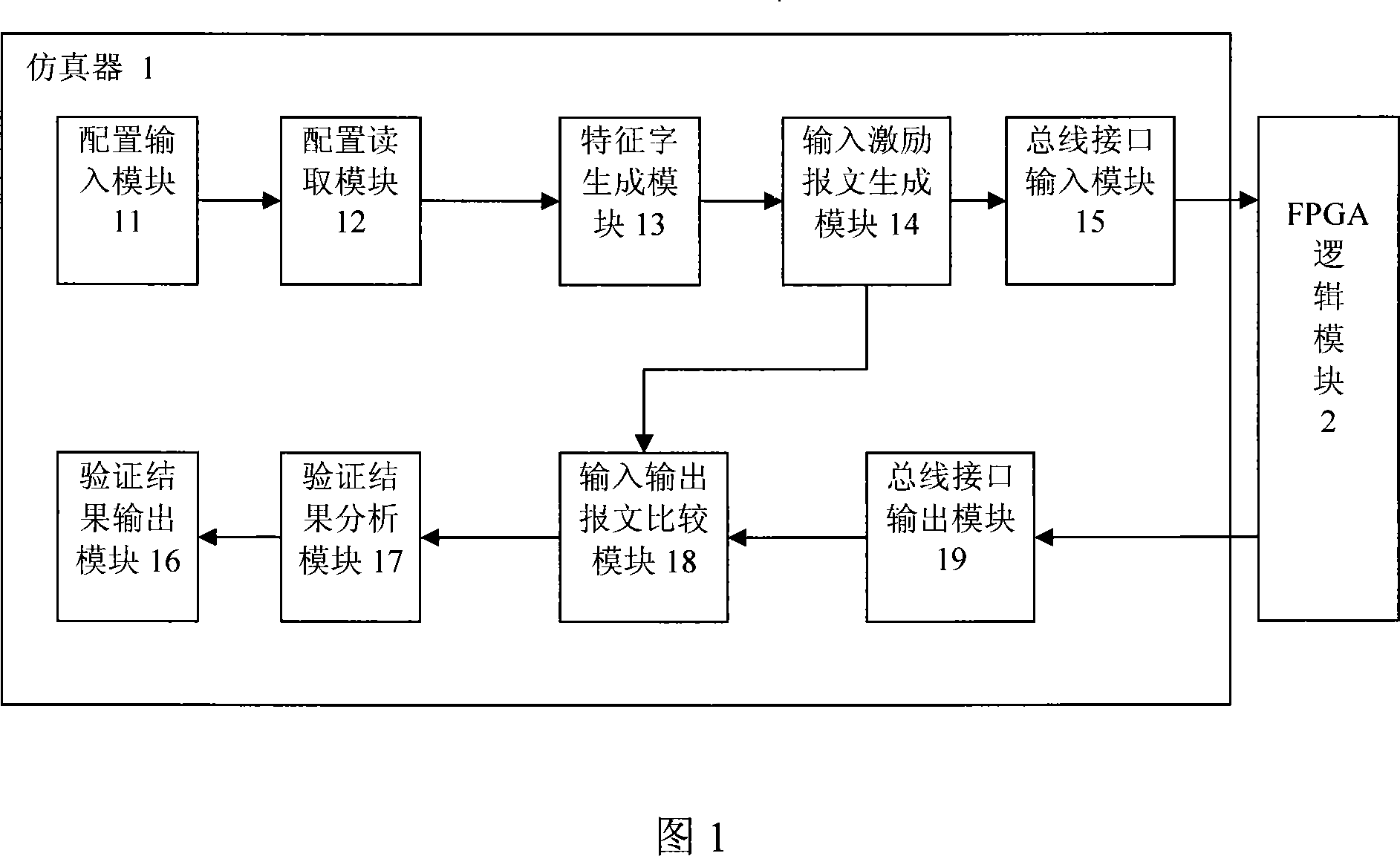

[0047] As shown in Figure 1, the FPGA emulator 1 based on feature word of the present invention comprises:

[0048] Configuration input module 11: it is a parameter input device for various message configurations. After manual input of these parameters, this module saves it as a sorted text file for later query.

[0049] Configuration reading module 12: it reads out the various parameters stored in the text file generated by the configuration input module 11, and sends it to the feature word generation module 13.

[0050] Characteristic word generation module 13: it divides and processes the characteristic word signature transmitted by the configuration reading module 12 according to the design requirements, etc., and then converts the processed characteristic word signature into hexadecimal ASCII code and sends it to the incentive message to generate Module 14.

[0051] Incentive message generation module 14: after the signature in the signature generation module 13 is trans...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More