Hierarchical FPGA layout and wiring method based on multi-level method and empowerment hypergraph

A weighted hypergraph, layout and routing technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as division that cannot escape local optimum, and achieve reduction of global interconnection lines and optimal clustering effect of effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0090] In order to understand more clearly the technical content of the hierarchical FPGA layout and routing method based on the multi-level method and the weighted hypergraph of the present invention, the following examples are given in detail.

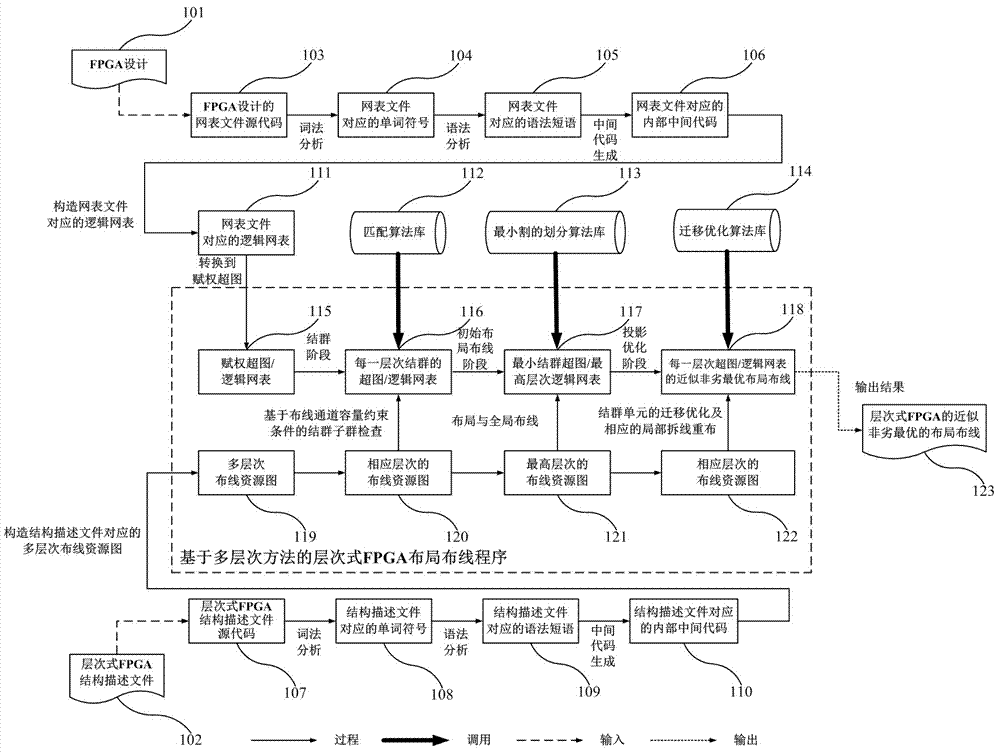

[0091] The flow chart of the hierarchical FPGA layout and routing method based on the multi-level method and the weighted hypergraph of the present embodiment is as follows figure 1 As shown, describe this FPGA design 101 with hardware description language, synthetically generate the netlist file 103 that this FPGA designs; The character stream of the code is scanned and decomposed to identify each word 104; the grammatical analysis of the netlist file is to decompose the word sequence into various grammatical phrases 105 on the basis of the lexical analysis, and determine according to the grammatical rules of the netlist file Whether the entire character stream constitutes a grammatically correct netlist file; the semantic anal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More