Delay fault testing method and system oriented to the application of FPGA

A delayed fault, application-oriented technology, applied in electronic circuit testing, digital circuit testing, electrical measurement, etc., can solve problems such as changing circuit structure and reducing circuit performance, so as to simplify generation steps, improve controllability, and fault coverage high effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The application-oriented FPGA delay fault testing method and system proposed by the present invention are described as follows in conjunction with the accompanying drawings and embodiments.

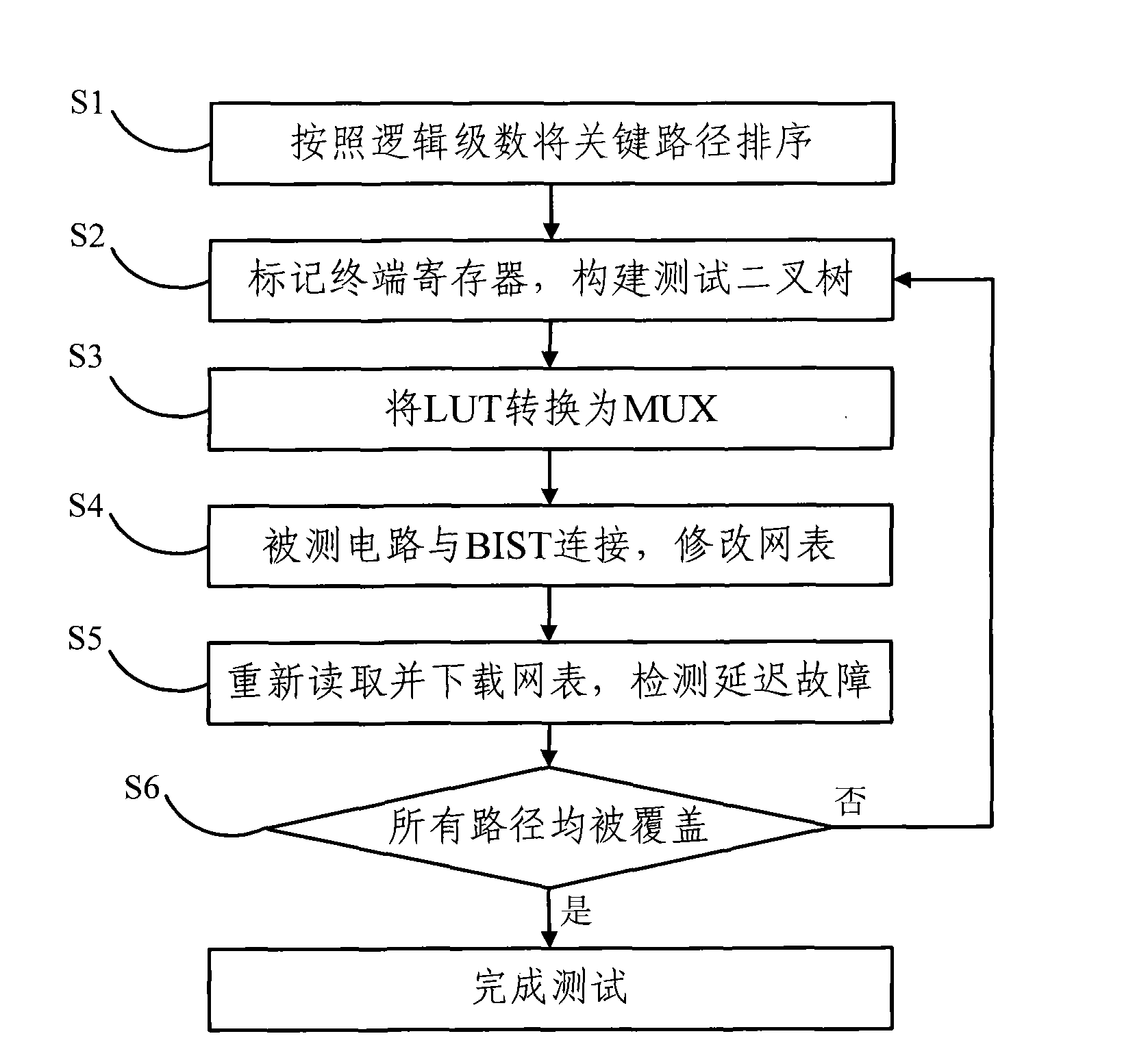

[0043] Such as figure 1 As shown, in the application-oriented FPGA delay fault testing method of the present invention, at first, the critical path needs to be determined according to the clock frequency required by the circuit design, and all paths whose delay is greater than 70% of the clock cycle are all defined as critical paths. Then proceed to the following steps

[0044] S1. Determine the critical paths to be tested according to the clock cycle required by the circuit design, and sort all the critical paths according to the logical progression;

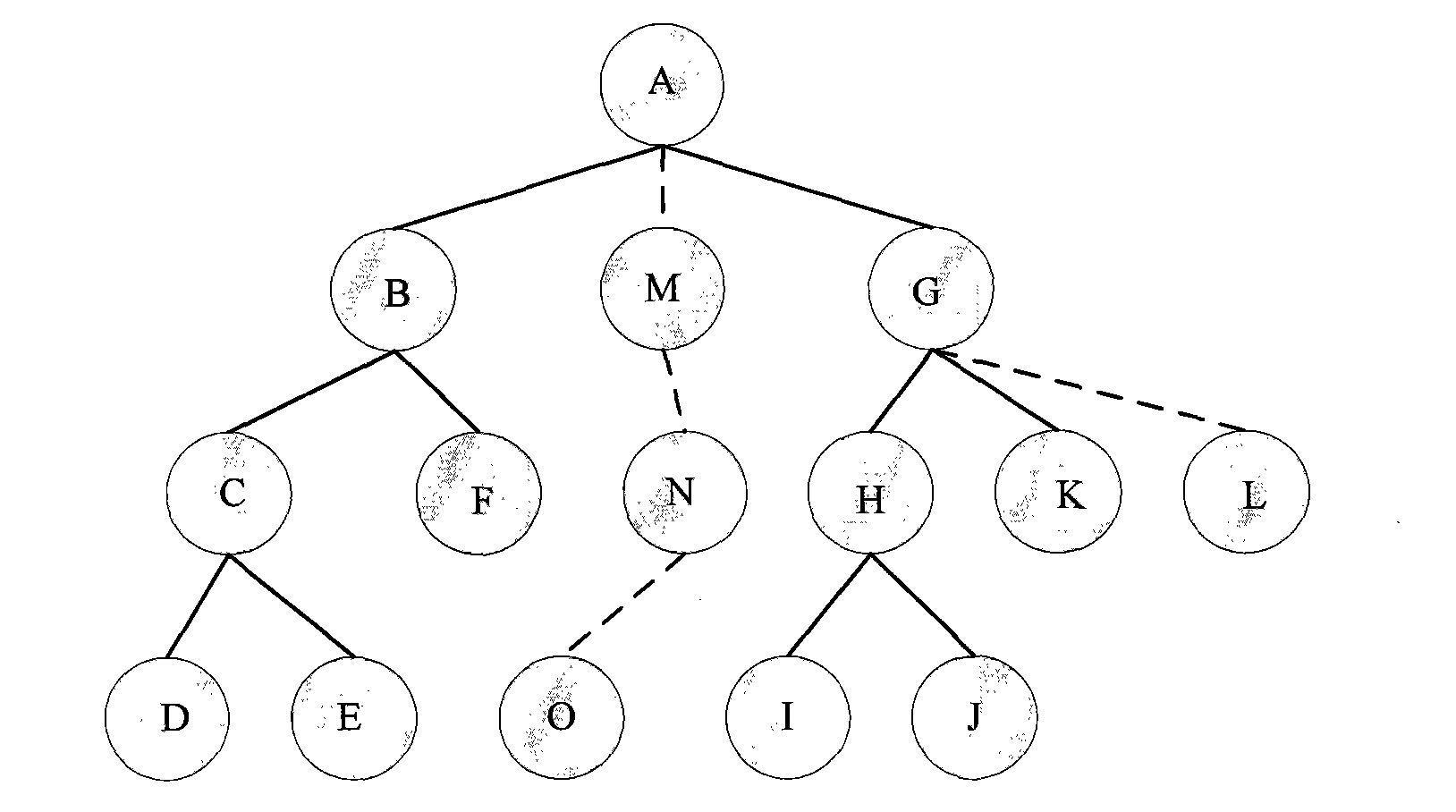

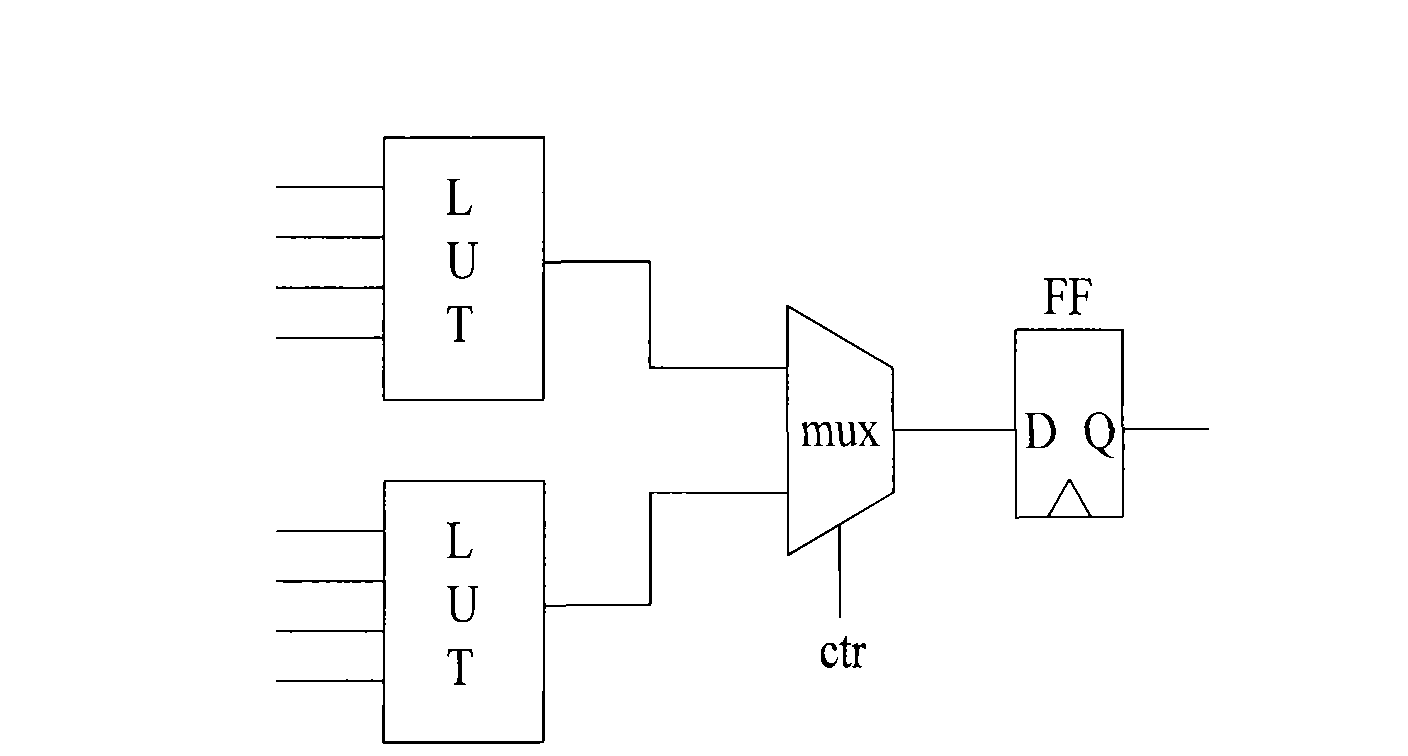

[0045]S2. Take the terminal register of the critical path with the highest logic level as the root node, mark the terminal register as measured, and select the second measured path from all paths whose terminals are the register an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More