Self-adaption timing sequence calibrating method of high-speed serial communication interface

A serial communication interface and communication interface technology are applied in the field of high-speed serial communication interface adaptive timing calibration and high-speed serial communication interface timing calibration to ensure data alignment and synchronization, accurate data sampling, and reduce system clock frequency. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

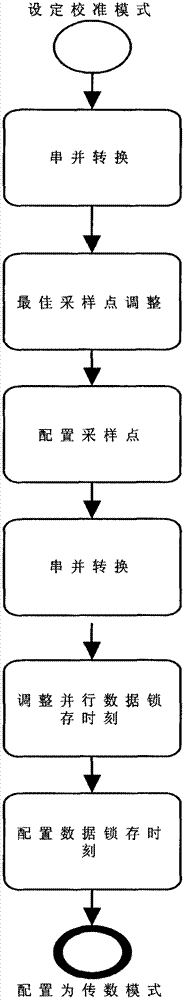

[0029] The present invention utilizes FPGA to realize, has added a kind of calibration mode for the high-speed serial communication interface, and the flow chart is as follows figure 1 shown. In the calibration mode, the sending end sends a specific command sequence, and uses sampling, comparison, calibration, and re-sampling, such a reciprocating closed-loop calibration method, to realize the dynamic adaptive adjustment of the high-speed serial data sampling by the receiving end to achieve high-speed serial The purpose of automatic calibration of interface timing is to make accurate sampling, data alignment and data synchronization at the receiving end.

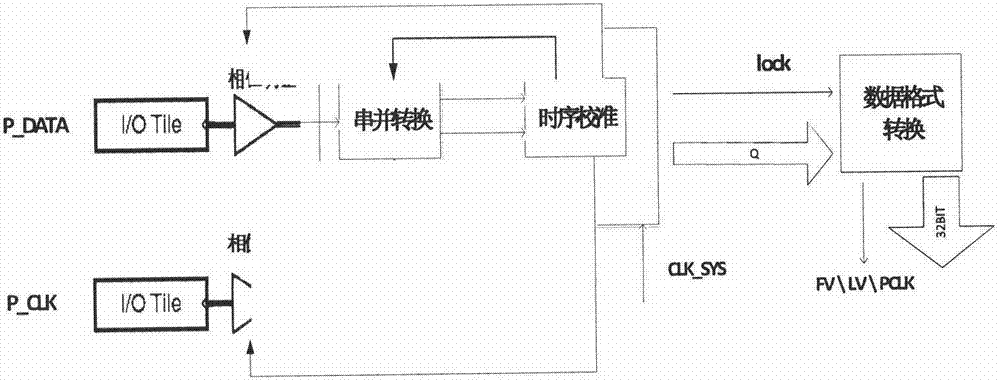

[0030] The organization structure of the receiving end of the high-speed serial bus is as follows: figure 2 shown. The content of serial data transmission is divided into clock, data, and control signals, which are transmitted by different channels. The edge alignment of data and control signals and clock signals at the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More