Universal calibration method for transmission path delay errors of parallel ADC sampling system

A technology of transmission path and delay error, which is applied in the field of alignment and calibration of multi-channel parallel data input delay in high-speed variable sampling system, can solve the problem that multiple sets of parallel ADC sampling systems are not universal, sampling system delay parameters are inconsistent, Difficulties in program version management and other issues, to achieve the effects of easy porting and version management, enhanced readability and standardization, and good application prospects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

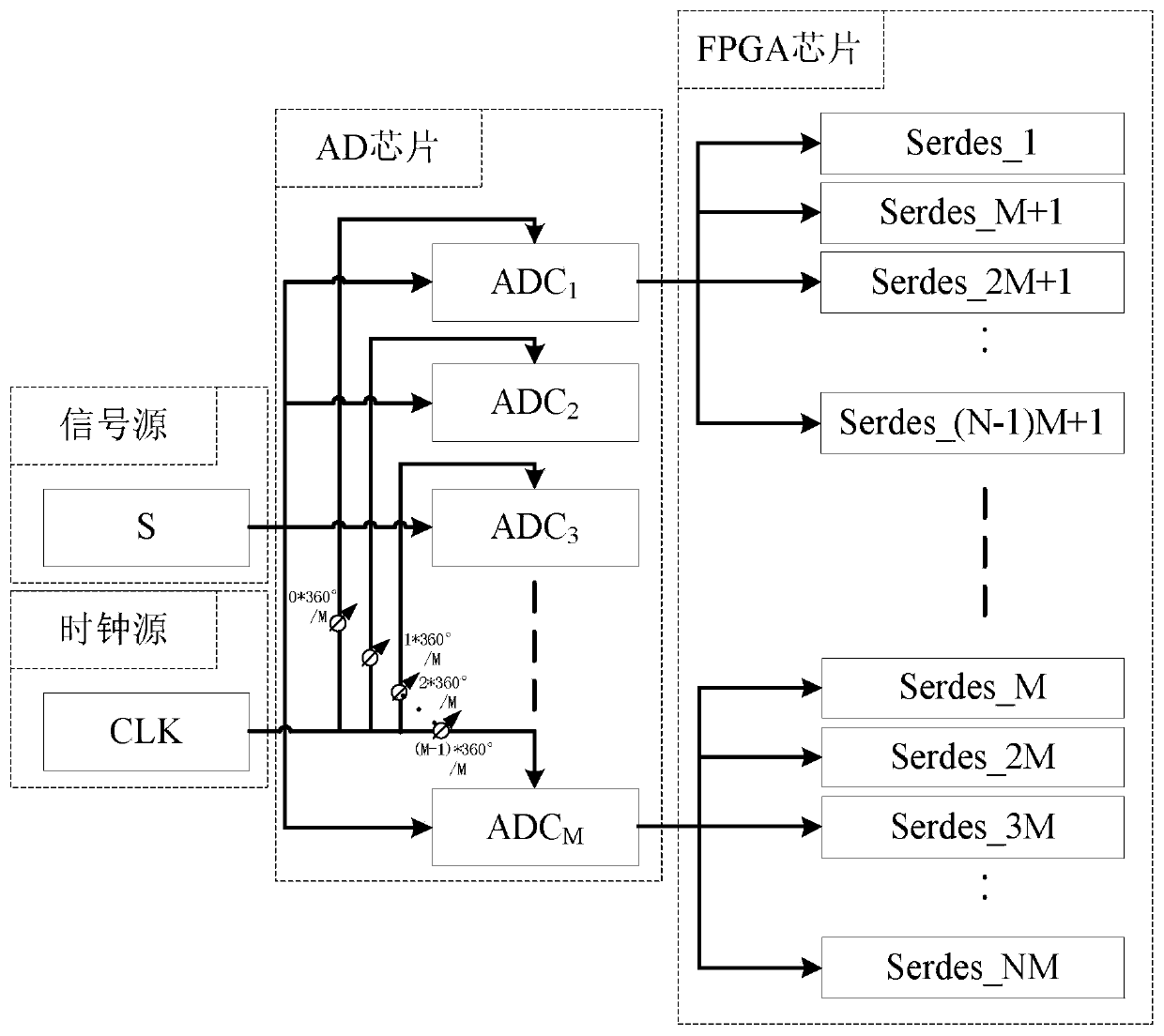

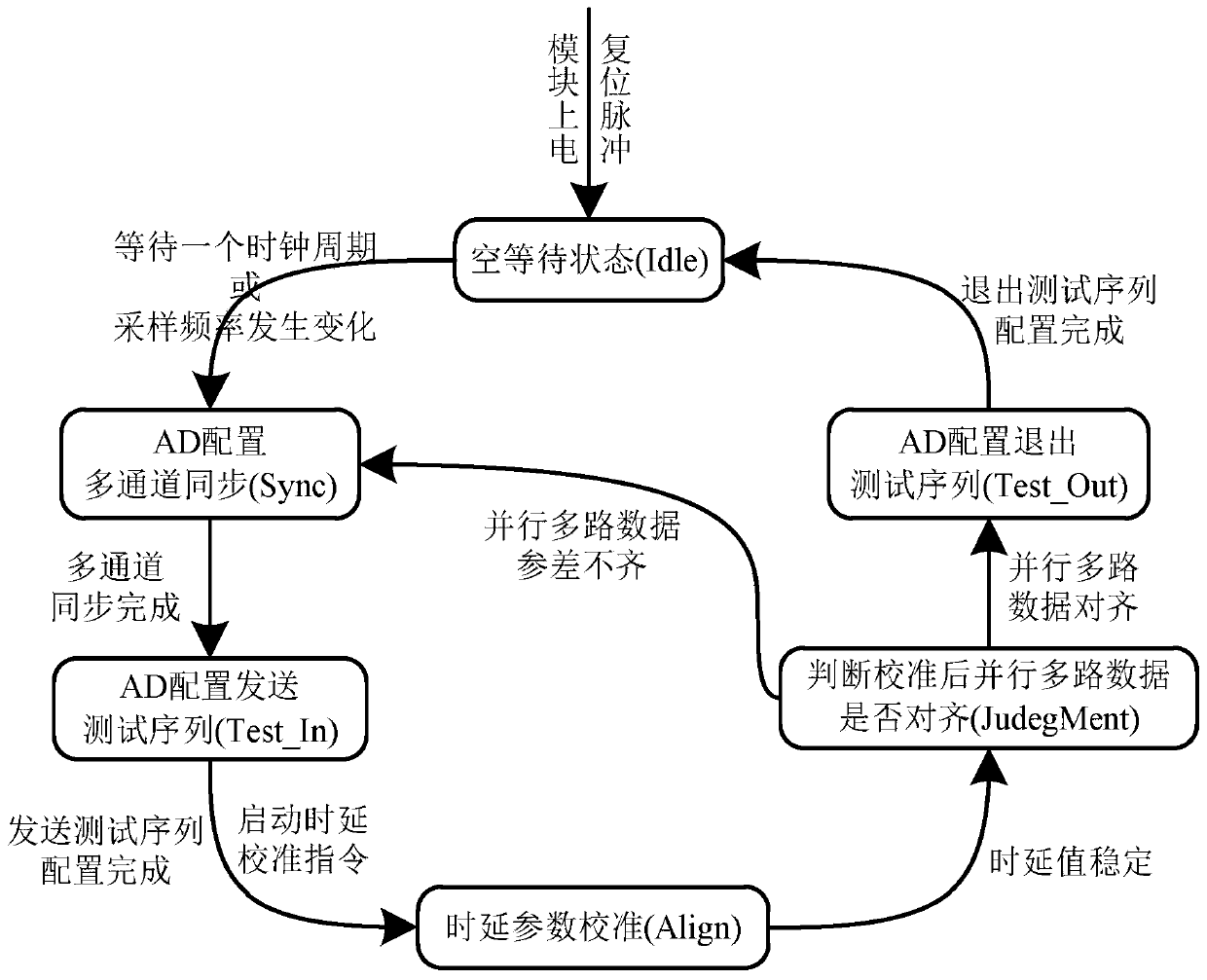

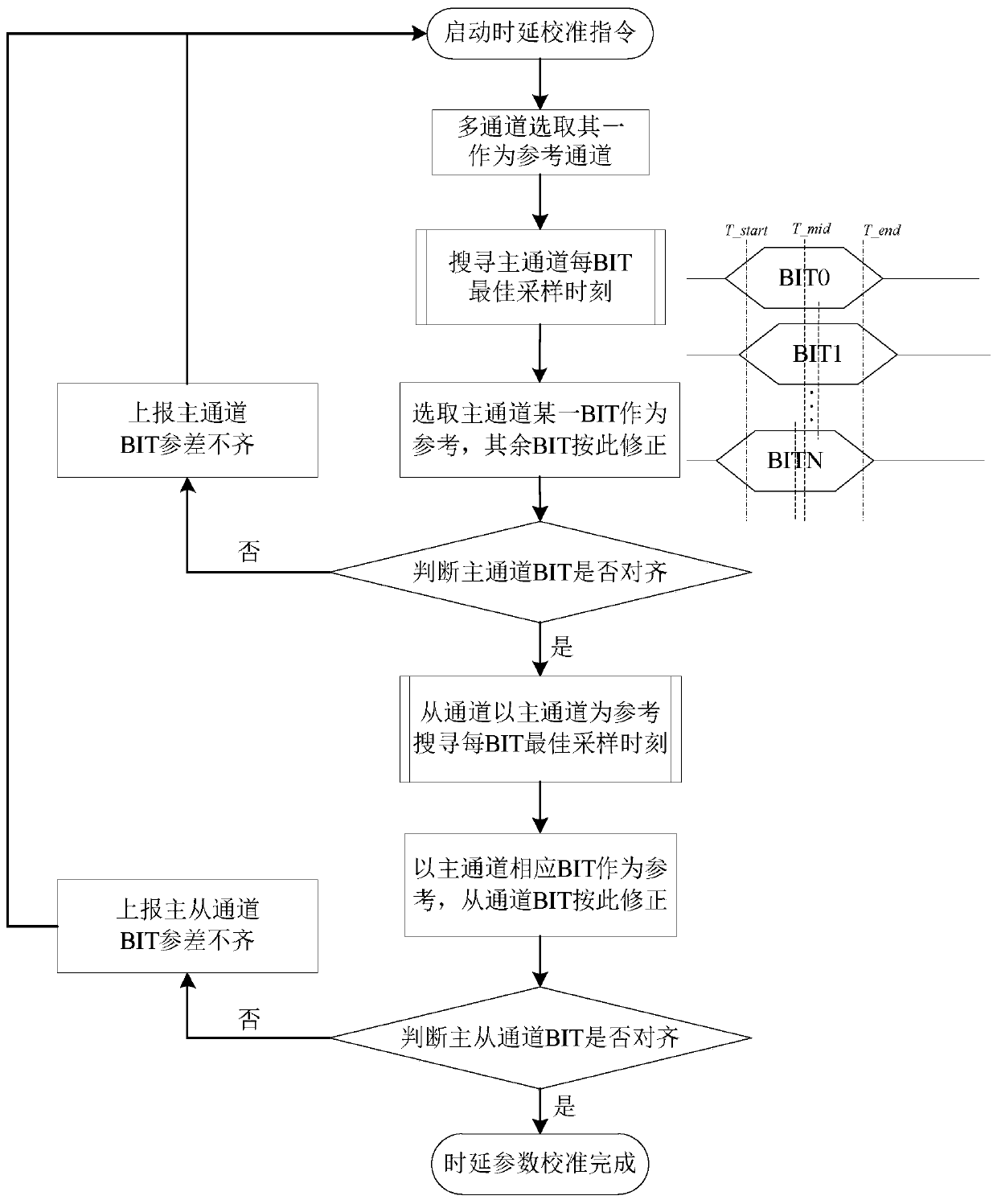

[0015] refer to figure 1. According to the present invention, the clock source CLK and the signal source S are configured as multi-channel output through an integrated M-channel high-speed analog-to-digital conversion AD chip, and the AD chip is connected to a large-scale programmable gate array FPGA through a high-speed serial interface to form a high-speed variable sampling rate system ; The AD chip transmits the high-speed sampling data grouped in parallel and reduces the speed through the parallel multi-channel mode to achieve the first level of speed reduction; by configuring the relevant registers, the parallel sampling data and the AD test sequence of each channel output phase relationship, FPGA adopts high-speed serial-to-parallel conversion The primitive ISERDES or the serial-to-parallel conversion IP core SelectIO converts high-speed serial data into parallel data to achieve the second level of speed reduction; the FPGA built-in program sets the virtual logic analyze...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More