Digital integrated circuit chip testing system

A technology for testing integrated circuits and chips, which is applied in the direction of measuring electricity, measuring devices, and measuring electrical variables, etc. It can solve the problems of cumbersome test operations, complex functions, and difficulty in understanding test methods and processes.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] One of the purposes of the present invention is to provide a low-cost, easy-to-operate automatic small digital integrated circuit machine test system device and its method, so as to realize the functional test of small digital integrated circuits.

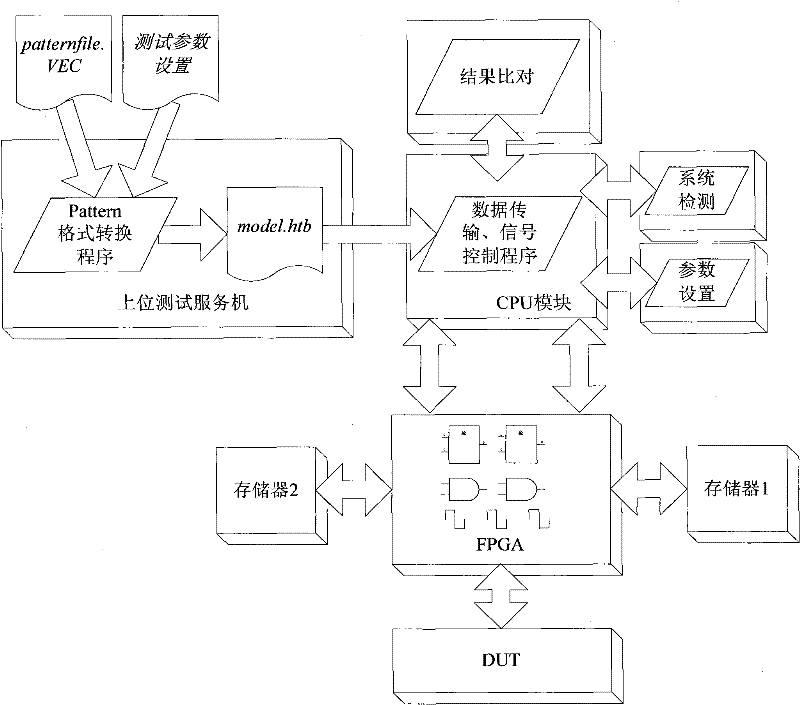

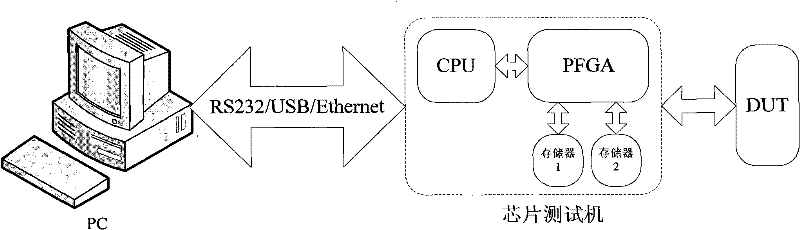

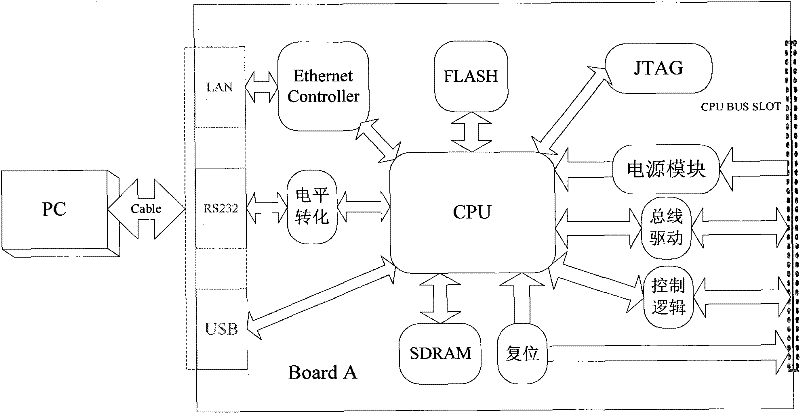

[0028] The test system consists of a host test server and a digital integrated circuit chip tester, the host test server executes the test vector file conversion software, and at the same time serves as the terminal of the digital integrated circuit chip tester; the digital integrated circuit chip tester is based on the CPU processor And signal processor FPGA to realize, it is composed of AC-DC switching power supply, FPGA signal processing bus module, CPU control module and test channel module; among them:

[0029] The host test server is equipped with an interface, and the digital integrated circuit chip tester is connected to the host test server through the interface;

[0030] The AC-DC switching power supply converts th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More