Memory interface method based on CLB (Central Logic Bus) bus

A memory interface and memory technology, applied in instruments, electrical digital data processing, etc., can solve problems such as occupation, not improving work efficiency, etc., and achieve the effect of prolonging the latching time, improving the clock utilization rate, and reducing the number of waiting cycles.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

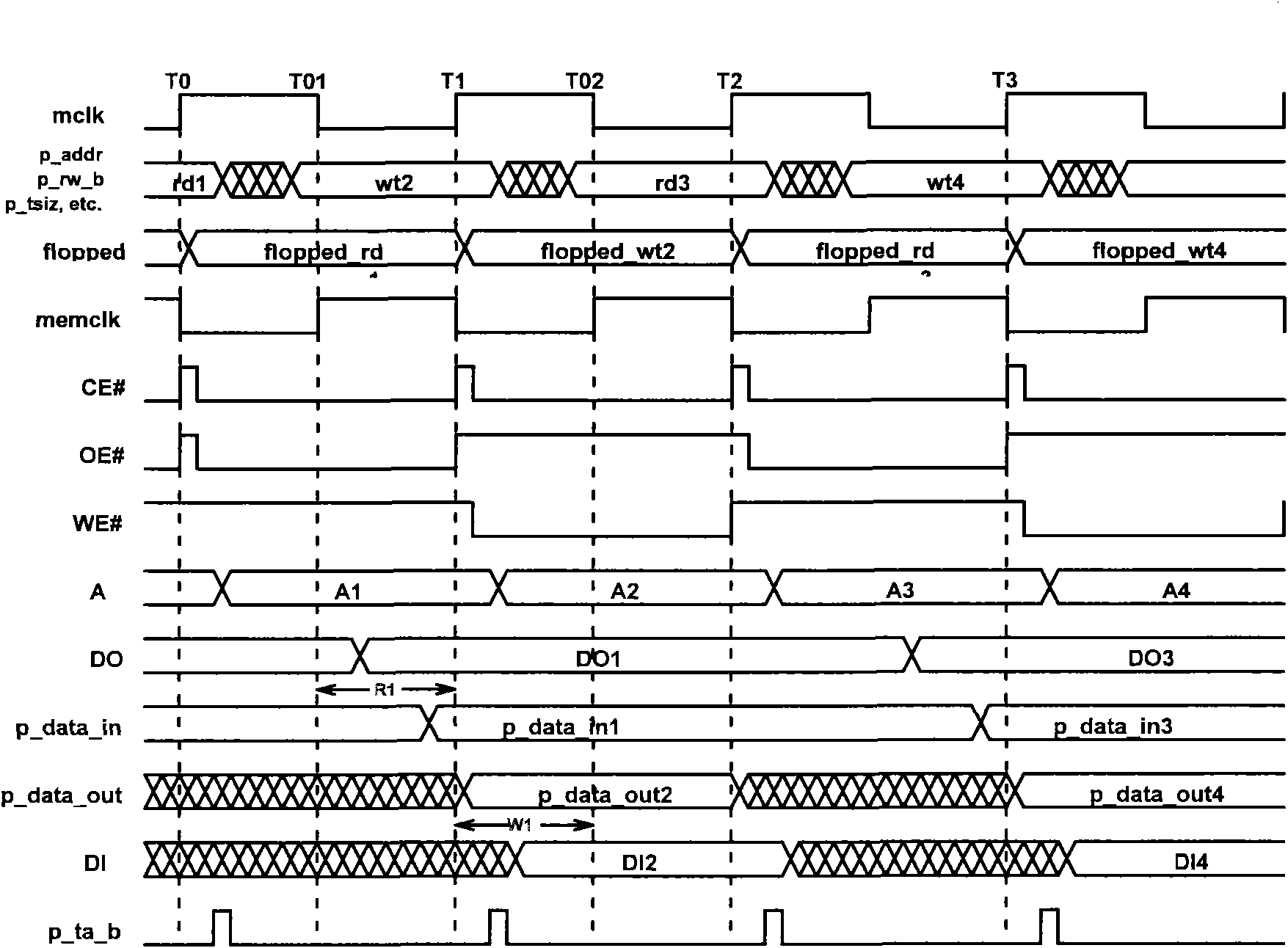

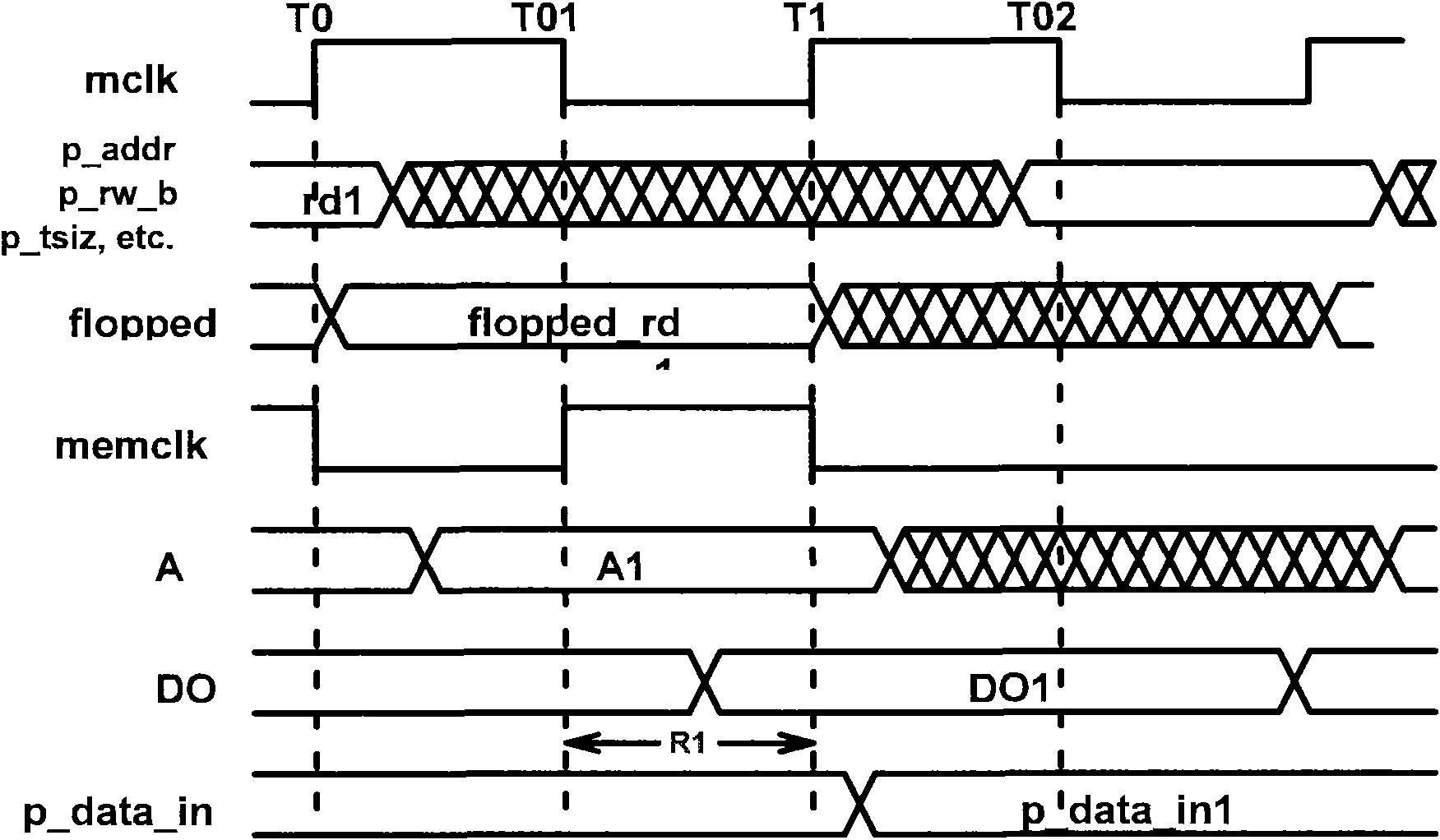

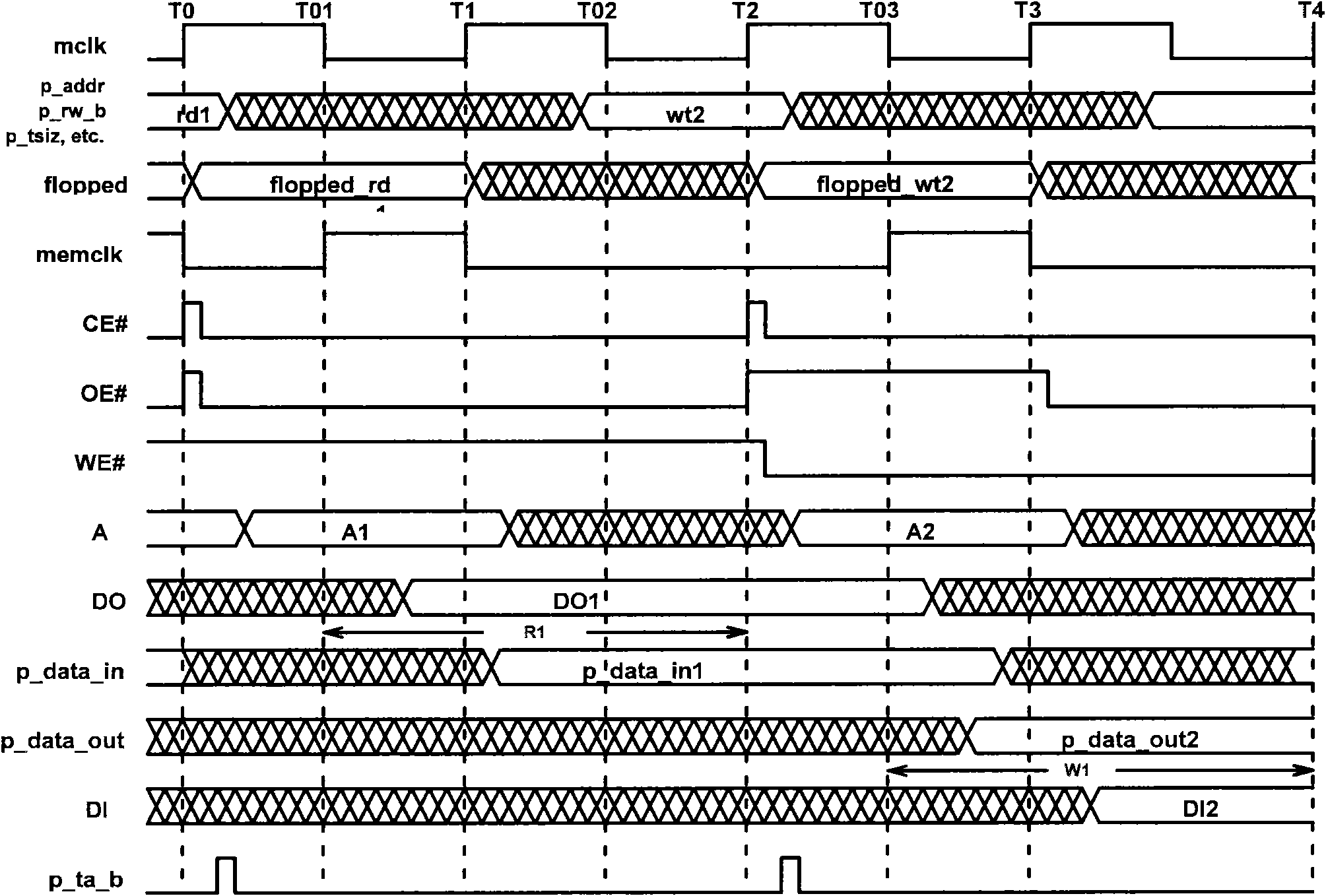

[0027] Embodiment: a kind of memory interface method based on CLB bus,

[0028] Including: on the rising edge of the bus clock m_clk, the processor sends a read or write operation request, and the bus latches the address signal and control signal from the processor to obtain the first latch signal, and generates a memory enable signal; at the same time, the address Inputs for transmission of signals and control signals to the memory;

[0029] After the rising edge of the bus clock, the adjacent falling edge latches the address and control signal again to obtain the second latch signal. At this time, the memory generates the memory clock mem_clk according to the memory enable signal, and the falling edge of the memory clock mem_clk Synchronized with the falling edge of the bus clock m_clk; at the same time, the memory receives the first latch signal or the second latch signal from the bus;

[0030] After the falling edge of the memory clock mem_clk, when a read operation is pe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More