Patents

Literature

330results about How to "High-speed performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

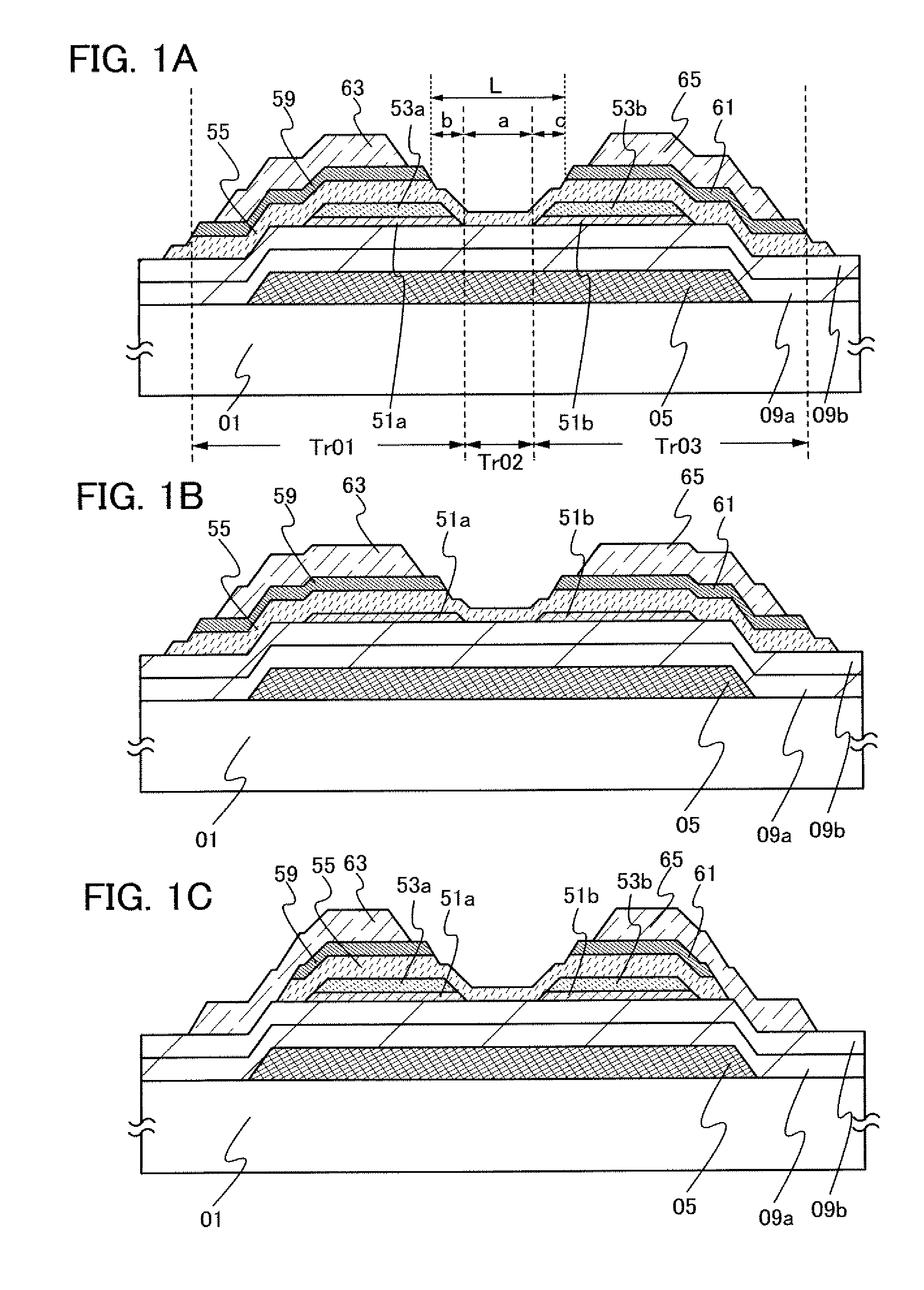

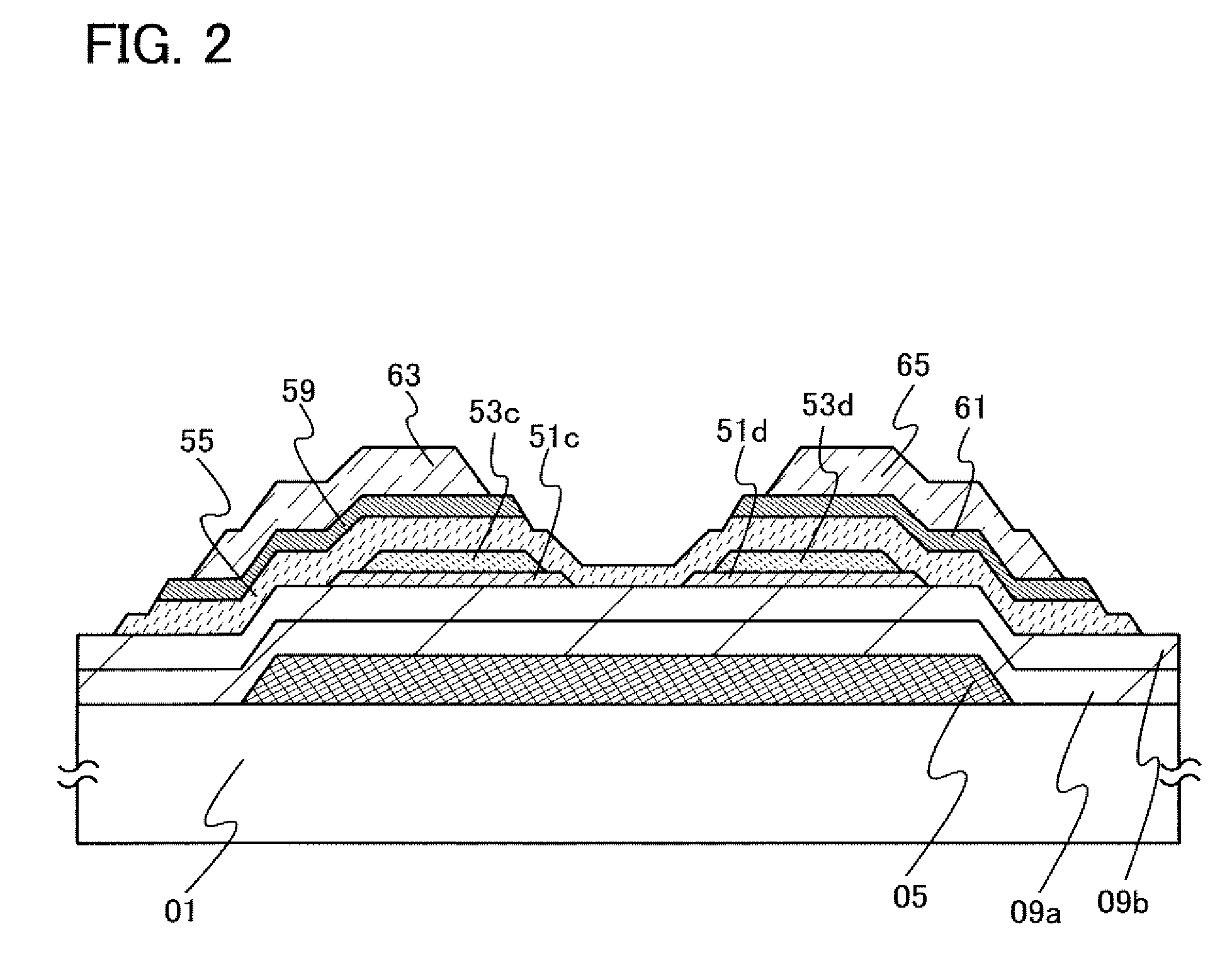

Thin-film transistor, method of producing the same, and devices provided with the same

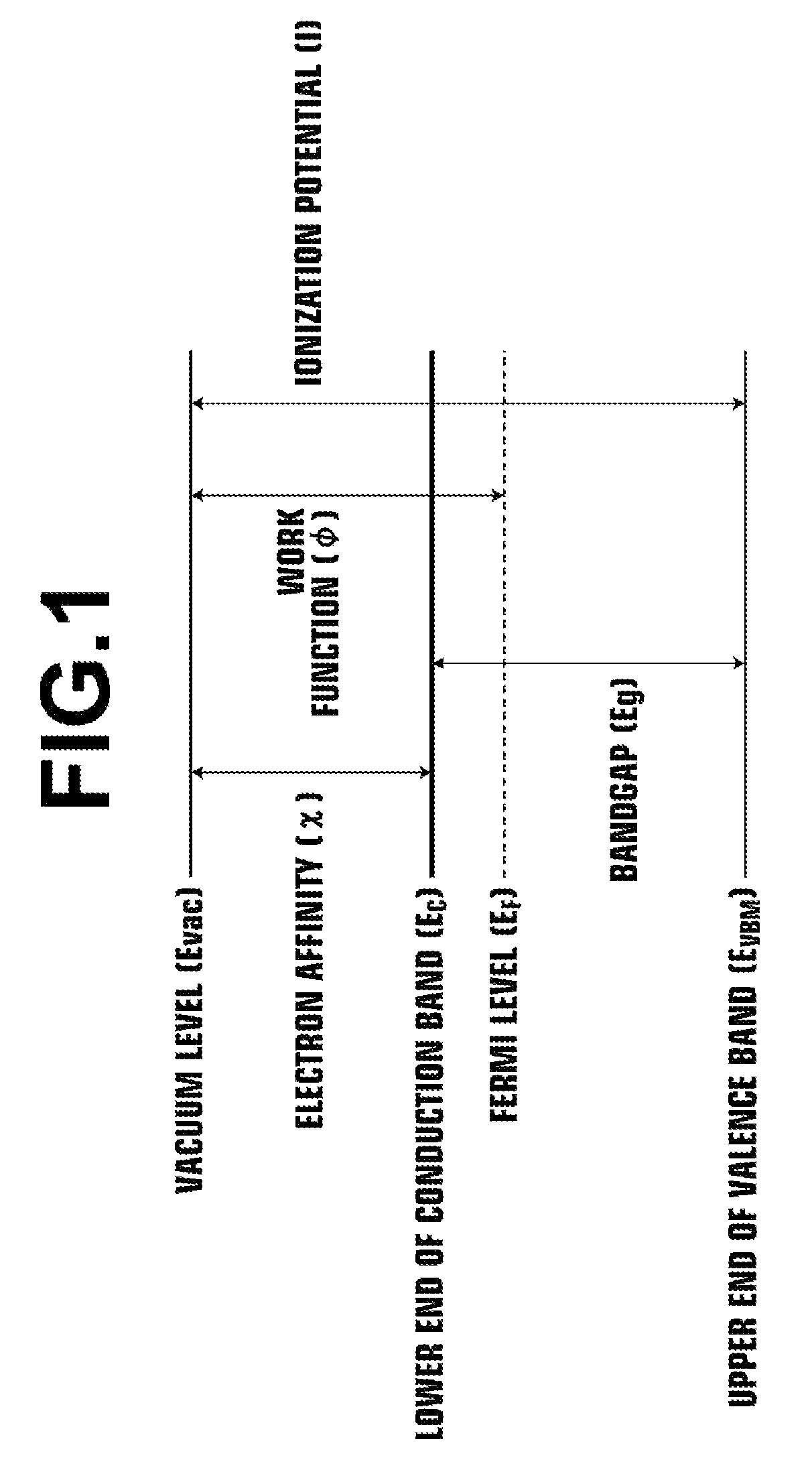

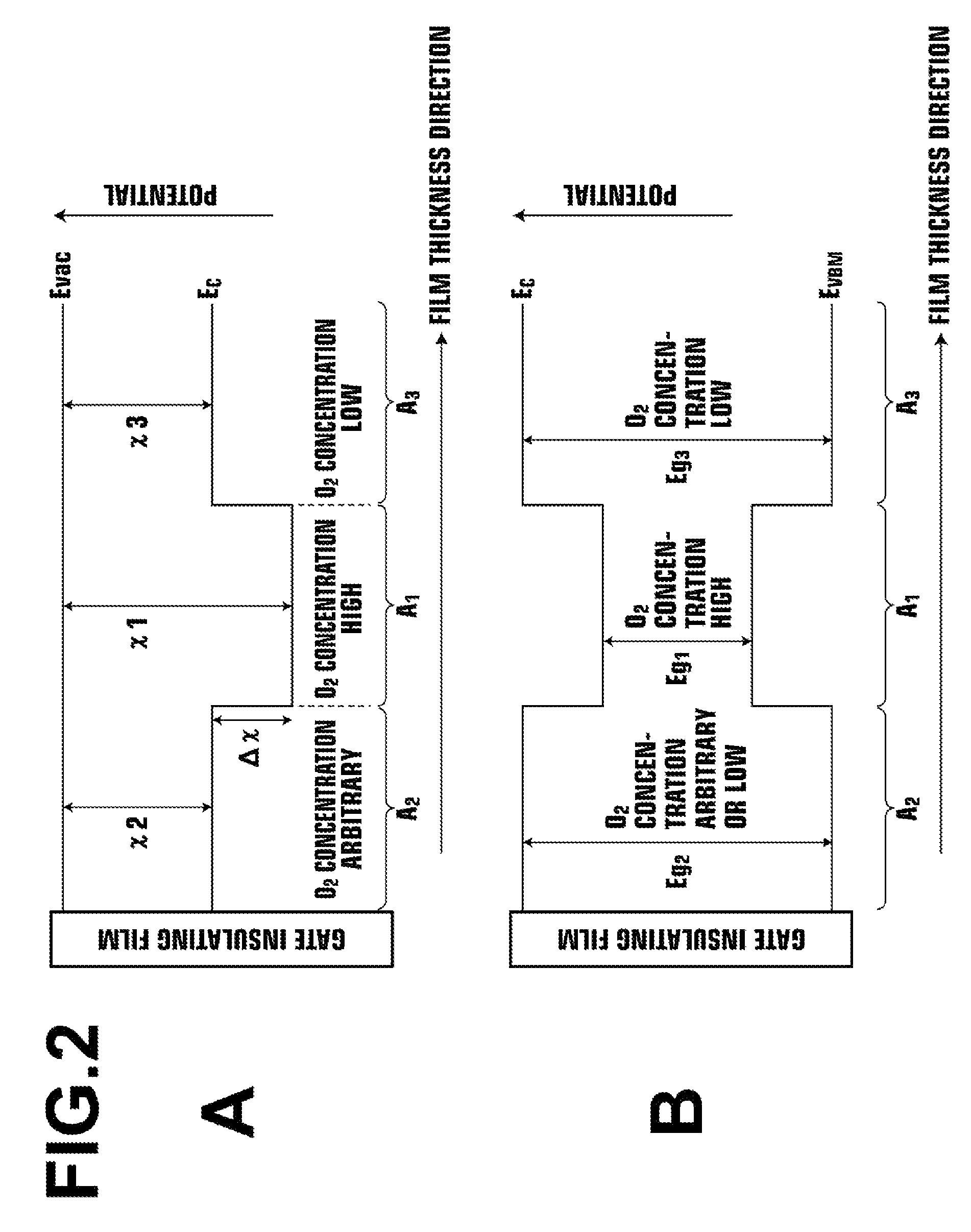

ActiveUS20110140100A1Low mobilityIncrease carrier densityTransistorSemiconductor/solid-state device manufacturingOxygenSemiconductor

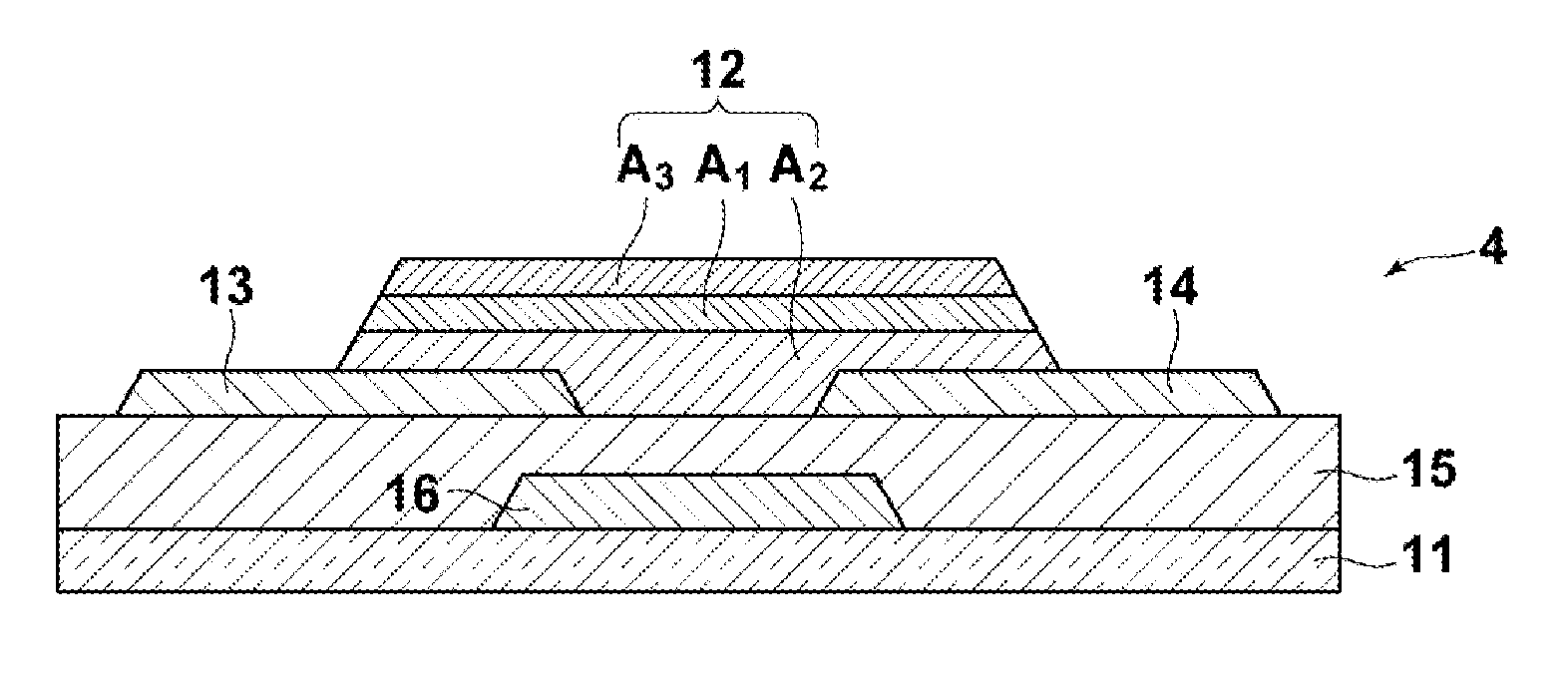

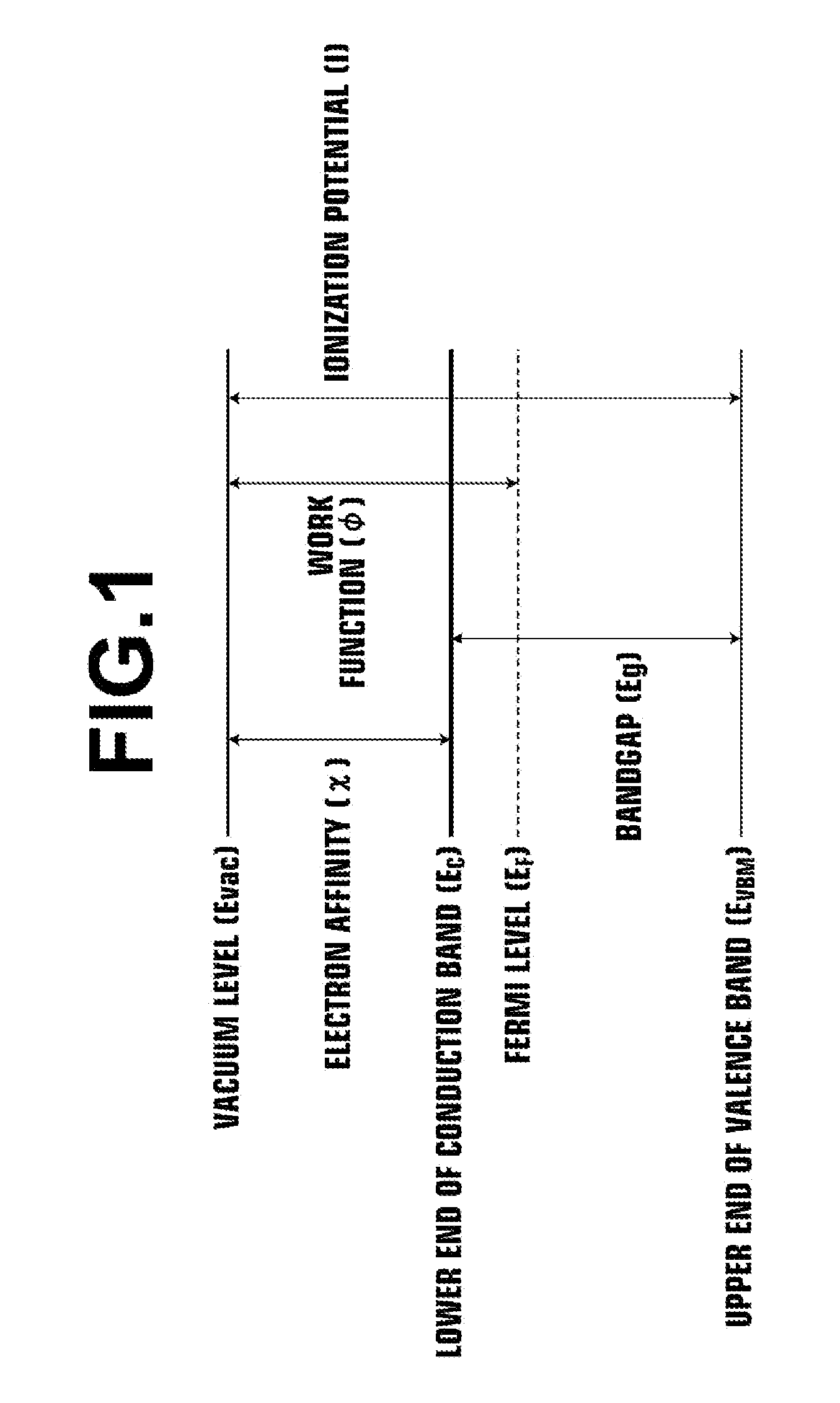

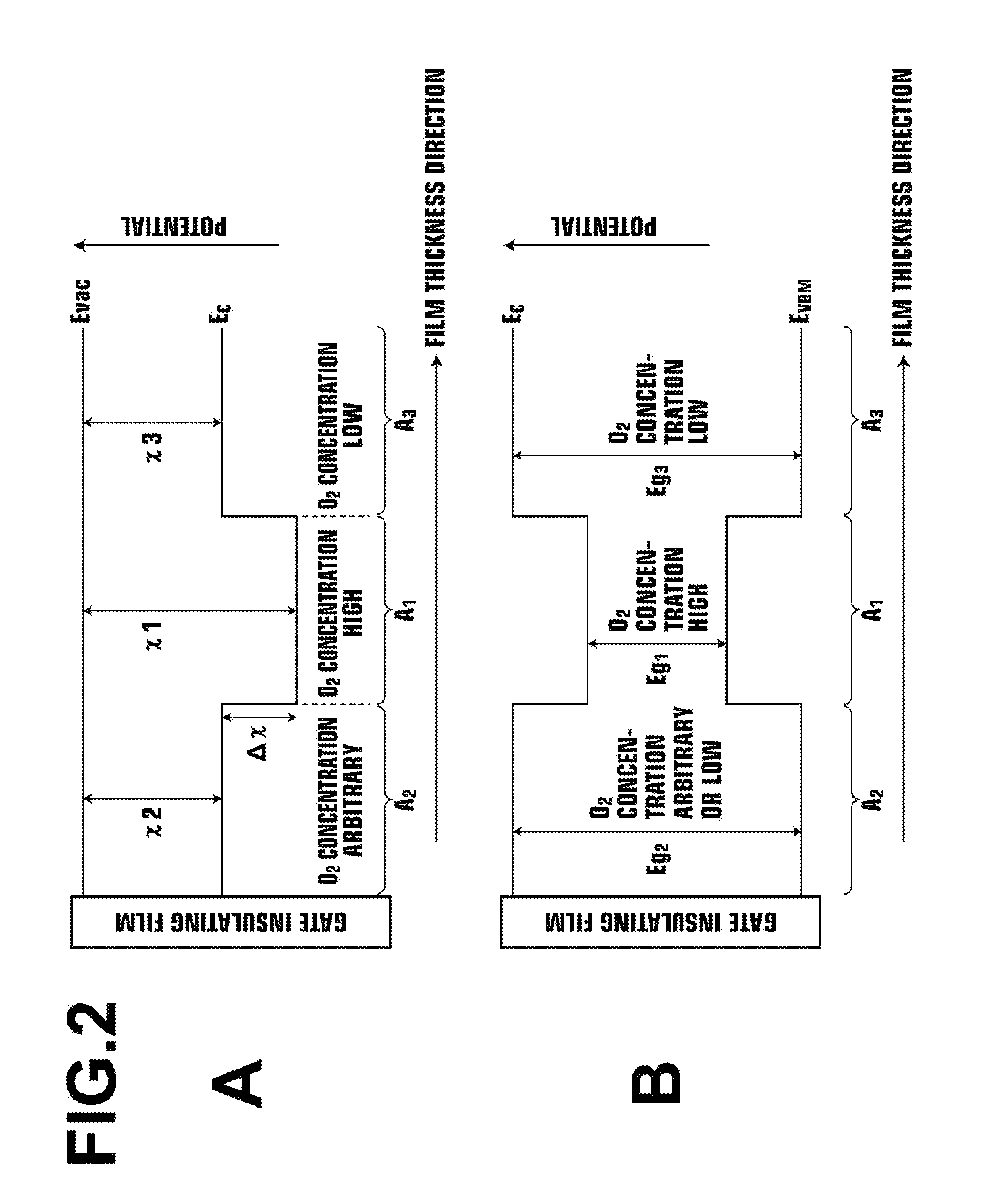

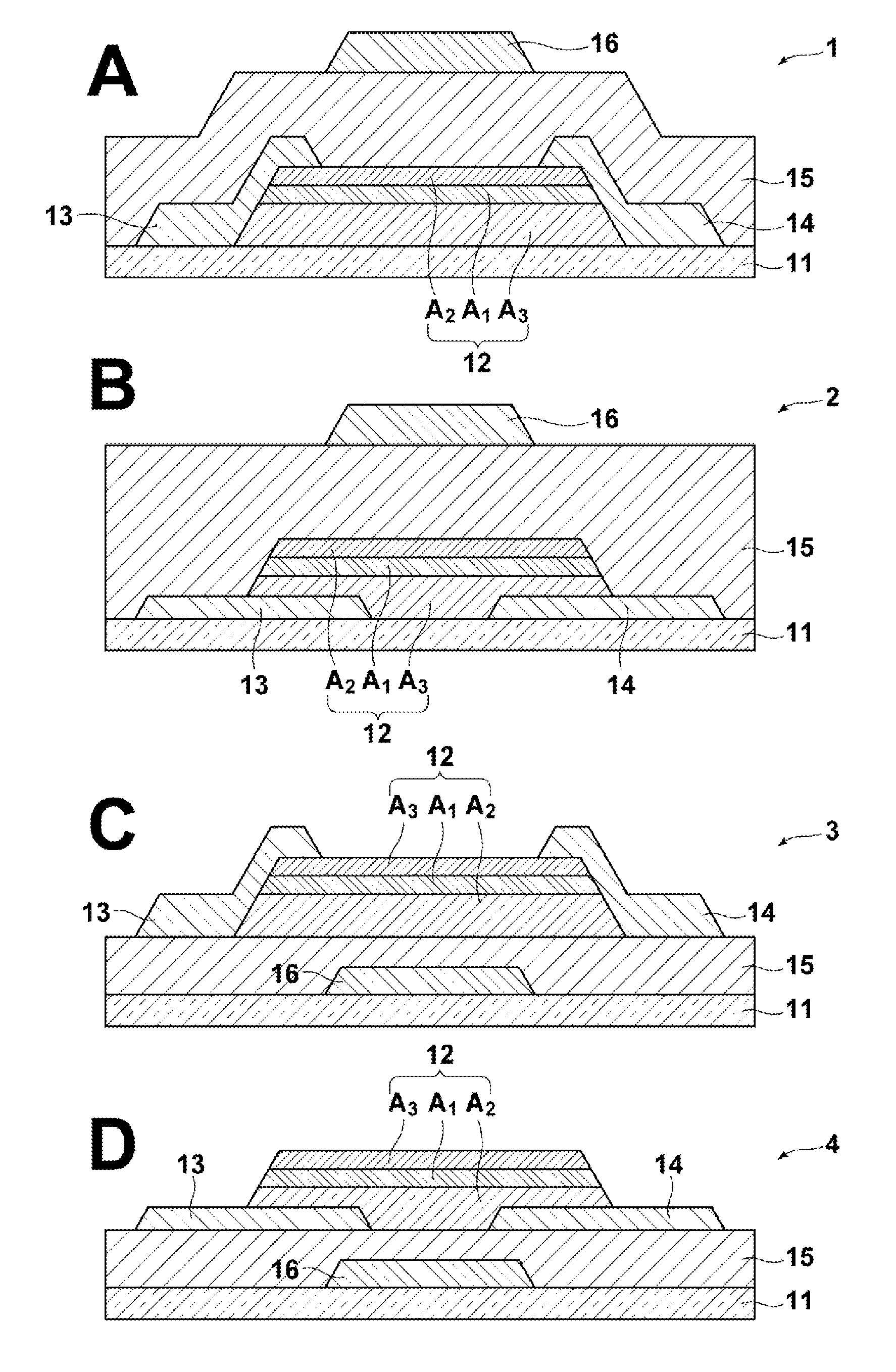

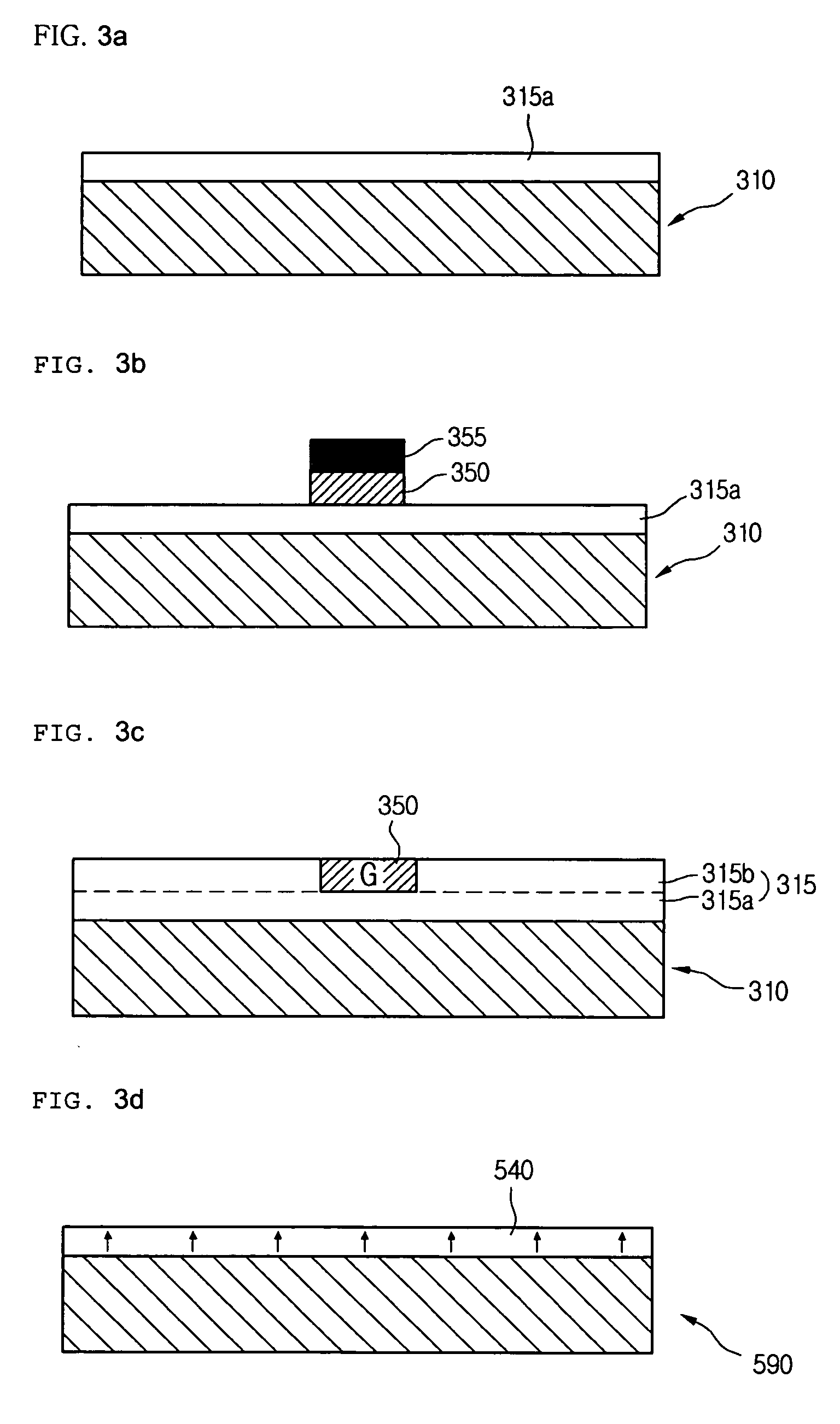

A thin-film transistor including an oxide semiconductor layer is disclosed. The oxide semiconductor layer includes a first area, a second area and a third area forming a well-type potential in the film-thickness direction. The first area forms a well of the well-type potential and has a first electron affinity. The second area is disposed nearer to the gate electrode than the first area and has a second electron affinity smaller than the first electron affinity. The third area is disposed farther from the gate electrode than the first area and has a third electron affinity smaller than the first electron affinity. At least an oxygen concentration at the third area is lower than an oxygen concentration at the first area.

Owner:SAMSUNG DISPLAY CO LTD

Thin-film transistor, method of producing the same, and devices provided with the same

ActiveUS8692252B2Improve performanceImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesOxygenSemiconductor

Owner:SAMSUNG DISPLAY CO LTD

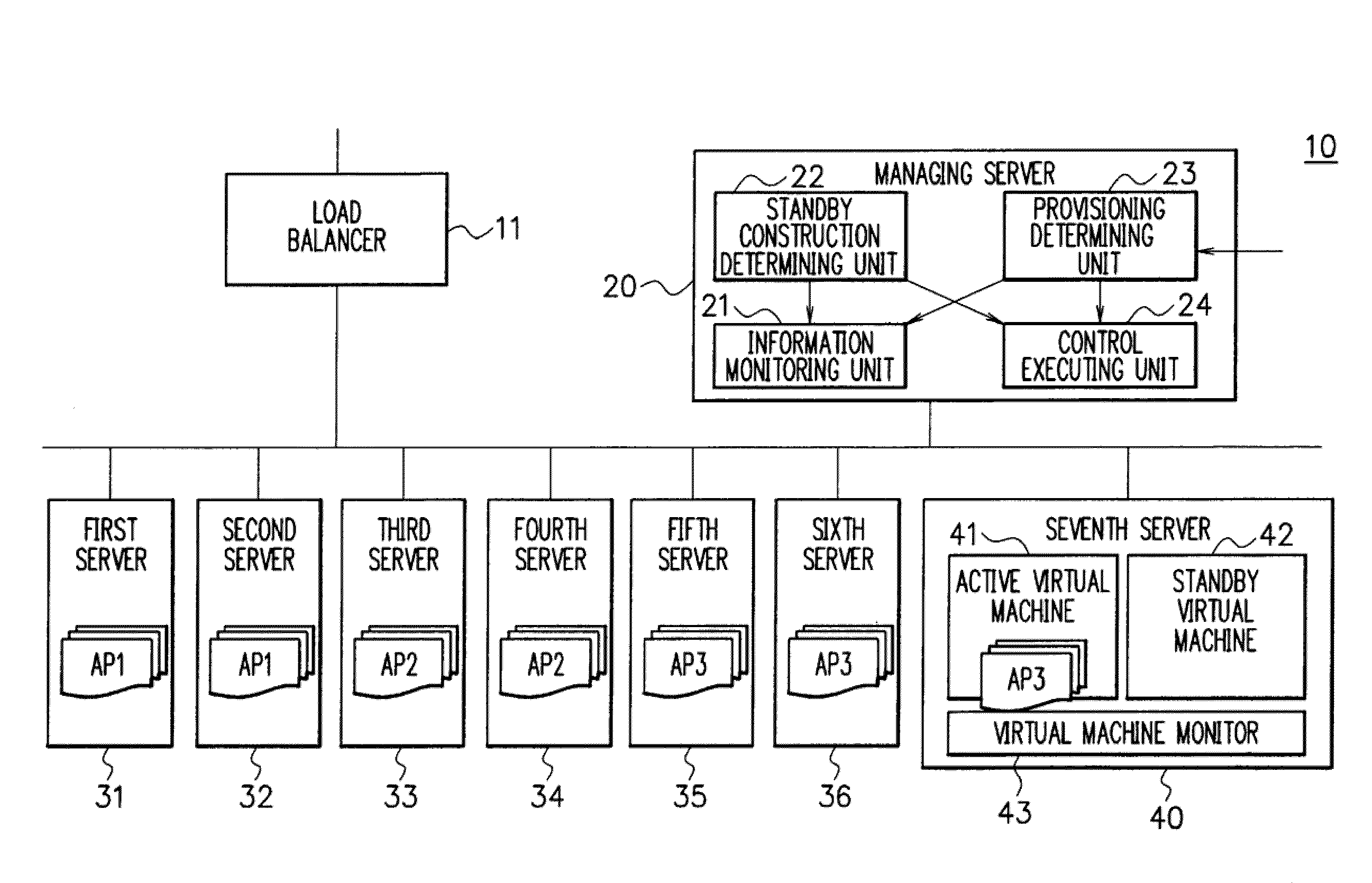

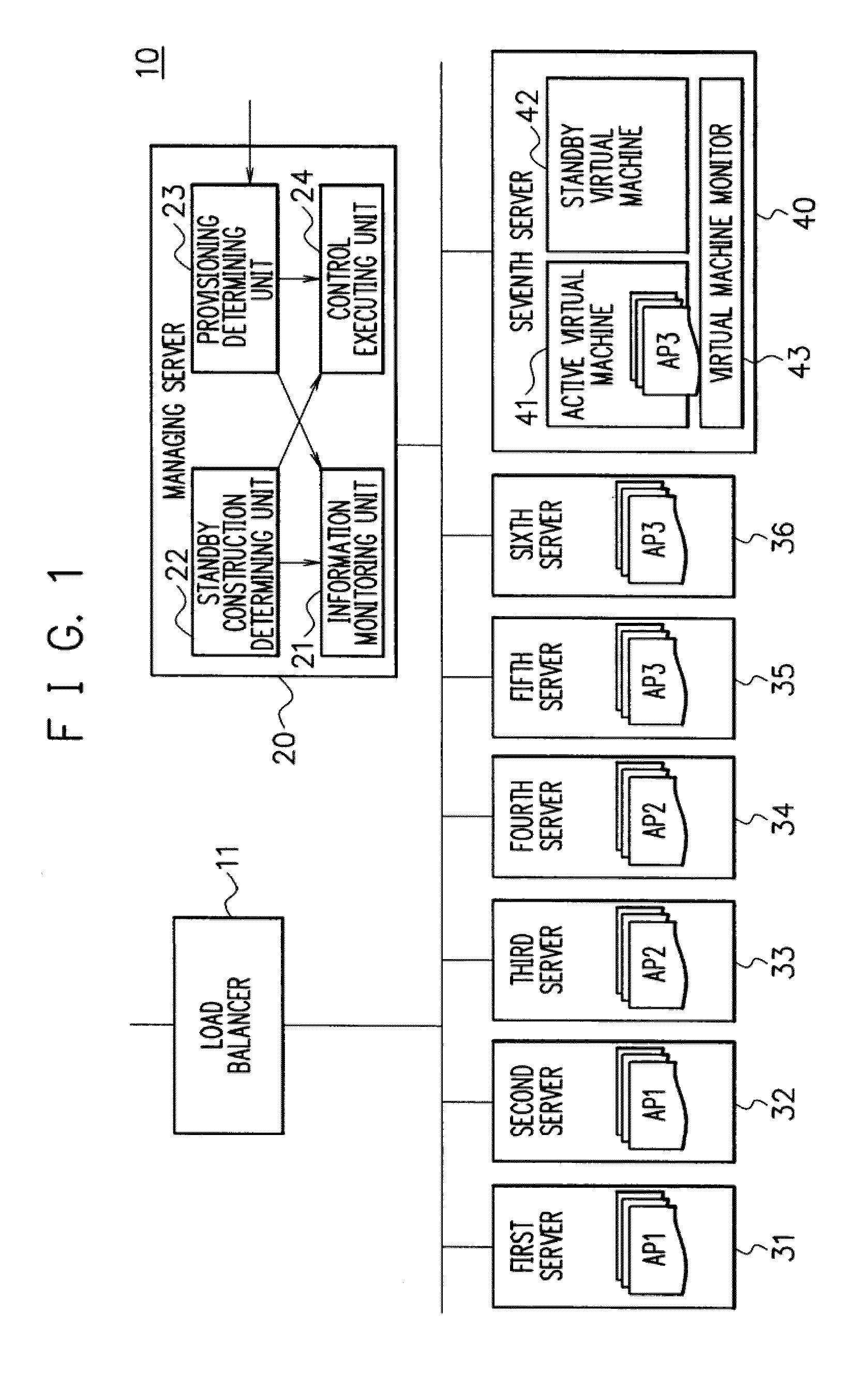

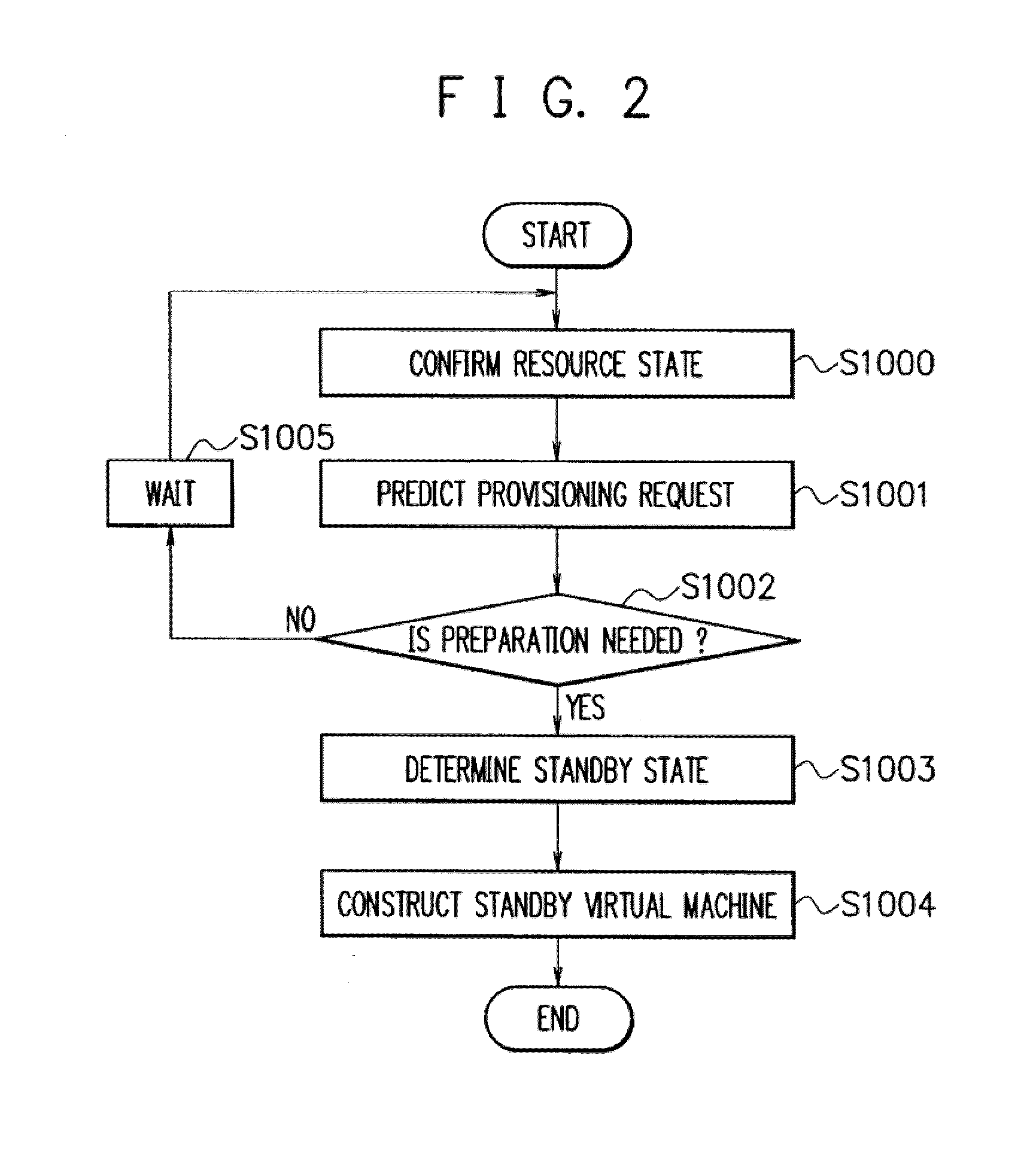

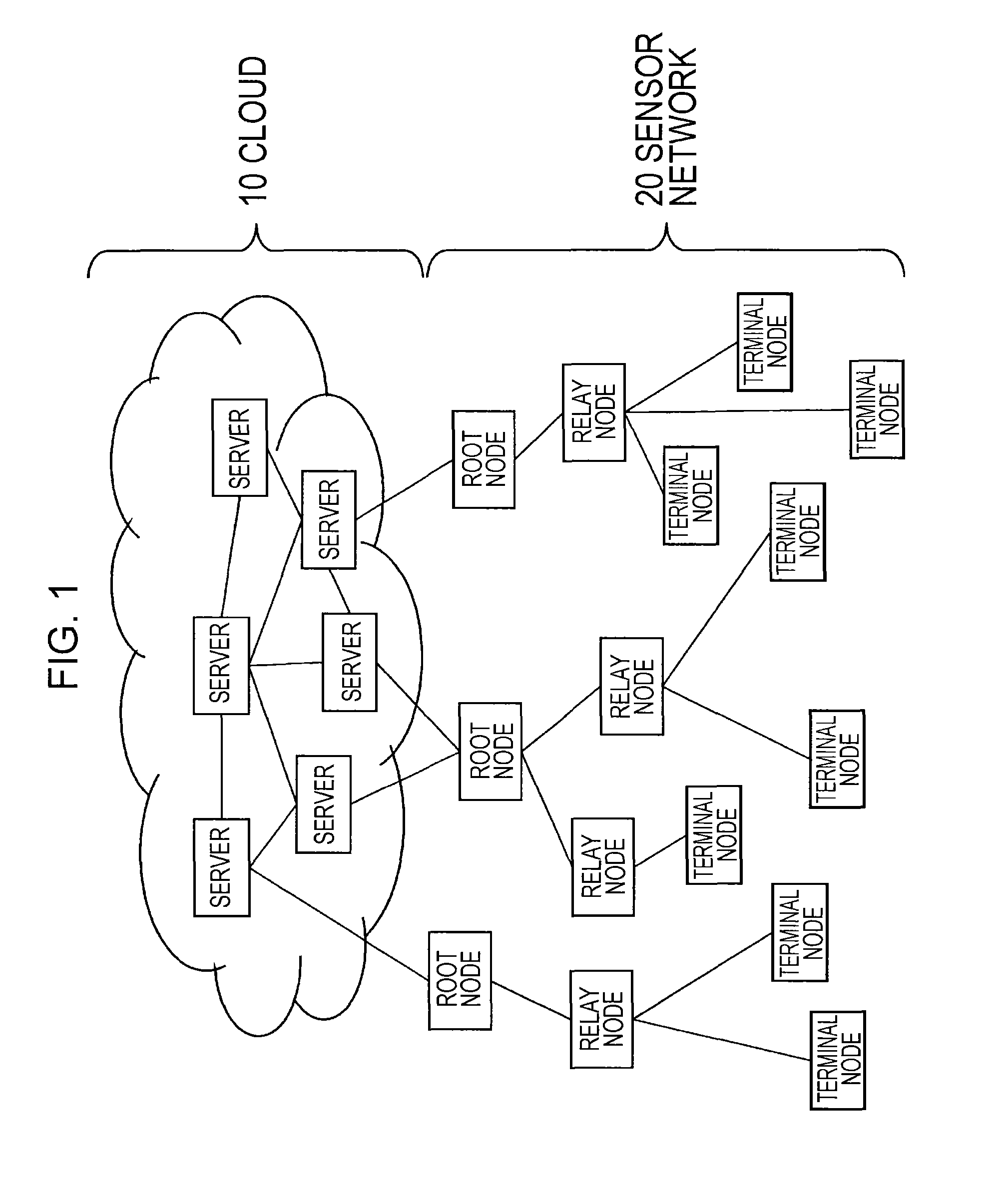

Provisioning system, method, and program

ActiveUS20100058342A1Addressing slow performanceEasy to useResource allocationSoftware simulation/interpretation/emulationResource allocationComputer science

A shared server 40 includes an active virtual machine 41 where a sufficient amount of resources are allocated to an operation of an application system and a standby virtual machine 42 that starts with a minimum amount of resources. When it is predicted that a provisioning request is generated, a standby construction determining unit 22 previously executes provisioning on a standby virtual machine 42, and performs a start of an OS and an application or a setting change of a network apparatus. A provisioning determining unit 23 changes the resource allocation amounts of the active virtual machine 41 and the standby virtual machine 42, allocates a sufficient amount of resources to the standby virtual machine 42, registers the standby virtual machine 42 as a target of load balancing in a load balancer 11, and executes provisioning.

Owner:NEC CORP

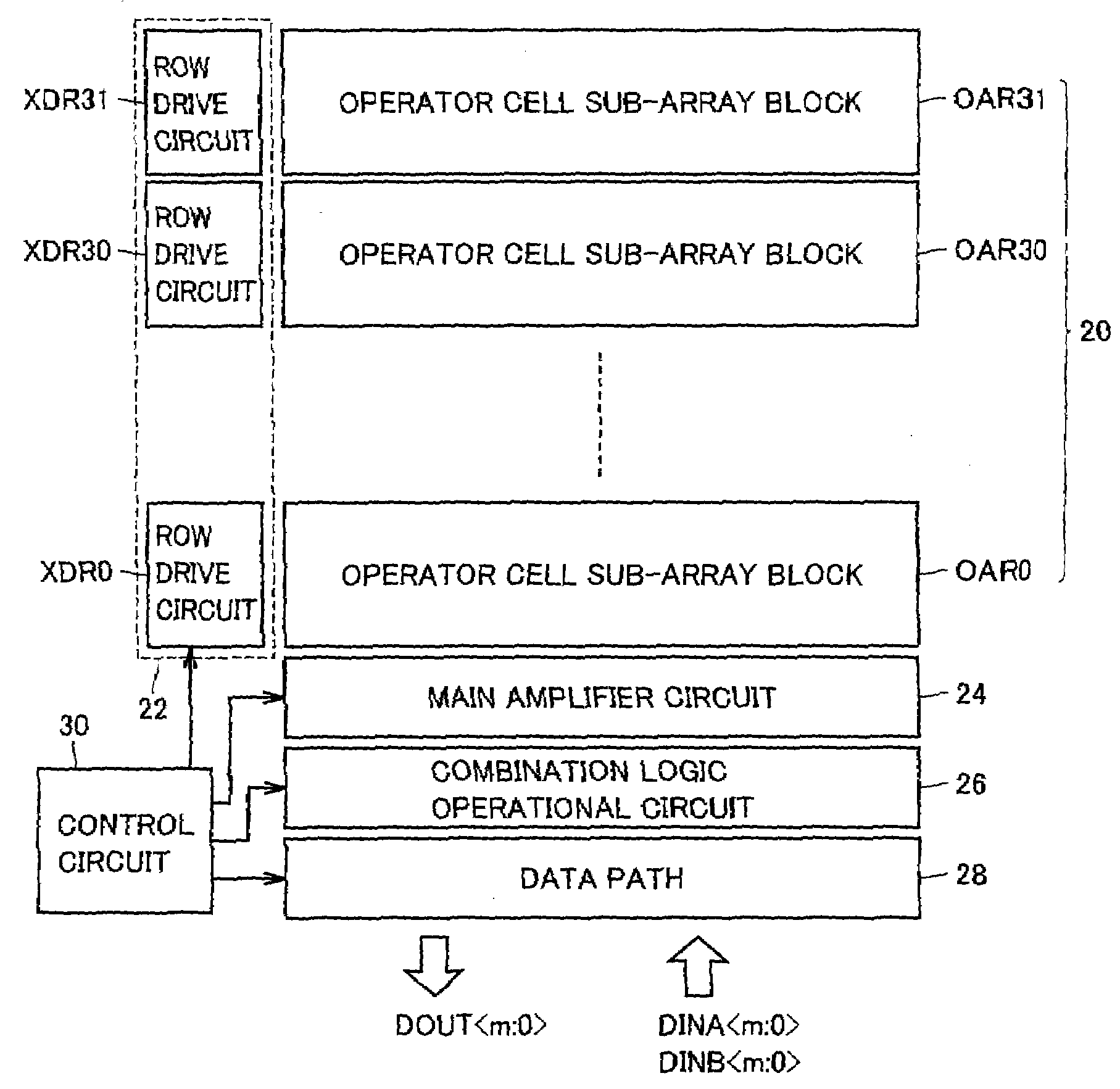

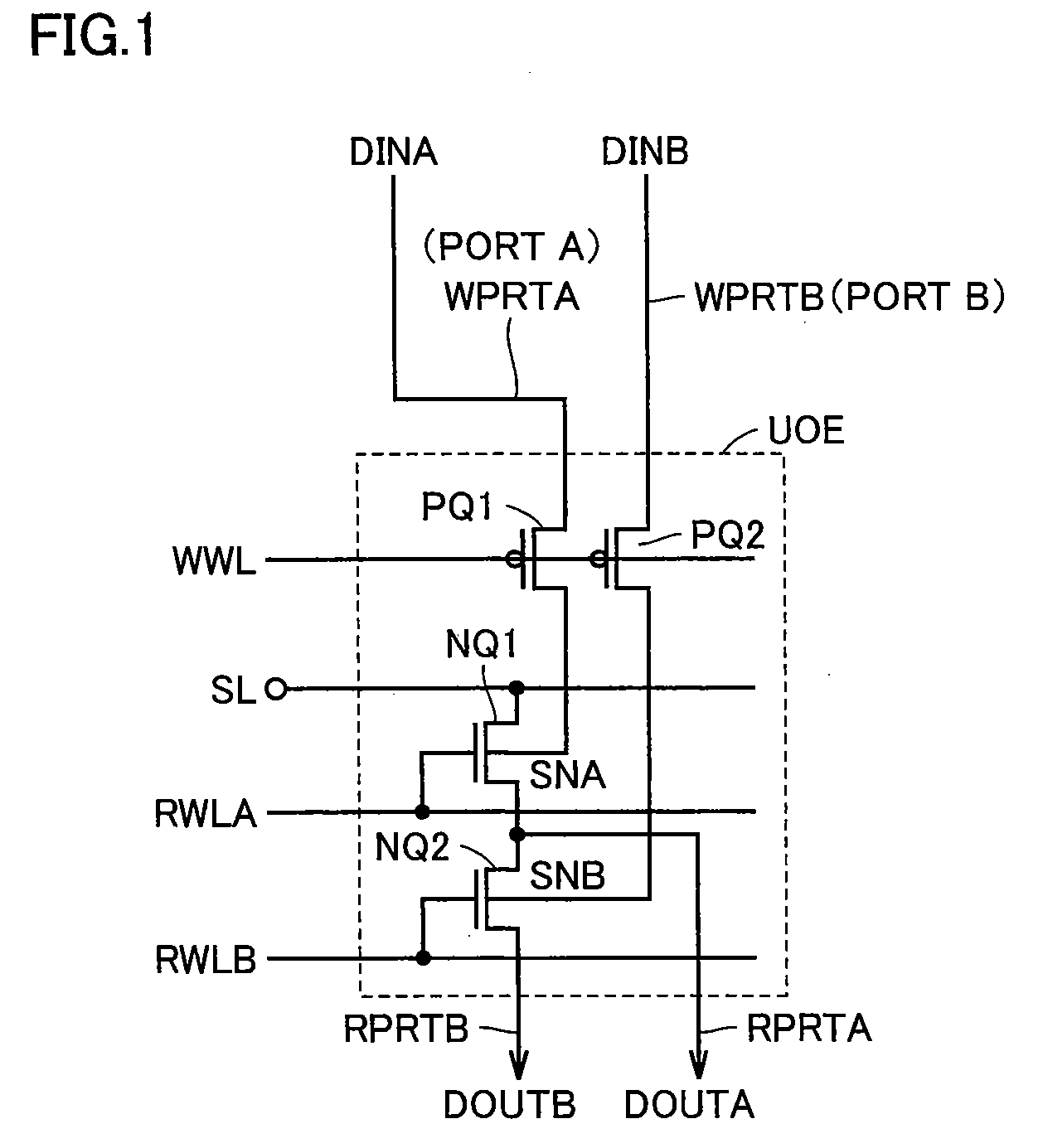

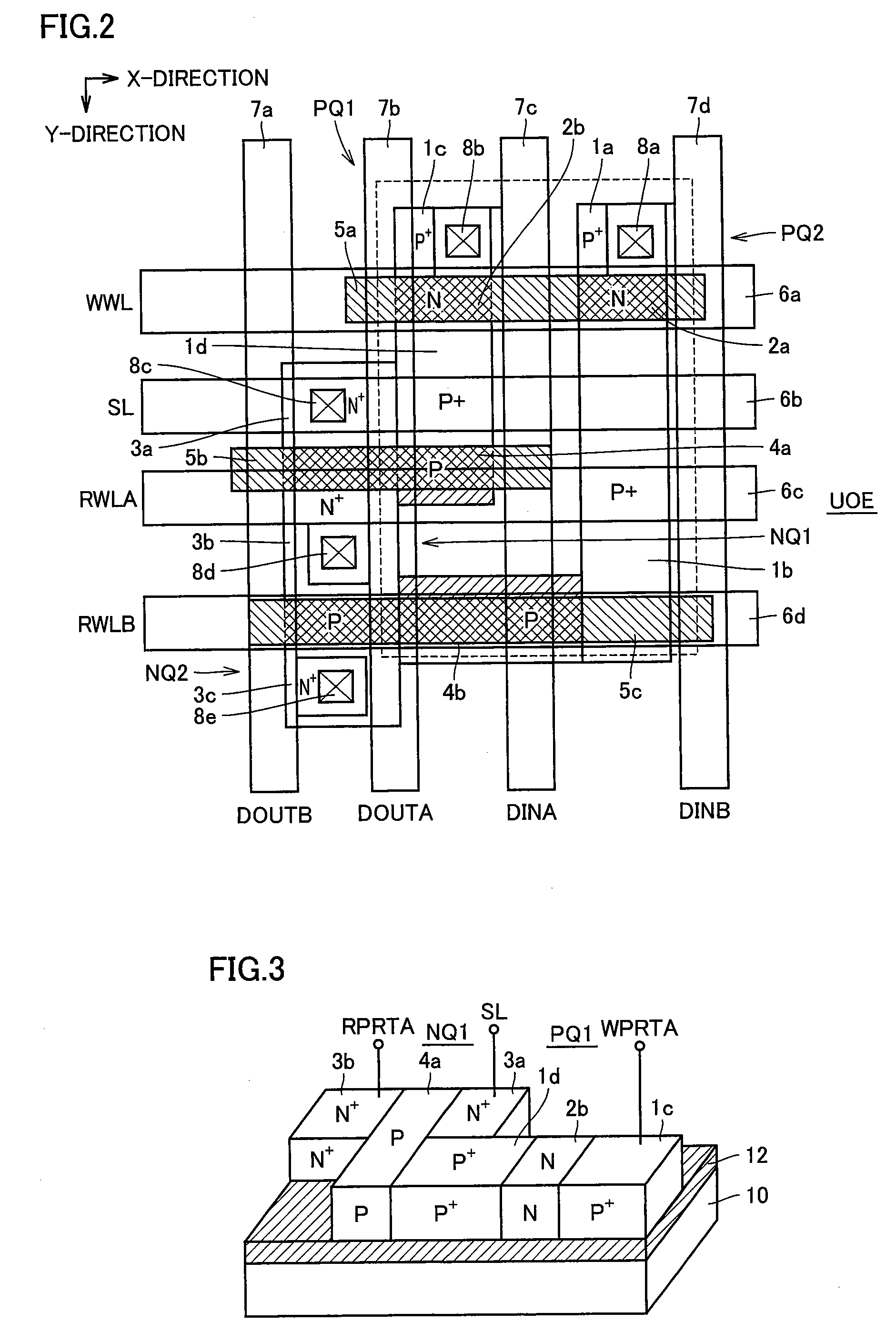

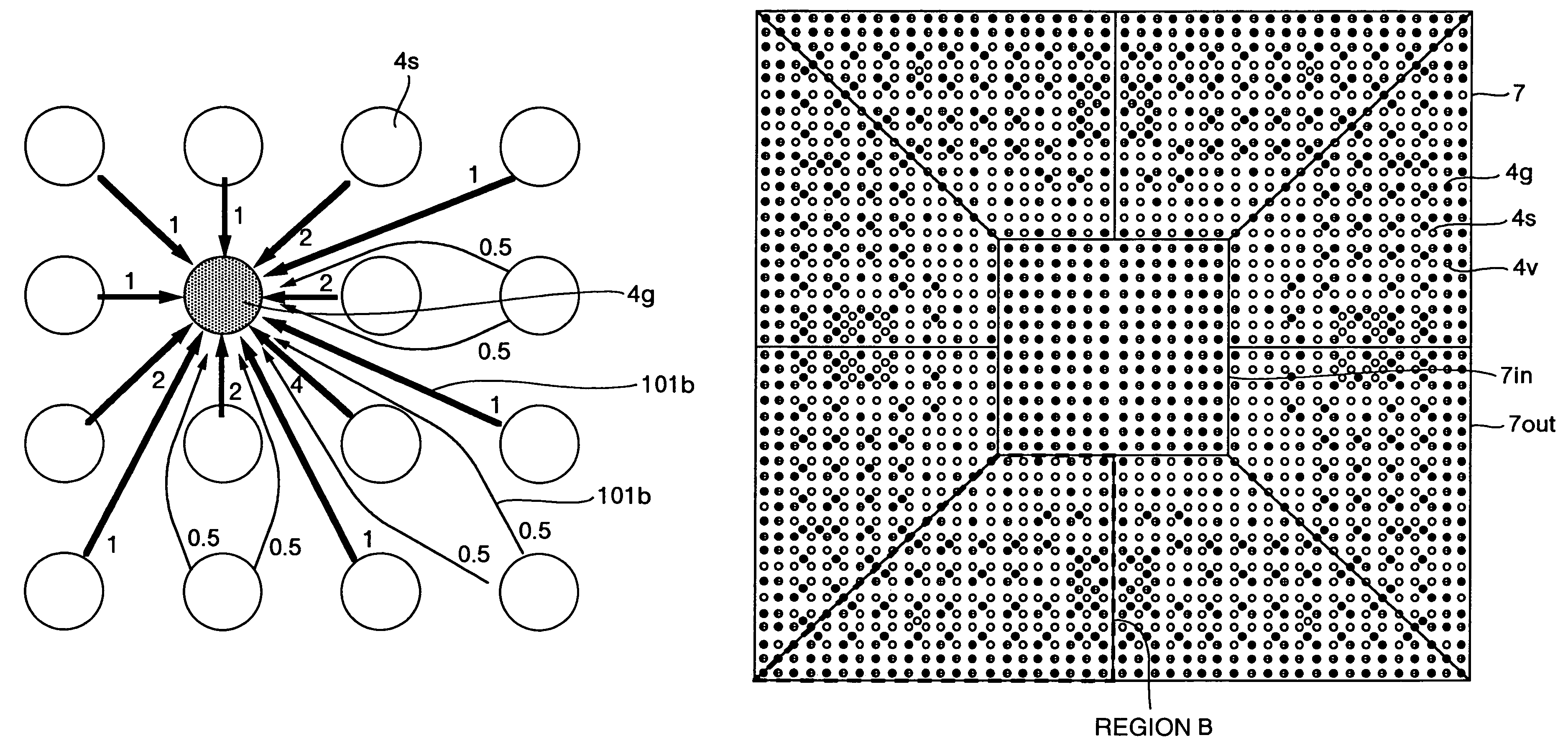

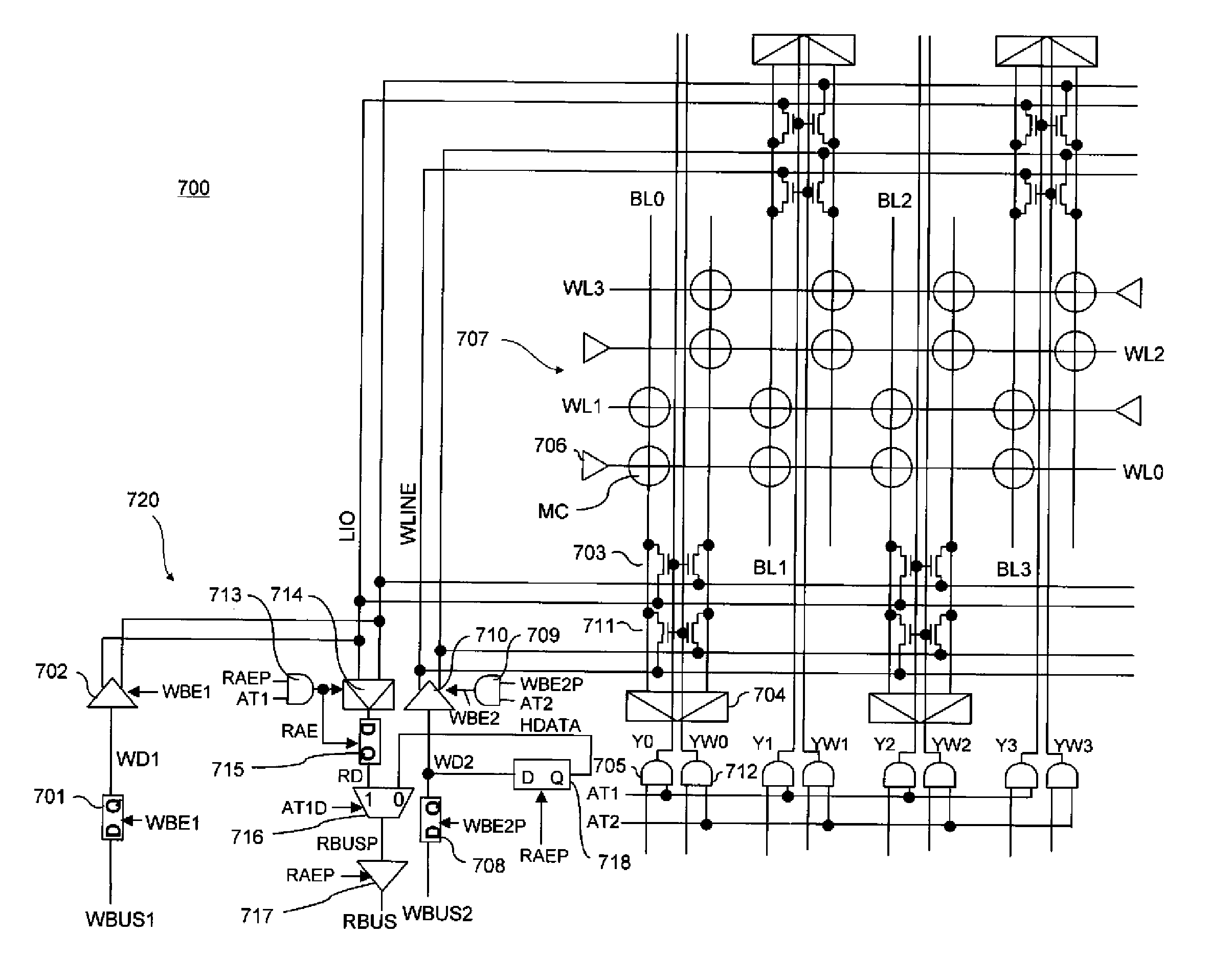

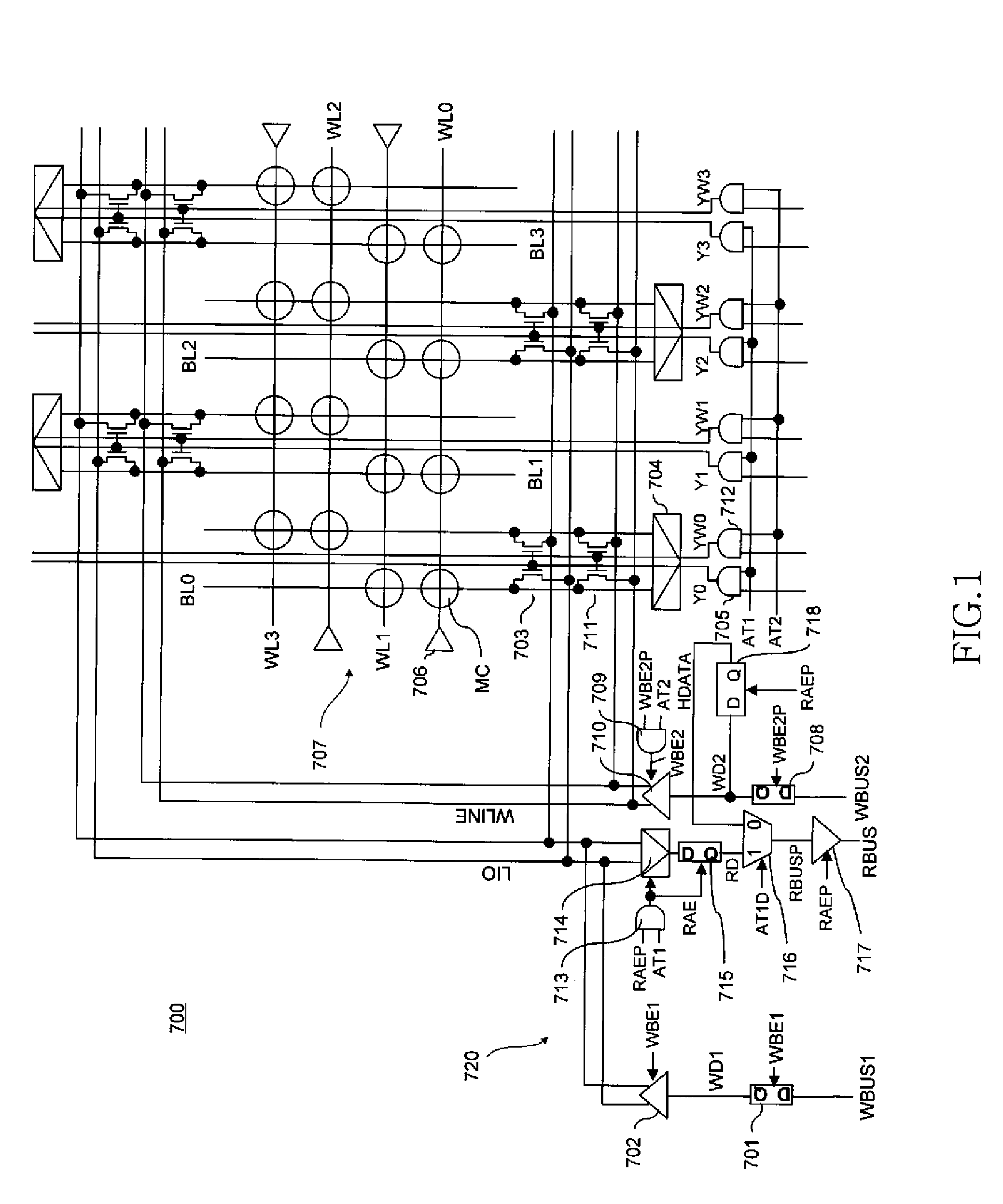

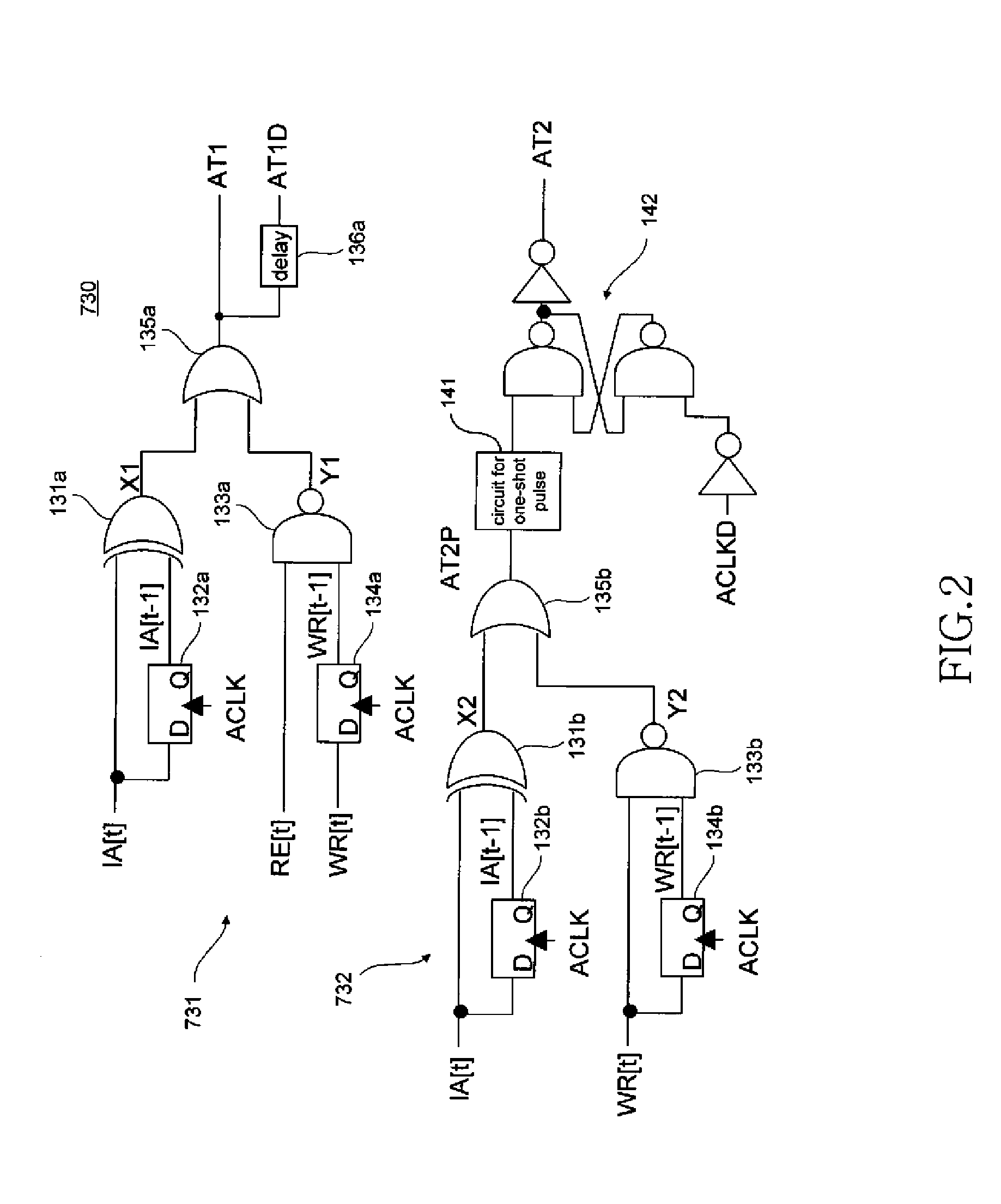

Semiconductor signal processing device

InactiveUS20090207642A1Small footprintIncrease speedSolid-state devicesDigital storageSoftware engineeringData storing

A unit operator cell includes a plurality of SOI (Silicon on Insulator) transistors, write data is stored in a body region of at least two SOI transistors, and the storage SOI transistors are connected in series with each other to a read port or each of the storage SOI transistors is singly connected to the read port. Therefore, an AND operation result or a NOT operation result of data stored in the unit operator cells can be obtained, and operation processing can be performed only by writing and reading data. A semiconductor signal processing device that can perform logic operation processing and arithmetic operation processing at high speed is implemented with low power consumption and a small occupation area.

Owner:RENESAS ELECTRONICS CORP

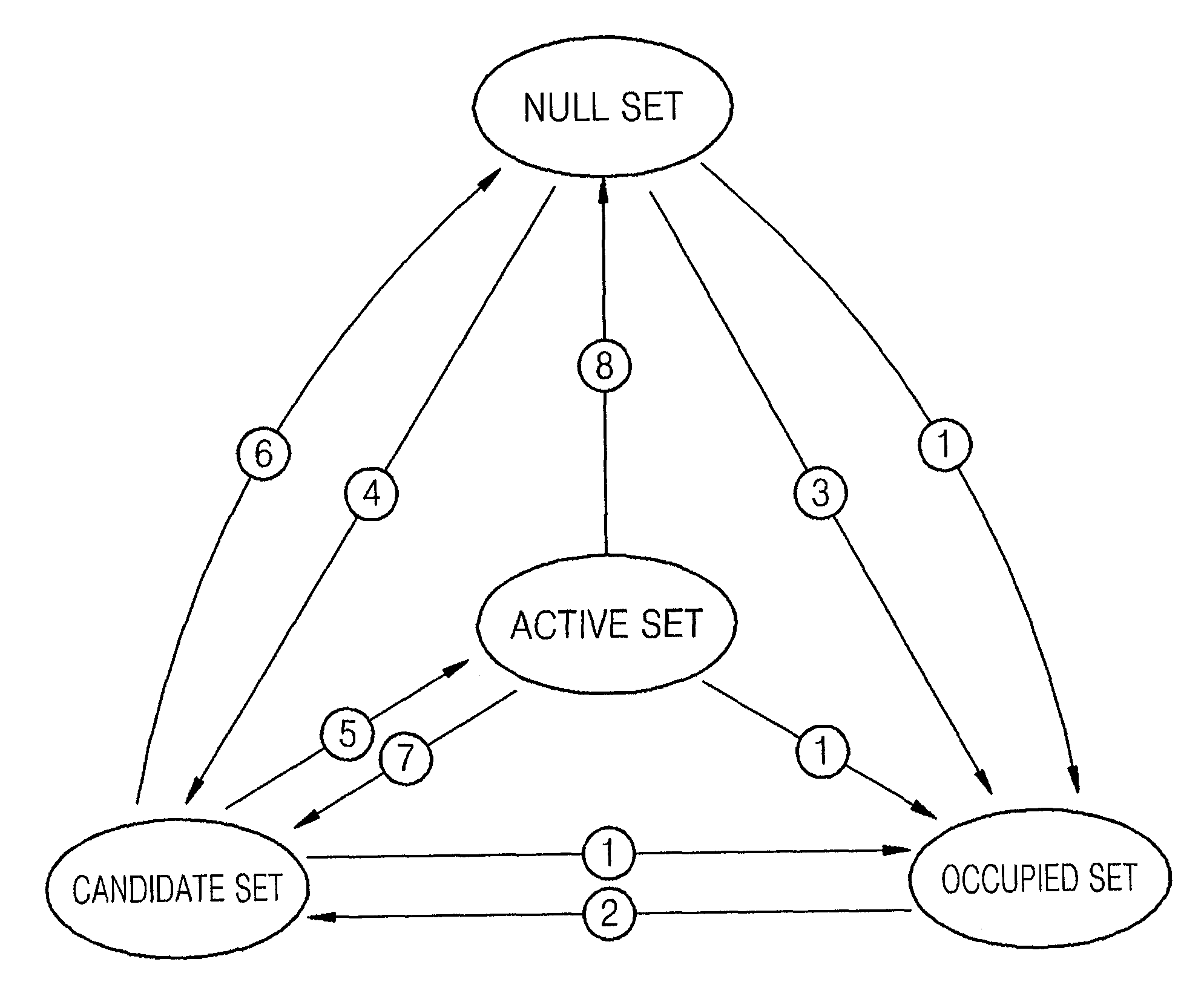

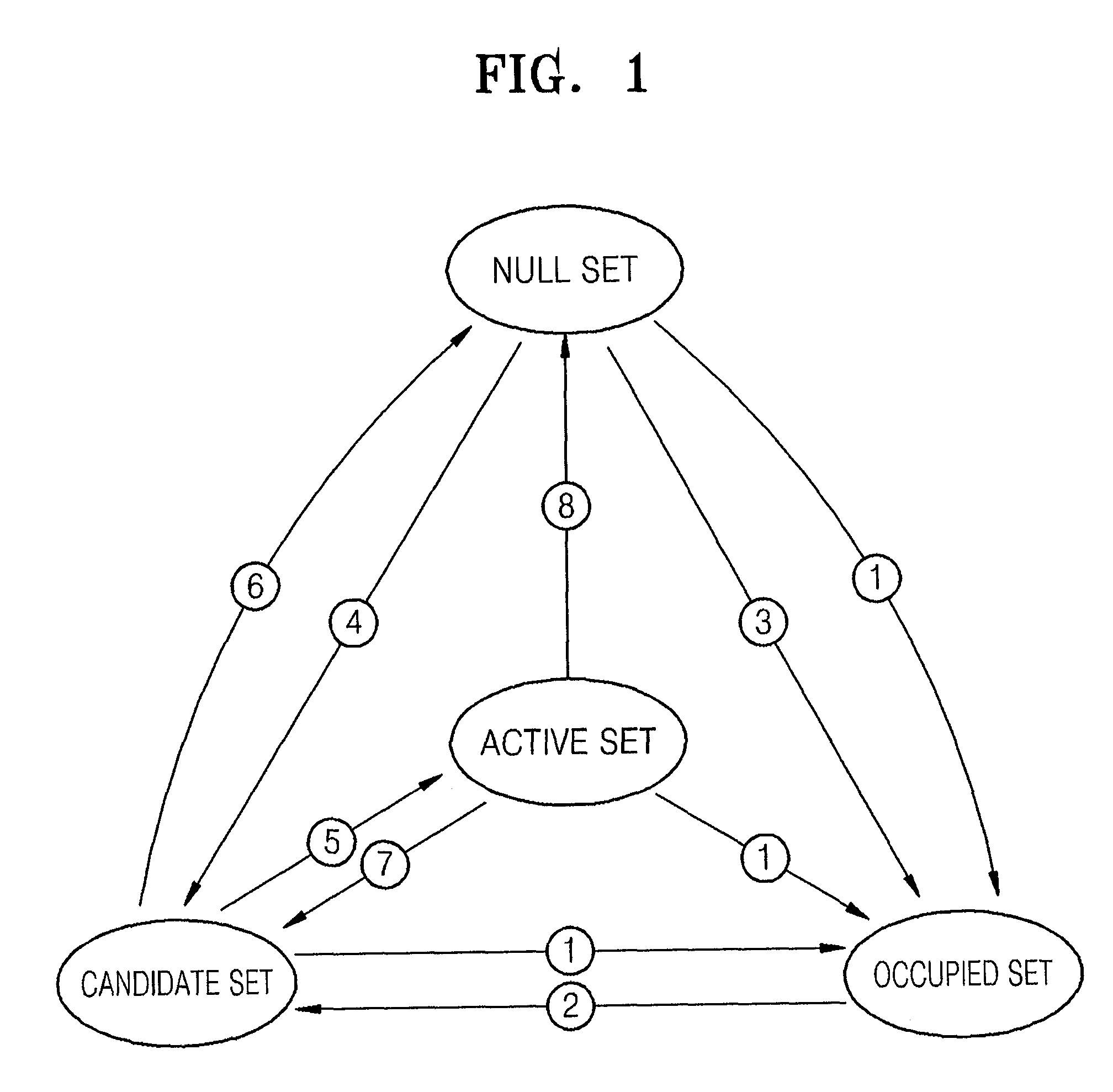

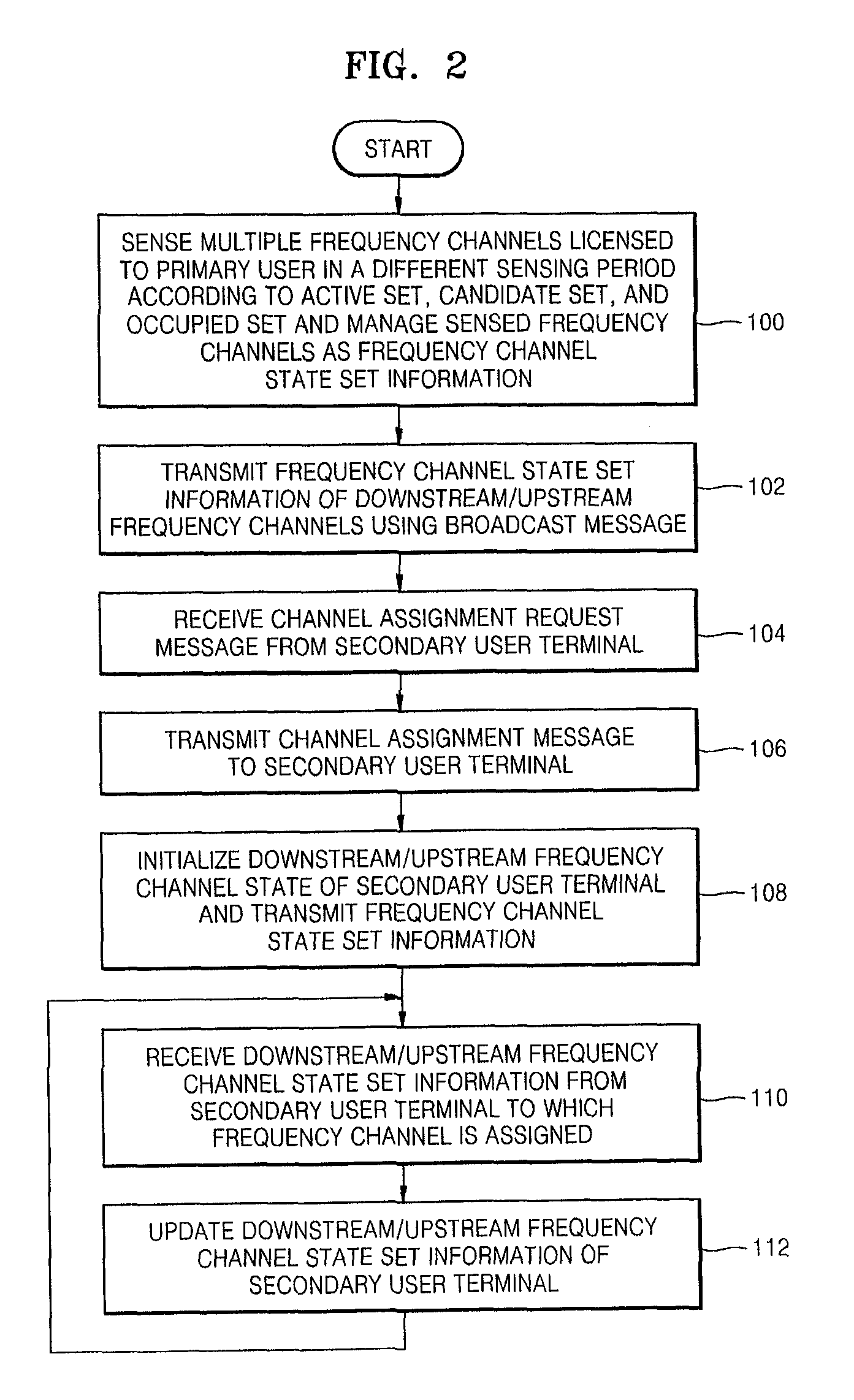

Method of frequency channel assignment using effective spectrum sensing in multiple frequency assignment system

ActiveUS20090161610A1Reduce in quantityHigh-speed performanceFrequency-division multiplexWireless commuication servicesMultiple frequencyAssignment methods

Provided is a method of assigning a frequency channel using efficient spectrum sensing in a multiple Frequency Assignment (FA) system. The method includes a channel sensing process, wherein abase station (BS) of a secondary user classifies multiple frequency channels licensed to a primary user into a plurality of channel states by changing a sensing period according to the types of classified channel state sets, and manages the sensed channel states as frequency channel state set information; a channel state set broadcasting process, wherein the BS transmits the frequency channel state set information manage d in the channel sensing process to secondary user terminals using a broadcast message; and a channel assigning process, wherein if the BS receives a channel assignment request message from a new secondary user terminal which has received the broadcast message, the BS assigns an unused frequency channel from among frequency channels licensed to the primary user to the new secondary user terminal using the frequency channel state set information. Accordingly, a frequency channel can be assigned to a secondary user requesting channel assignment using frequency channel state set information without a primary user experiencing interference noise.

Owner:ELECTRONICS & TELECOMM RES INST

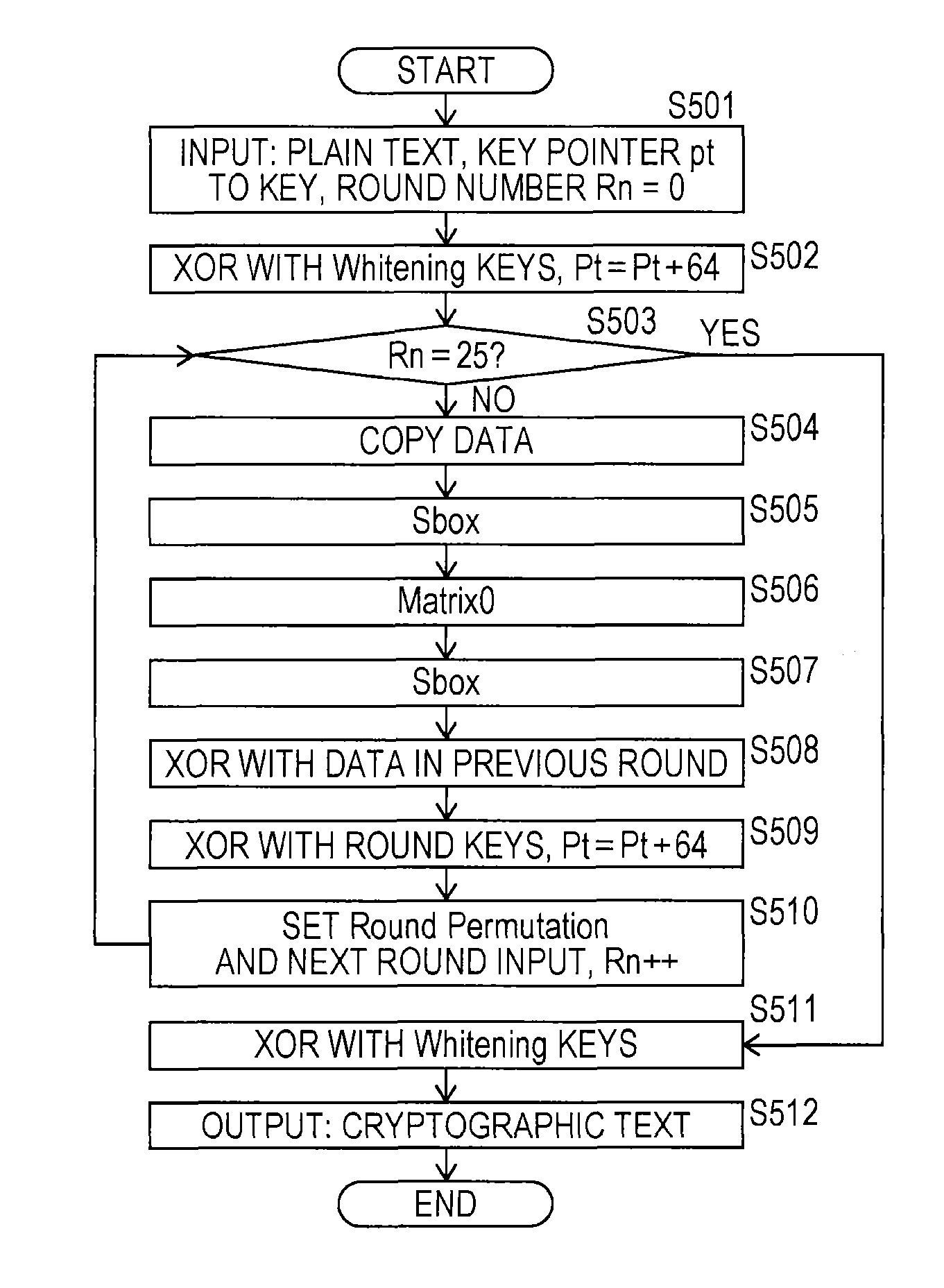

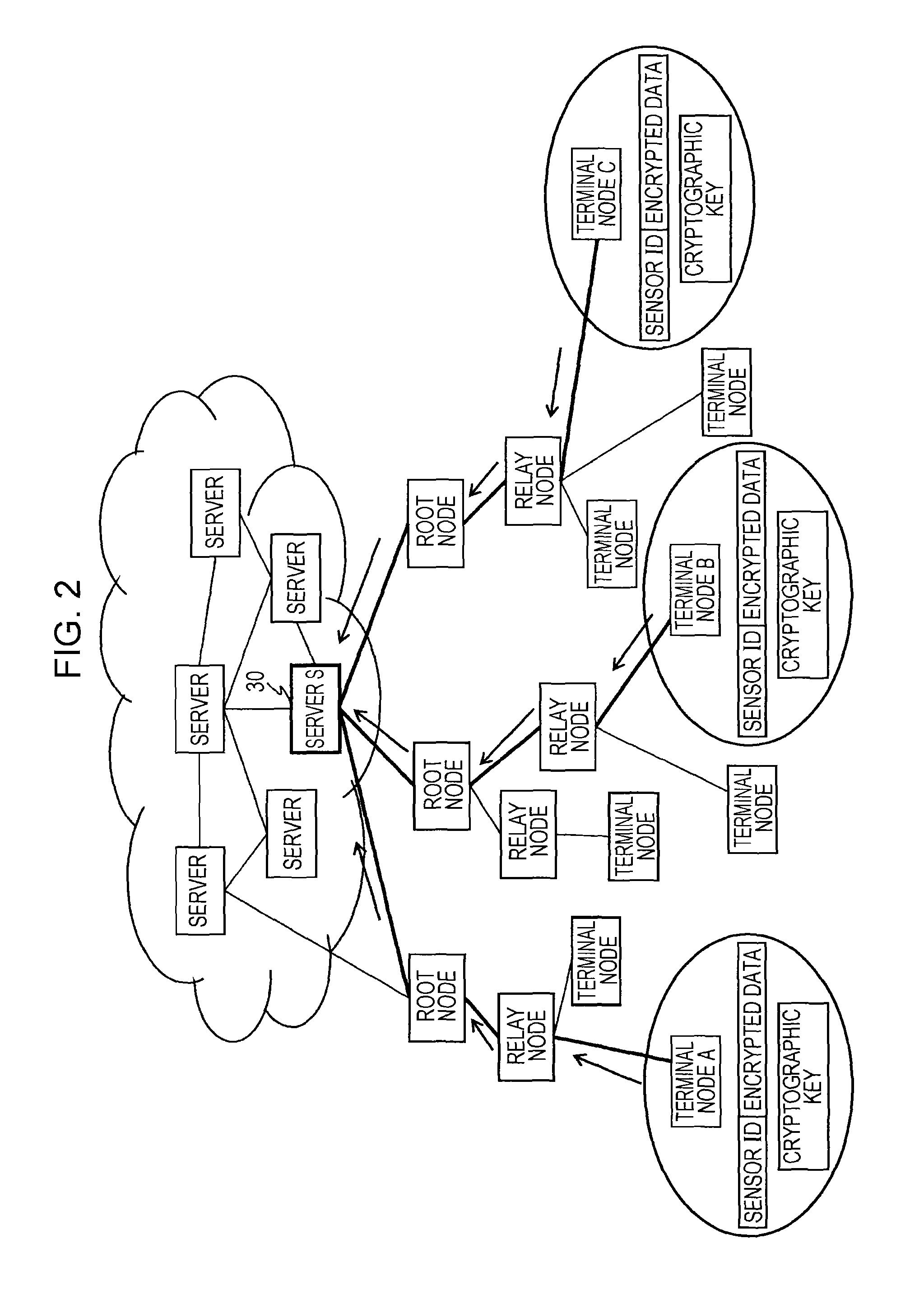

Information processing apparatus, information processing method, and program

ActiveUS9281940B2Fast processingHigh-speed performanceEncryption apparatus with shift registers/memoriesInternal/peripheral component protectionComputer hardwareInformation processing

Speed-up of a cryptographic process by software (program) is realized. A data processing unit which executes a data process according to a program defining a cryptographic process sequence is included, and the data processing unit, according to the program, generates a bit slice expression data based on a plurality of plain text data items which are encryption process targets and a bit slice expression key based on a cryptographic key of each plain text data item, generates a whitening key and a round key based on the bit slice expression key, executes the cryptographic process including operation and movement processes of a block unit of the bit slice expression data, and an operation using the round key, as a process according to a cryptographic algorithm Piccolo, and generates the plurality of encrypted data items corresponding to the plurality of plain text data items by the reverse conversion of the data with respect to the cryptographic process results.

Owner:SONY CORP

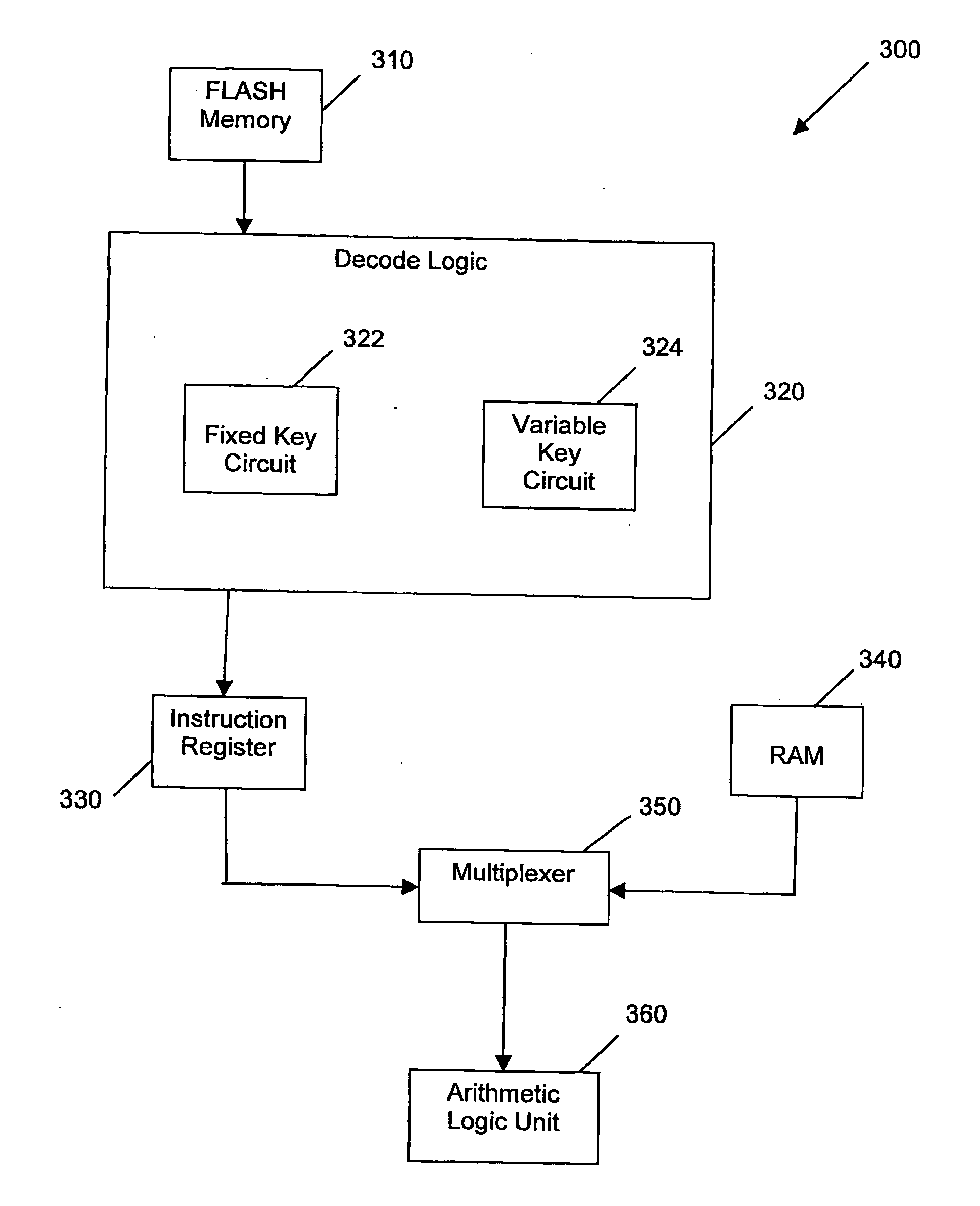

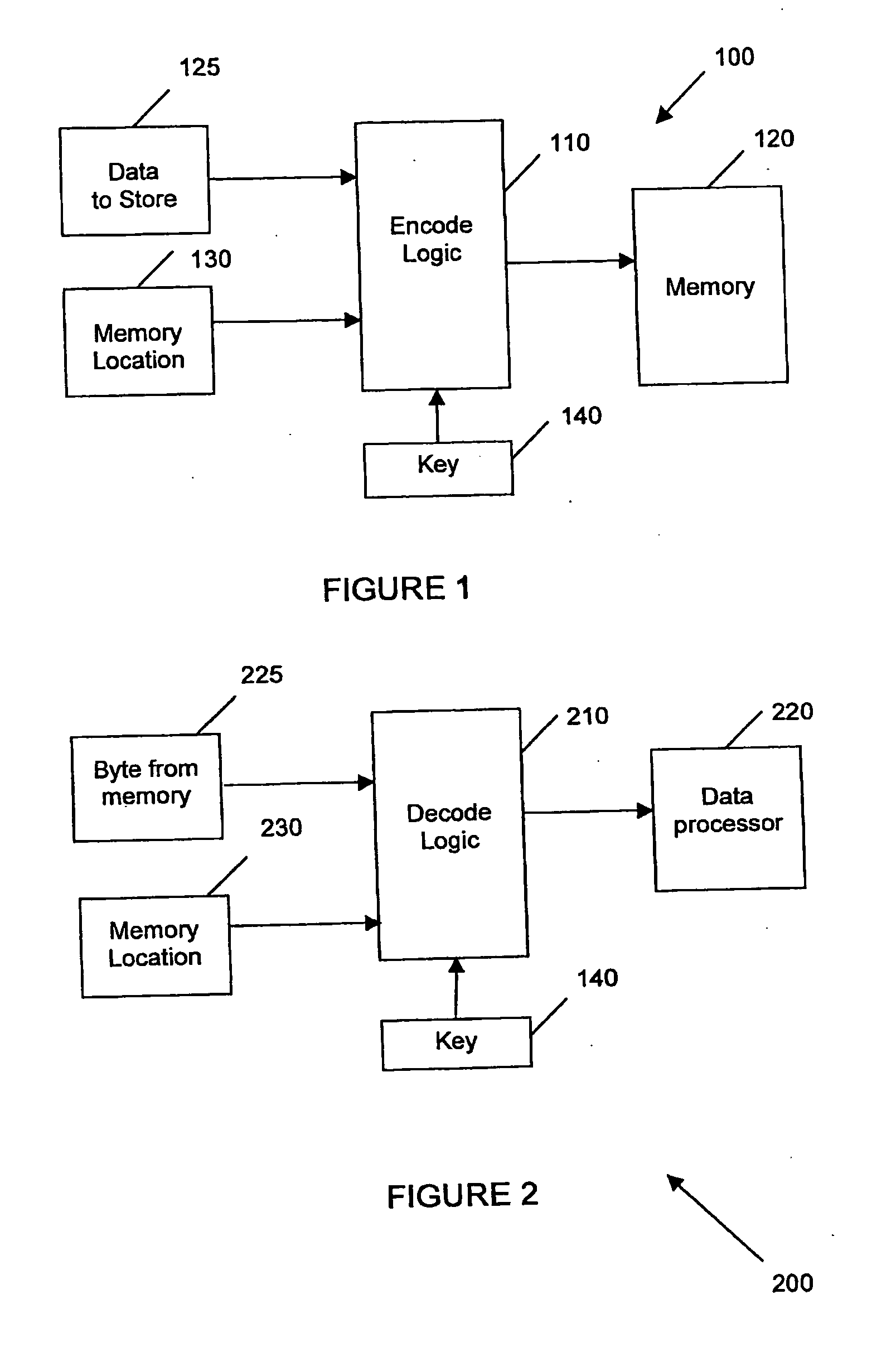

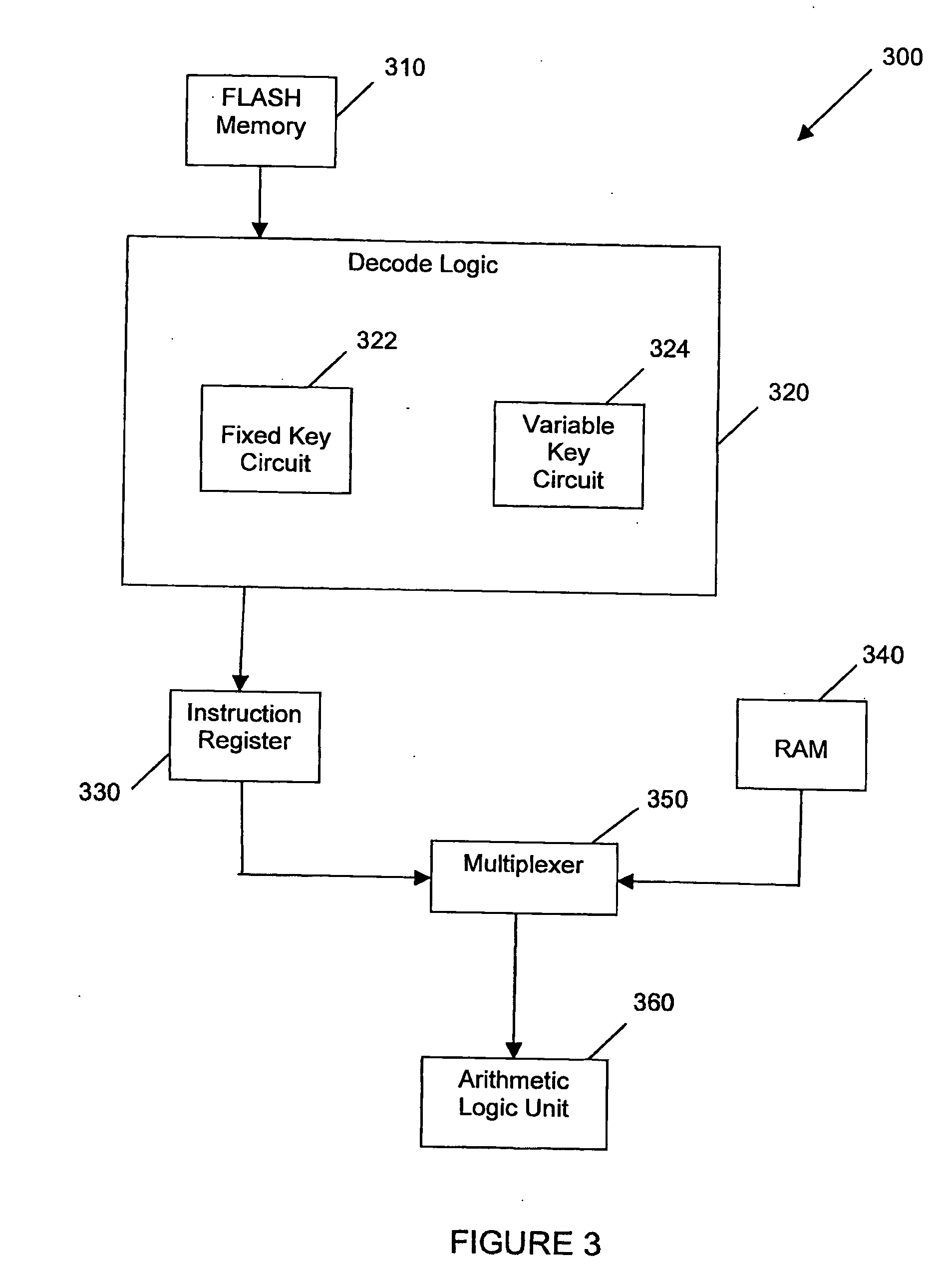

Method and system for microprocessor data security

InactiveUS20070172053A1Improve securityAvoid loopholesData stream serial/continuous modificationUser identity/authority verificationByteEncryption

Embodiments of the invention relate generally to methods and systems for microprocessor data security, involving data encryption and decryption of stored data in, or in communication with, a computer microprocessor. Such encryption and decryption can be performed on a per-byte basis. Such encryption and decryption involves performing a logic operation on the byte using a decryption key or encryption key to generate a respective decrypted byte or encrypted byte. The key can be fixed or variable or a combination of both. The key is encoded in a dedicated hard-wired key circuit within the microprocessor and accessible to encryption and decryption circuitry within the microprocessor.

Owner:UNIVERSAL DATA PROTECTION CORP

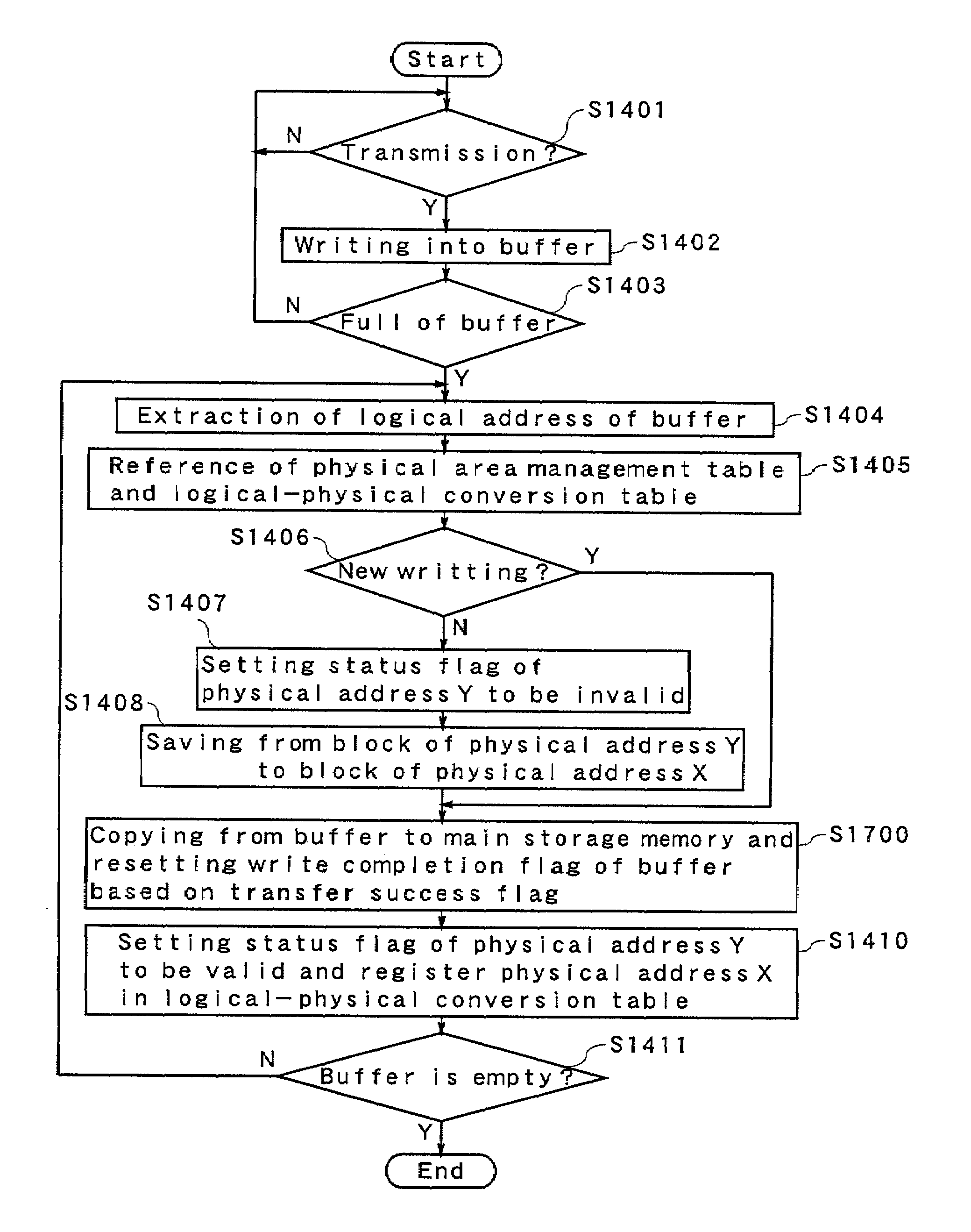

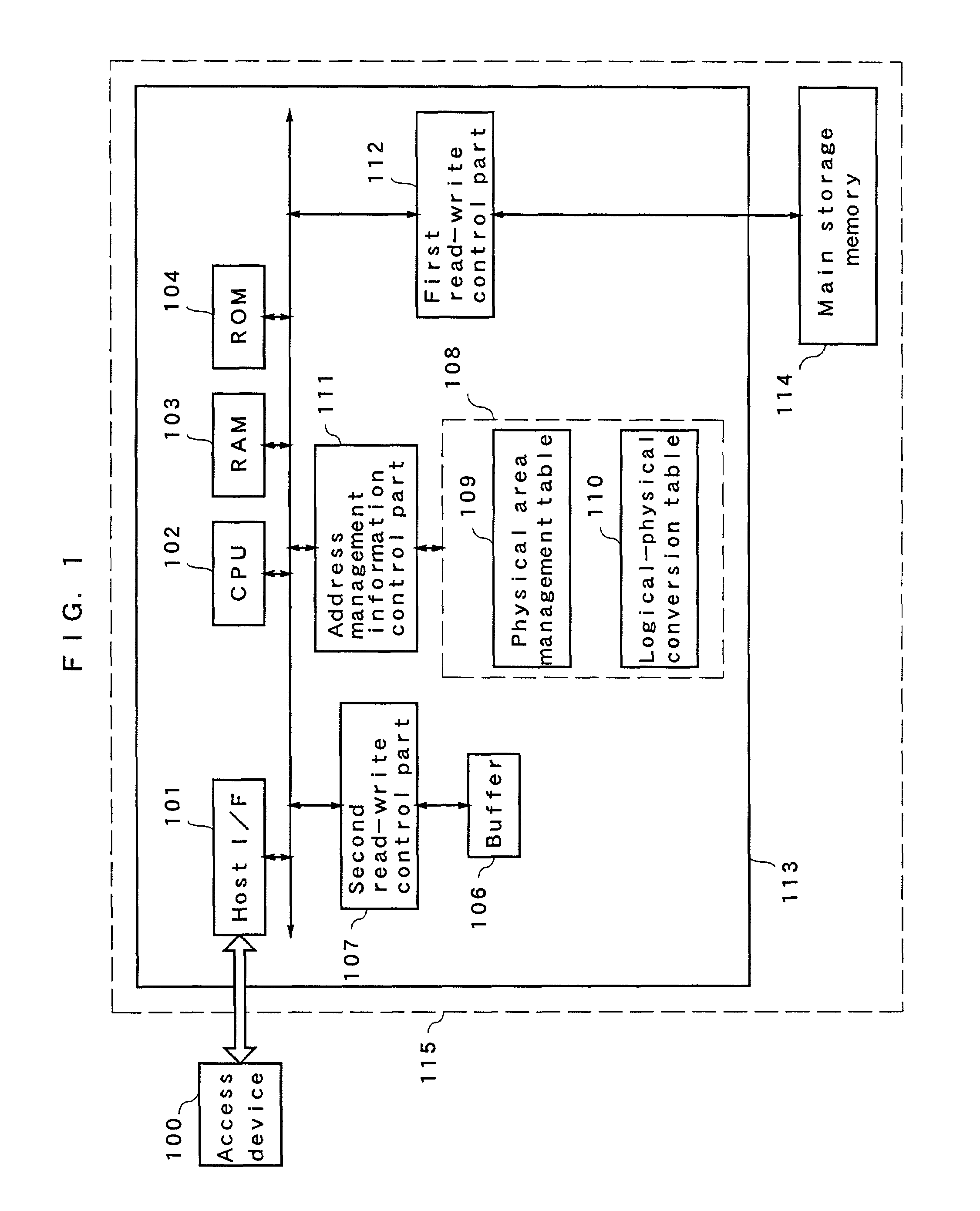

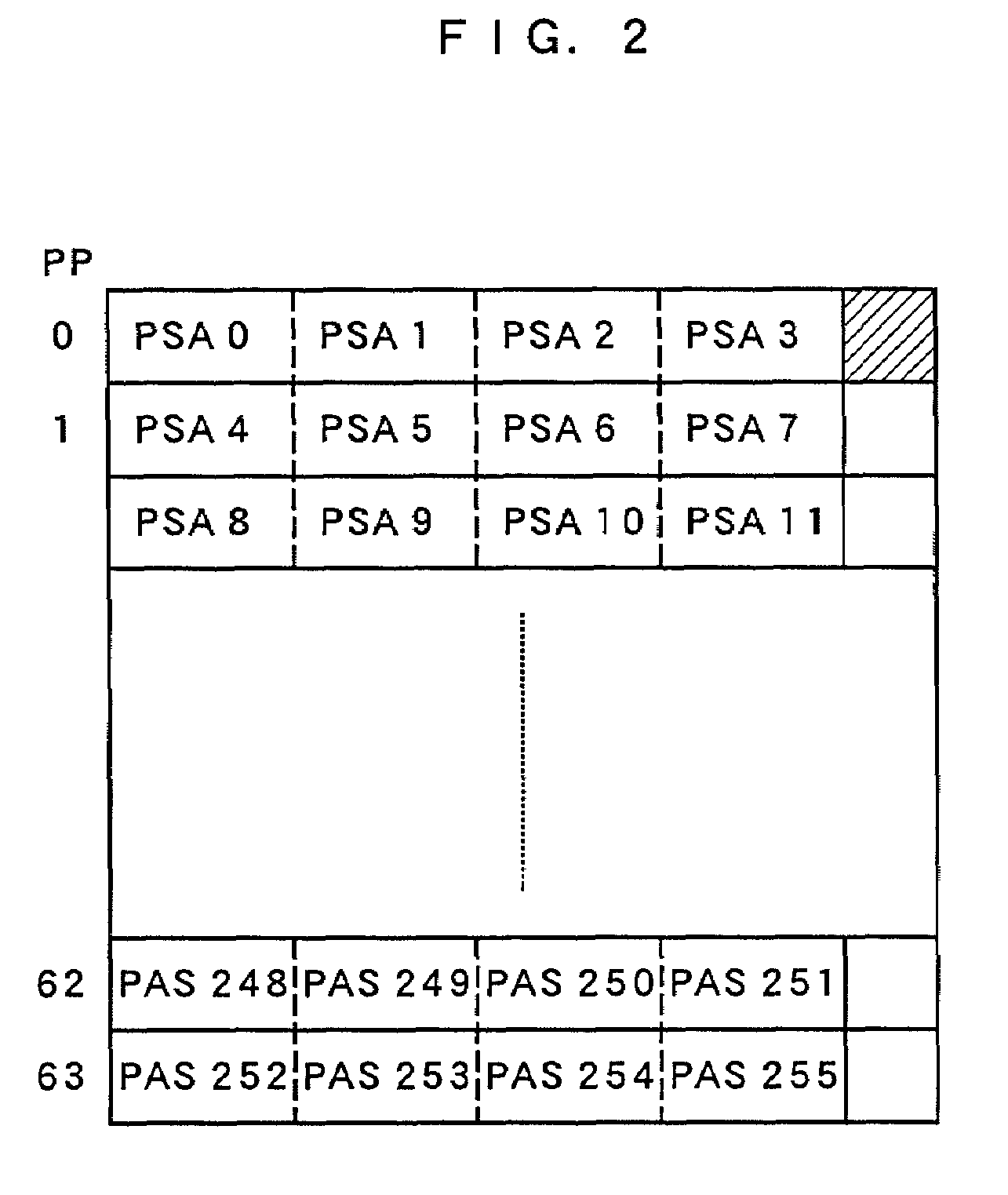

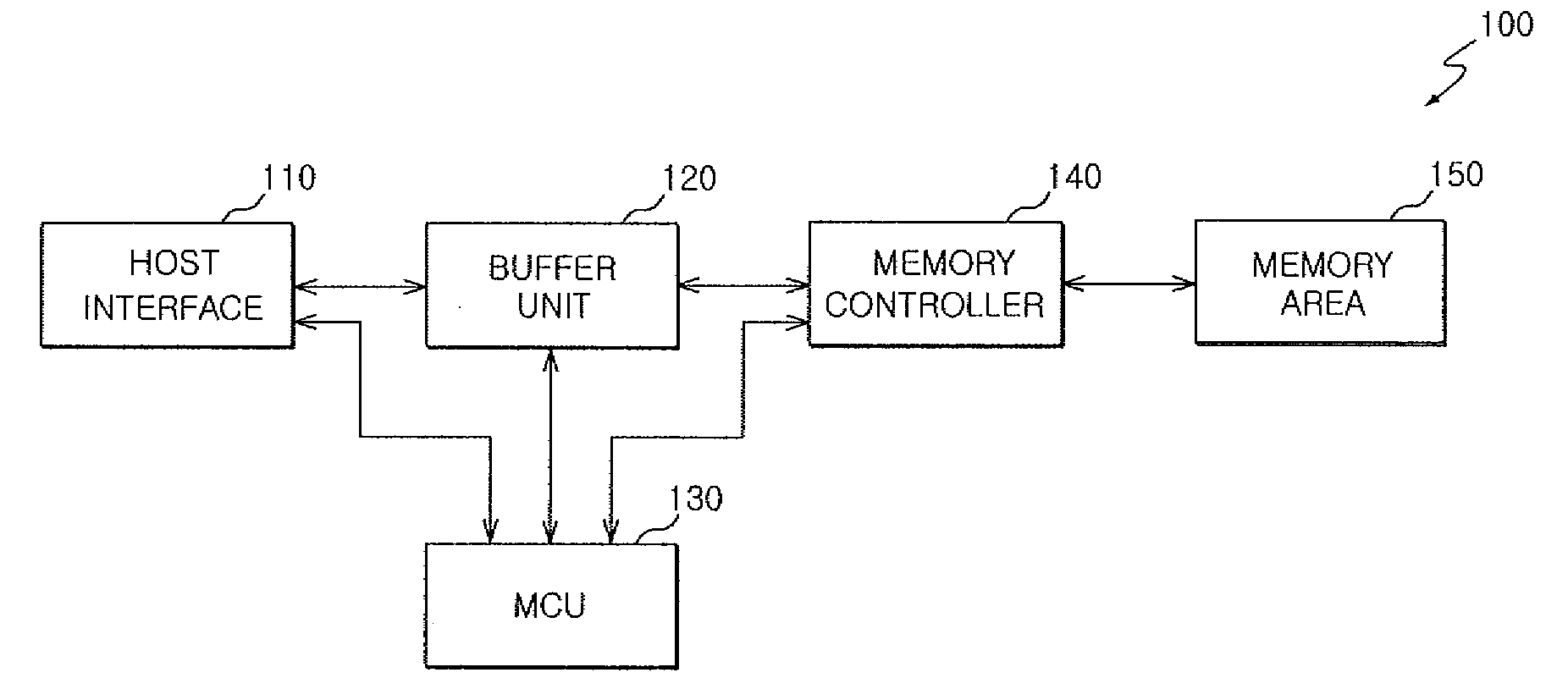

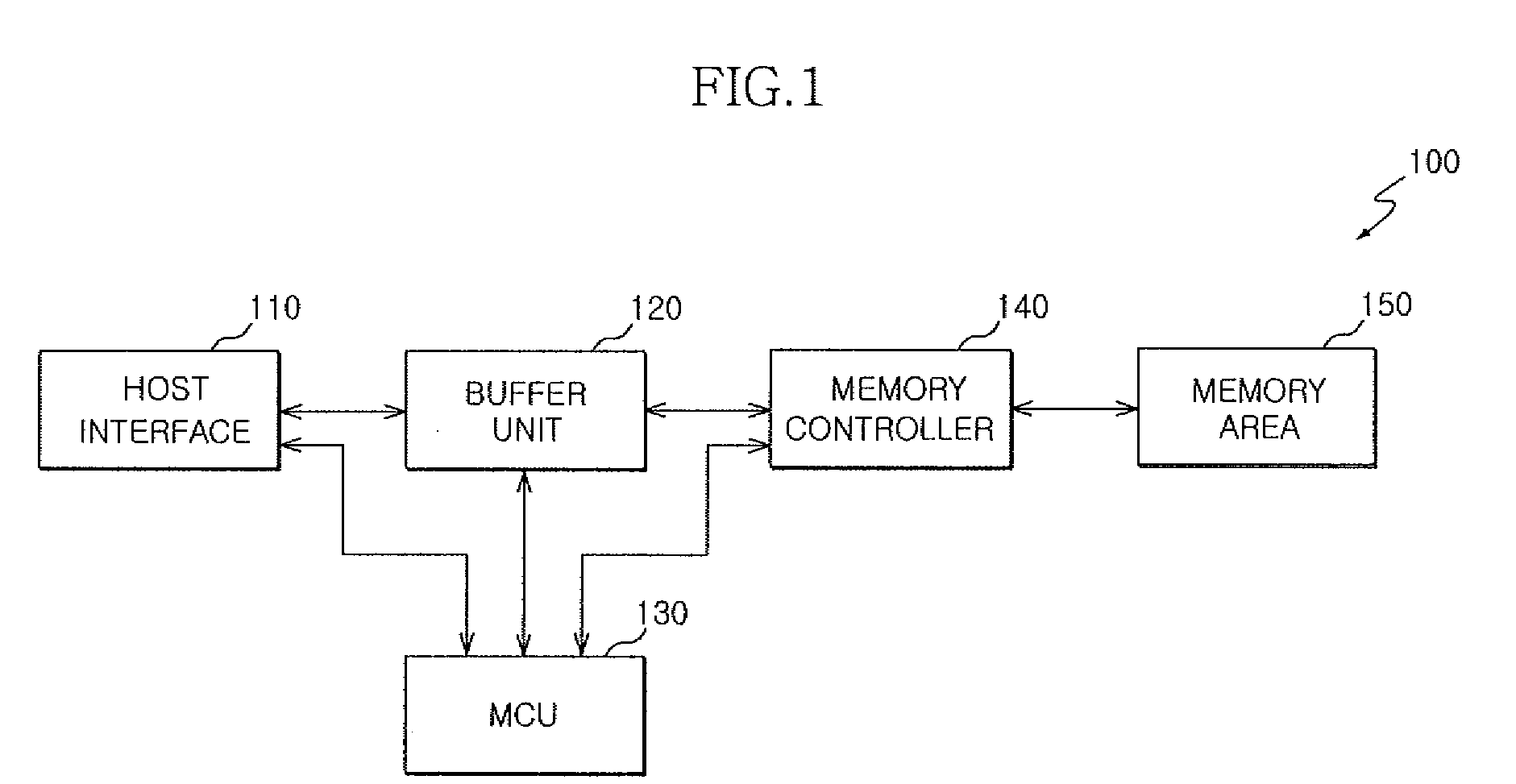

Memory controller, nonvolatile storage device, nonvolatile storage system, and data writing method

InactiveUS7702846B2Increase speedHigh-speed performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationAuxiliary memoryMemory controller

A nonvolatile storage device is provided with a nonvolatile main storage memory whose erase size is larger than a cluster size, and a buffer, i.e. a nonvolatile auxiliary storage memory. At the time of writing data in the memory, the data is temporarily stored in the buffer, then, a plurality of data in the buffer are collectively taken out to be stored in the main storage memory. Data in an original block is saved in a write block in the main storage memory. Thus, the data can be written in the main storage memory at a high speed.

Owner:PANASONIC CORP

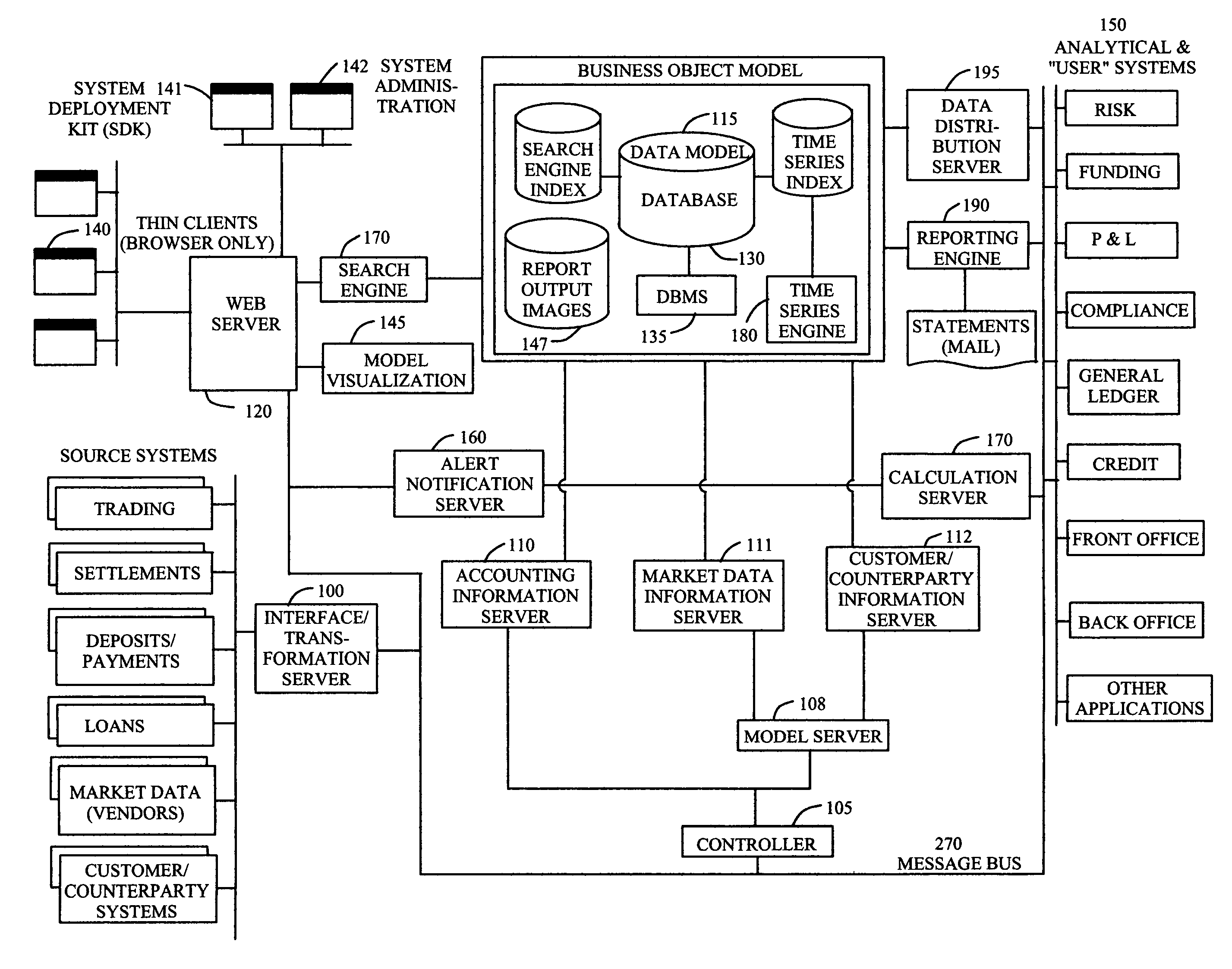

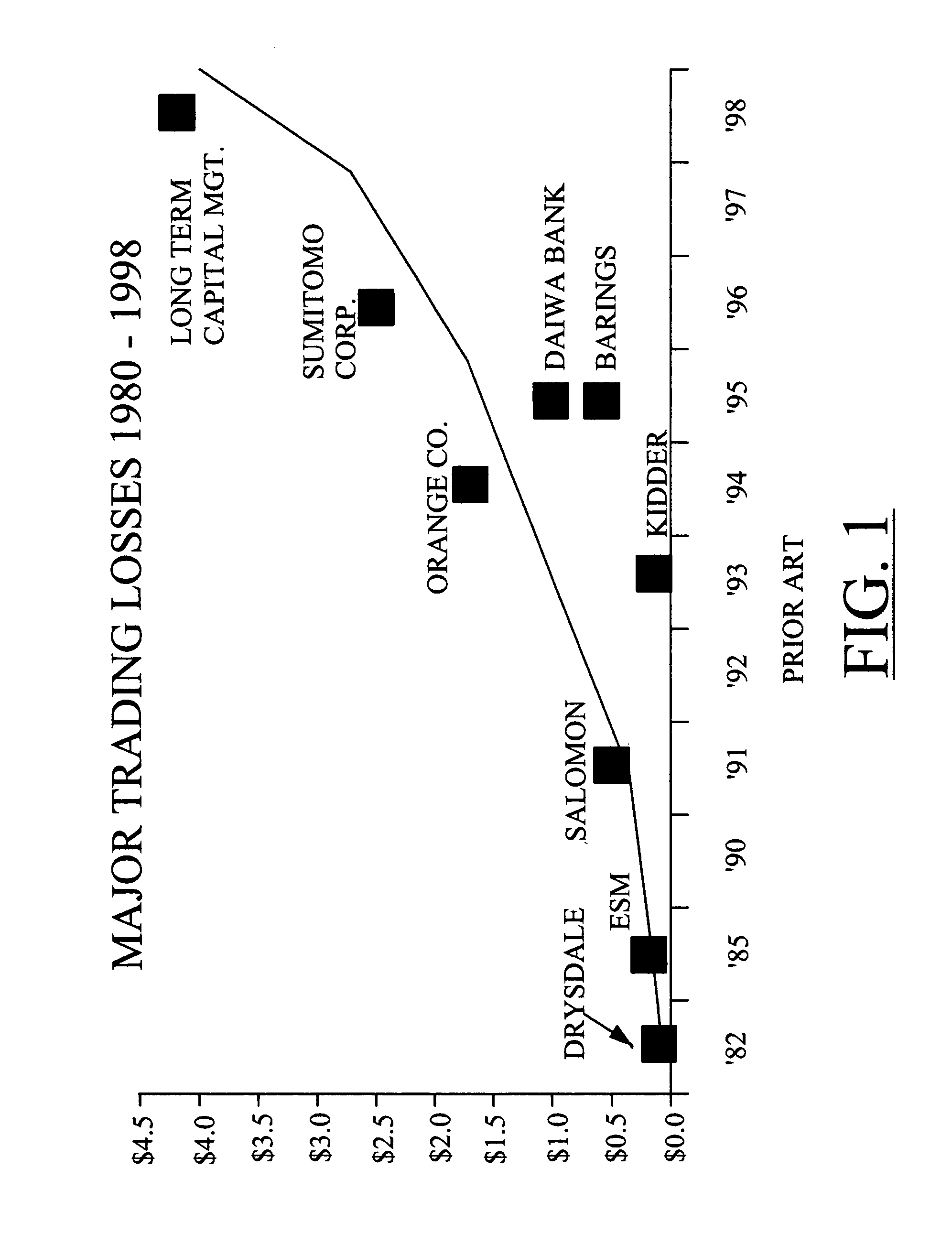

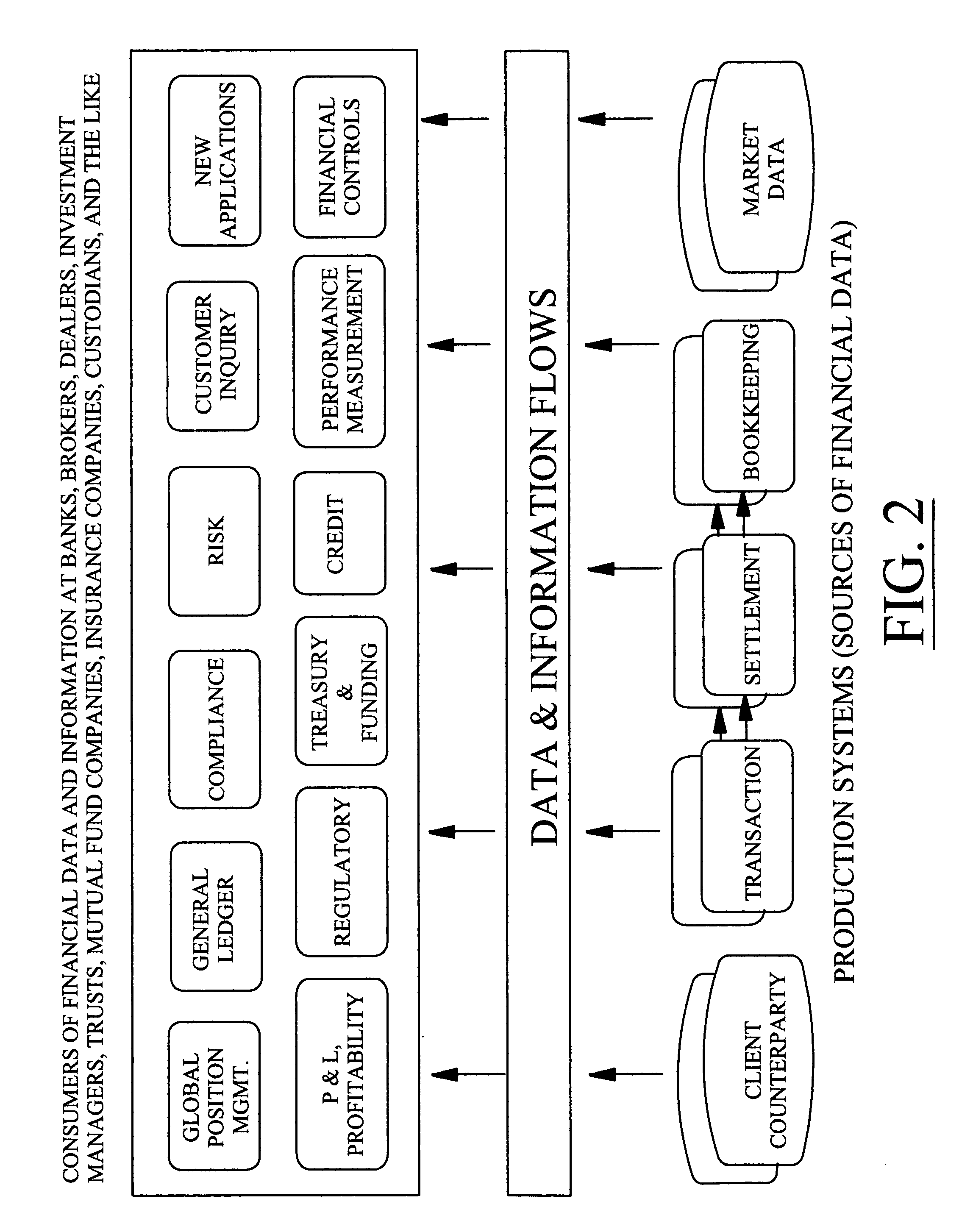

Financial data reporting system with alert notification feature and free-form searching capability

InactiveUS7310615B2Improve scalabilityMinimal experienceComplete banking machinesFinanceReal-time dataFree form

An integrated financial data reporting system provides for real time data entry, assessment, and report generation. The system includes message formatting, database management, and select applications for preparing sophisticated financial presentations in essentially real time. An alert notification server alerts users when a financial threshold specifying a credit limit and / or a trading limit has been crossed. A data distribution server electronically distributes data to users on a recurring and / or periodic basis, and a search engine server provides free-form searches against information stored in a consolidated database. Through the inventive system, financial institutions rationalize risk, performance, and compliance positions in a cost-effective manner.

Owner:GOLDENSOURCE CORP

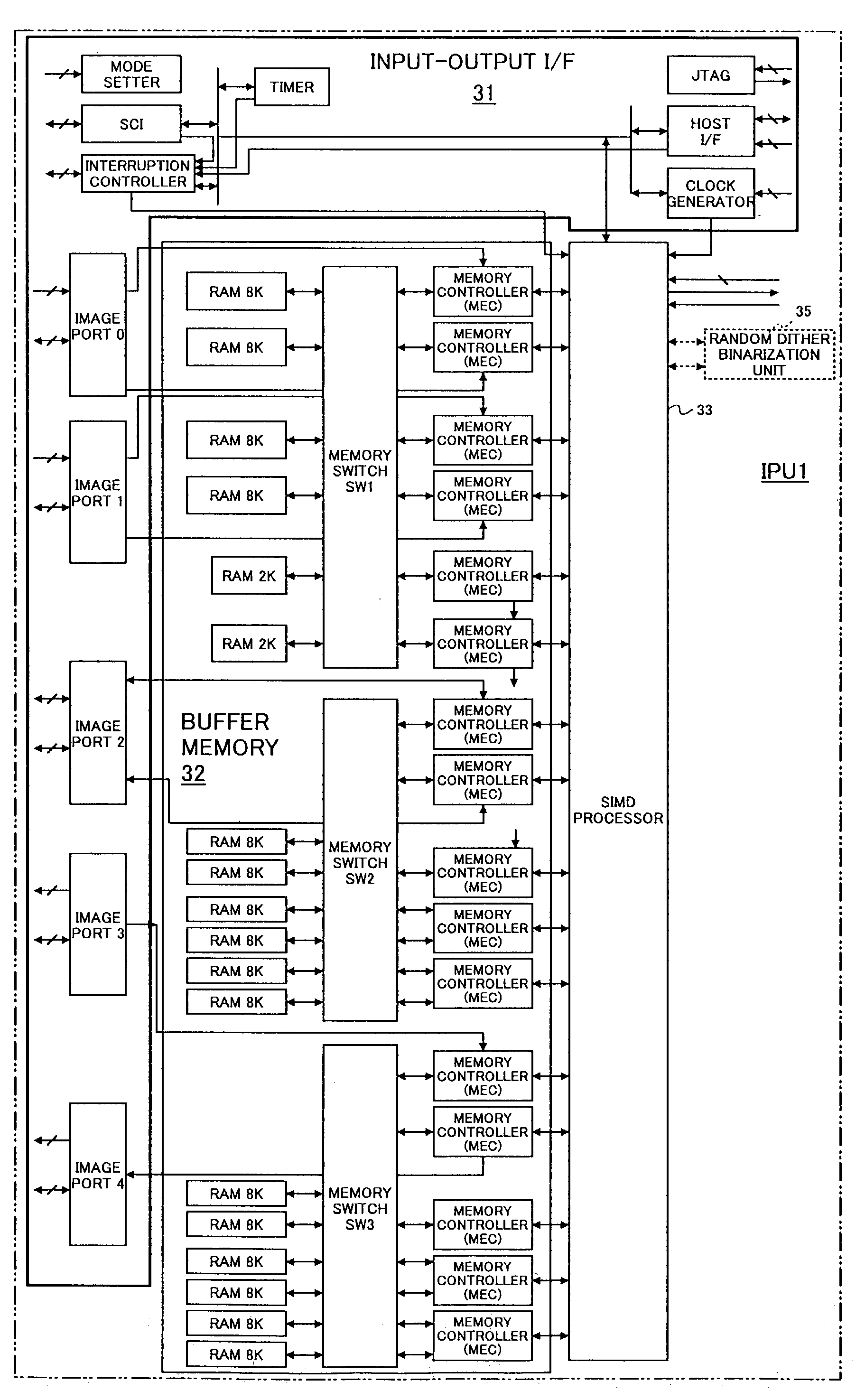

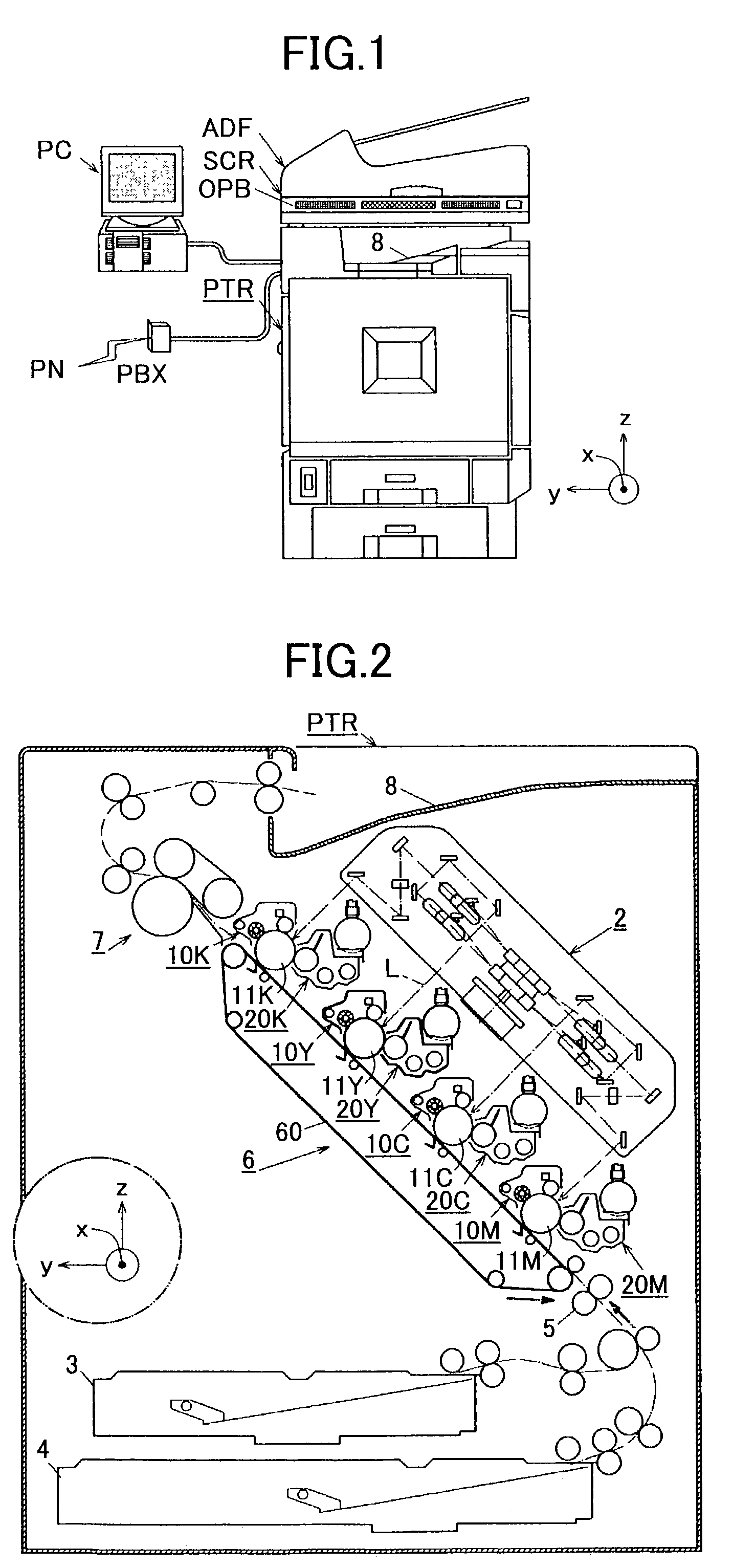

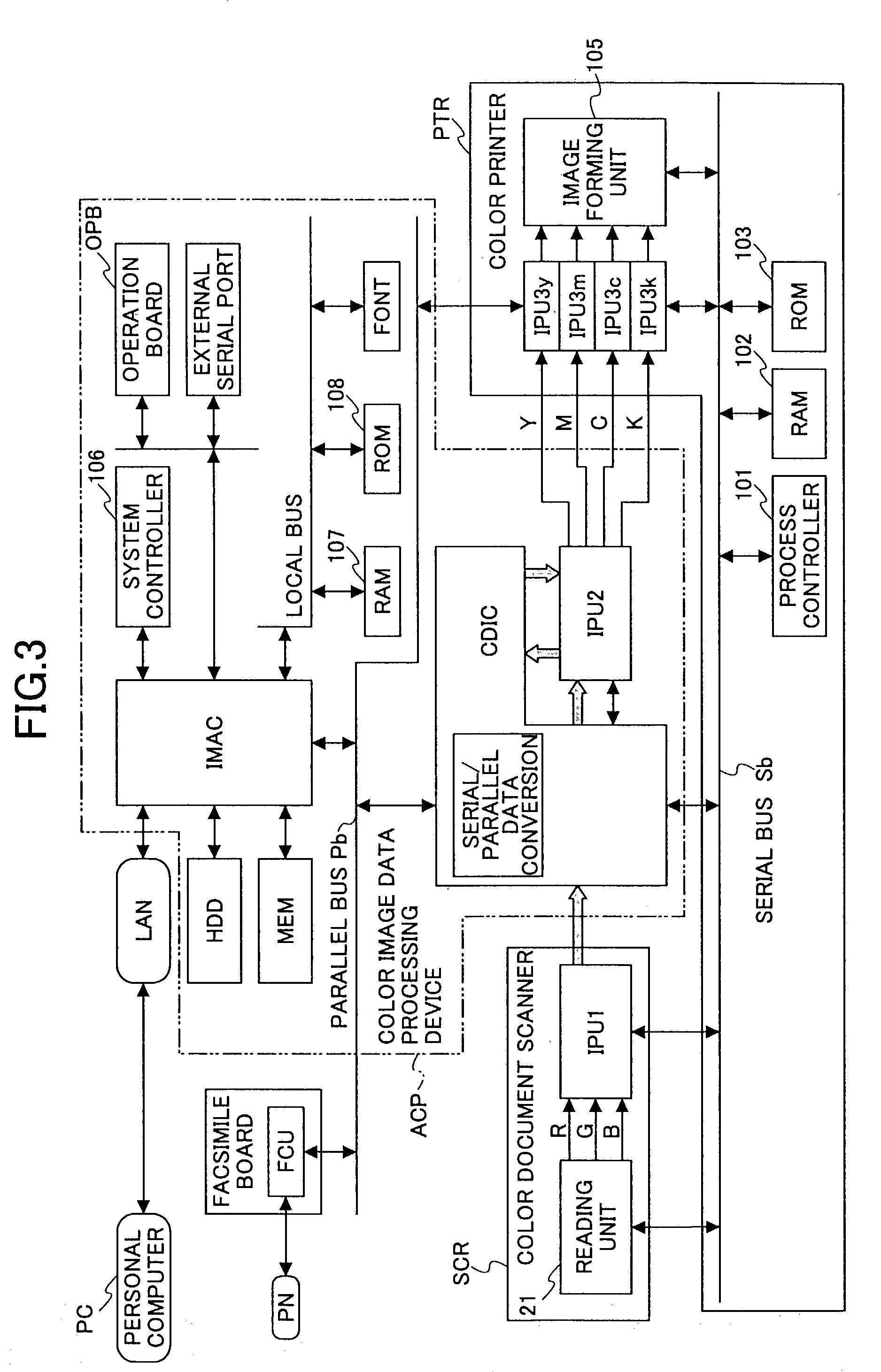

Image data processing device processing a plurality of series of data items simultaneously in parallel

InactiveUS7286717B2Eliminate problemHigh-speed performanceDigitally marking record carriersDigital computer detailsData conversionMemory controller

In a data conversion device, a plurality of series of data to be converted is input from a buffer memory device to a data processor. The data processor processes a plurality of the series of the data to be converted, simultaneously in parallel, and outputs a plurality of the series of the data to be converted, simultaneously in parallel. A memory controller of the buffer memory device relates a plurality of the series of the data to be converted to respective conversion tables formed therein by the data processor so as to read converted data corresponding to the series of the data to be converted from the respective conversion tables simultaneously in parallel.

Owner:RICOH KK

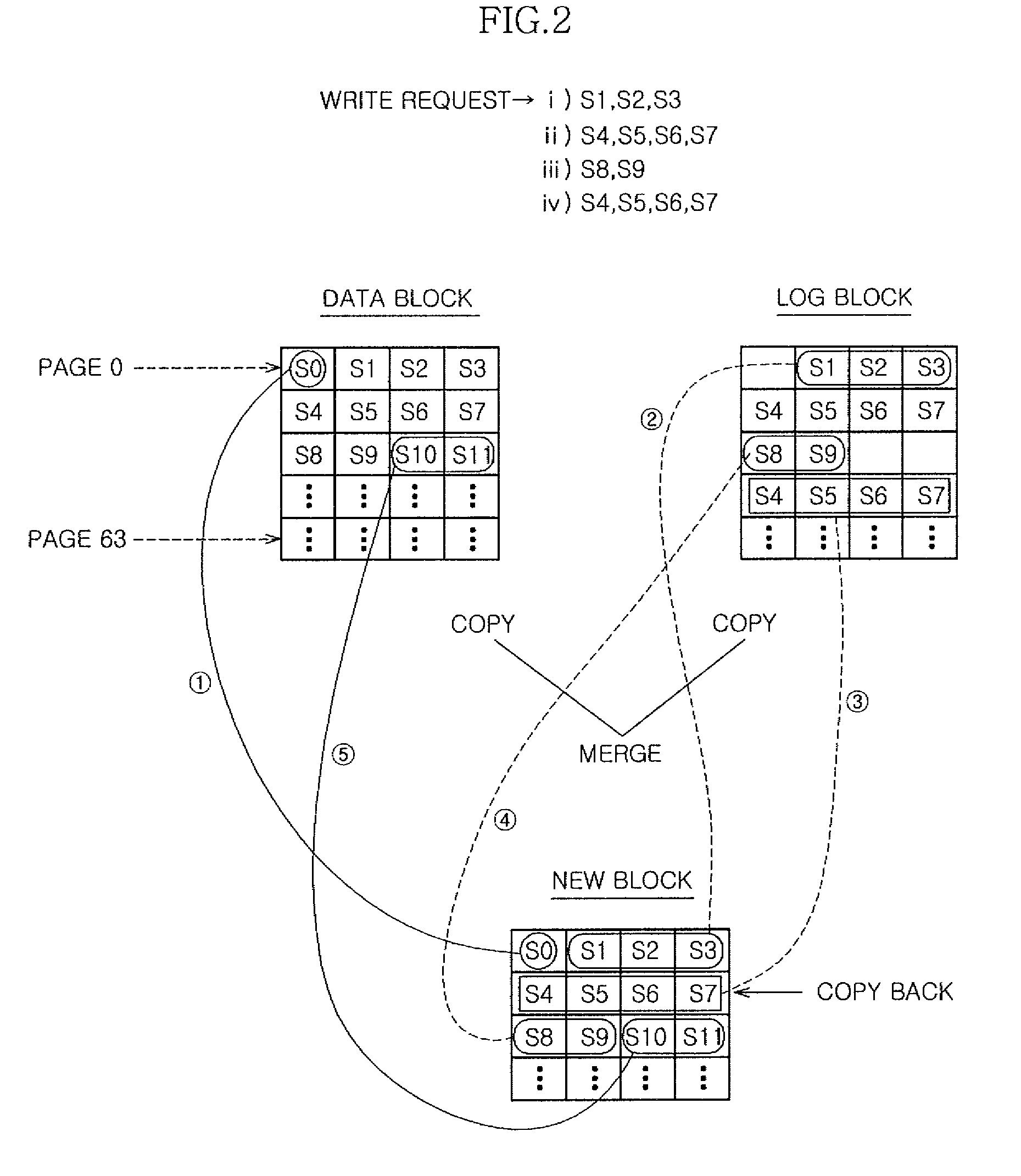

Solid state storage system for data merging and method of controlling the same according to both in-place method and out-of-place method

InactiveUS20100023676A1Improve solid performanceSimply performedMemory architecture accessing/allocationMemory adressing/allocation/relocationSolid-state storageMemory block

A solid state storage system includes a controller configured to divide memory blocks of a flash memory area into first blocks and second blocks corresponding to the first blocks, newly allocates pages of the second blocks when an external write command is requested. The controller is also configured to allocate selected sectors in the allocated pages according to sector addresses and execute a write command.

Owner:PAXDISK +1

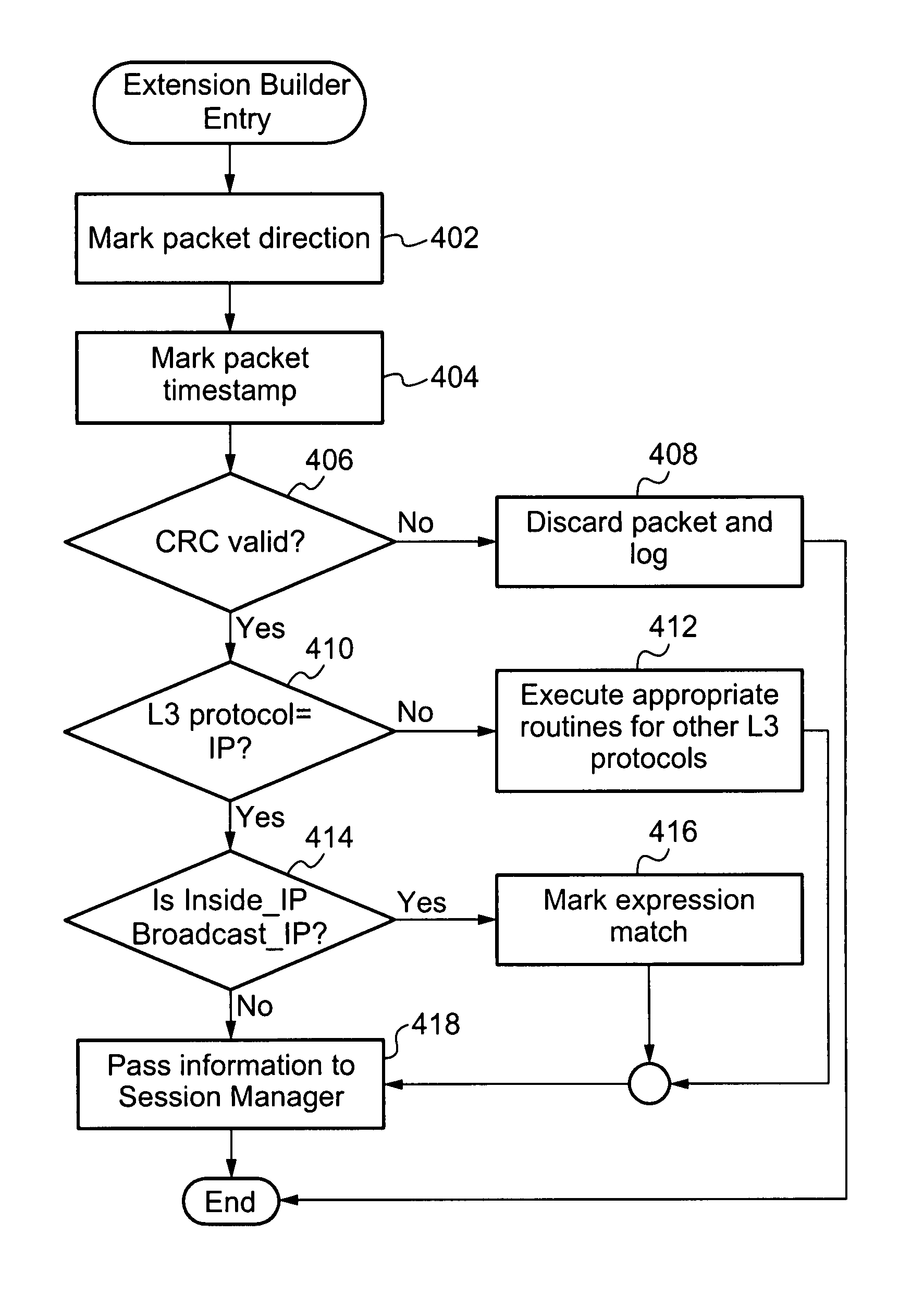

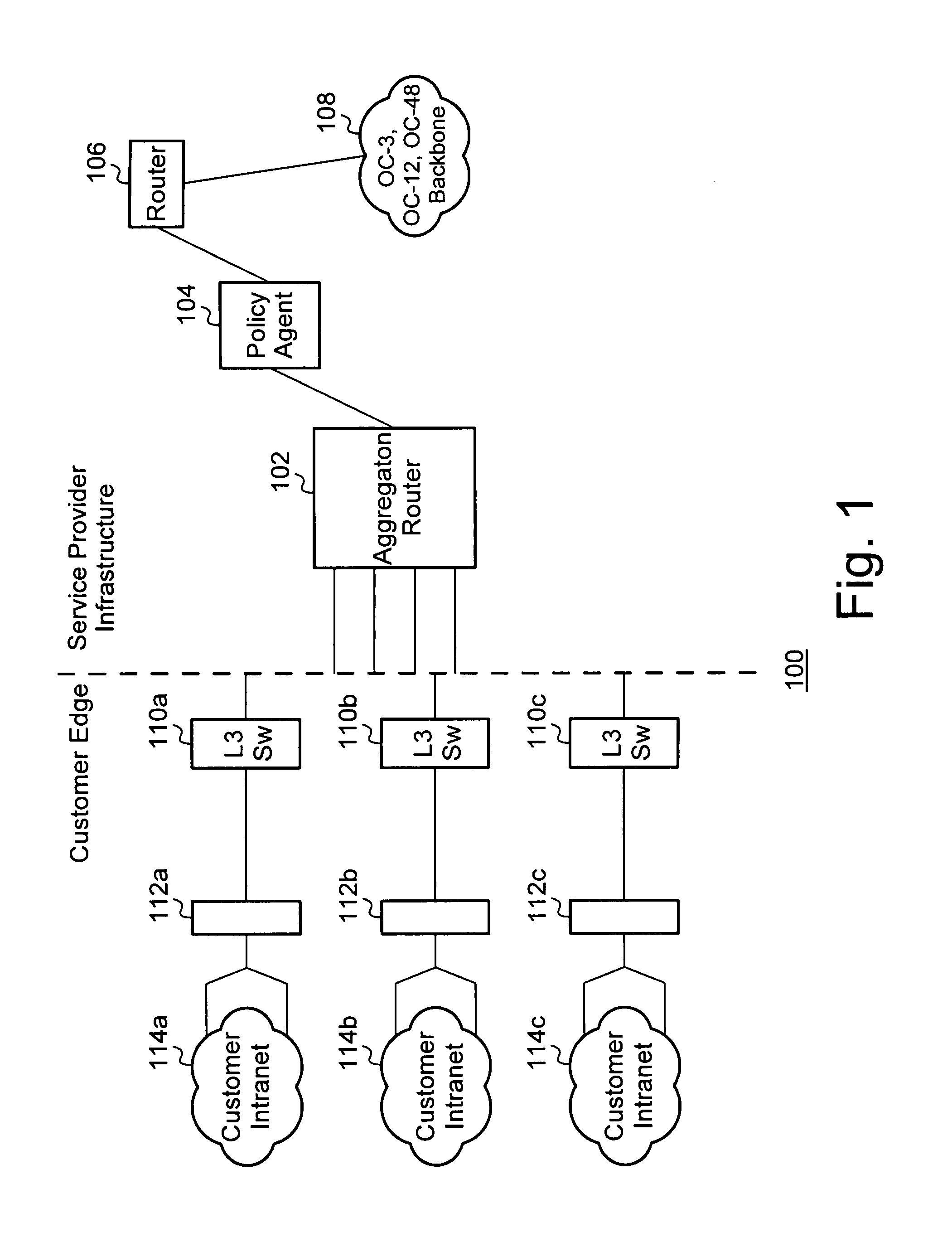

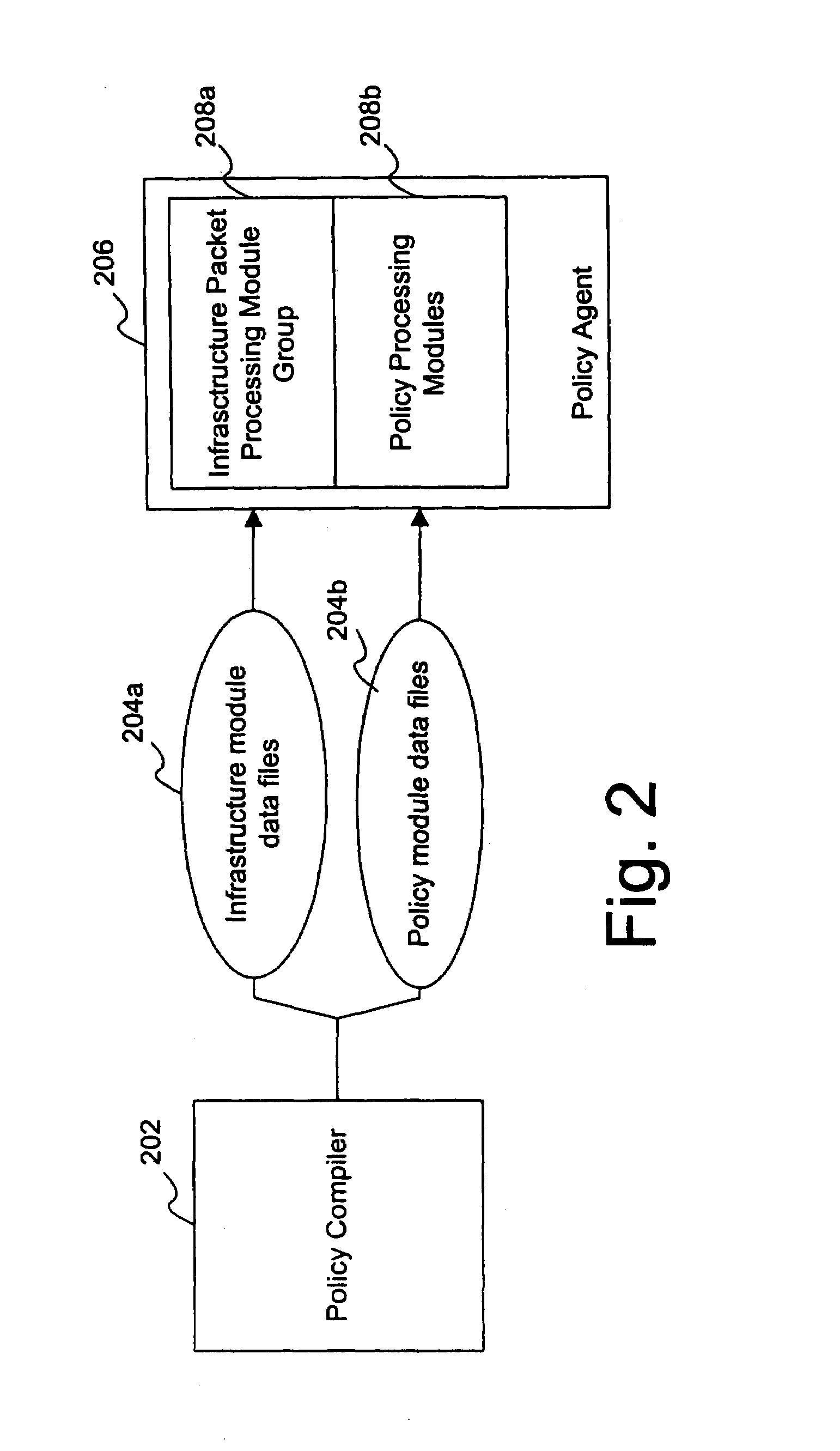

Architecture for an integrated policy enforcement system

InactiveUS7257833B1Increase enforcementHigh-speed performanceSpecial data processing applicationsSecuring communicationTree traversalPolicy enforcement

Enforcing a plurality of different policies on a stream of packets is disclosed. In lieu of running separate algorithms for each policy, the system exploits the commonalities of all of the policies. The conditions corresponding to the compiled rules are arranged in a condition tree and processed in a pipelined architecture that allows the results of the various stages to be carried forward into subsequent stages of processing. The rules for which all conditions have been satisfied can be identified by one stage of processing in one pass of condition tree traversal and are passed to subsequent stages. A rule table corresponding to an individual policy type can then be readily examined to determine partial or complete satisfaction of the rule of that policy type, without requiring a re-examination of the conditions underlying the rule. Additionally, corresponding actions can be taken where rule satisfaction is determined. This approach allows extremely high-speed policy enforcement performance.

Owner:TECH MAHINDRA INDIA

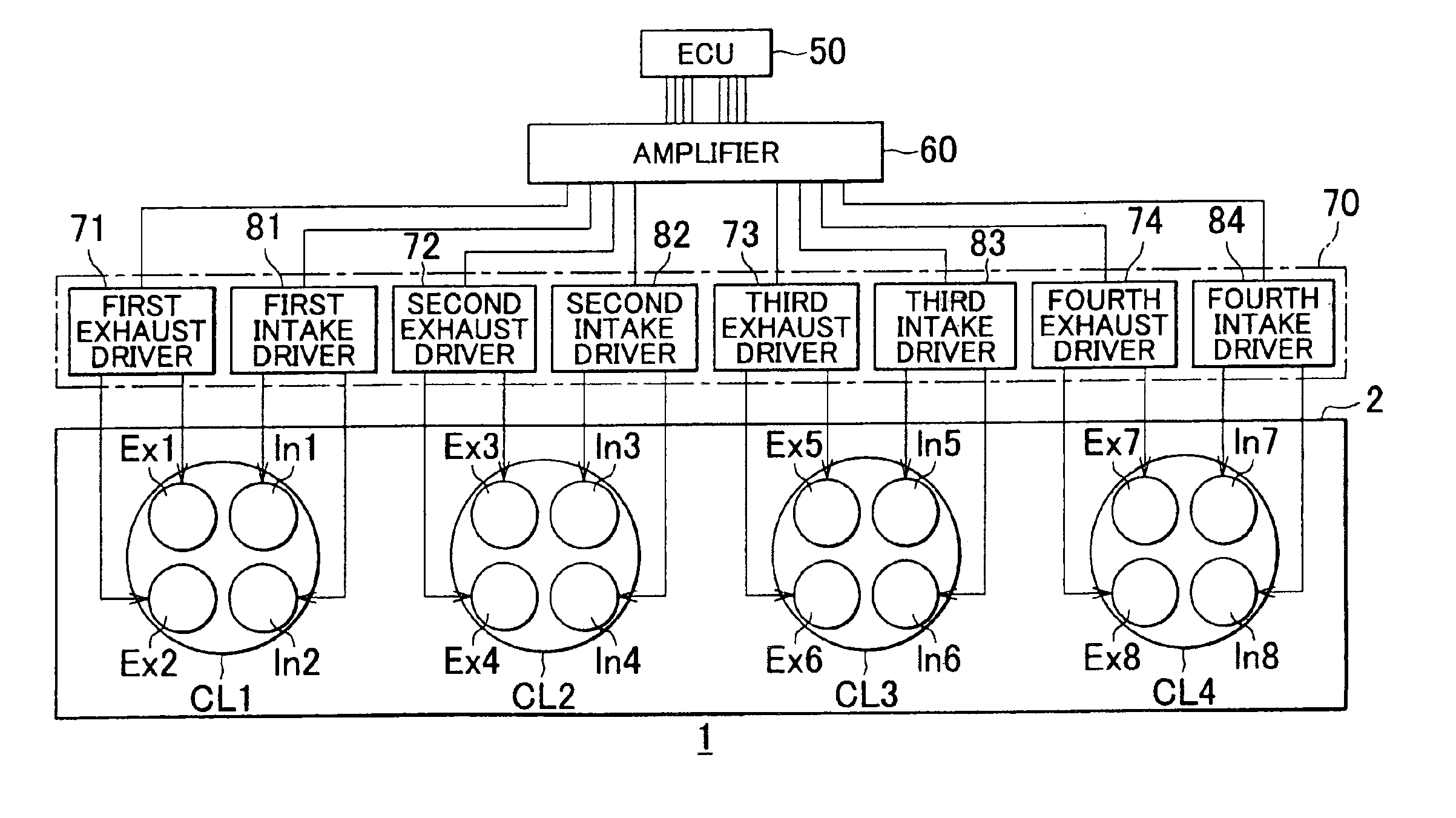

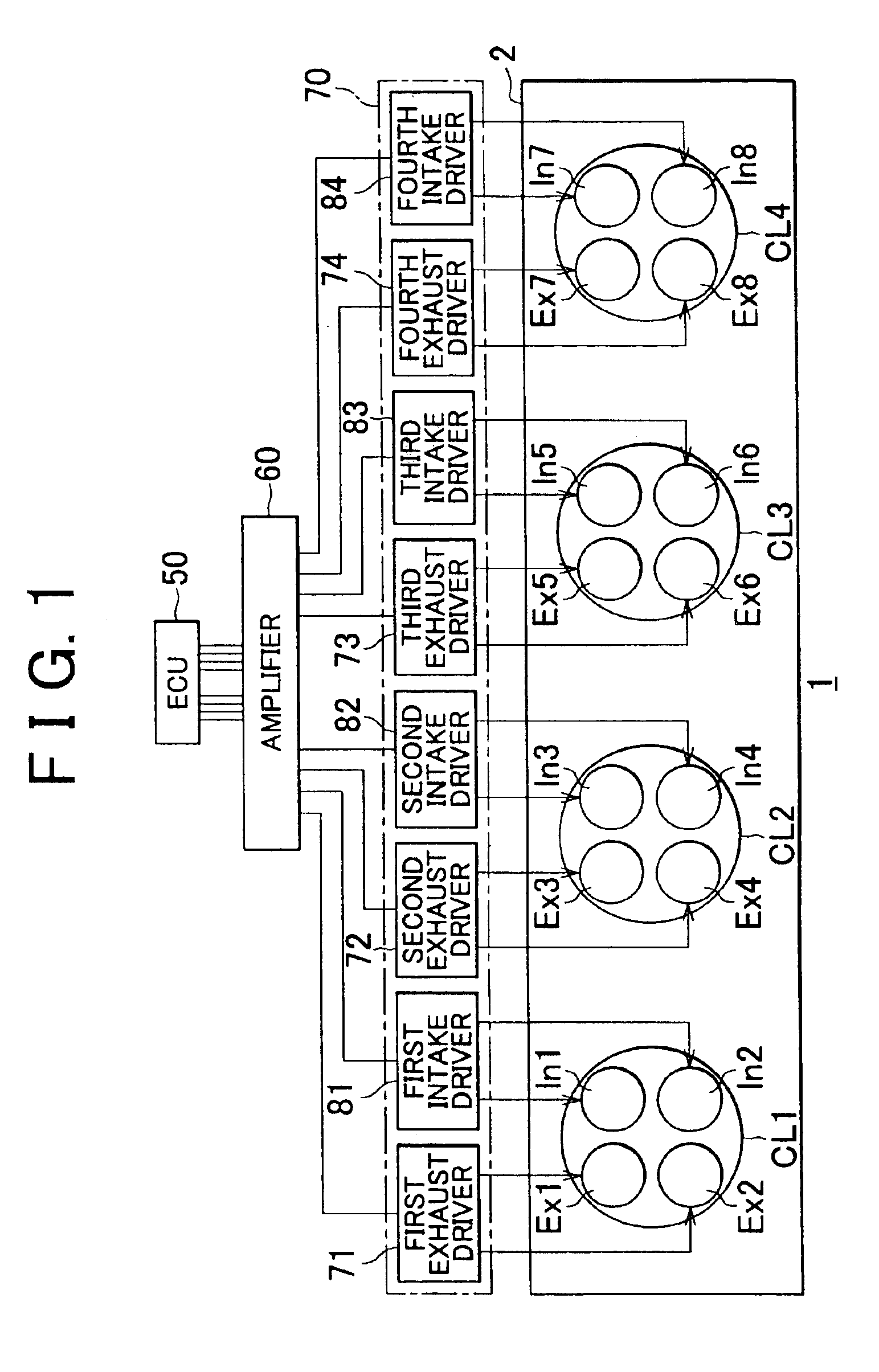

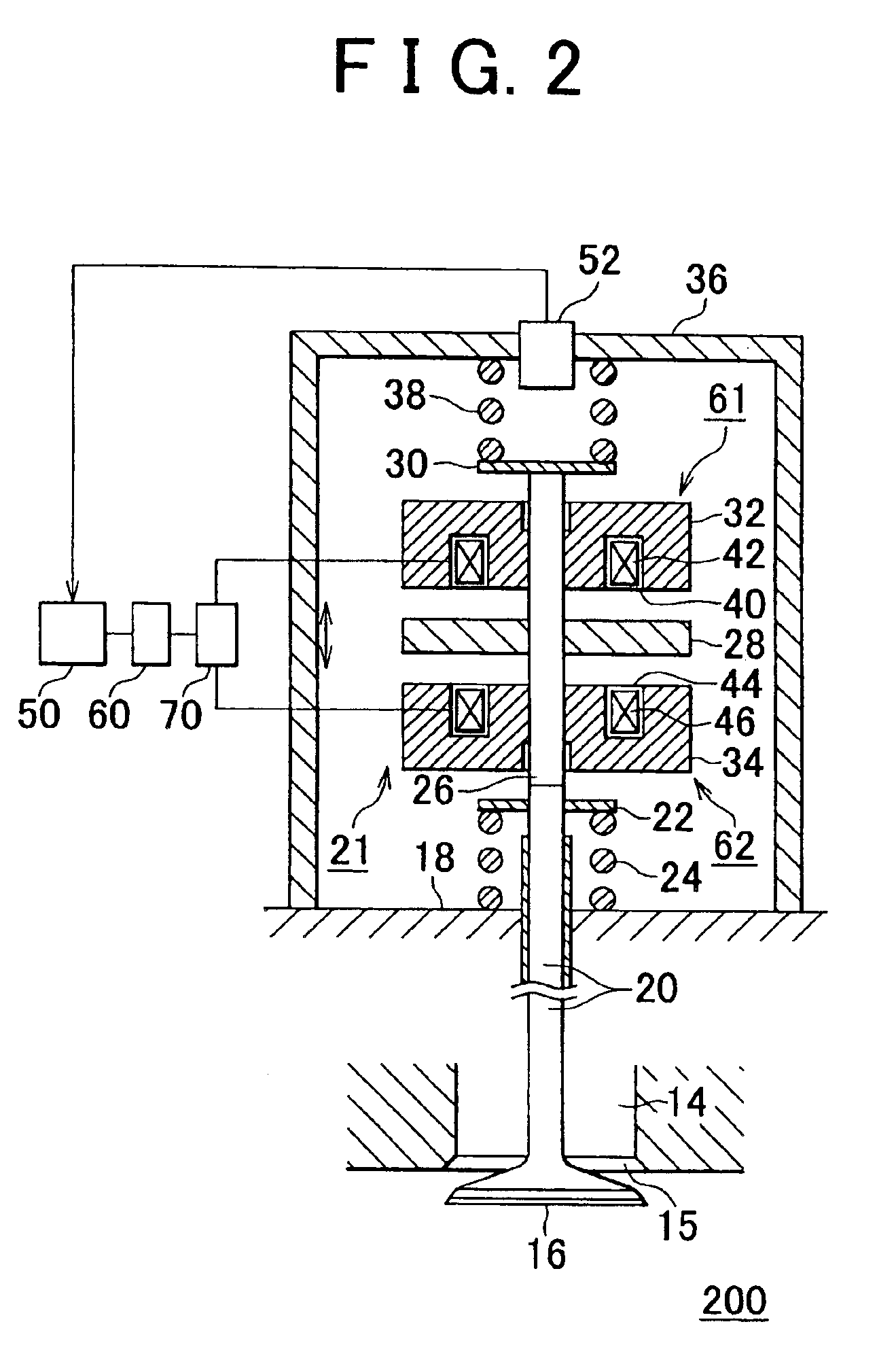

Electromagnetically driven valve control apparatus and electromagnetically driven valve control method for internal combustion engine

InactiveUS6866012B2Increase the number ofEffective controlAnalogue computers for vehiclesElectrical controlHigh speed controlLow speed

A main CPU determines whether or not there is a request for one valve driving based on an engine operating state such as an engine speed and a load factor, with reference to a control map. When it is determined that there is a request for one valve driving, it is determined whether or not there is an overlapping period between opening periods. When it is determined that there is no overlapping period, a high speed control is performed for controlling electromagnetically driven valves. When it is determined that there is no request for one valve driving, or when it is determined that there is the overlapping period, a low speed control is performed for controlling electromagnetically driven valves.

Owner:TOYOTA JIDOSHA KK

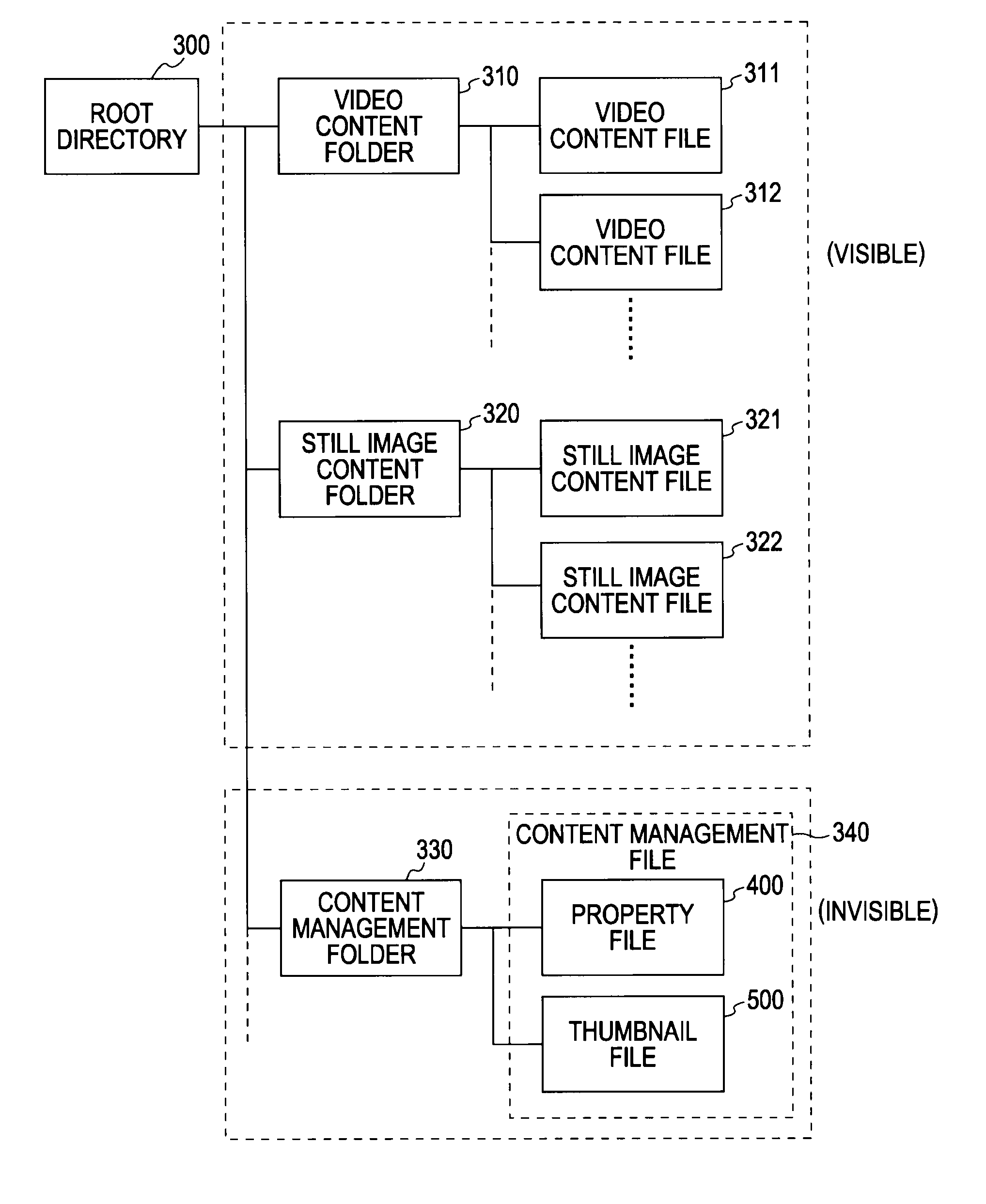

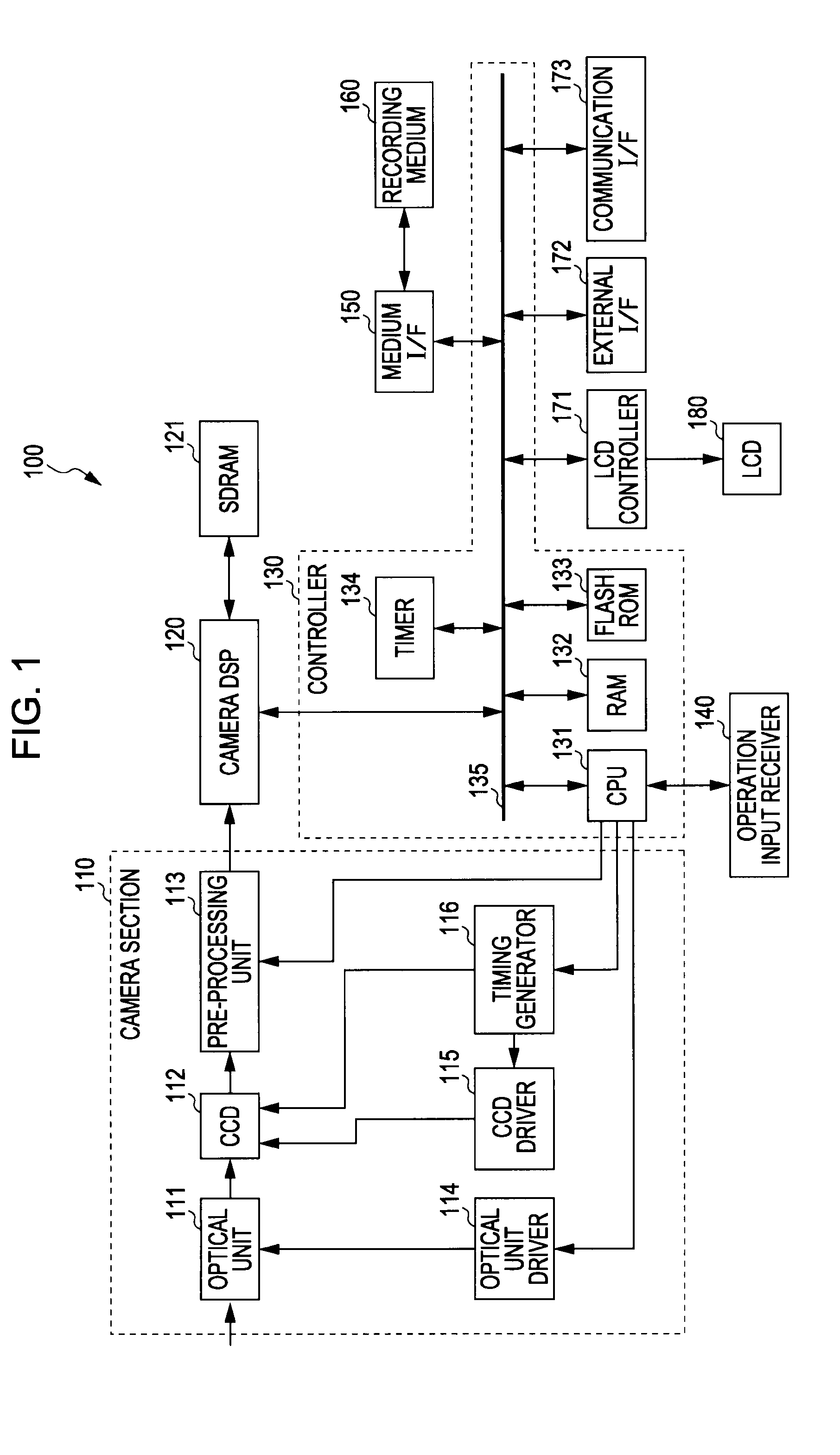

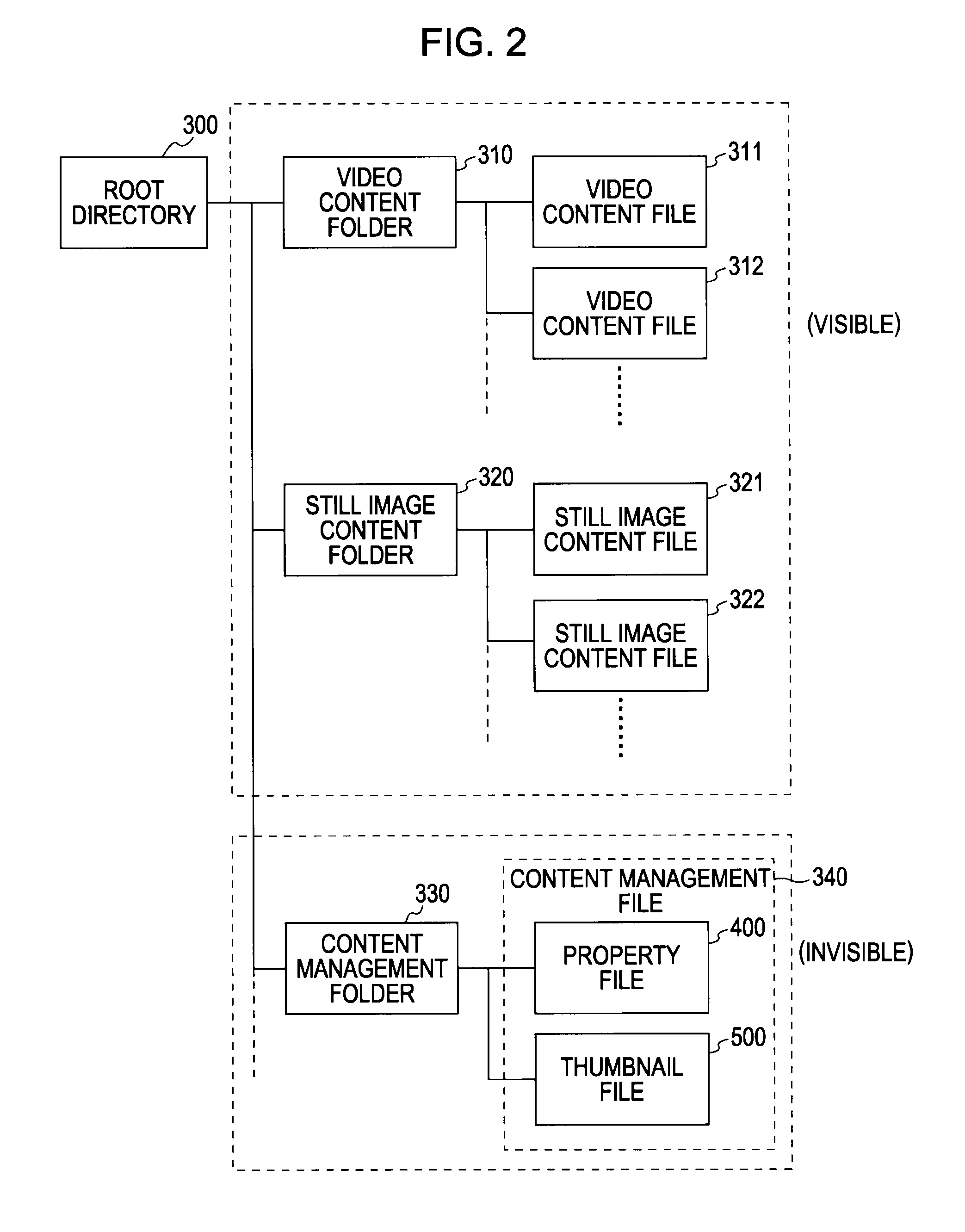

Image processing device, imaging apparatus, image-processing method, and program

ActiveUS20100026842A1Quickly pickingQuick to useTelevision system detailsStill image data indexingFace detectionImaging processing

An image processing device includes a storage unit,a face detection unit, a face discrimination unit, and a control unit. The storage unit is provided for storing a content management file that stores a file entry for managing contents and a particular face entry for managing a particular face. Each of the file entry and the particular face entry is a hierarchical entry with a hierarchical structure. The face detection unit is provided for detecting a face contained in the contents. The face discrimination unit is provided for determining whether the detected face is the particular face by comparing the particular face with the detected face. The control unit is provided for performing control of correlating the particular face entry with the file entry when the detected face is identified as the particular face.

Owner:SONY CORP

Semiconductor device

InactiveUS7151319B2Reduce noiseHigh-speed performanceSemiconductor/solid-state device detailsSolid-state devicesSurface layerSignal region

Owner:HITACHI LTD

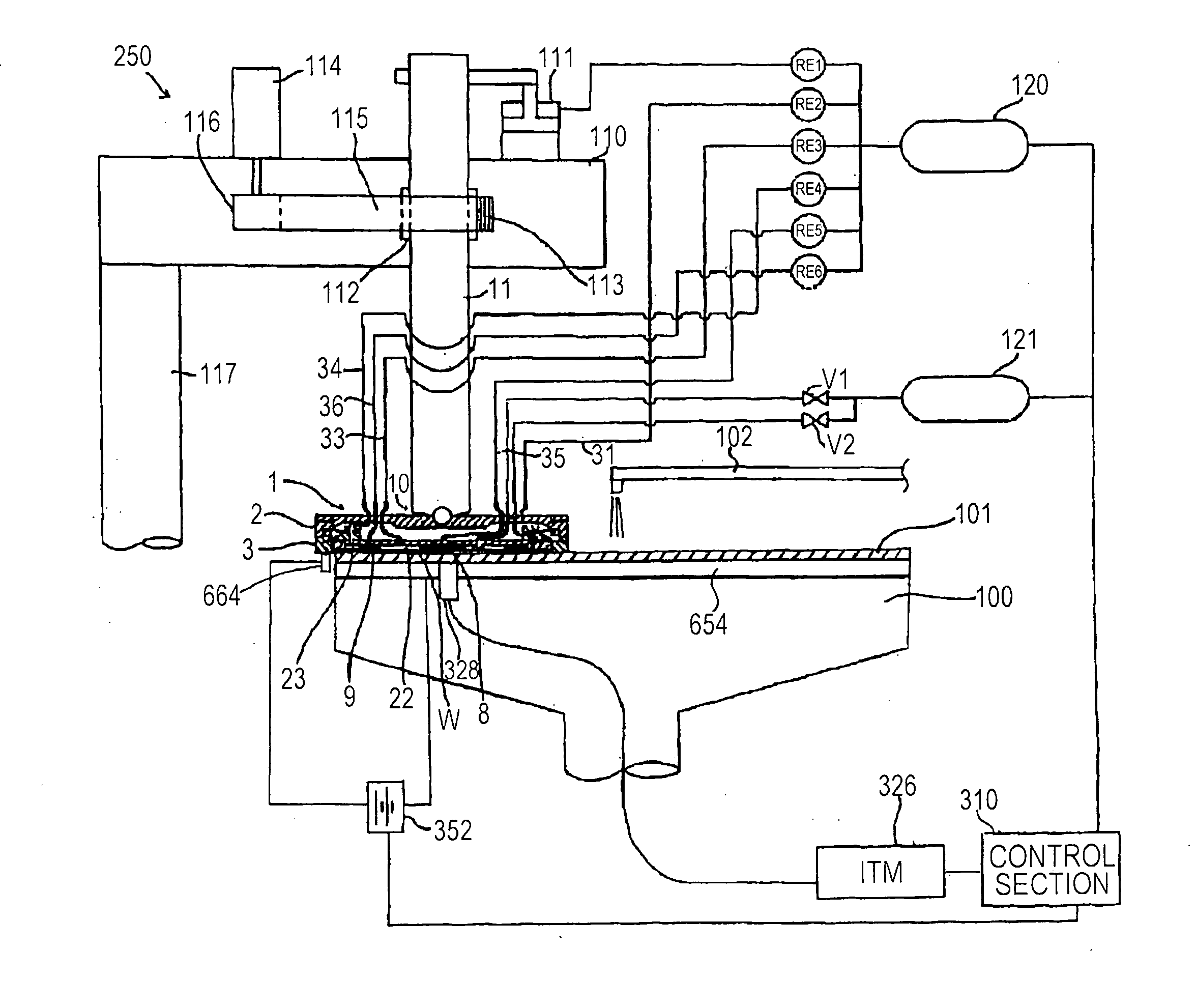

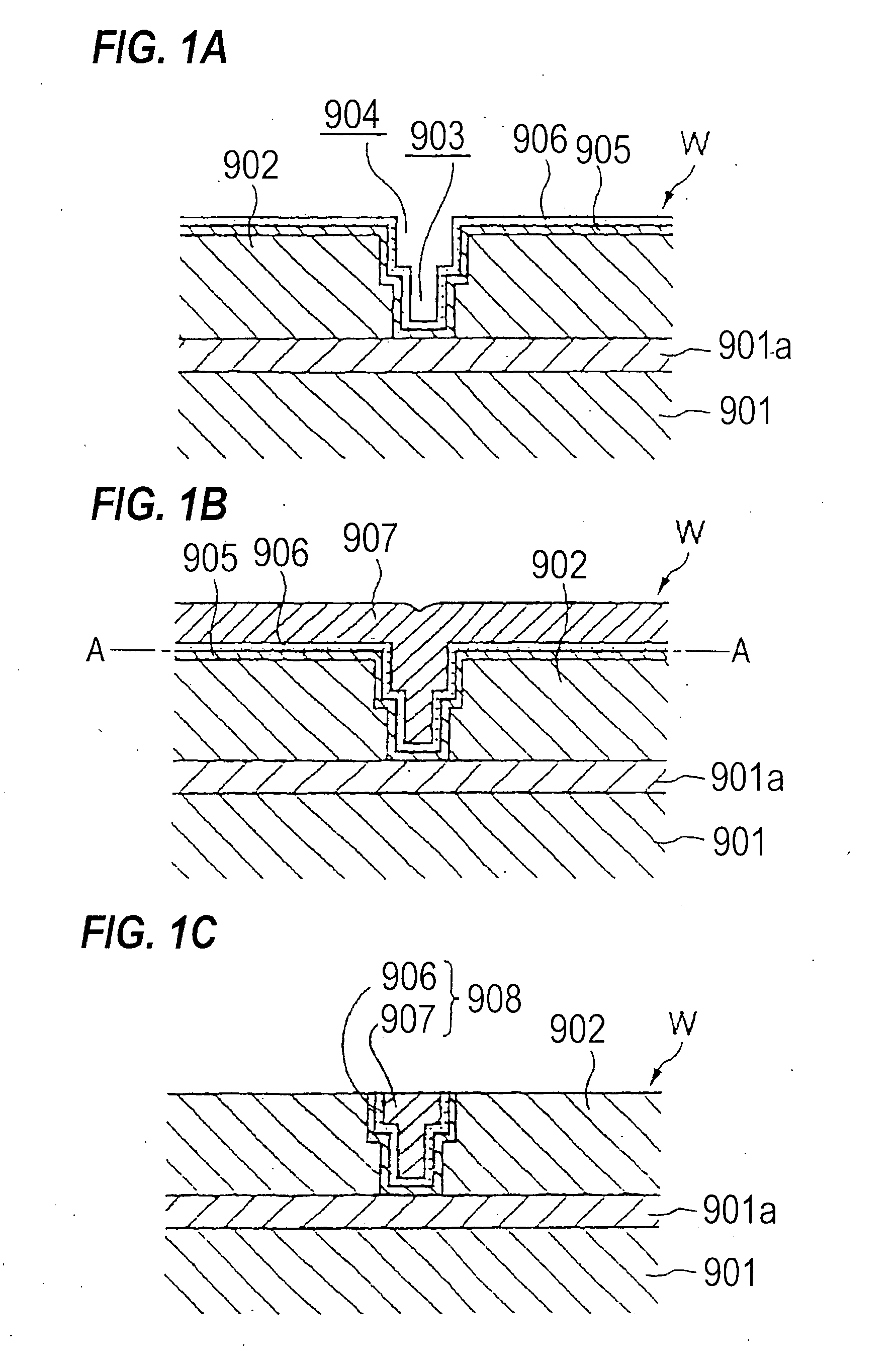

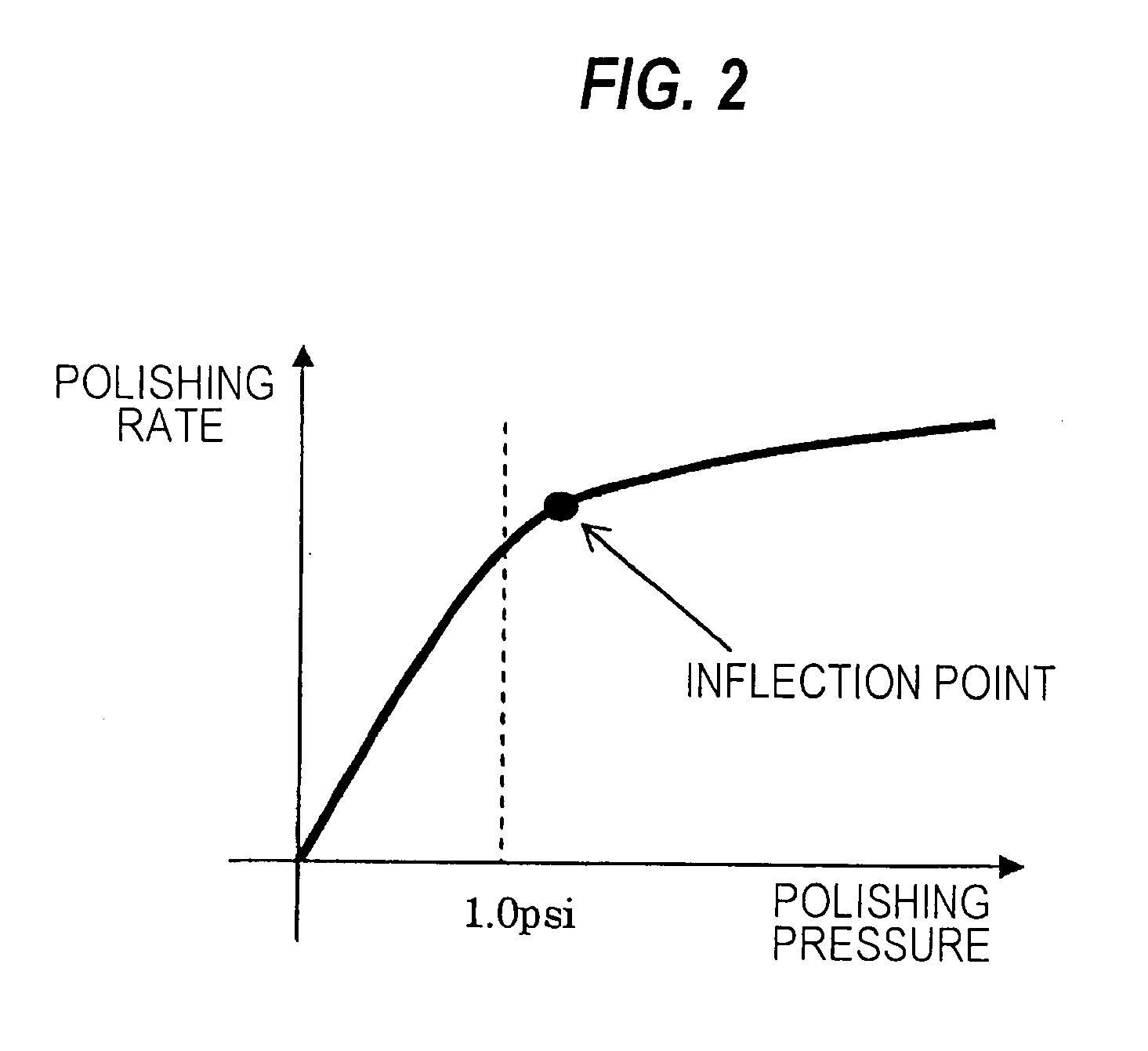

Electrochemical mechanical polishing apparatus conditioning method, and conditioning solution

InactiveUS20080188162A1Low costEasy to implementSemiconductor/solid-state device manufacturingLapping machinesElectrical resistance and conductancePower flow

An electrochemical mechanical polishing apparatus is for use in polishing of a conductive material (e.g., metal) on a surface of a substrate by combination of electrochemical action and mechanical action. This apparatus includes a polishing table having divided electrodes and adapted to hold a polishing pad having a polishing surface, a polishing head adapted to hold a workpiece having a conductive film and to press the workpiece against the polishing surface, a second electrode for supplying an electric current to the conductive film, an electrolytic-solution supply section for supplying an electrolytic solution to the polishing surface, a detecting section adapted to detect a signal corresponding to a thickness of the conductive film, a variable resistance unit having the same number of variable resistors as the number of divided electrodes, a moving mechanism for providing relative movement between the workpiece and the polishing surface, and a control section adapted to control each of the variable resistors based on the signal from the detecting section.

Owner:EBARA CORP

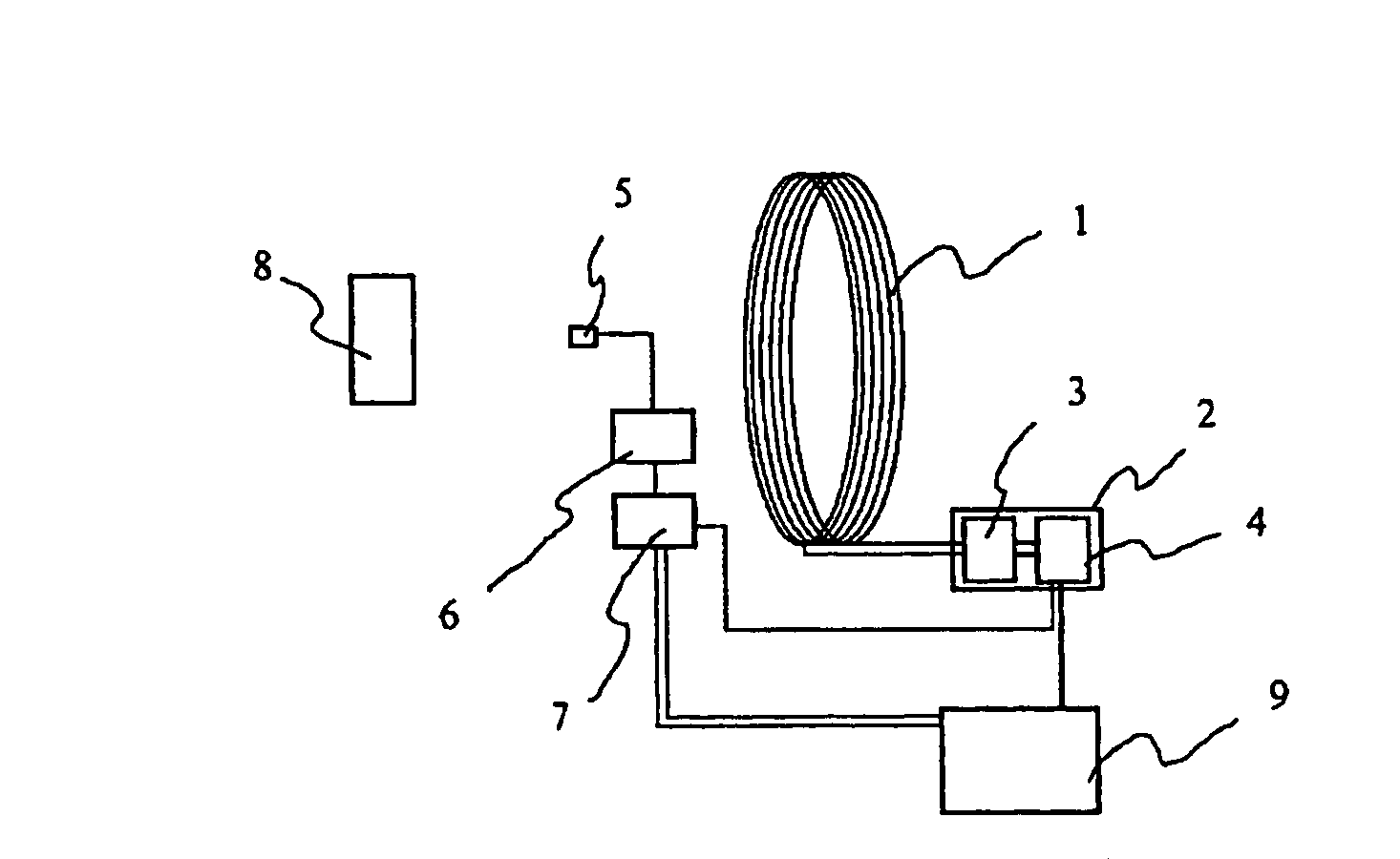

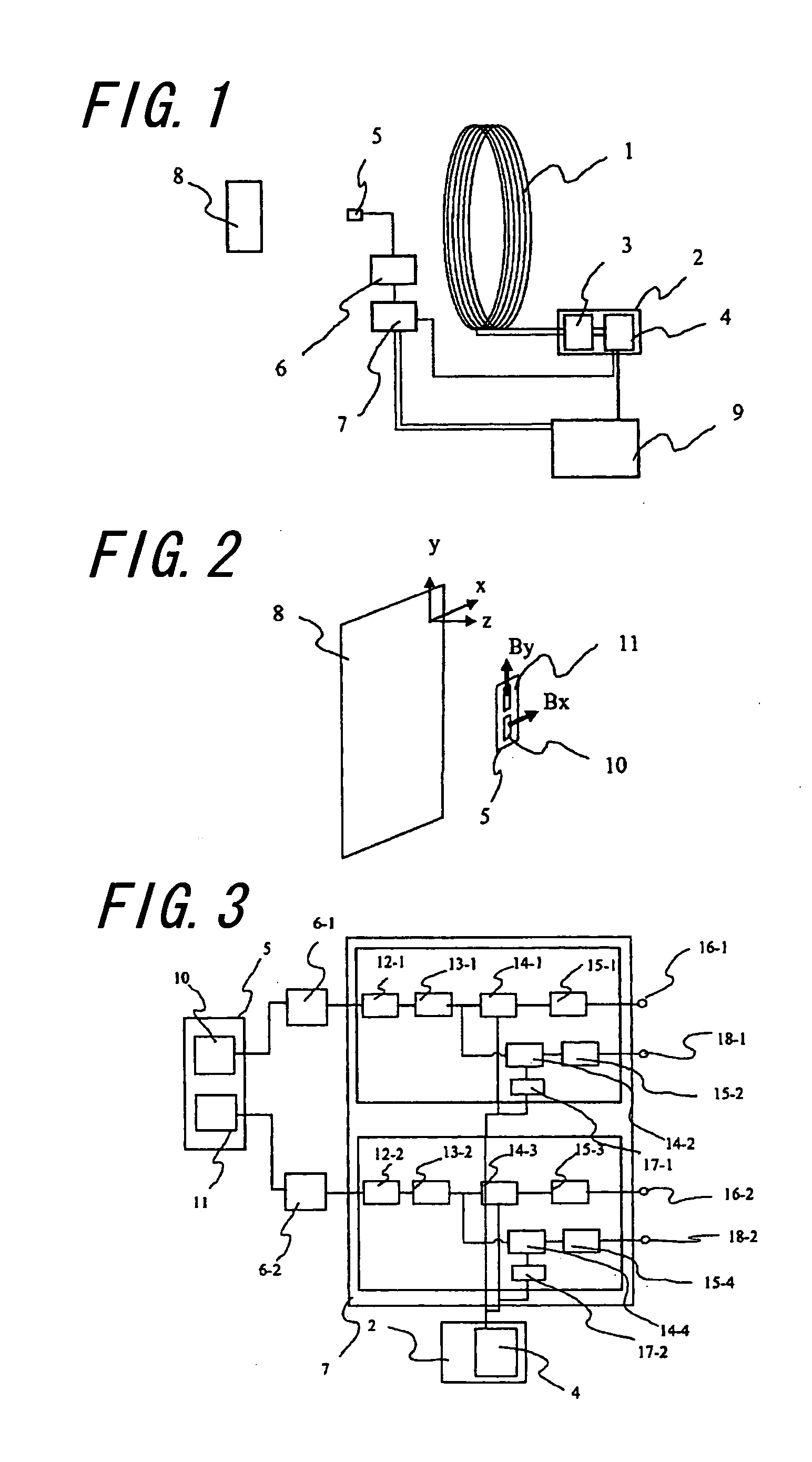

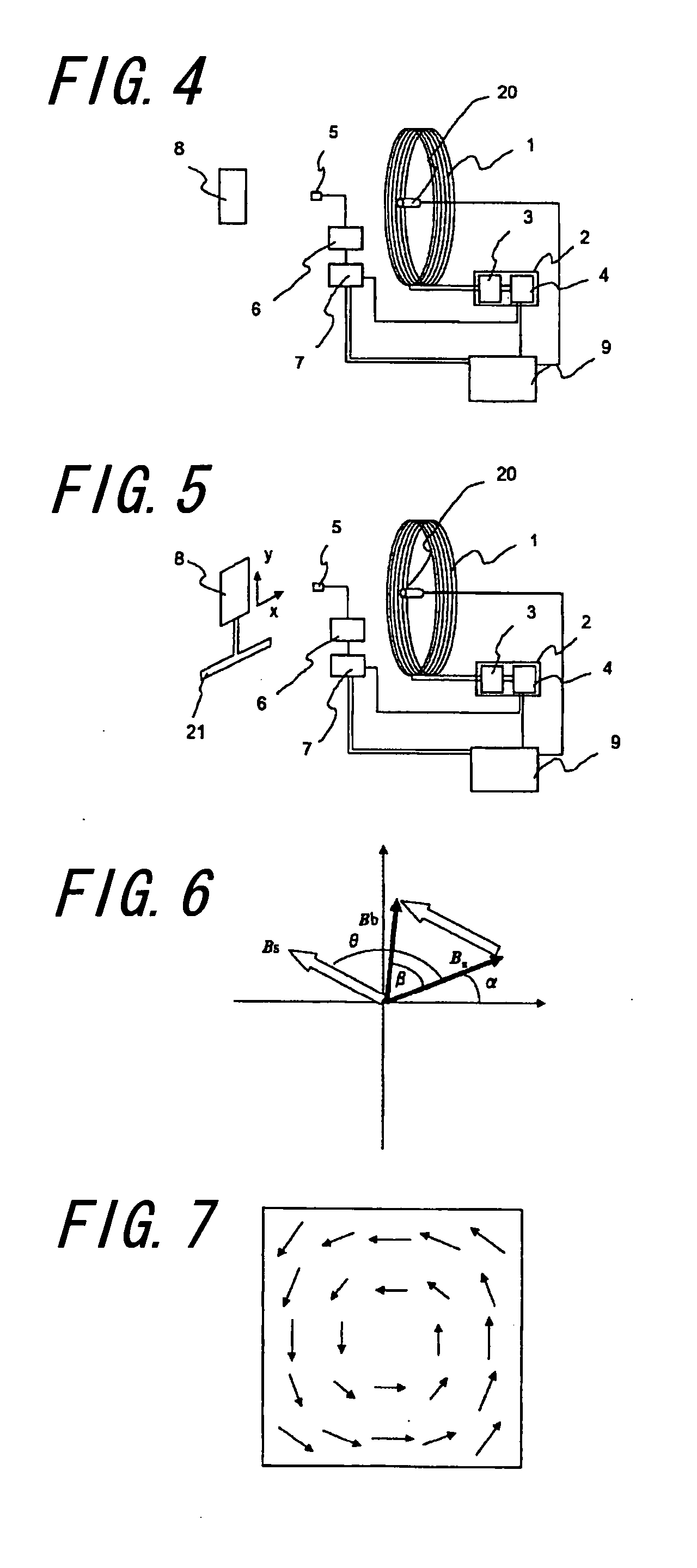

Magnetic Impedance Measurement Device

InactiveUS20080211492A1Simple configurationImprove accuracyMagnetic property measurementsBurglar alarm electric actuationMeasurement deviceTest object

The distribution of the impedance characteristic of a test object is detected by applying an alternate magnetic field of a low frequency to the test object and measuring the induced current generated therefrom.The present invention relates to a magnetic impedance measurement device comprising an apply coil for generating an alternate magnetic field of variable frequency, a power source for the apply coil, at least one magnetic sensor means comprising a pair of magnetic sensors for detecting orthogonal vector components of a magnetic field generated from a test object, the vector components being parallel to the face of the apply coil, a measurement means for the magnetic sensor for measuring a detected signal from said magnetic sensor mean, the measurement means being located at a distance from the face of said apply coil and facing said test object, a lock-in amplifier circuit for detecting from an output of said measurement means a signal having the same frequency as the frequency of said apply coil and an analysis means for analyzing intensity and phase changes of an output of said magnetic sensor means with the use of an output signal of said lock-in amplifier circuit.

Owner:NATIONAL UNIVERSITY

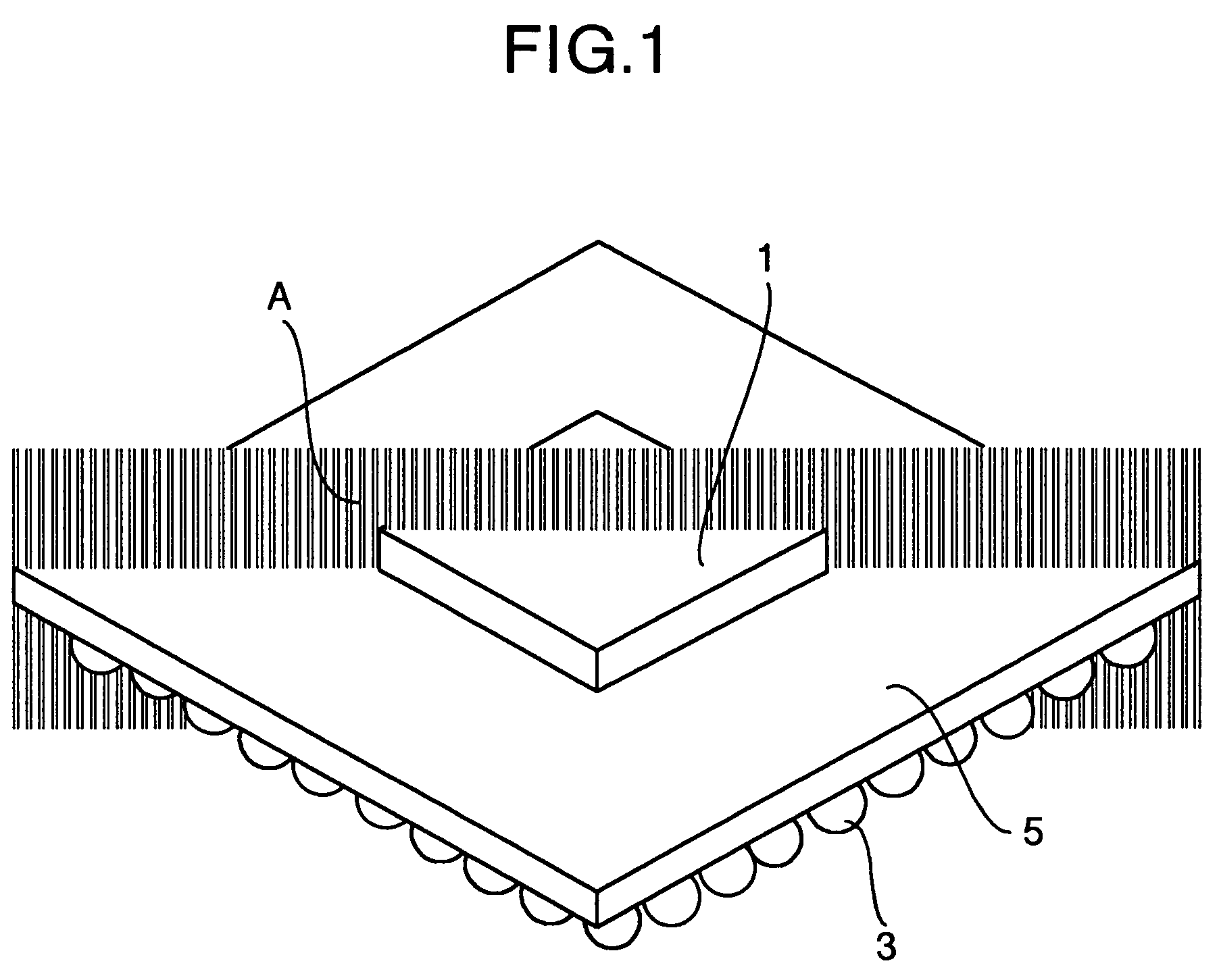

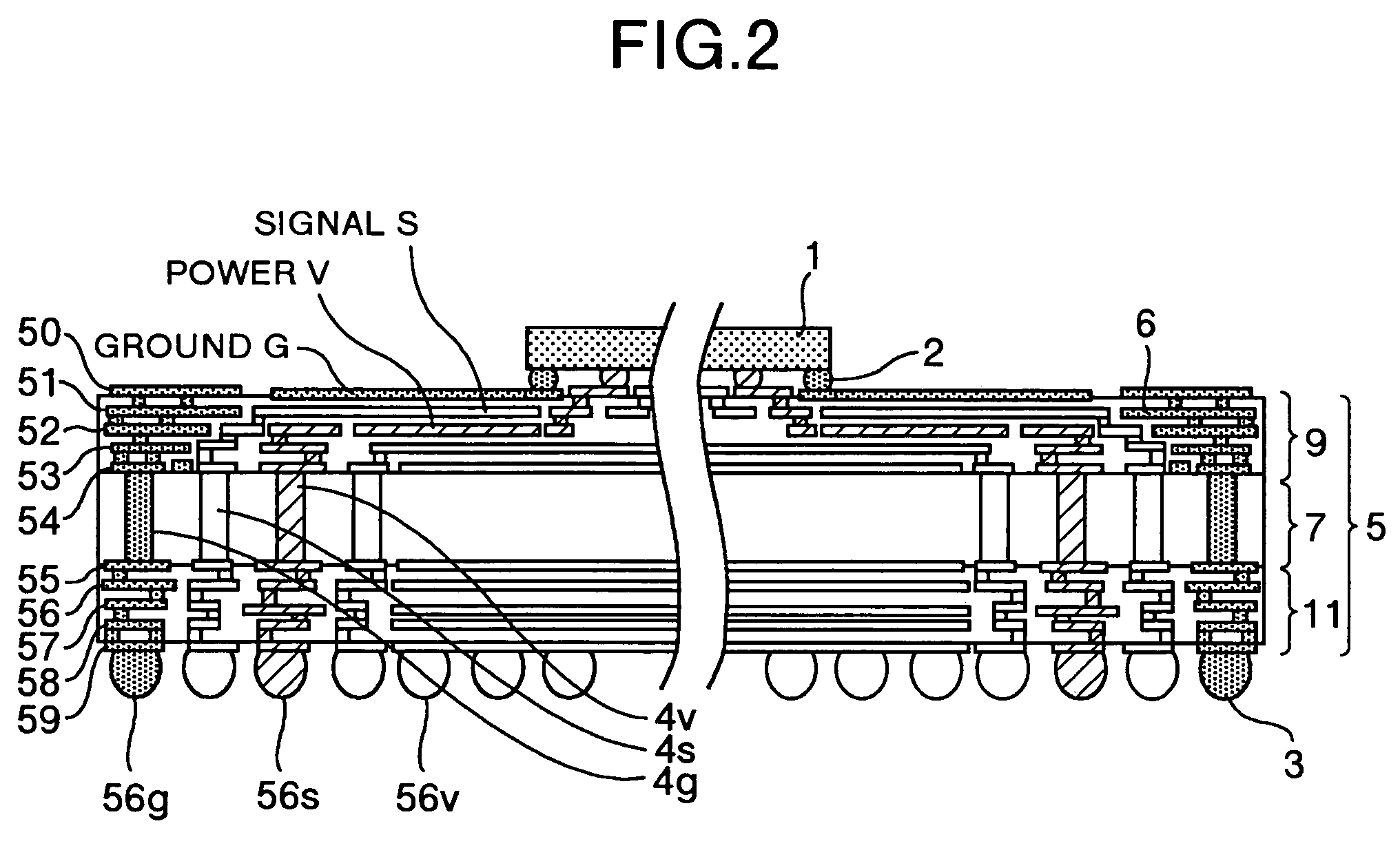

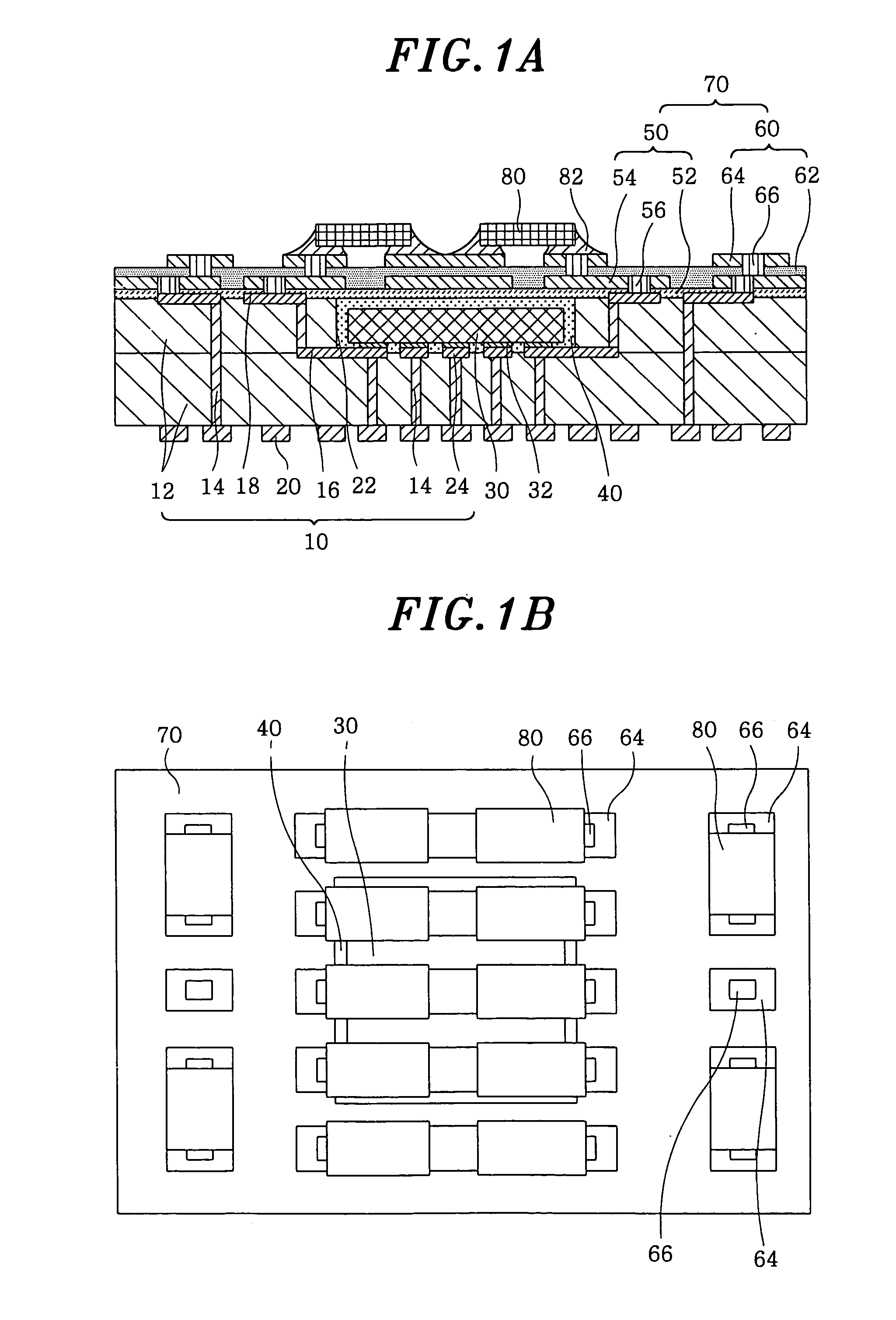

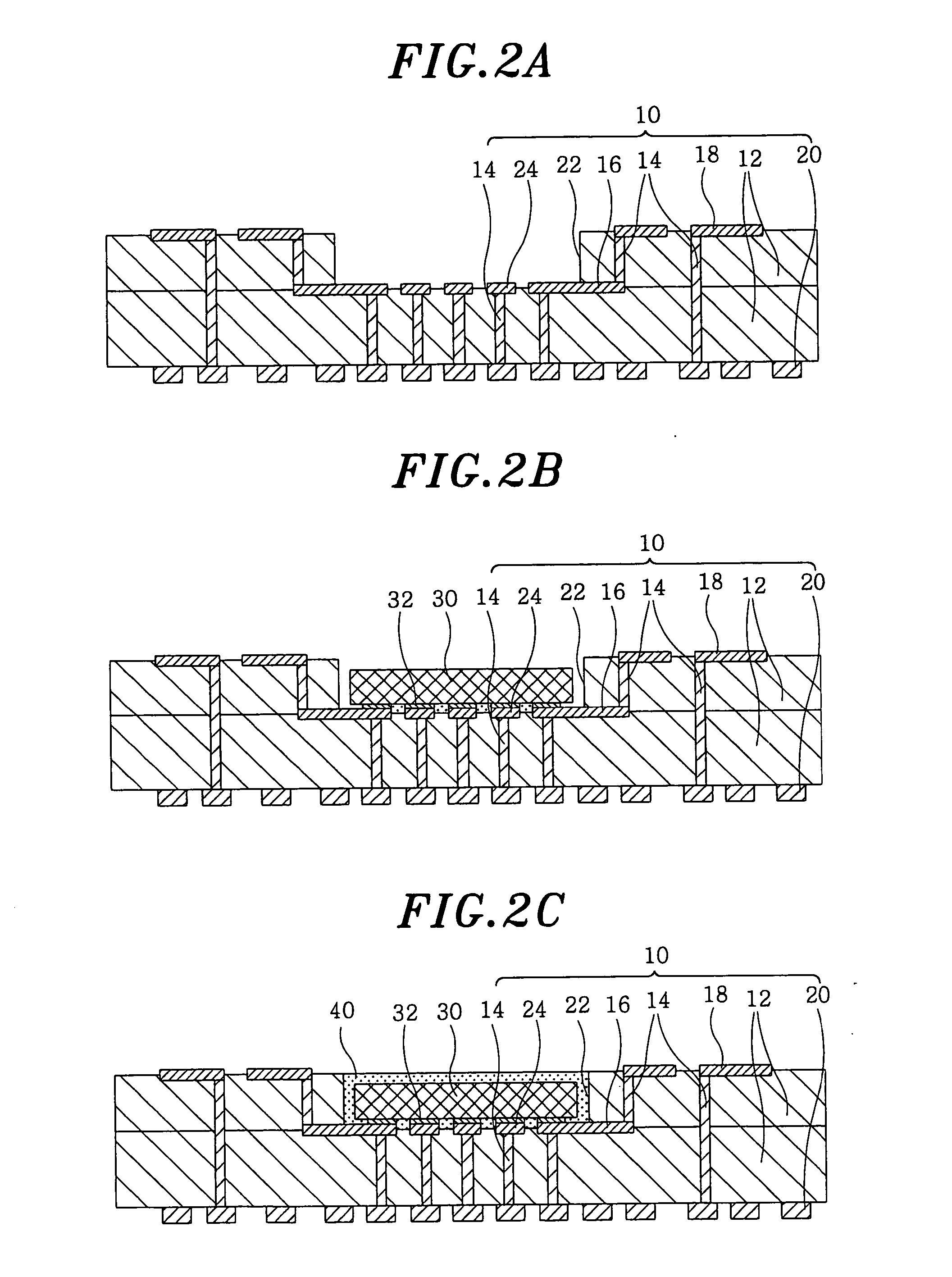

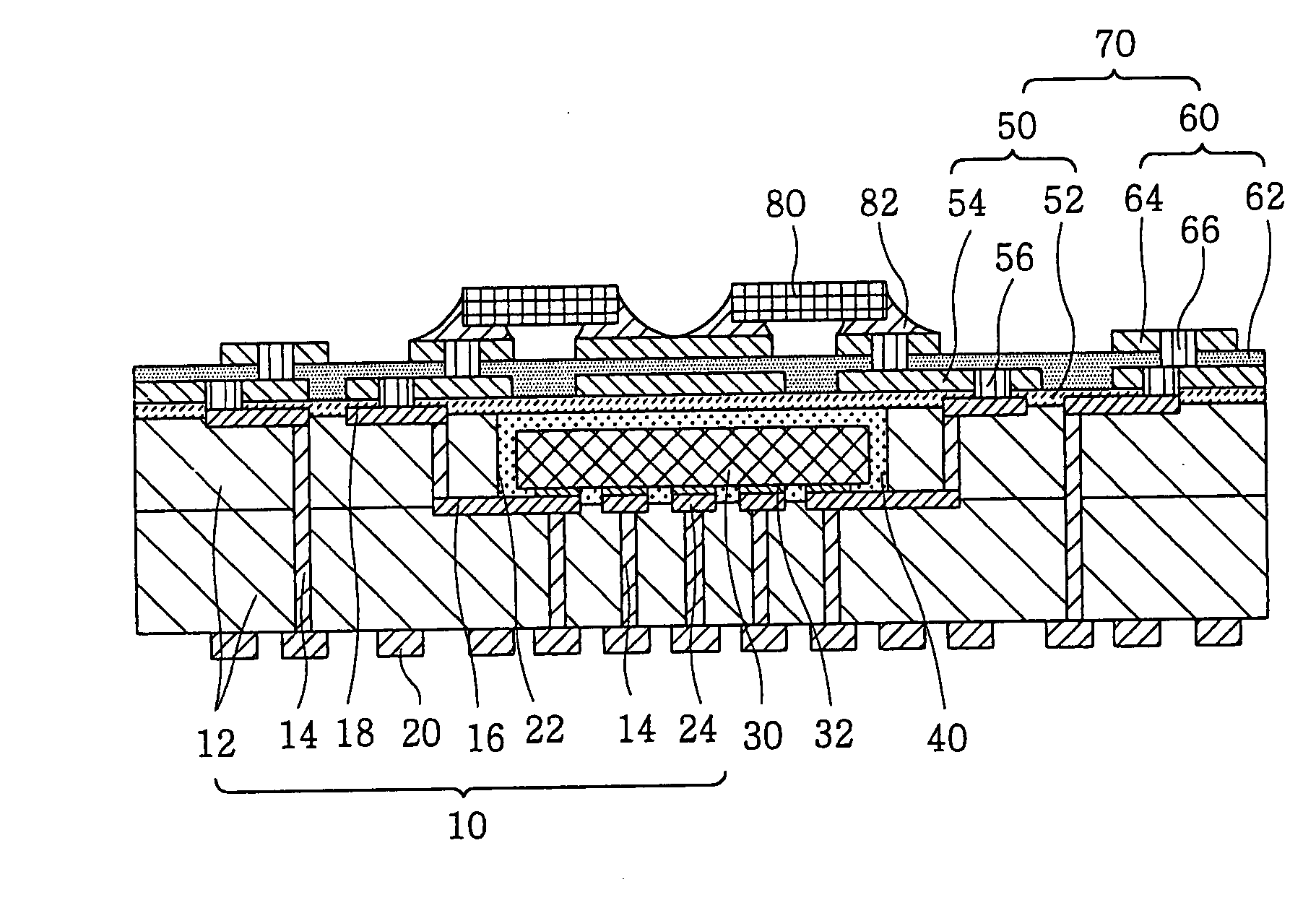

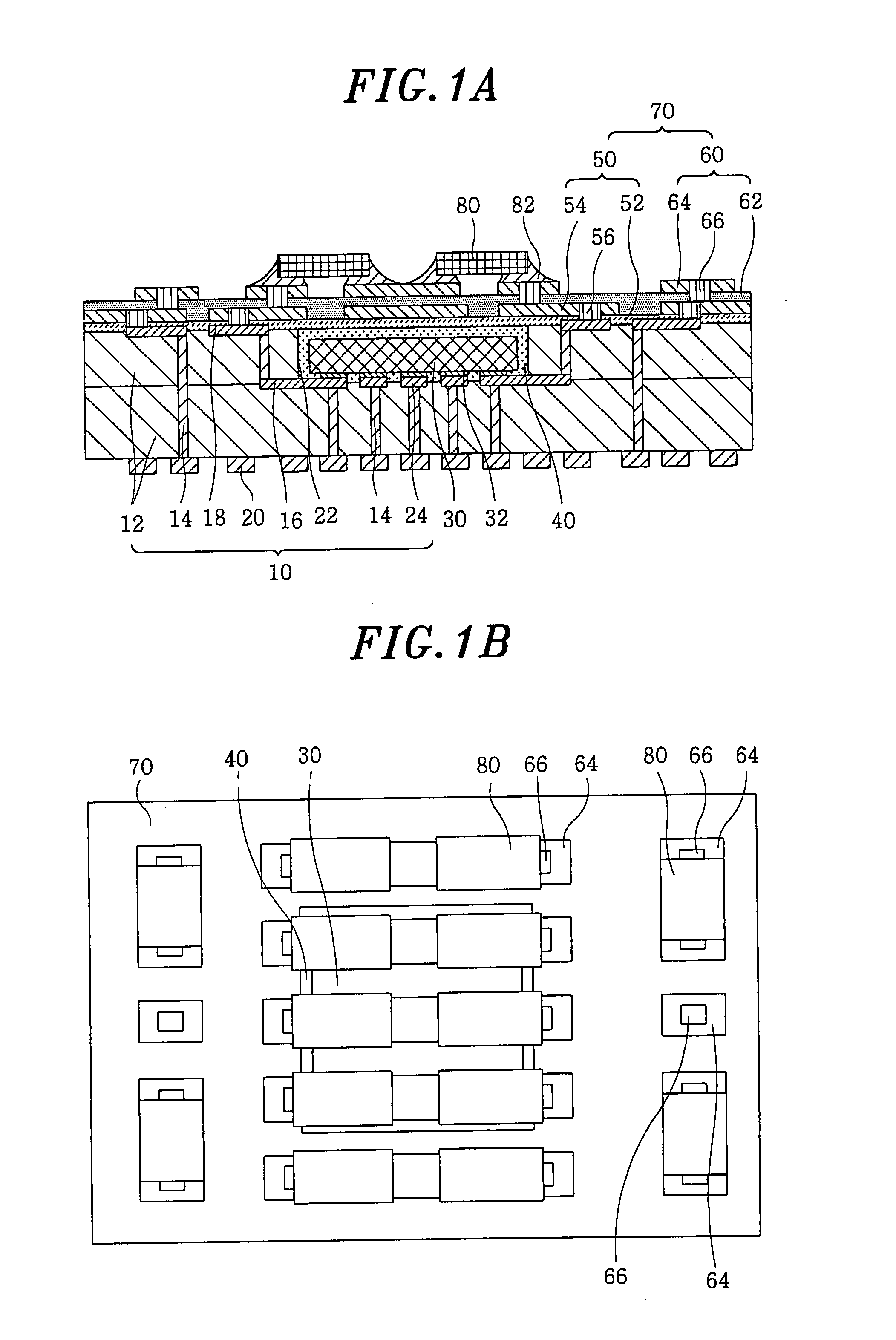

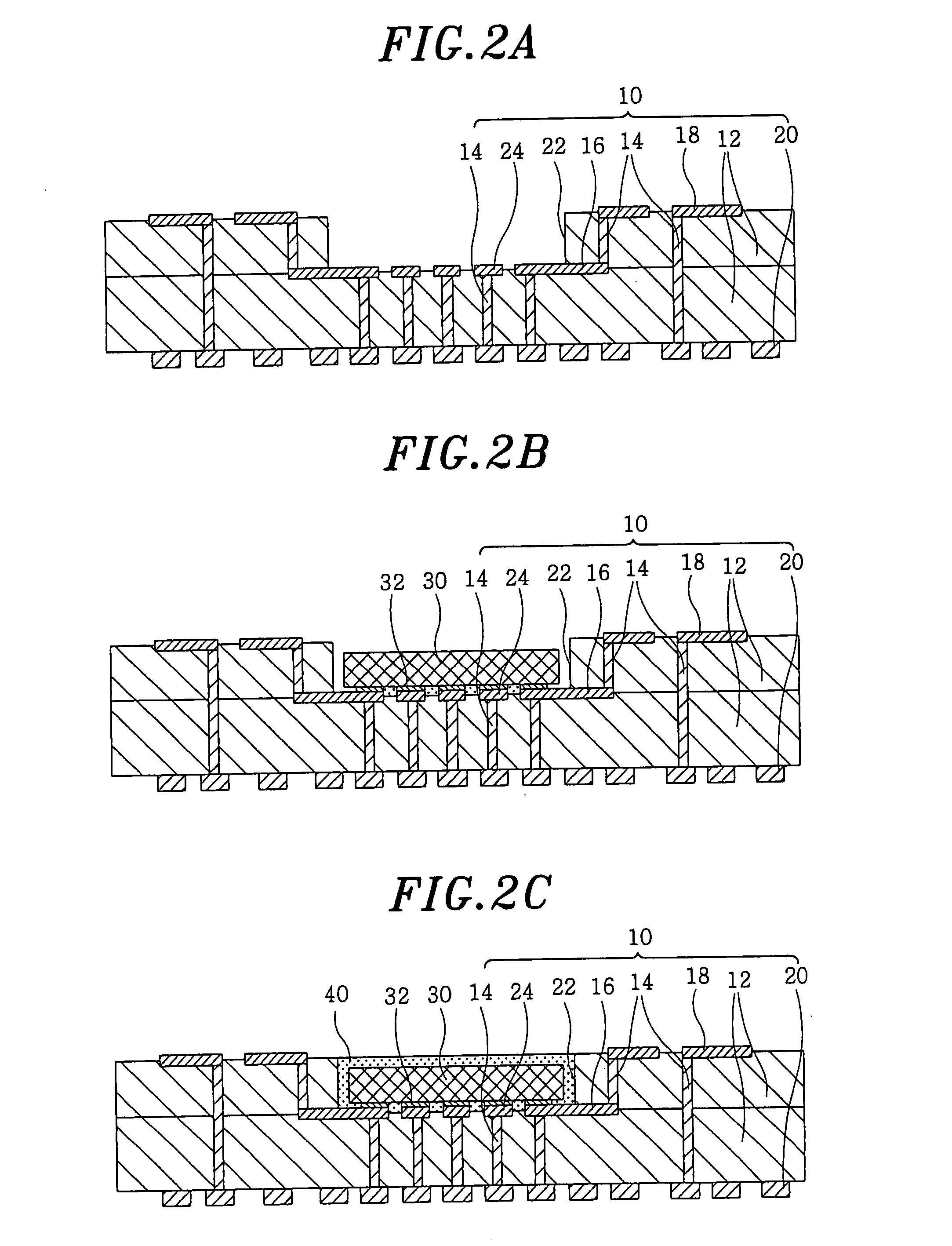

Circuit module and manufacturing method thereof

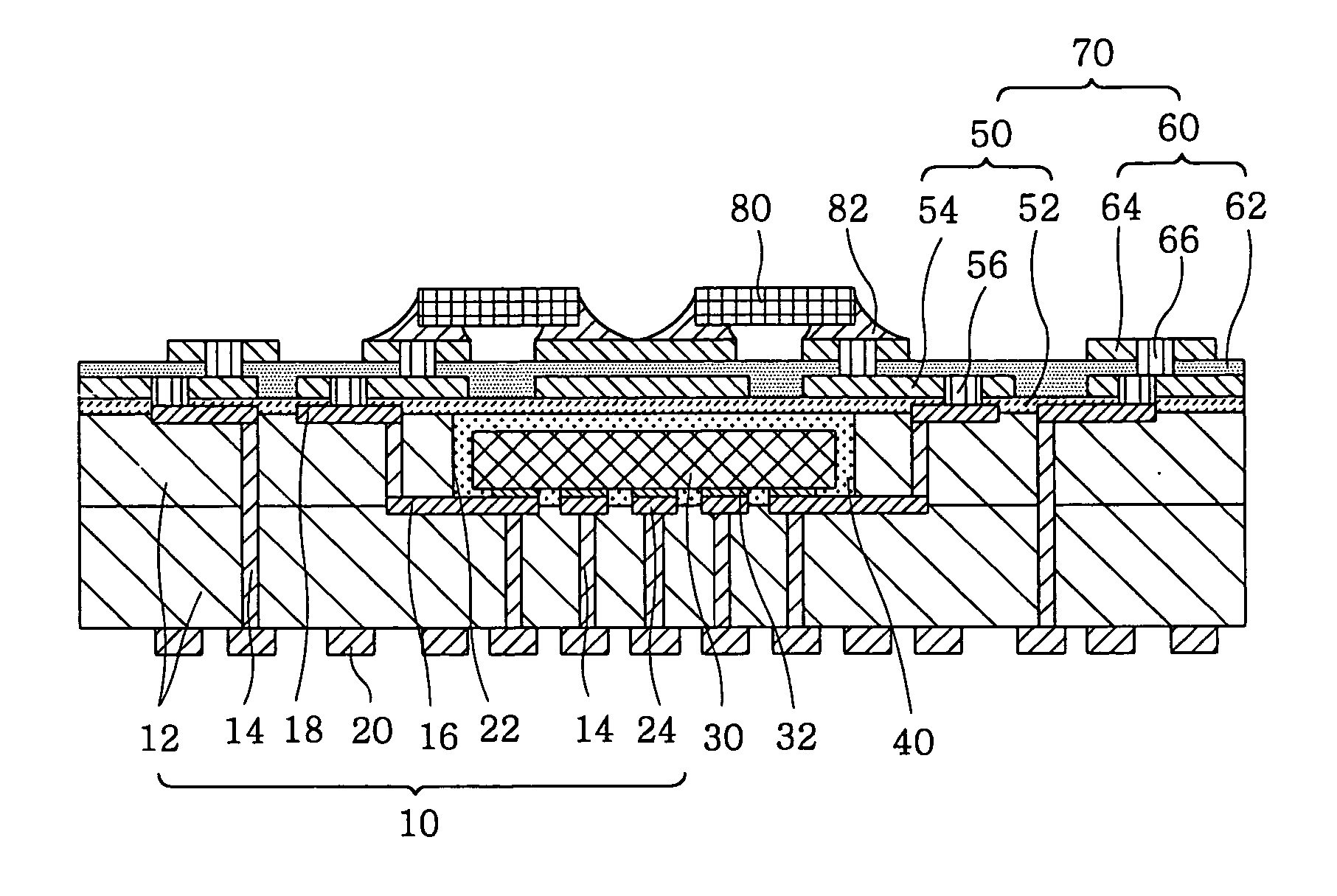

InactiveUS20050017347A1Higher-density mountabilityHigh-speed performanceInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsElectronic componentHemt circuits

A circuit module includes an electronic component, a ceramic multilayer substrate and a resin wiring substrate. The ceramic multilayer substrate is provided with a wiring layer disposed on top thereof and a cavity in which the electronic component is mounted, wherein a space between the electronic component and the cavity is filled with a thermosetting resin and a surface of the filled cavity is planarized. The resin wiring substrate has an insulating adhesive layer disposed at one side thereof and provided with at least one opening filled with a conductive resin. The ceramic multilayer substrate and the resin wiring substrate are bonded by the insulating adhesive layer, and the wiring layer on the ceramic multilayer substrate is electrically connected with the conductive resin.

Owner:PANASONIC CORP

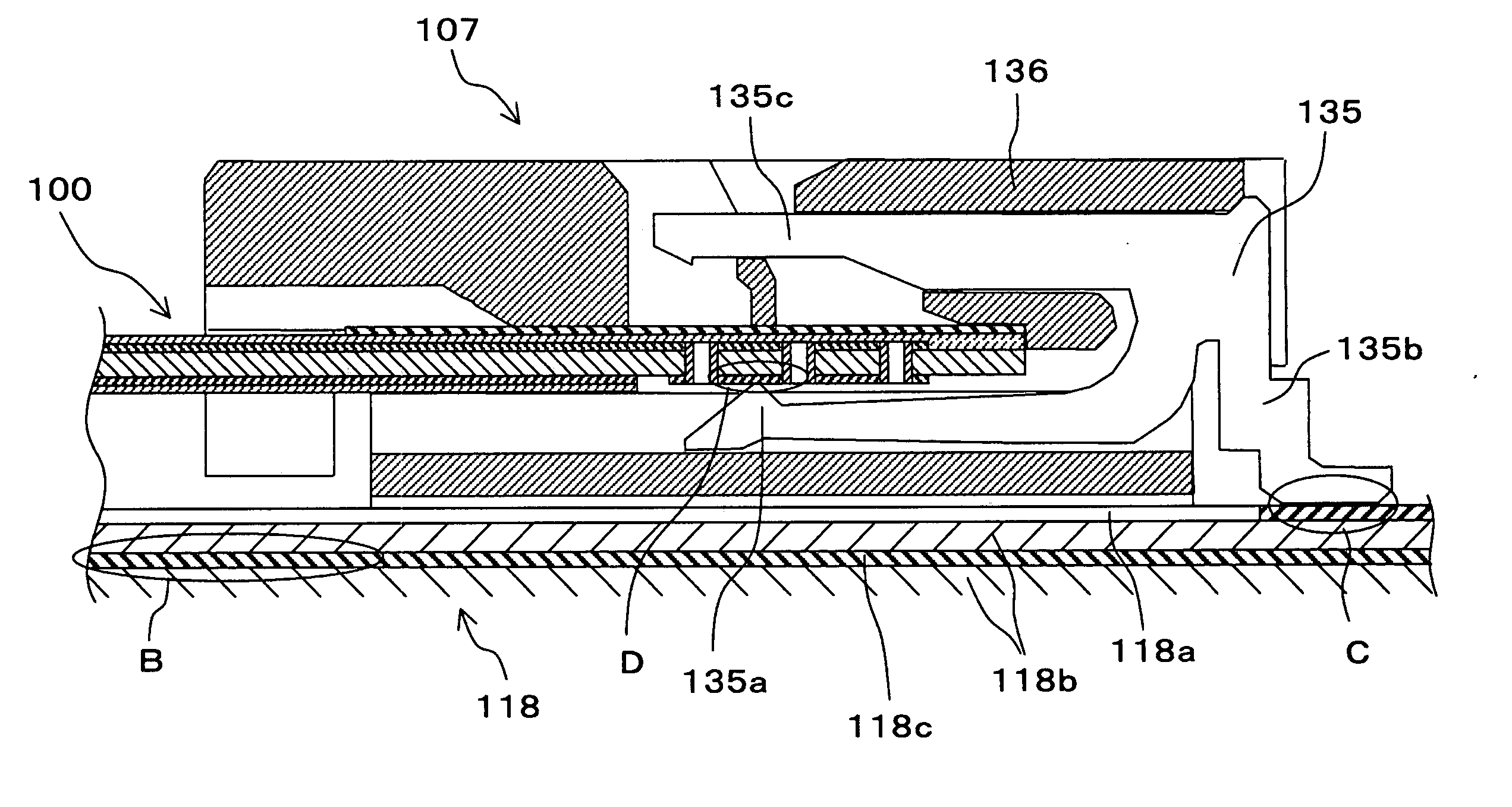

Flexible printed circuit board

InactiveUS20070102830A1Deterioration in transmission characteristicReduce electrical impedanceCoupling device connectionsSemiconductor/solid-state device detailsInsulation layerEngineering

A flexible printed circuit board has an insulation layer, a first signal wiring layer including a microstrip line, a second signal wiring layer including a signal connection terminal for allowing the microstrip line to connect the exterior connector electrically, and a ground conductive section having a ground connection terminal for connecting the exterior connector. The microstrip line and the signal connection terminal are connected to each other by a wiring via hole. The wiring via hole passes through the insulation layer, the first signal wiring layer, and the second signal wiring layer. The microstrip line has a taper section which gradually enlarges a width of the microstrip line toward the wiring via hole in the vicinity of the wiring via hole. The ground conductive section that corresponds to the microstrip line has a taper section with a shape matching the taper section of the microstrip line.

Owner:SONY CORP

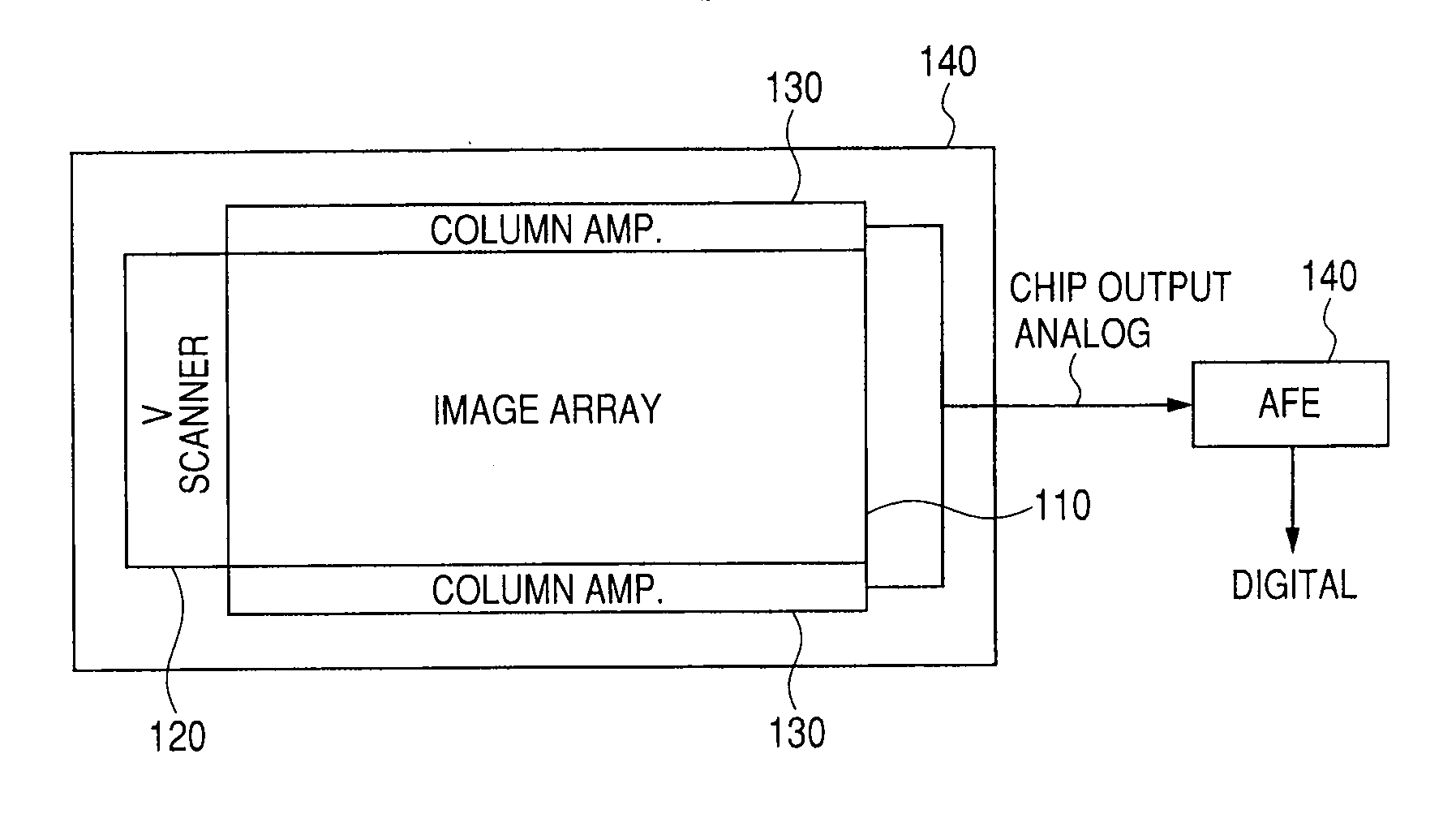

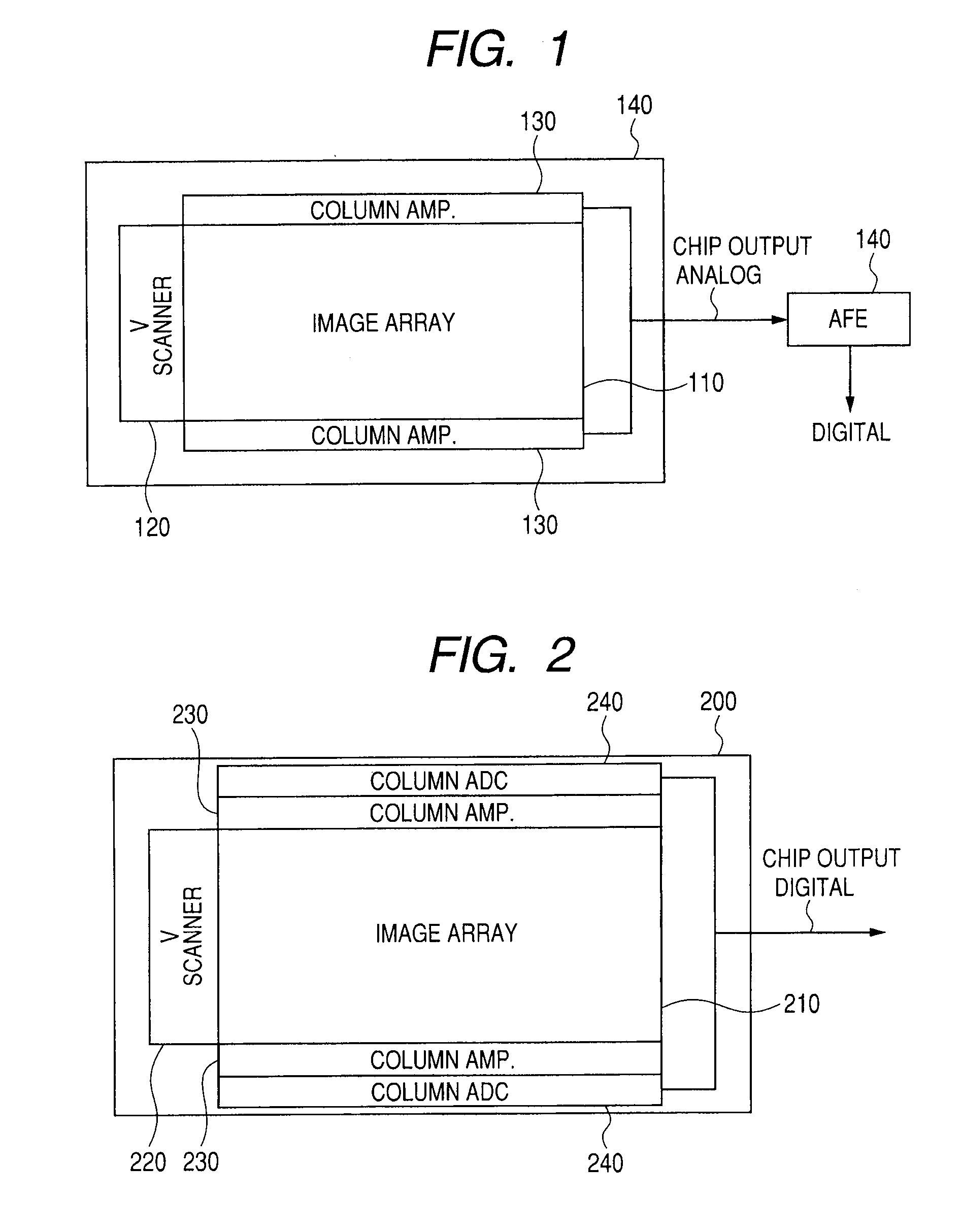

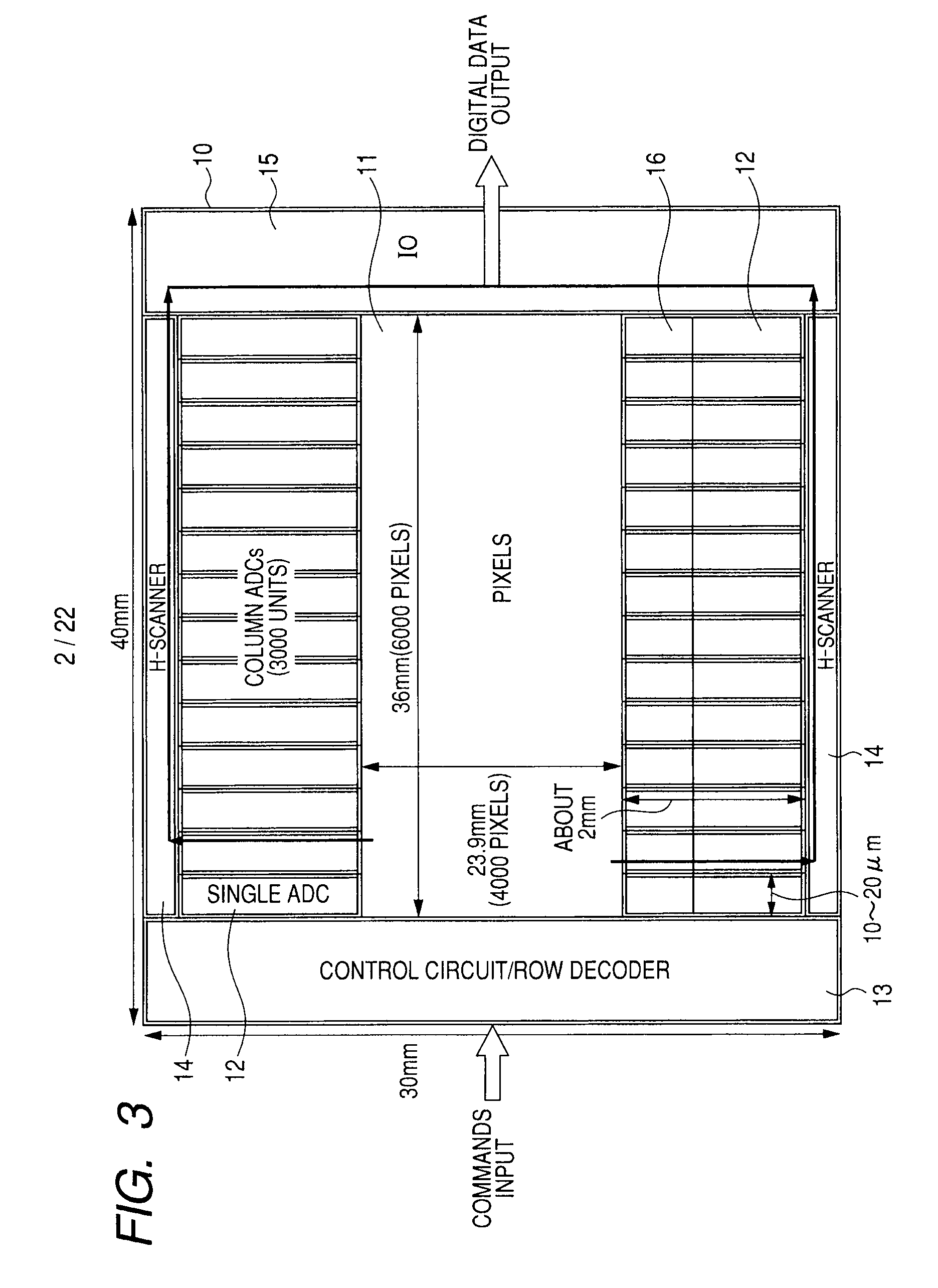

Solid-state image pickup device

ActiveUS20100231768A1Simple configurationIncrease speedTelevision system detailsTelevision system scanning detailsCapacitanceCapacitor

There is provided a solid-state image pickup device including ADCs that can be arranged in a limited space. The potential of a pixel signal outputted through a vertical readout line is held at a node. A plurality of capacitors are capacitively coupled to the node at which the pixel signal is held. The potential of the node is decreased in a stepwise manner by sequentially switching the voltages of the counter electrodes of the capacitors by the control of transistors. A comparator compares the potential of the node with the potential of the dark state of the pixel, and determines the upper bits of a digital value when the potential of the node becomes lower than the potential of the dark state. Following this, the conversion of the lower bits of the digital value is started. Therefore, it is possible to simplify the configuration of each ADC and arrange each ADC in a limited space.

Owner:RENESAS ELECTRONICS CORP

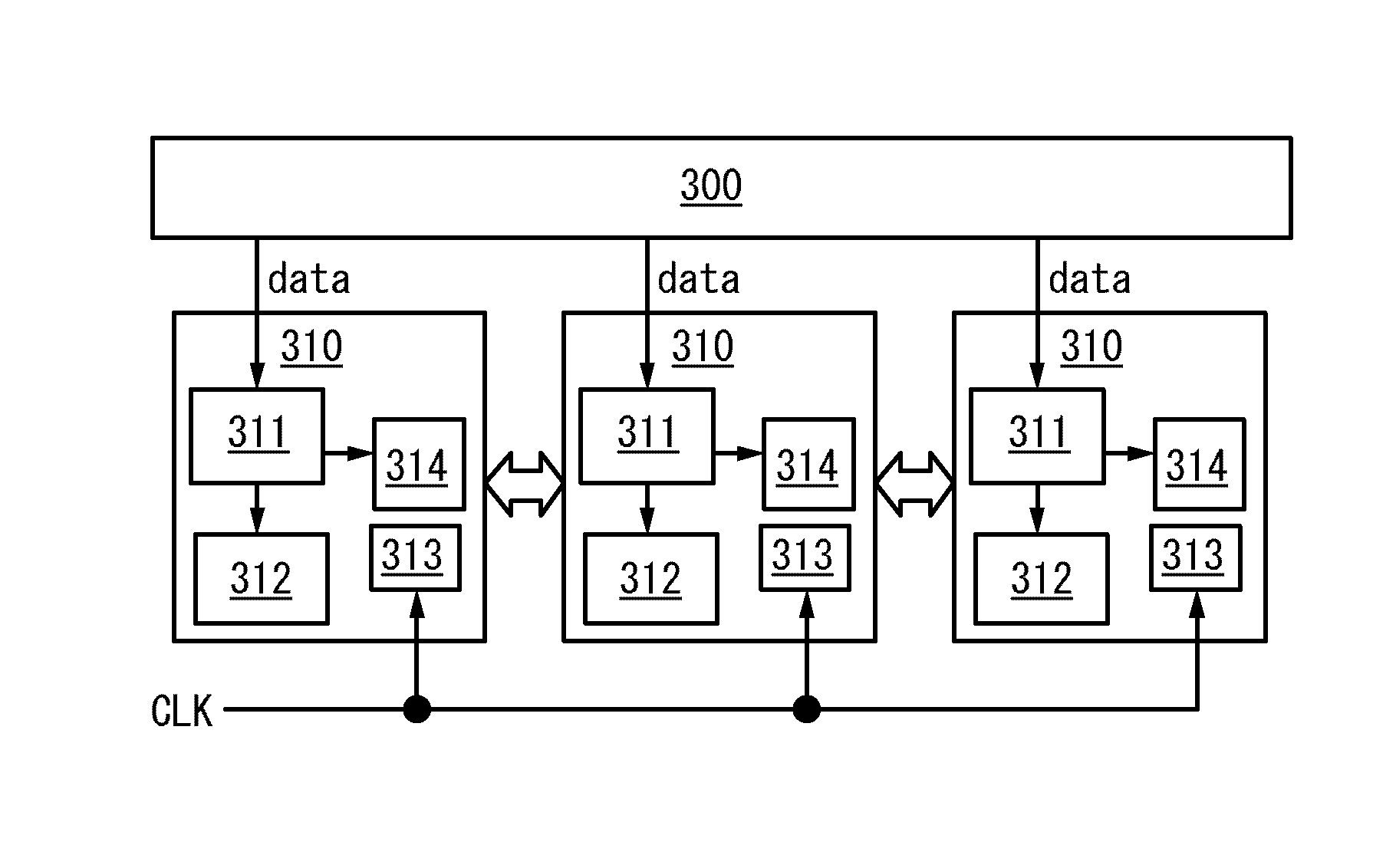

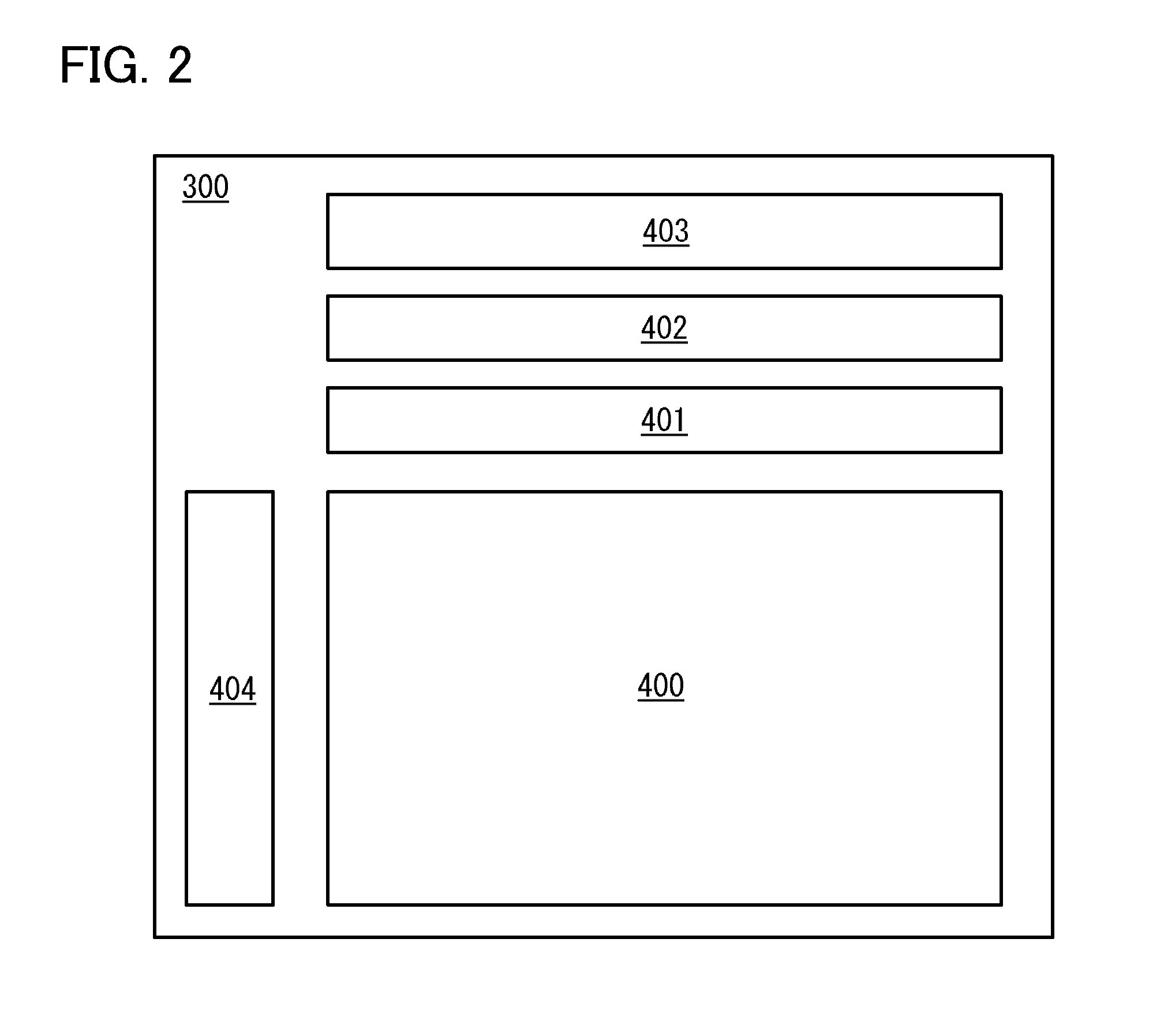

Programmable LSI

InactiveUS8675382B2Start fastIncrease speedDigital storageLogic circuitsElectricityComputer architecture

Owner:SEMICON ENERGY LAB CO LTD

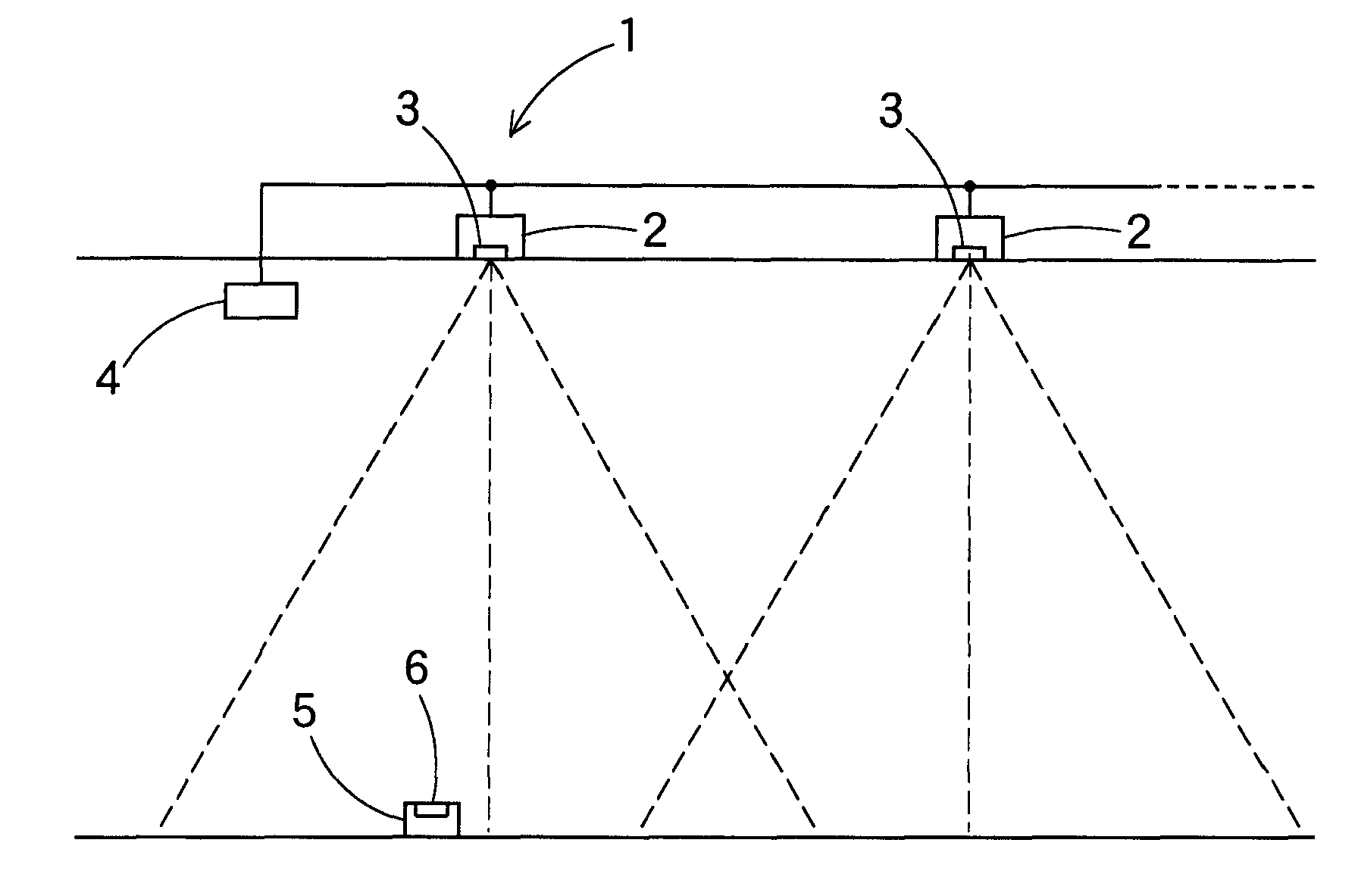

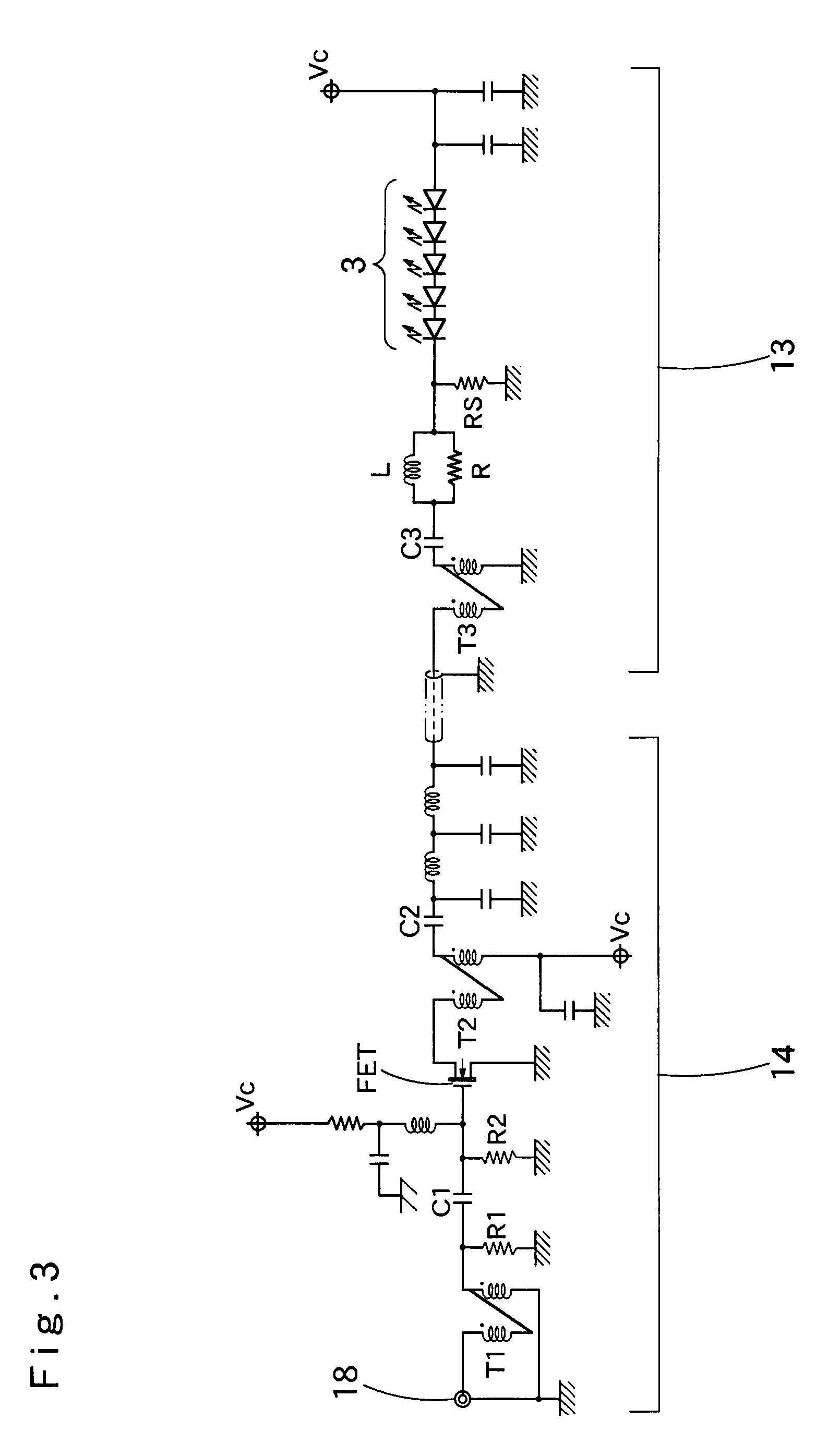

Visible light communication apparatus

A visible light communication apparatus is constituted with a transmitter for illuminating and projecting visible light on which an information signal is superimposed from a lamp fitting and a receiver for receiving the visible light to take out the information signal superimposed on the visible light. The transmitter modulates a transmission information signal, driving a light projecting element of the lamp fitting so as to superimpose the transmission information signal on the visible light of the lamp fitting, thereby radiating white light containing a blue light component as visible illumination light. The receiver receives the white visible light containing the blue light component radiated from the transmitter and generates a receiving information signal from the light receiving signal on a receiving circuit. A blue light photodiode which receives blue light at the highest sensitivity to output a light receiving signal is used as a light receiving element of the light receiving unit. The lamp fitting for radiating the white light containing the blue light component on the side of the transmitter as visible illumination light and the blue light photodiode for receiving blue light on the side of the receiver at the highest sensitivity can be used to perform visible light communications at high speed, while illuminating by the white light.

Owner:PLANNERS LAND

Semiconductor memory device and control method thereof

InactiveUS20100124090A1Increase speedReduce power consumptionDigital storageAudio power amplifierPhase-change memory

To provide data lines connected via column switches to a plurality of sense amplifiers and an input / output circuit that, in response to a write request, supplies pre-write data through the data line to selected phase change memory cells and then write data through the data line to the selected phase change memory cells. Thus, a pre-write operation and an actual write operation according to the write data can be performed at high speed. Because only the memory cells selected by a column address are subject to write, consumption power is reduced and lives of the memory cells are not shortened.

Owner:ELPIDA MEMORY INC

Circuit module and manufacturing method thereof

InactiveUS20080090335A1Higher-density mountabilityHigh-speed performanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

A circuit module includes an electronic component, a ceramic multilayer substrate and a resin wiring substrate. The ceramic multilayer substrate is provided with a wiring layer disposed on top thereof and a cavity in which the electronic component is mounted, wherein a space between the electronic component and the cavity is filled with a thermosetting resin and a surface of the filled cavity is planarized. The resin wiring substrate has an insulating adhesive layer disposed at one side thereof and provided with at least one opening filled with a conductive resin. The ceramic multilayer substrate and the resin wiring substrate are bonded by the insulating adhesive layer, and the wiring layer on the ceramic multilayer substrate is electrically connected with the conductive resin.

Owner:PANASONIC CORP

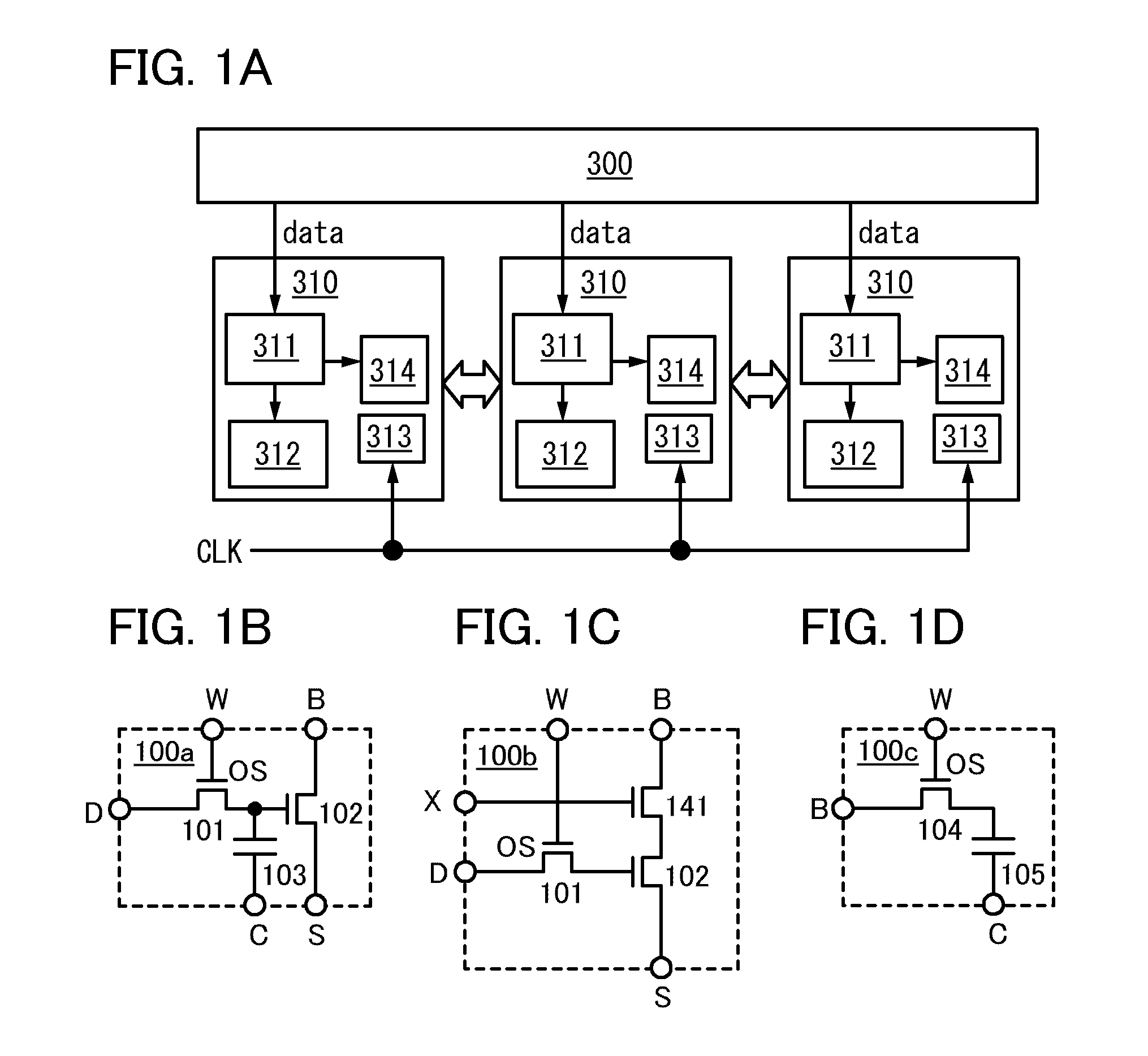

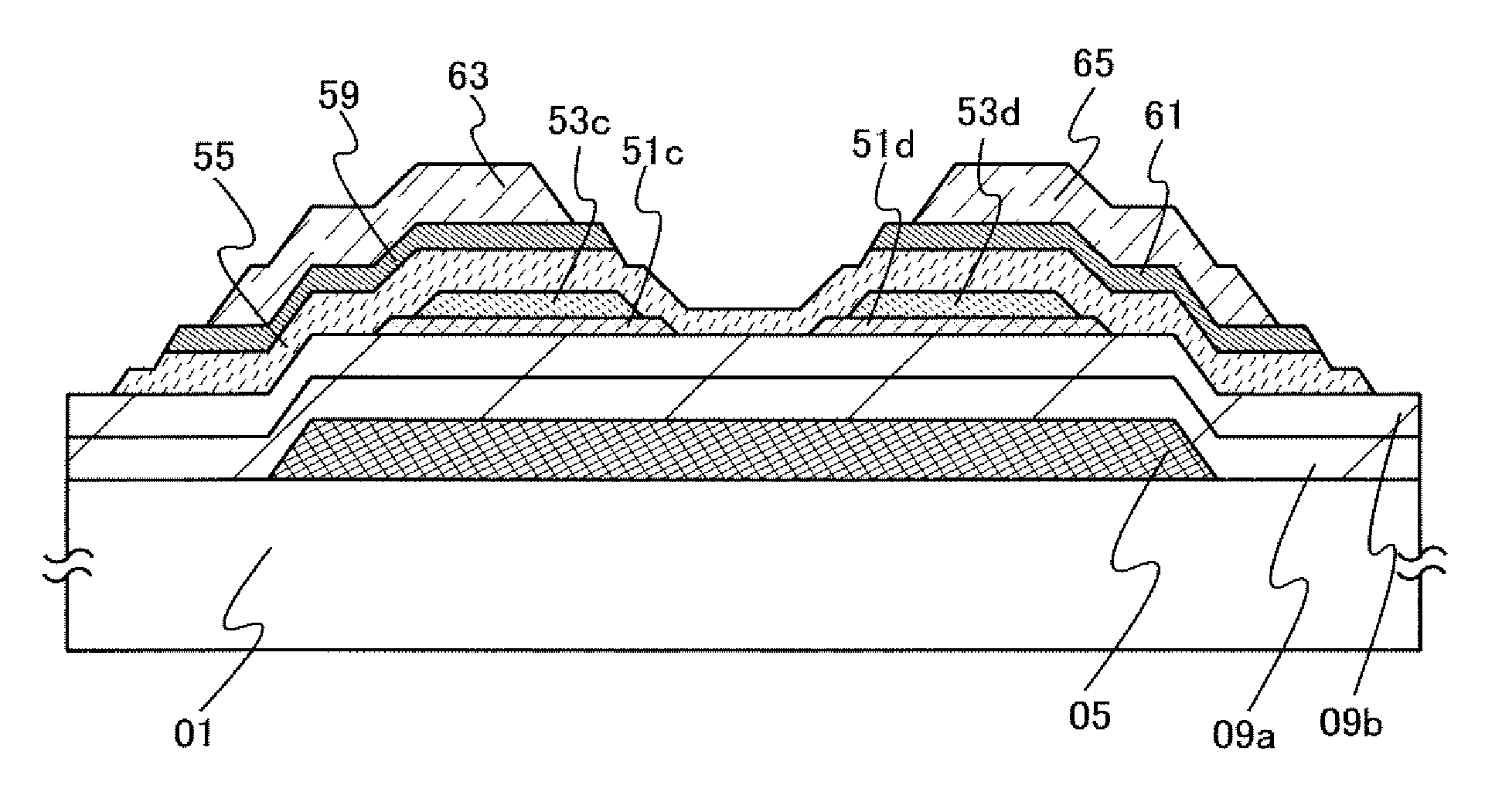

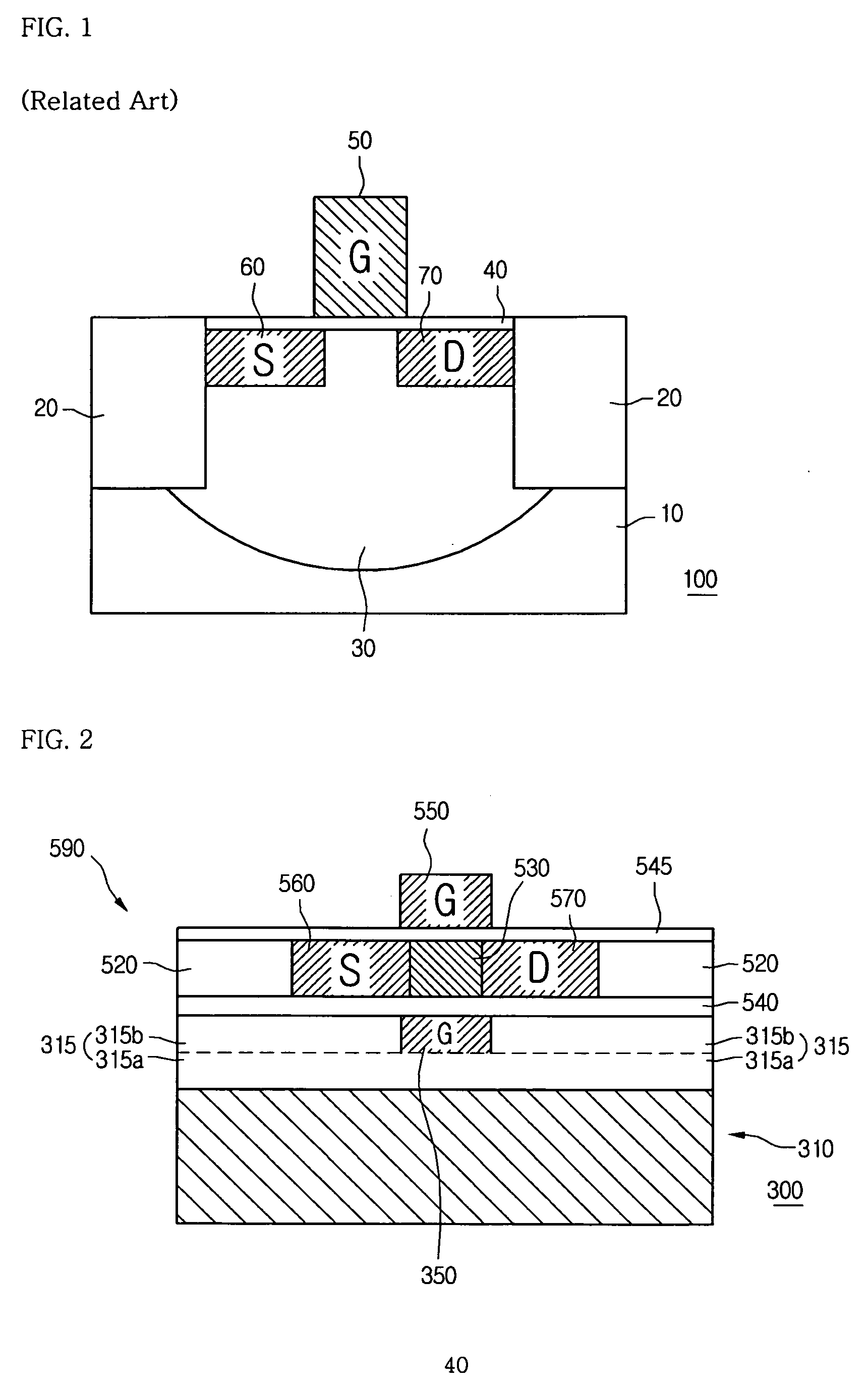

Thin-film transistor and display device

InactiveUS20090218572A1Increasing field-effect mobilityIncrease speedTransistorDisplay deviceImpurity

A thin-film transistor in which problems with ON-state current and OFF-state current are solved, and a thin-film transistor capable of high-speed operation. The thin-film transistor includes a pair of impurity semiconductor layers in which an impurity element imparting one conductivity type is added to form a source and drain regions, provided with a space therebetween so as to be overlapped with a gate electrode with a gate insulating layer interposed between the gate electrode and the impurity semiconductor layers; a pair of semiconductor layers in which an impurity element which serves as an acceptor is added, overlapped over the gate insulating layers with the gate electrode and the impurity semiconductor layers, and disposed with a space therebetween in a channel length direction; and an amorphous semiconductor layer being in contact with the gate insulating layer and the pair of semiconductor layers and extended between the pair of semiconductor layers.

Owner:SEMICON ENERGY LAB CO LTD

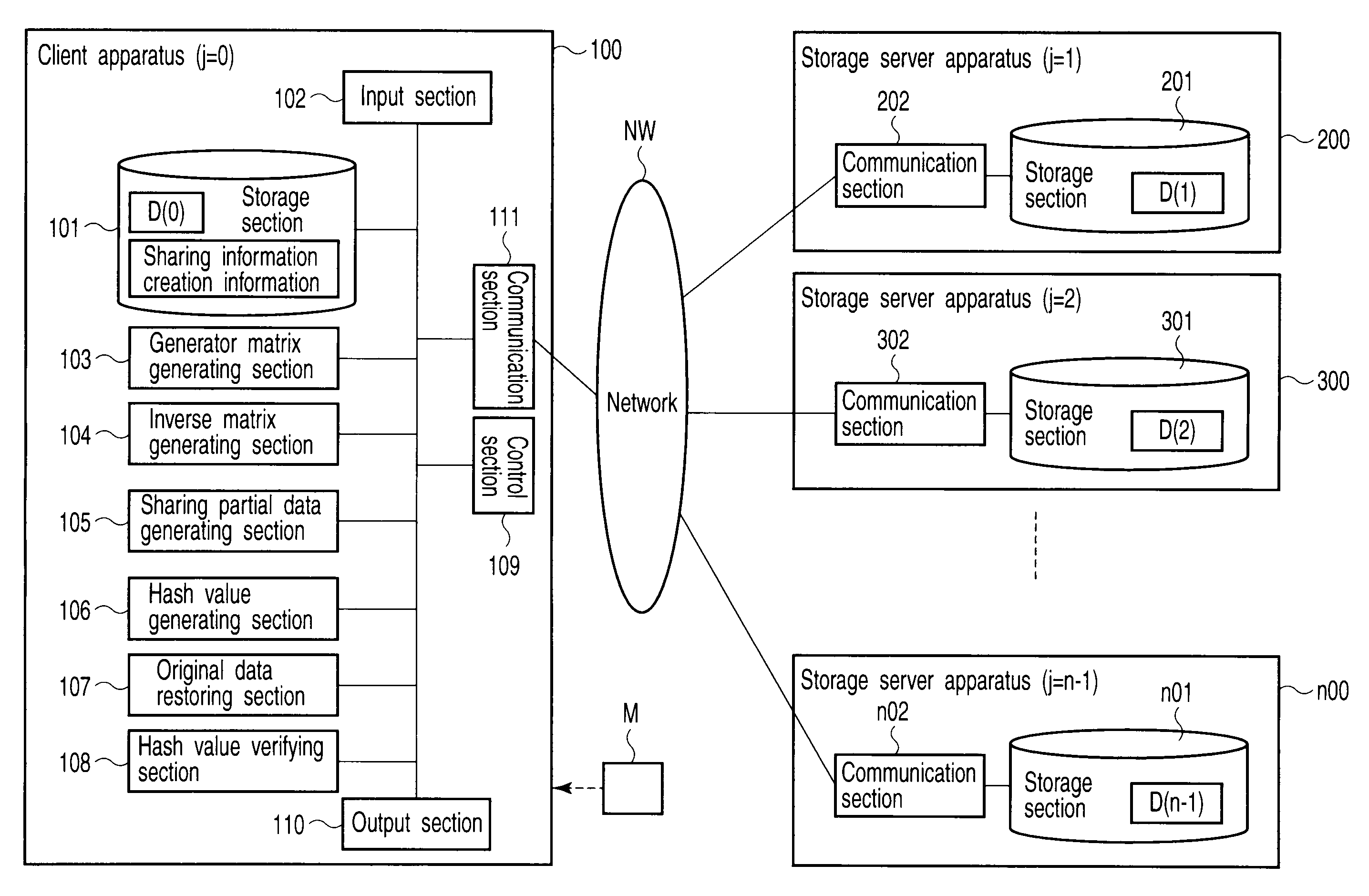

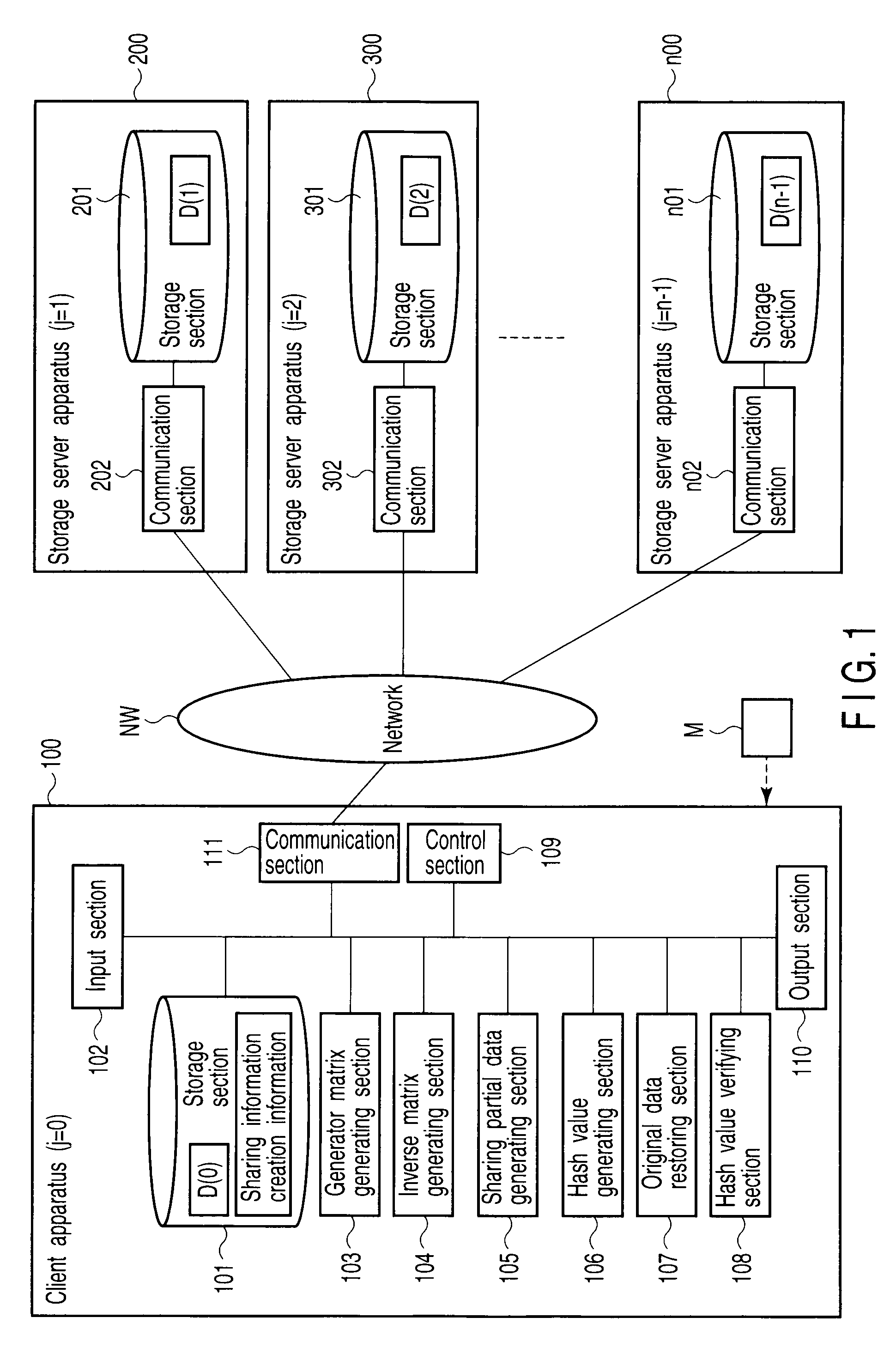

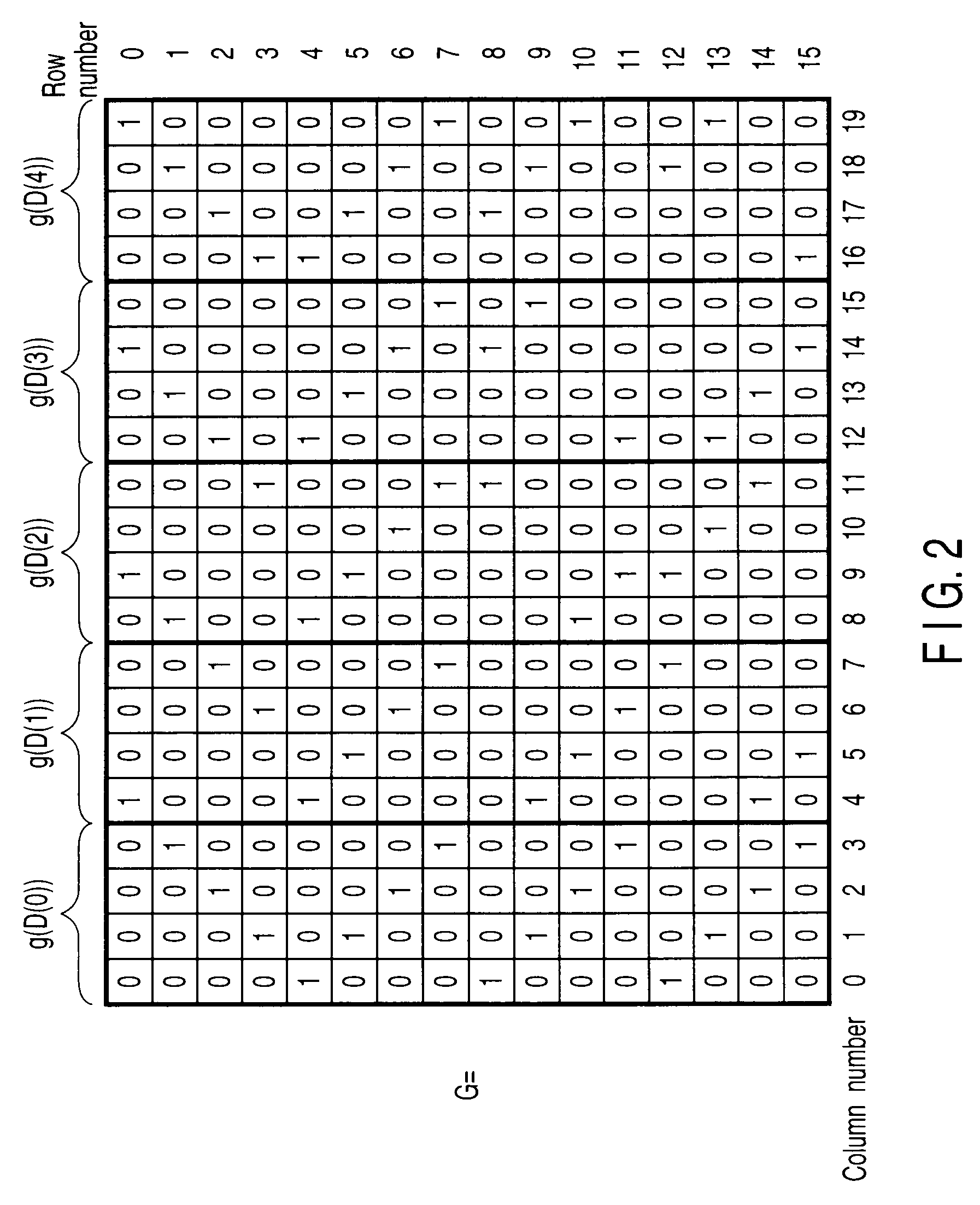

Secret sharing apparatus, method, and program

ActiveUS20080232580A1Increase speedHigh-speed performanceSecret communicationTelevision systemsAlgorithmTheoretical computer science

A secret sharing apparatus according to the present invention is based on a (k,n)-threshold scheme with a threshold of at least 4. The secret sharing apparatus generates a generator matrix (G) of GF(2) in which any k of n column vectors are at a full rank, divides secret information into n−1 pieces to generate divided secret data (K(1), . . . , K(n−1)), generates random data (U(0,1), . . . , U(k−2,n−1)), calculates the product of matrixes of the divided secret data, the random data, and the generator matrix (G), assigns the j×(n−1)+ith column of the calculation result to sharing partial data (D(j,i)) to calculate sharing partial data (D(j,1)), generates header information (H(j)), and individually distributes n pieces of sharing information (D(0), . . . , D(n−1)) made up of the header information (H(j)) and sharing partial data (D(j,i)) to n storage apparatuses.

Owner:TOSHIBA DIGITAL SOLUTIONS CORP +1

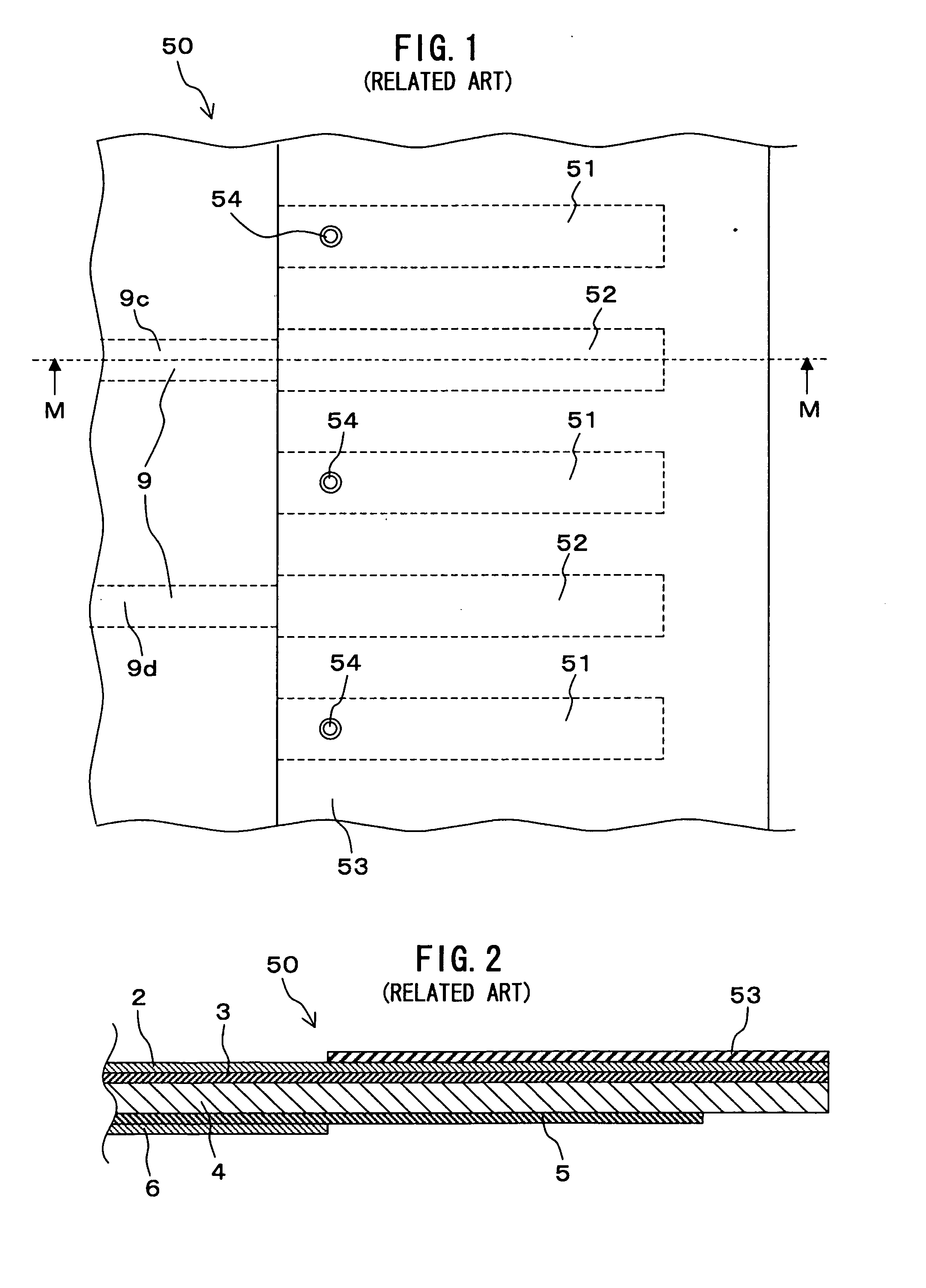

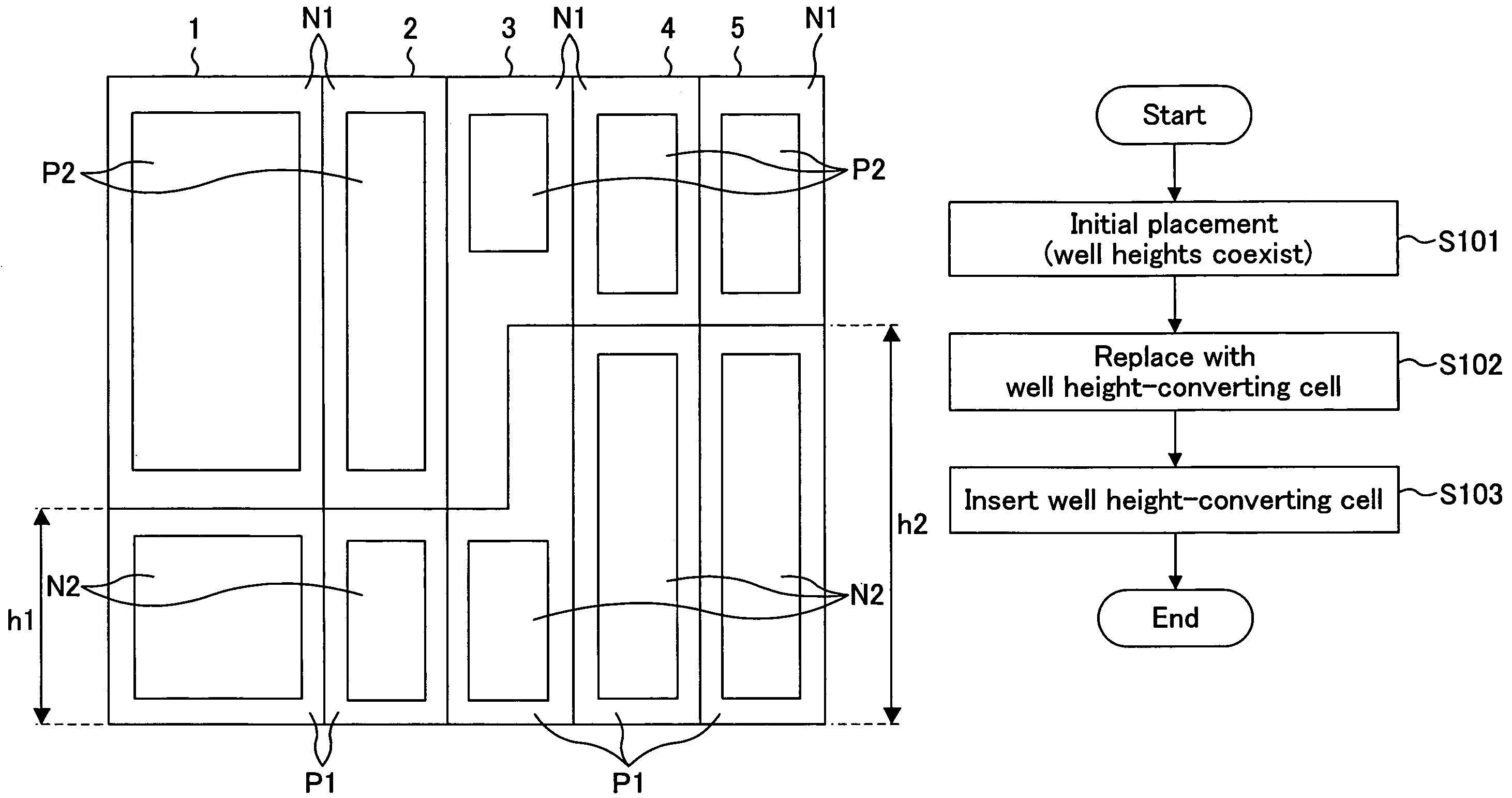

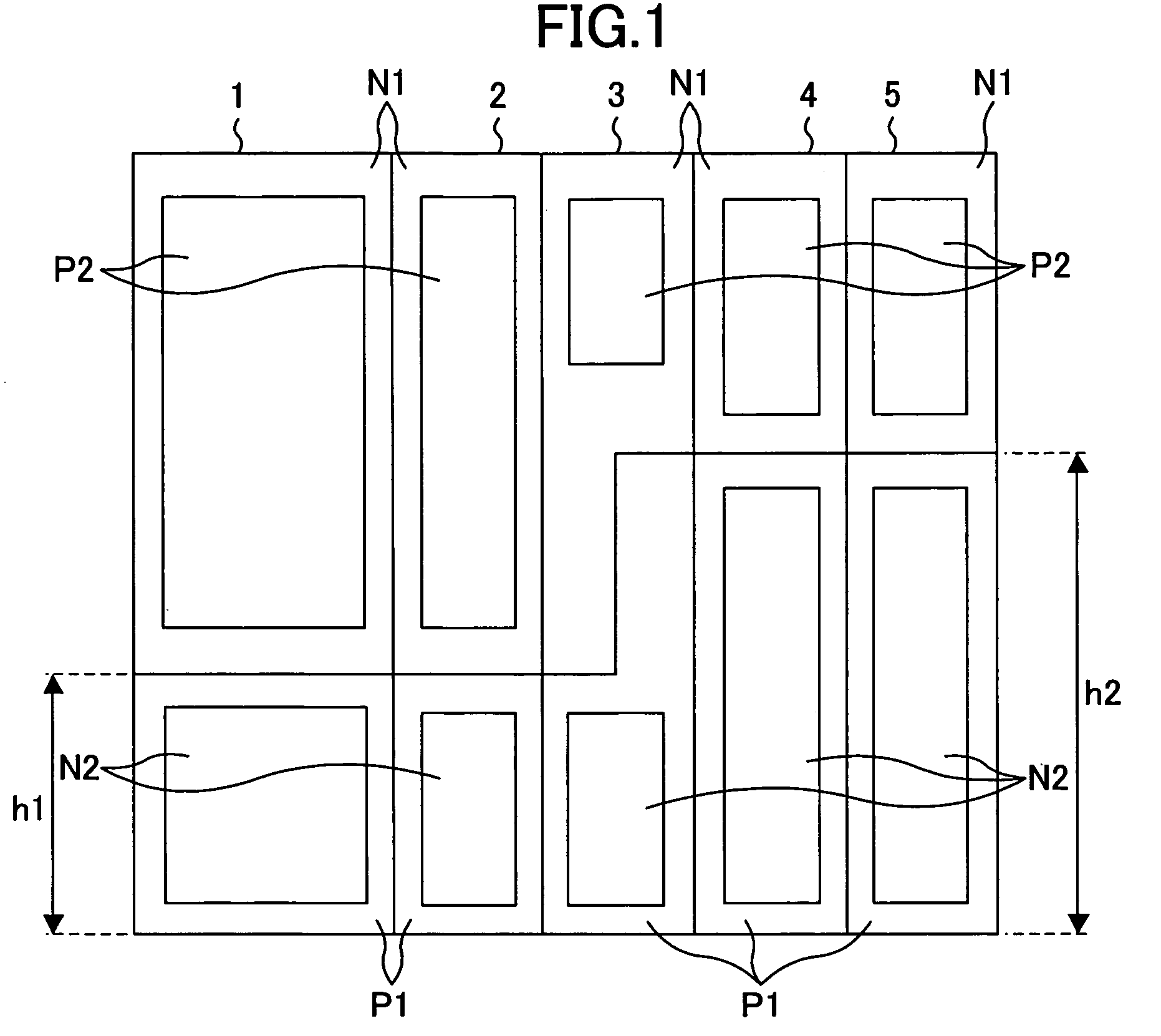

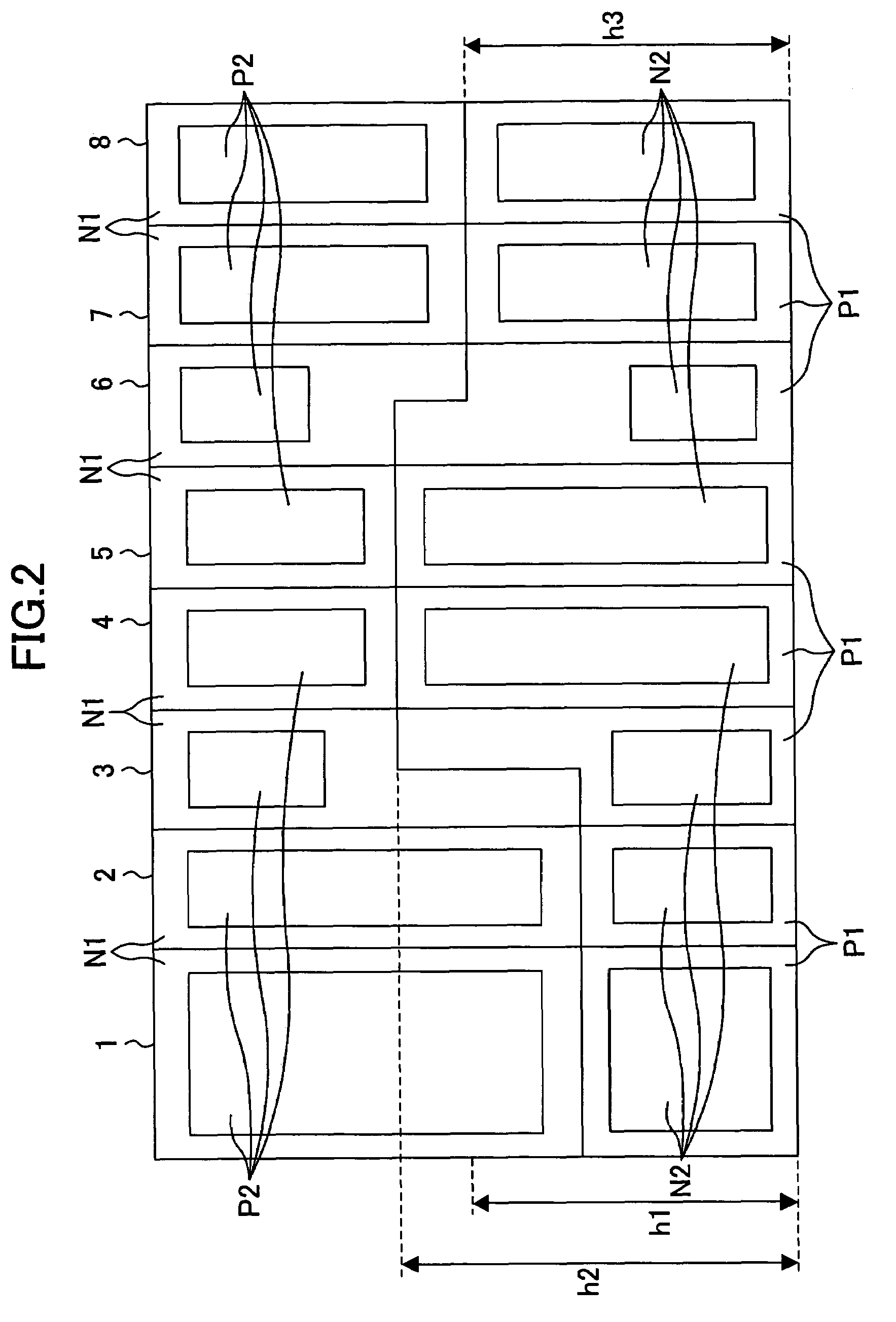

Standard cell, standard cell library, semiconductor device, and placing method of the same

InactiveUS7302660B2Satisfactory level of area efficiencySolve the lack of heightSolid-state devicesSemiconductor/solid-state device manufacturingBorder lineEngineering

Of a plurality of standard cells in which an N-well region and a P-well region are vertically formed, some standard cells have a border line between the N-well region and the P-well region which is set to be a low height (first height), and other standard cells have a border line between the N-well region and the P-well region which is set to be a high height (second height), depending on the size of a transistor formed in the standard cell. Although these standard cells have different border lines, a standard cell for linking the border lines is provided. In such a standard cell, an empty space is created by forming a small-size transistor therein, and the empty space is utilized so that, for example, a left end of the border line is set to have the first height and a right end of the border line is set to have the second height, whereby the border line is converted so as to link the heights therein.

Owner:SOCIONEXT INC

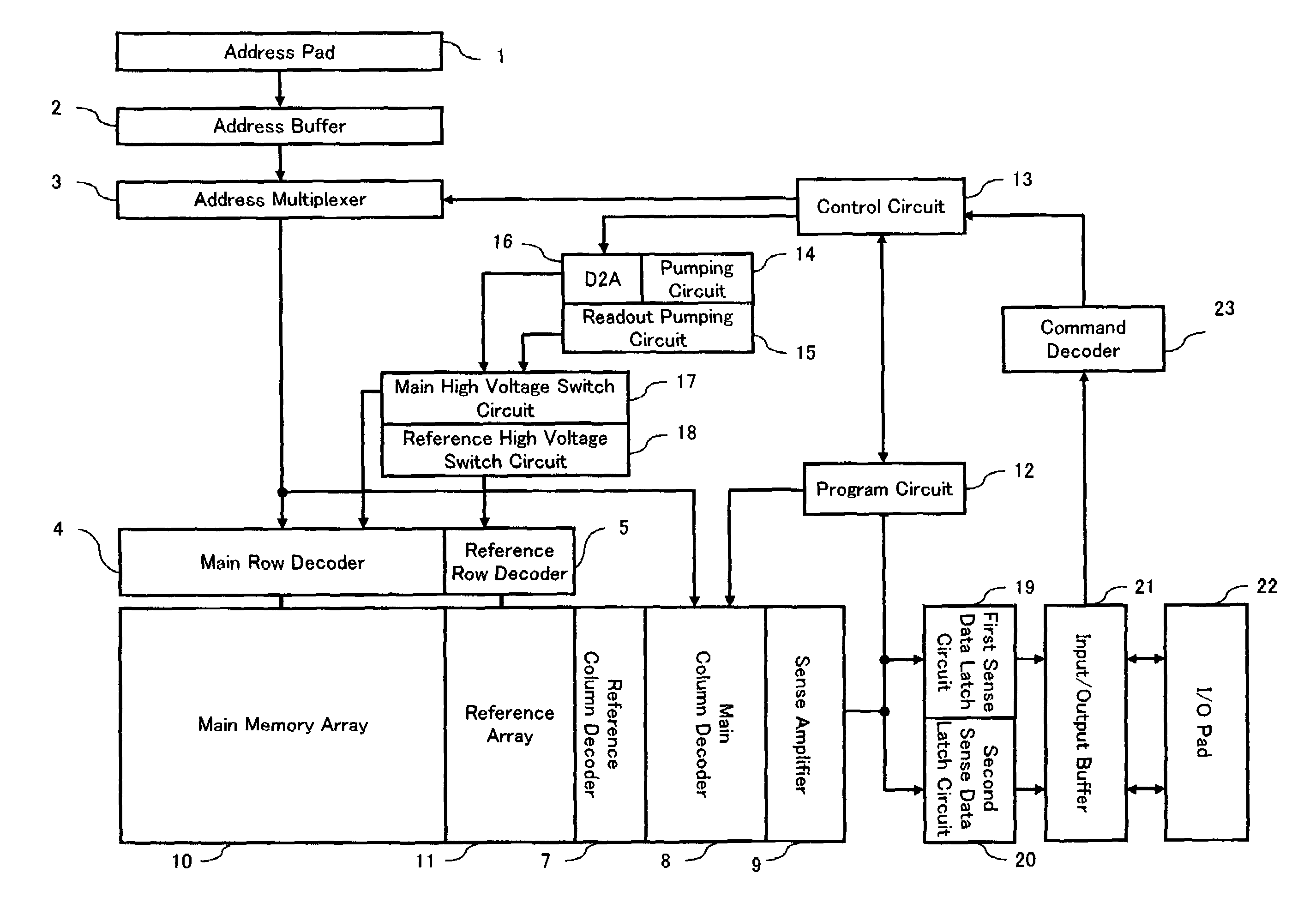

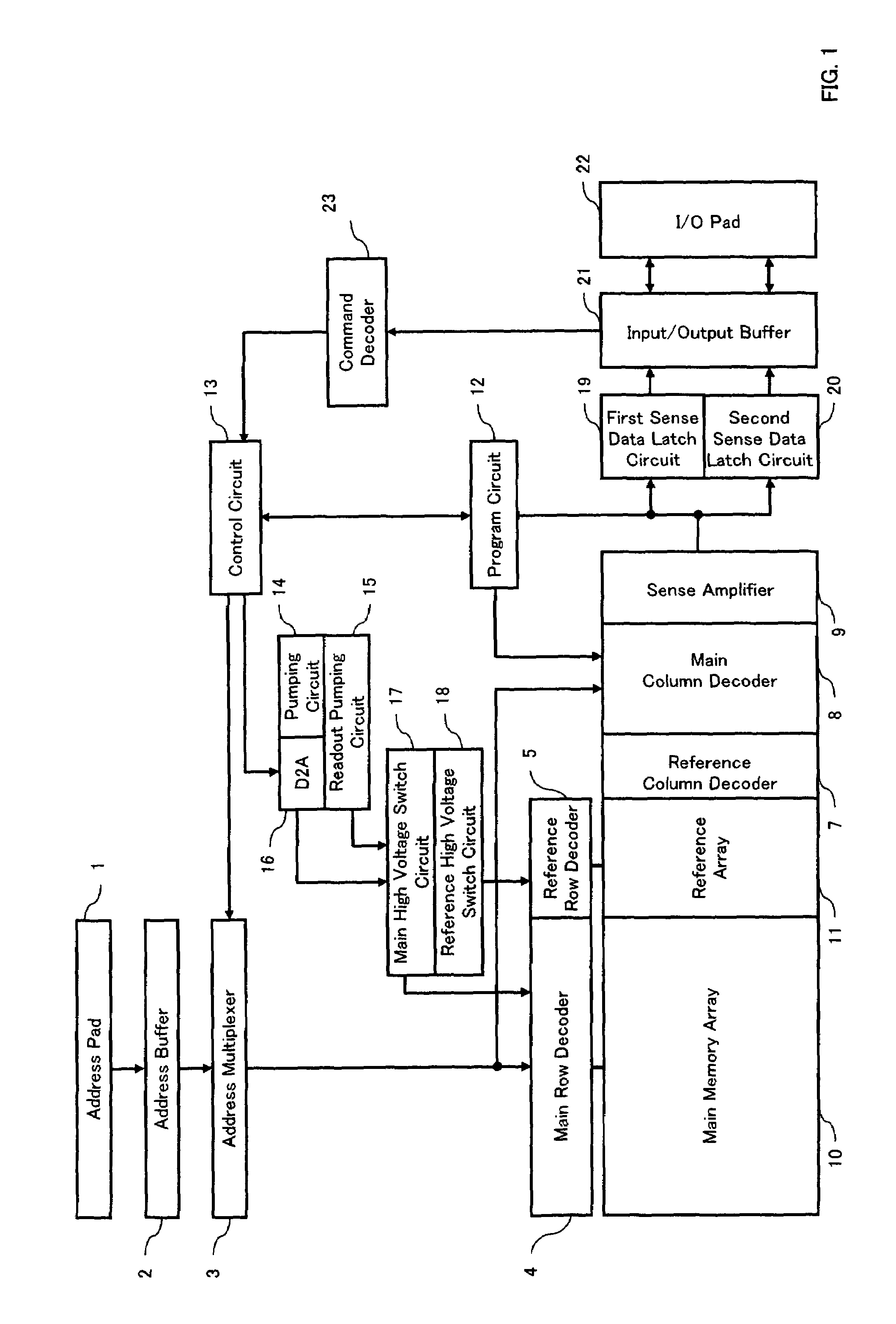

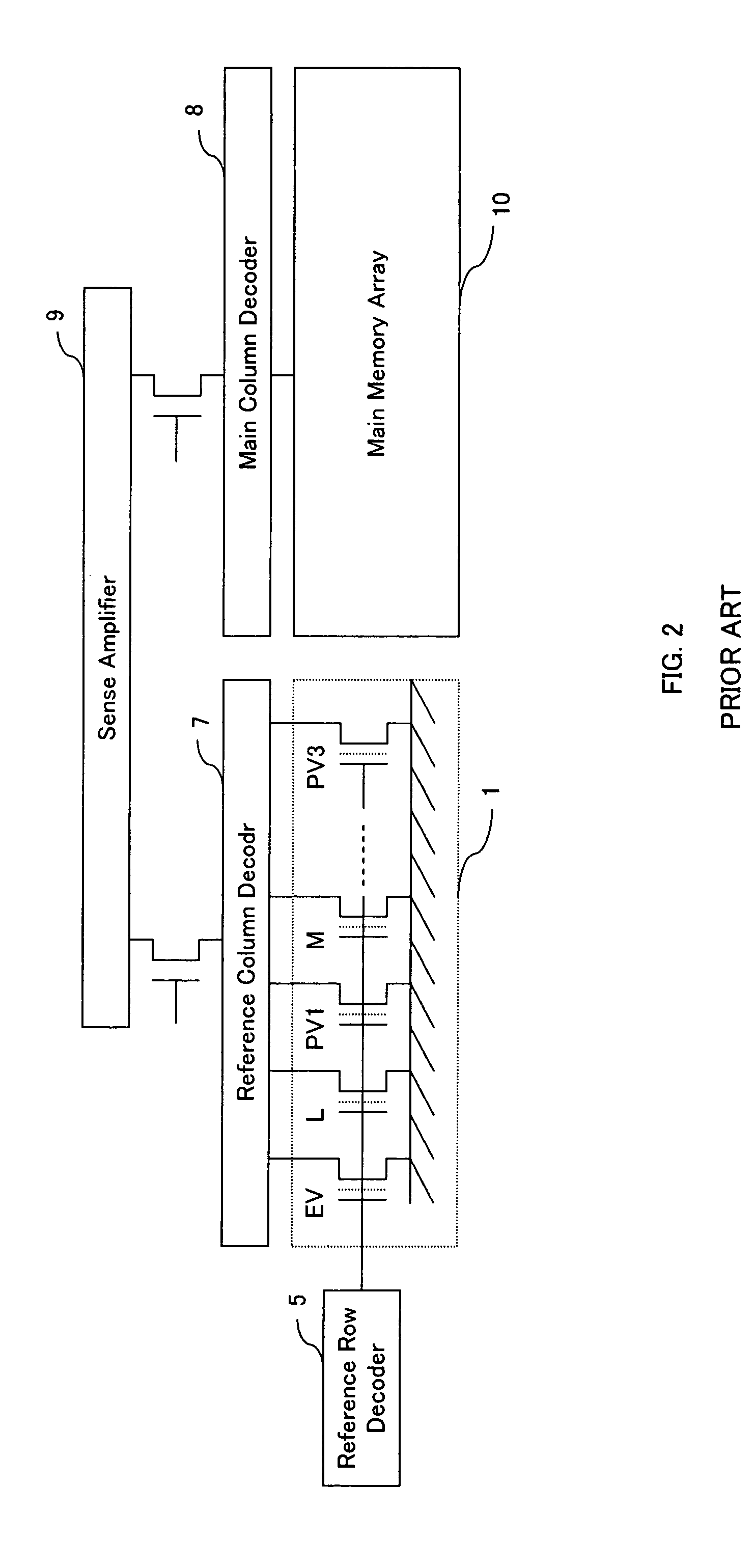

Nonvolatile semiconductor memory device

InactiveUS7020037B2Increase speedHigh-speed performanceFloating sedimentation devicesWater treatment parameter controlHemt circuitsData storing

A nonvolatile semiconductor memory device includes a readout circuit which reads data stored in a selected memory cell by applying predetermined voltage to the selected memory cell and a reference cell such that currents corresponding to the respective threshold voltage may flow, and comparing the current flowing in the selected memory cell with the current flowing in the reference cell. The readout circuit commonly uses the reference cell set in the same storage state for normal readout and for readout for program verification, and when the predetermined voltage is applied to the selected memory cell and the reference memory cell at the time of the readout for the program verification, it sets an applying condition to the reference memory cell such that its storage state may be shifted more in the program state direction than that in an applying condition at the time of the normal readout.

Owner:SHARP KK

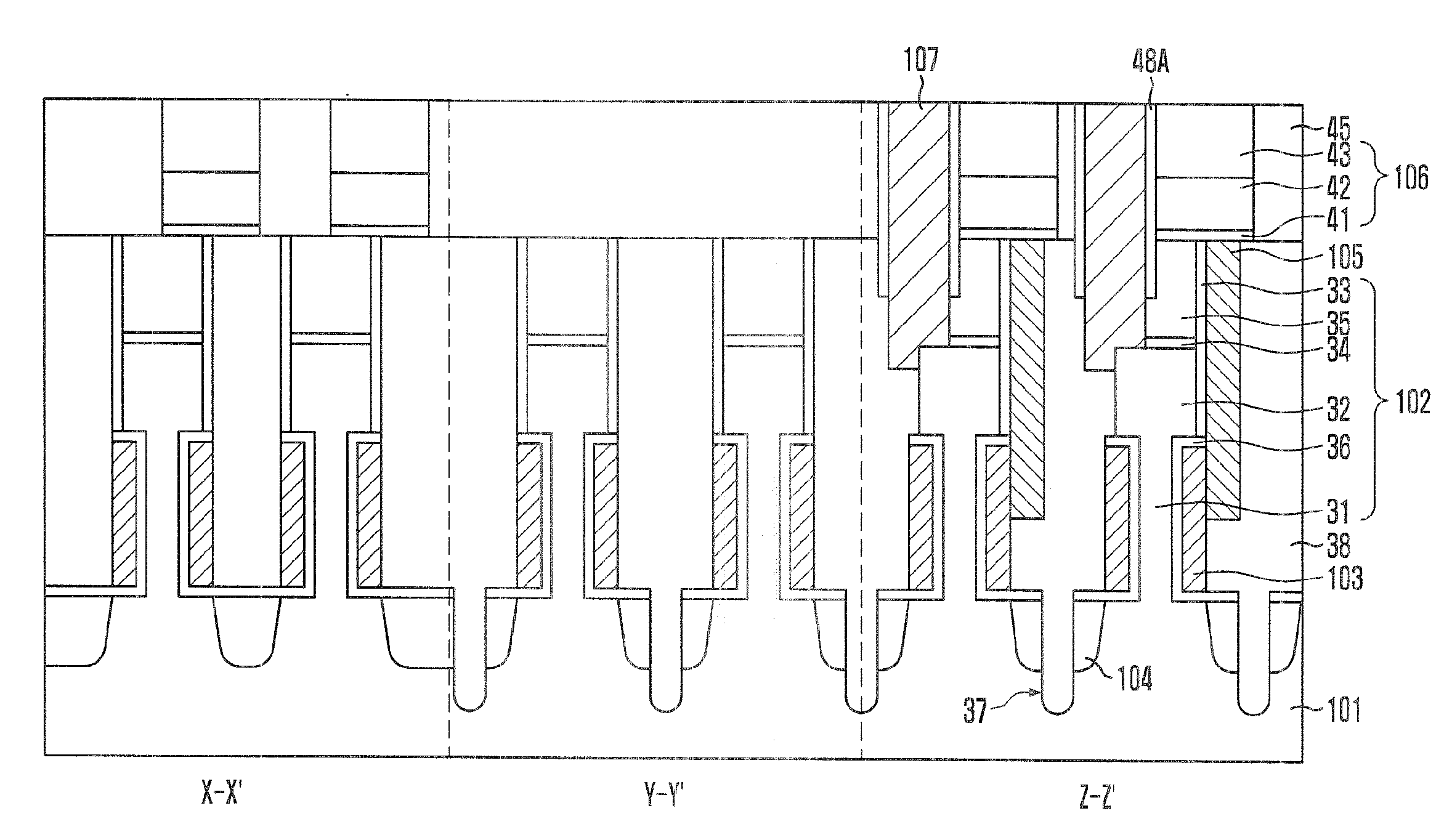

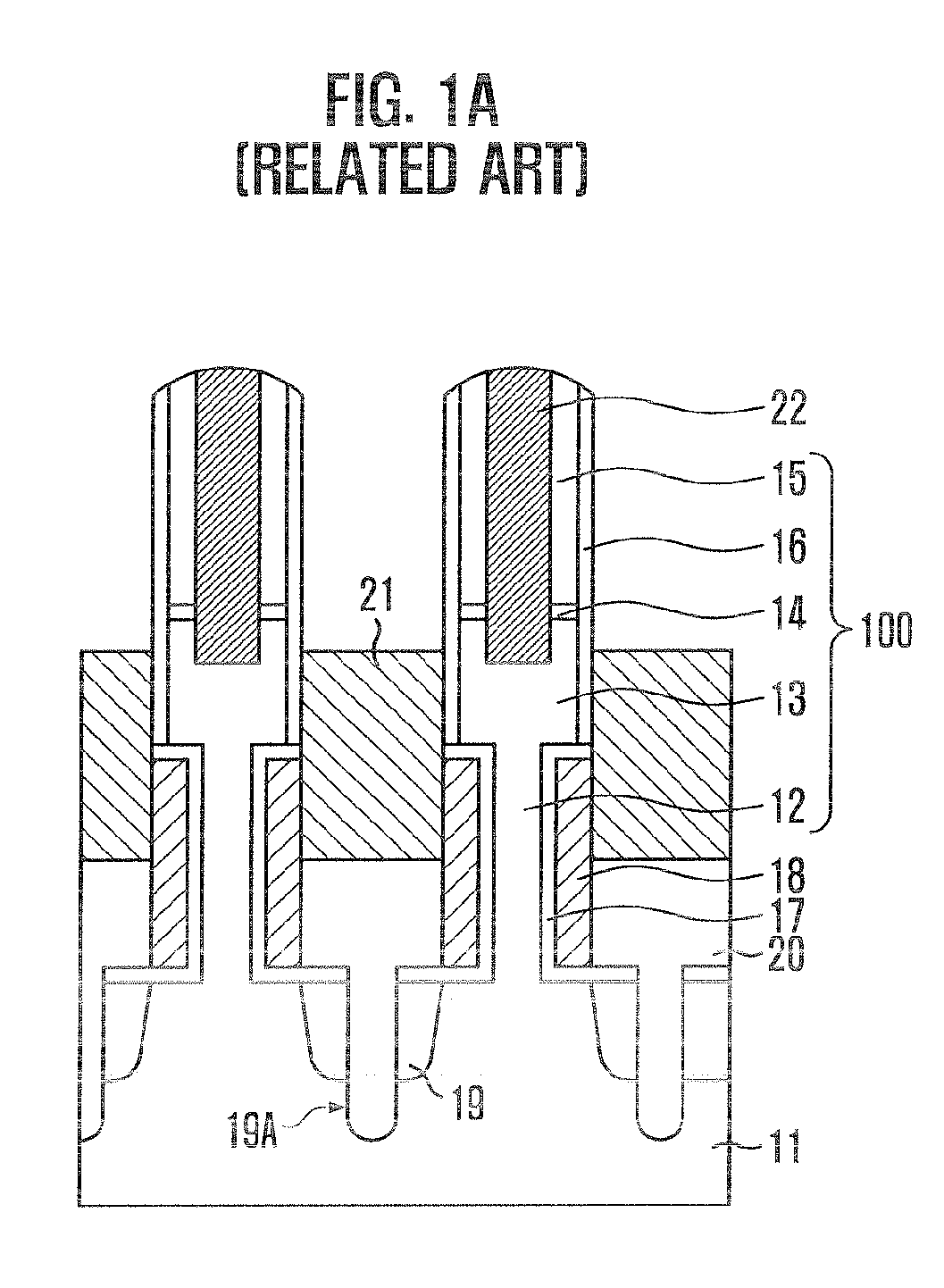

Semiconductor device having vertical channel transistor and method for fabricating the same

InactiveUS20090236656A1High-speed performanceDecrease resistance of word lineTransistorSolid-state devicesDielectricDevice material

A semiconductor device having a substrate; a plurality of pillar structures, wherein each pillar structure includes an active pillar disposed over the substrate; a gate electrode surrounding an outer wall of the active pillar; an interlayer dielectric (ILD) layer insulating adjacent pillar structures; a gate contact penetrating the ILD layer and configured to connect to a sidewall of the gate electrode; and a word line connected to the gate contact.

Owner:SK HYNIX INC

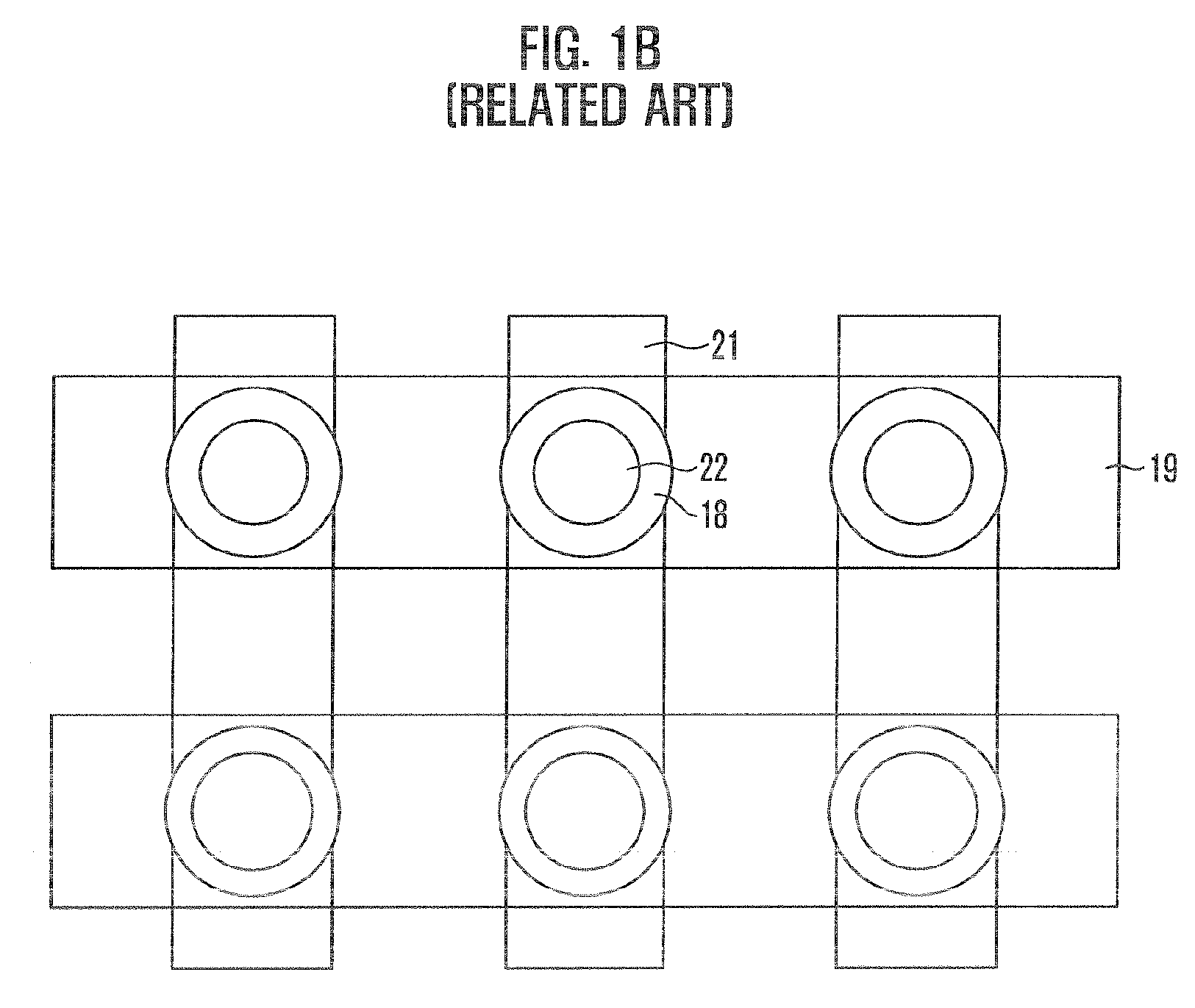

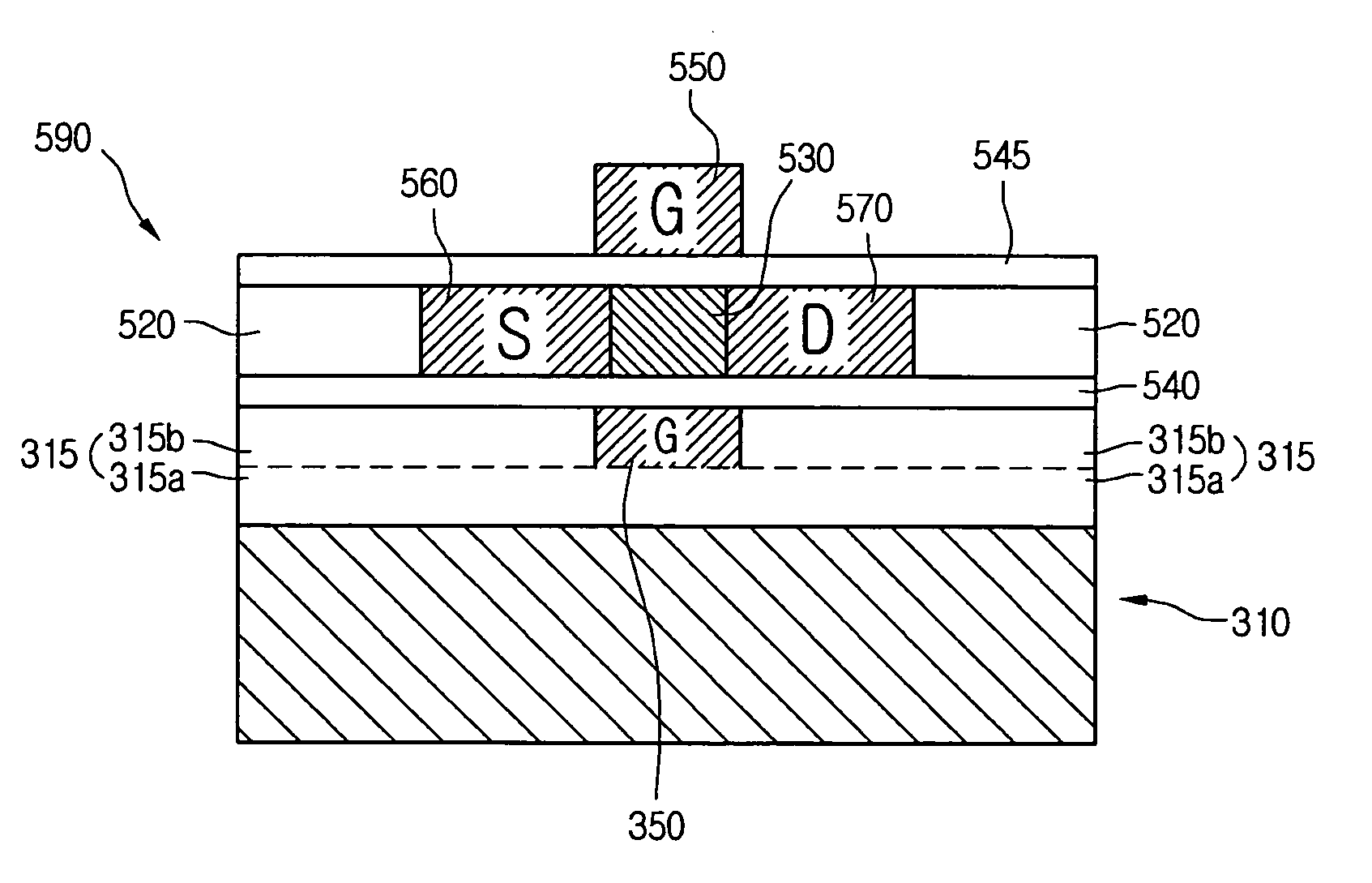

MOS transistor having double gate and manufacturing method thereof

InactiveUS20070120200A1Low power and high-speed performancePrevent parasitic effectTransistorSolid-state devicesDouble gateElectrical and Electronics engineering

There are provided a MOS transistor having a double gate and a manufacturing method thereof. The MOS transistor includes a substrate on which an insulating layer is formed, a first gate embedded in the insulating layer, in which the top surface of the first gate is exposed, a first gate oxide layer formed on the insulating layer and the first gate, a silicon layer formed on the first gate oxide layer, a source region and a drain region formed in the silicon layer to be in contact with the first gate oxide layer, a second gate oxide layer formed on the silicon layer to be in contact with the source and drain regions, and a second gate formed on the second gate oxide layer disposed between the source region and the drain region.

Owner:DONGBU ELECTRONICS CO LTD