Patents

Literature

51 results about "Dead layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The dead layer is a traditional oil painting technique where the artist builds up the higher tonal values of the painting by adding white over the underpainting.

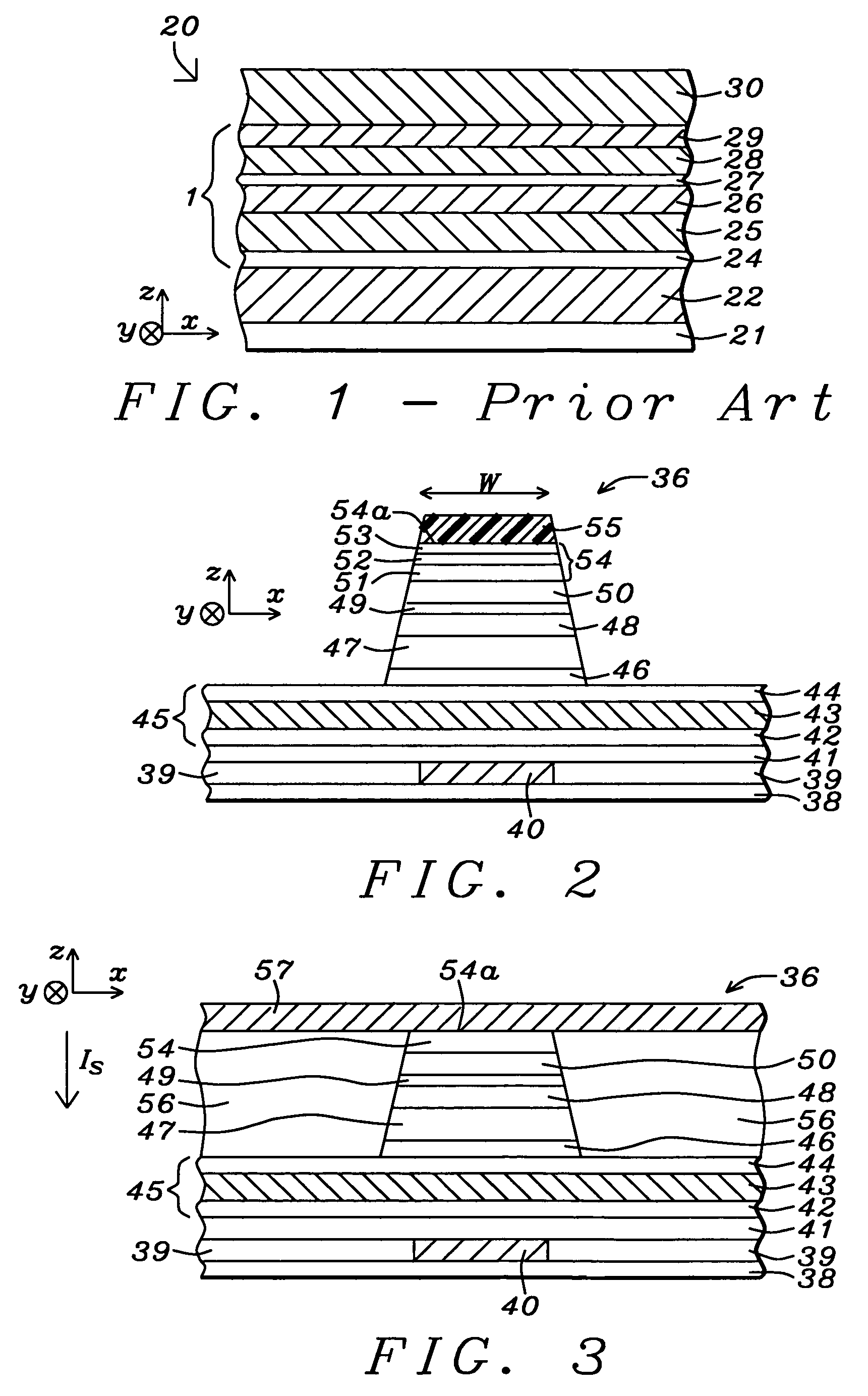

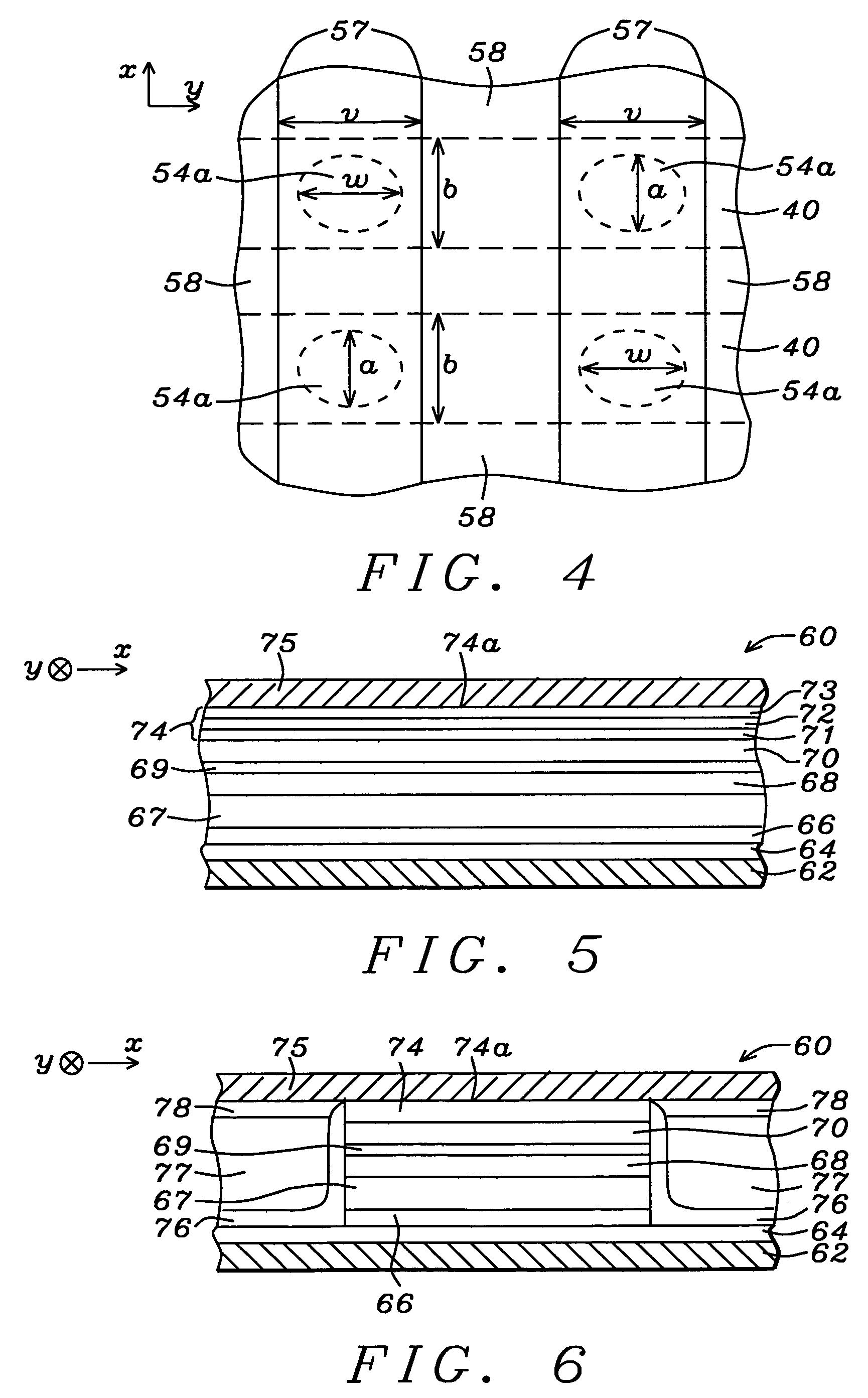

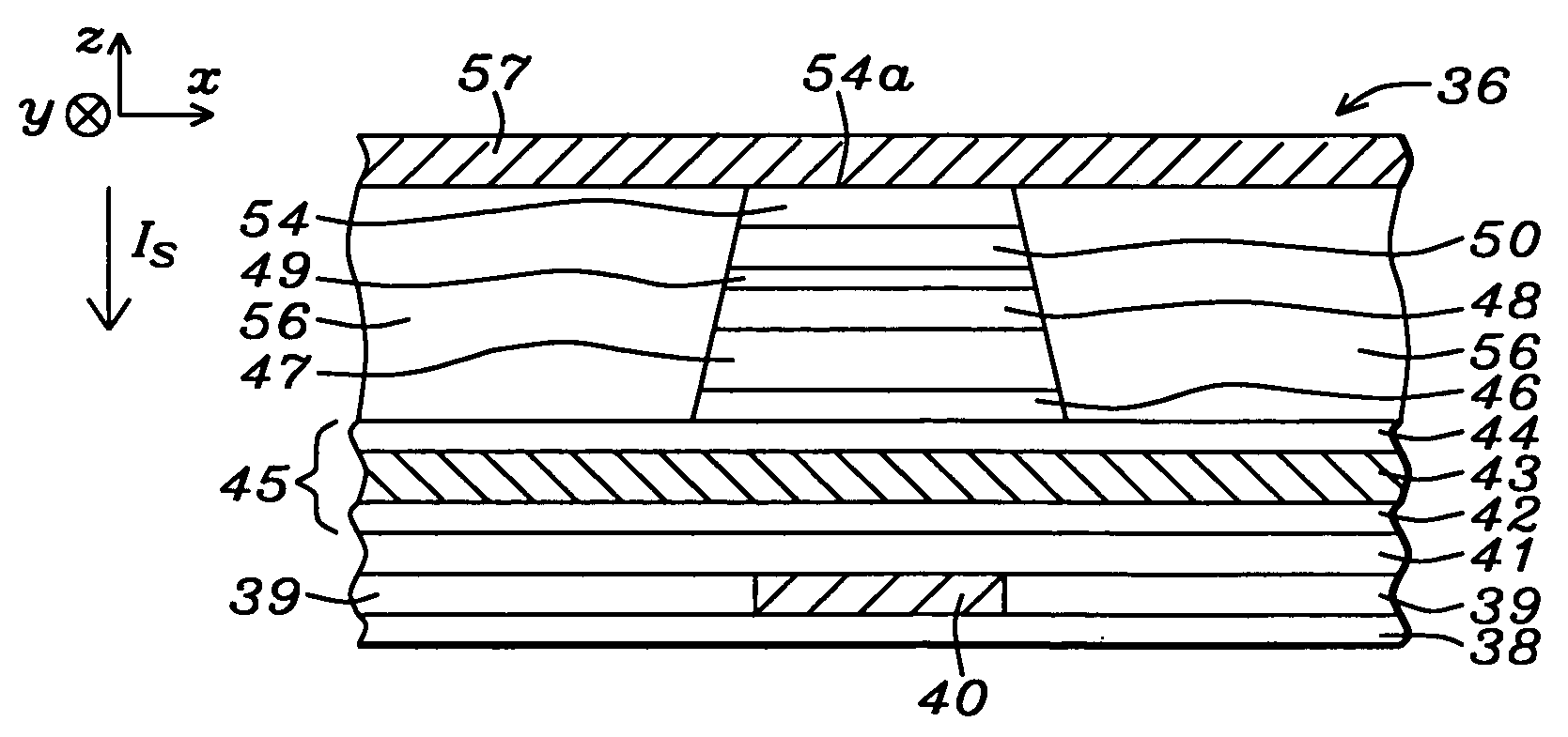

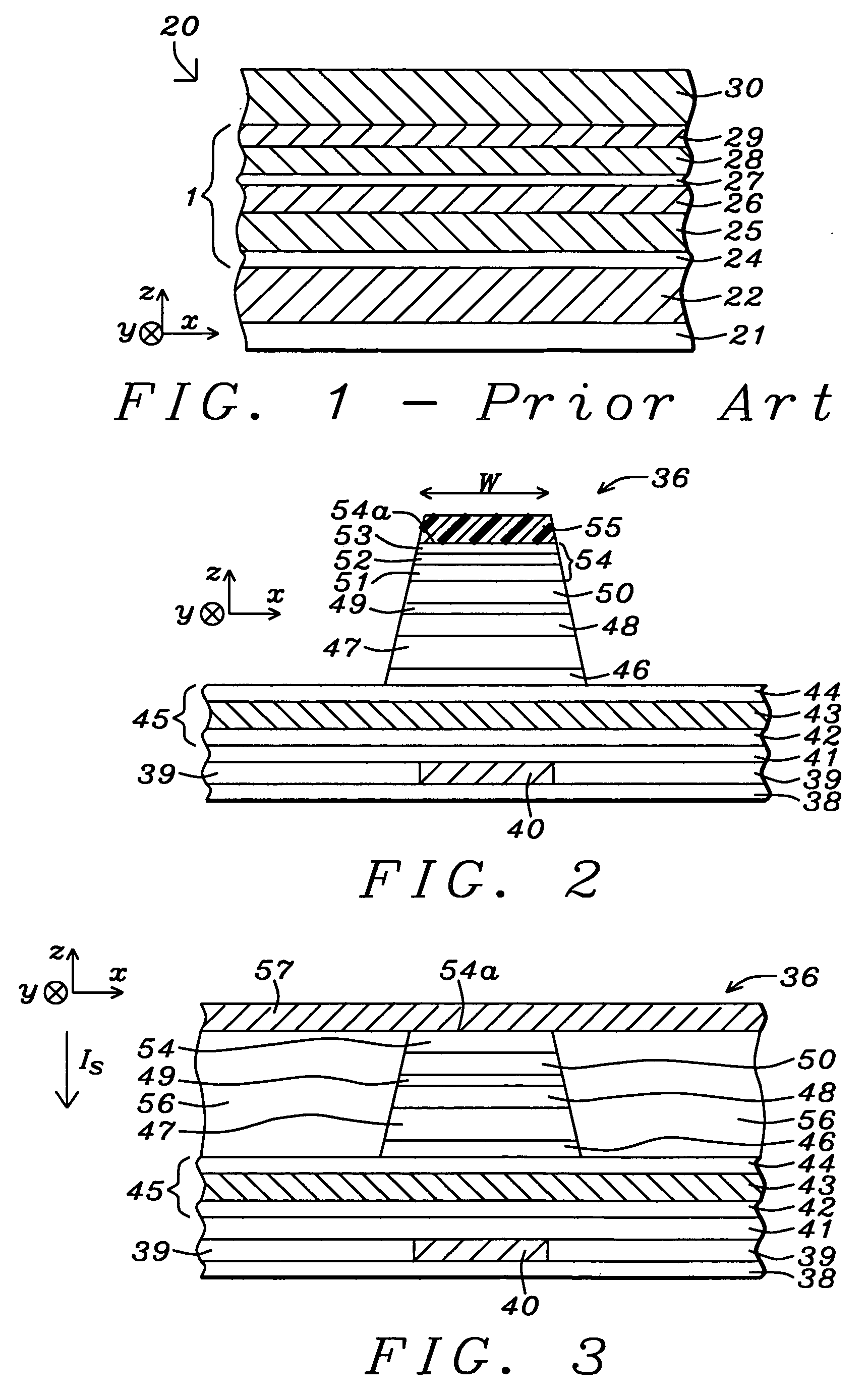

Novel magnetic tunnel junction (MTJ) to reduce spin transfer magnetization switching current

ActiveUS20080179699A1Reduce magnetic “ dead layer ”Magnetic-field-controlled resistorsSolid-state devicesLayer interfaceSpins

Owner:TAIWAN SEMICON MFG CO LTD

Capping layer for a magnetic tunnel junction device to enhance dR/R and a method of making the same

An MTJ in an MRAM array or TMR read head is disclosed in which a low magnetization capping layer is a composite having a NiFeHf inner layer formed on a NiFe or CoFeB / NiFe free layer, a Ta middle layer, and a Ru outer layer on the Ta layer. For example, a low magnetization NiFeHf layer is achieved by co-sputtering NiFe and Hf targets with a forward power of 400 W and 200 W, respectively. A higher Hf content increases the oxygen gettering power of the NiFeHf layer and the thickness is modified to change dR / R, RA, and magnetostriction values. A so-called dead layer between the free layer and capping layer is restored by incorporating a NiFeHf layer on the free layer to improve lattice matching. The Fe content in the NiFe target used to make the NiFeHf layer is preferably the same as in the NiFe free layer.

Owner:TAIWAN SEMICON MFG CO LTD

Novel capping layer for a magnetic tunnel junction device to enhance dR/R and a method of making the same

ActiveUS20080023740A1Magnetization is so lowLow layerNanomagnetismSolid-state devicesSputteringMagnetization

An MTJ in an MRAM array or TMR read head is disclosed in which a low magnetization capping layer is a composite having a NiFeHf inner layer formed on a NiFe or CoFeB / NiFe free layer, a Ta middle layer, and a Ru outer layer on the Ta layer. For example, a low magnetization NiFeHf layer is achieved by co-sputtering NiFe and Hf targets with a forward power of 400 W and 200 W, respectively. A higher Hf content increases the oxygen gettering power of the NiFeHf layer and the thickness is modified to change dR / R, RA, and magnetostriction values. A so-called dead layer between the free layer and capping layer is restored by incorporating a NiFeHf layer on the free layer to improve lattice matching. The Fe content in the NiFe target used to make the NiFeHf layer is preferably the same as in the NiFe free layer.

Owner:TAIWAN SEMICON MFG CO LTD

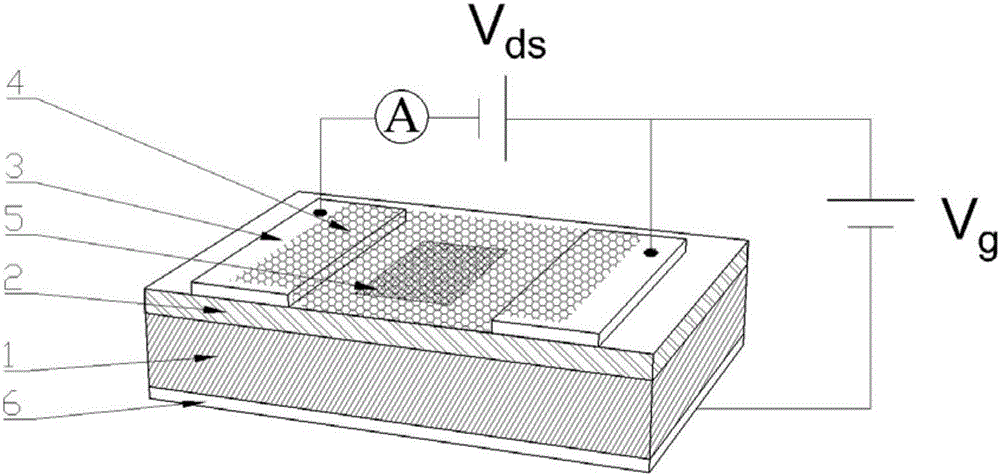

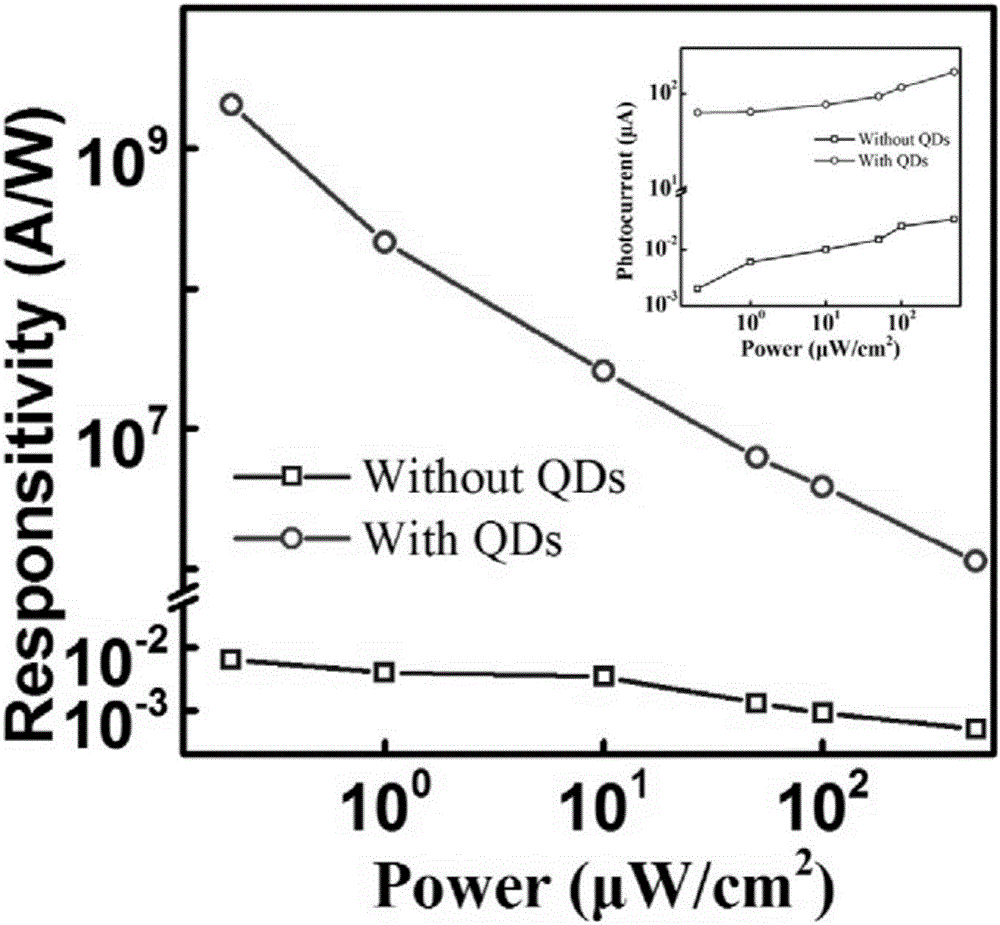

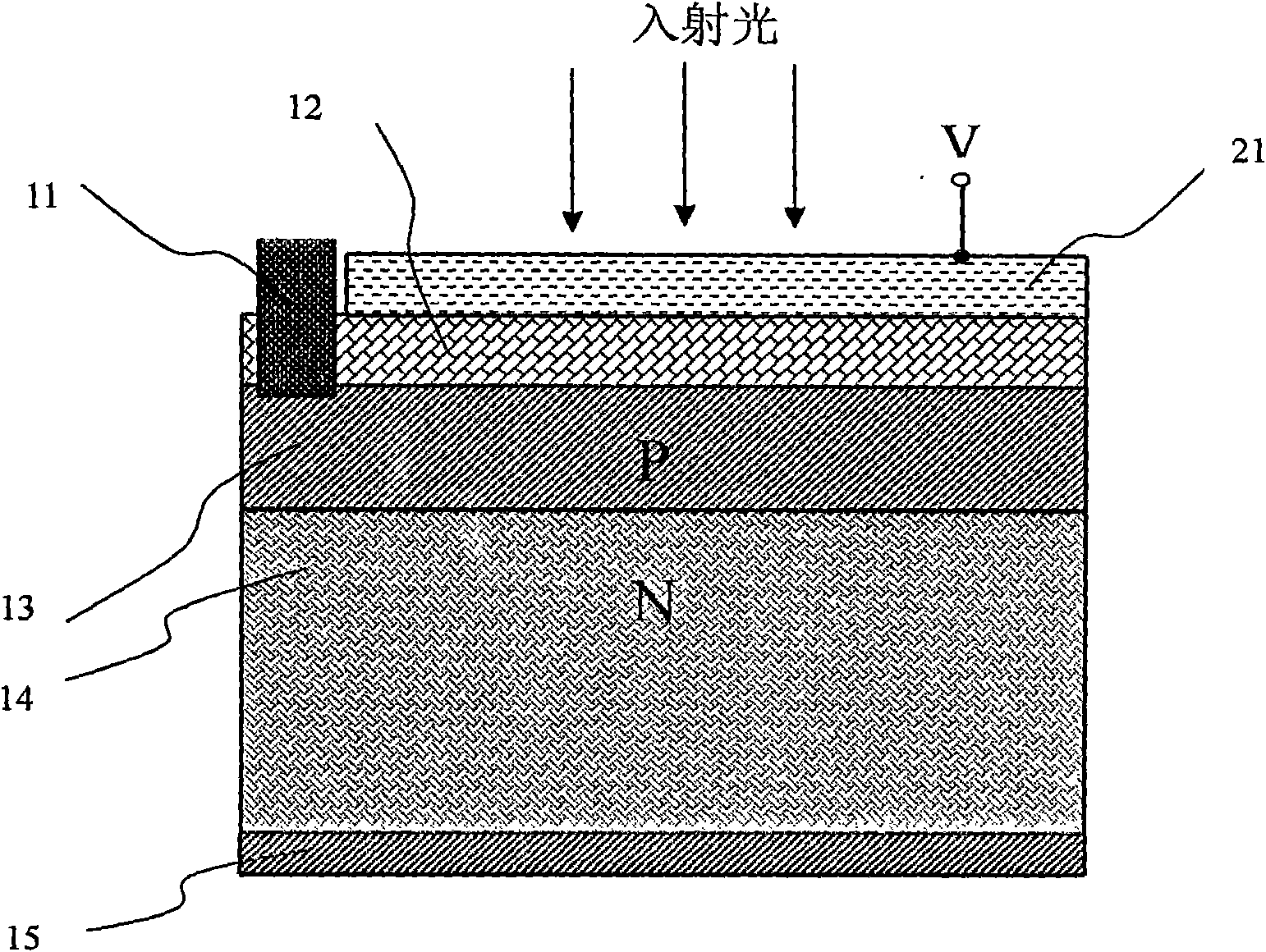

Photoconductive detector based on boron-doped silicon quantum dot/graphene/silicon dioxide and preparation method thereof

ActiveCN106601857ALarge light signal currentHigh gainFinal product manufactureSemiconductor devicesPhotoconductive detectorP type silicon

Owner:ZHEJIANG UNIV

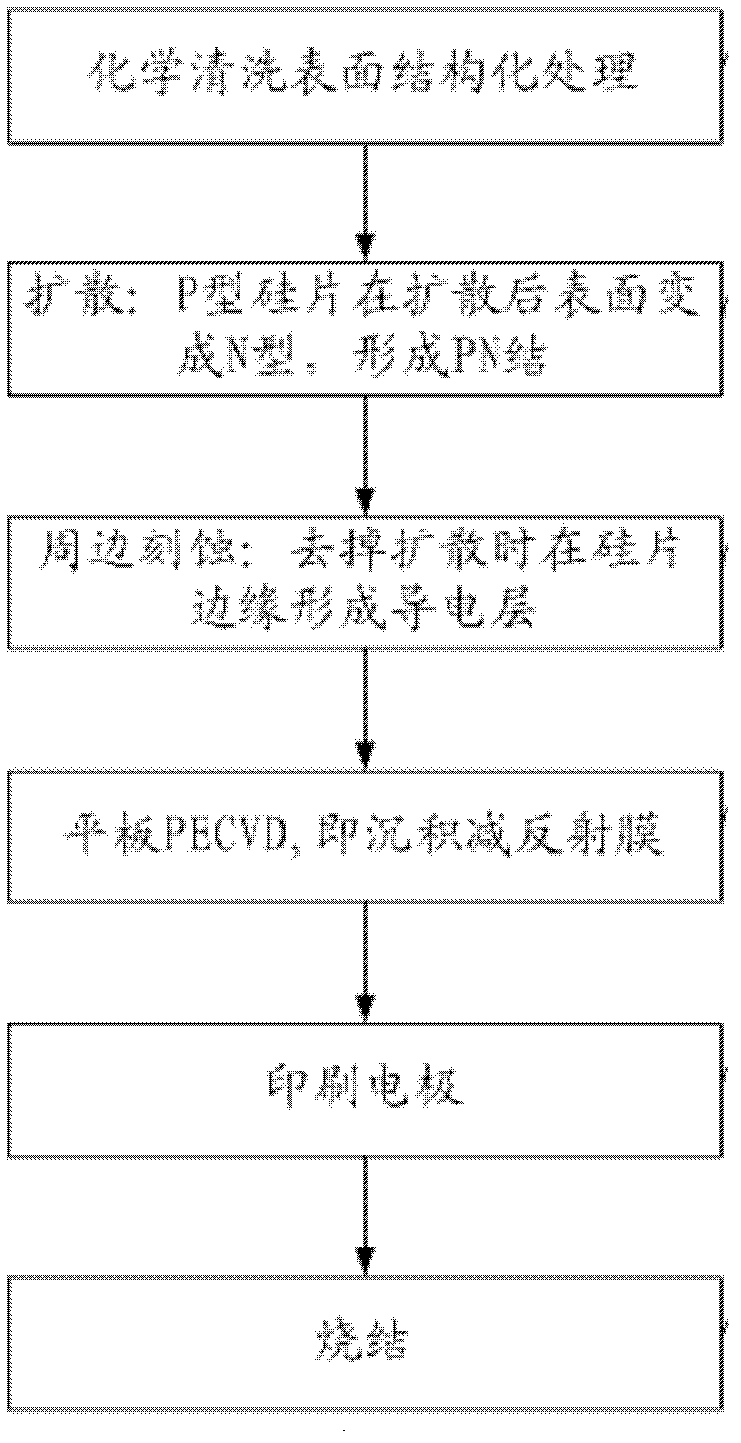

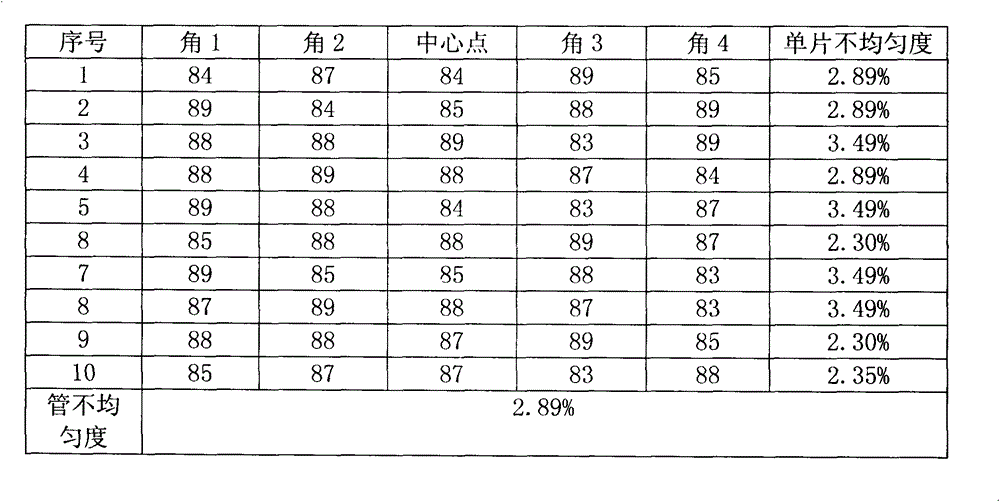

Phosphorus gettering process of silicon chip

InactiveCN101667605AImprove electrical performance parametersIncreased average life expectancyFinal product manufactureSemiconductor devicesEtchingSurface oxidation

The invention relates to a phosphorus gettering process of silicon chips in the manufacture of solar cells, which comprises the following steps: putting sueded silicon chips into a diffusion furnace for pre-deposition, removing a phosphorosilicate glass layer after diffusion, soaking the silicon chips through distributed processing in a hydrofluoric acid solution, and removing oxide layers from the surfaces of the silicon chips; then putting the silicon chips after washing into the diffusion furnace for secondary diffusion processing, taking the silicon chips out from the diffusion furnace after the processing of the secondary diffusion working procedure, cooling the silicon chips to room temperature, and measuring the square resistance of the silicon chips. The invention can effectively decrease heavily doped 'dead layers' and greatly prolong the average minority carrier lifetime of the silicon chips; after the processes including etching, PECVD, silk screen sintering and the like arefinished according to the normal process of a cell chip, the average transformation efficiency of the made cell chip is further improved, and the cell chip has better electrical performance parameters.

Owner:无锡尚品太阳能电力科技有限公司

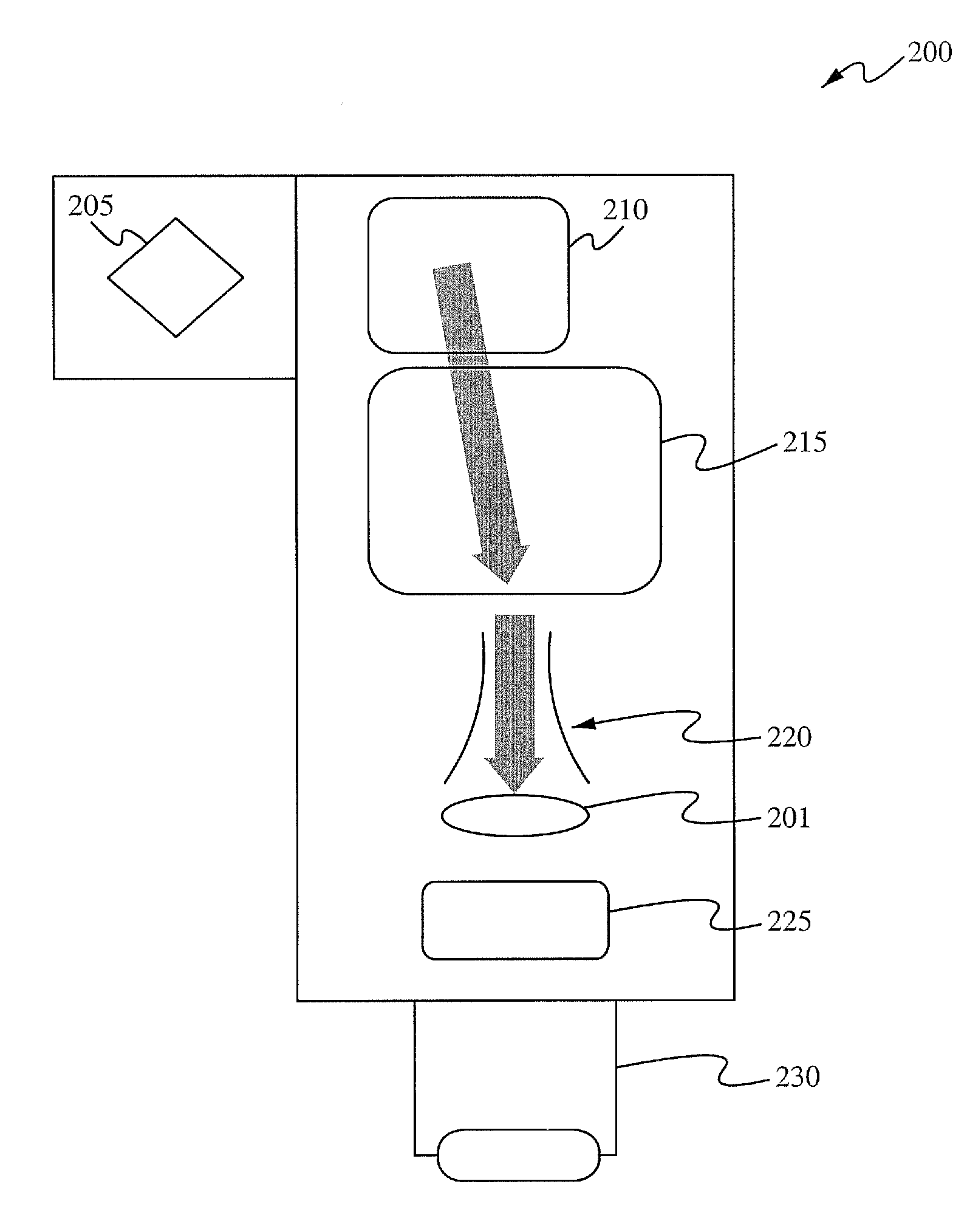

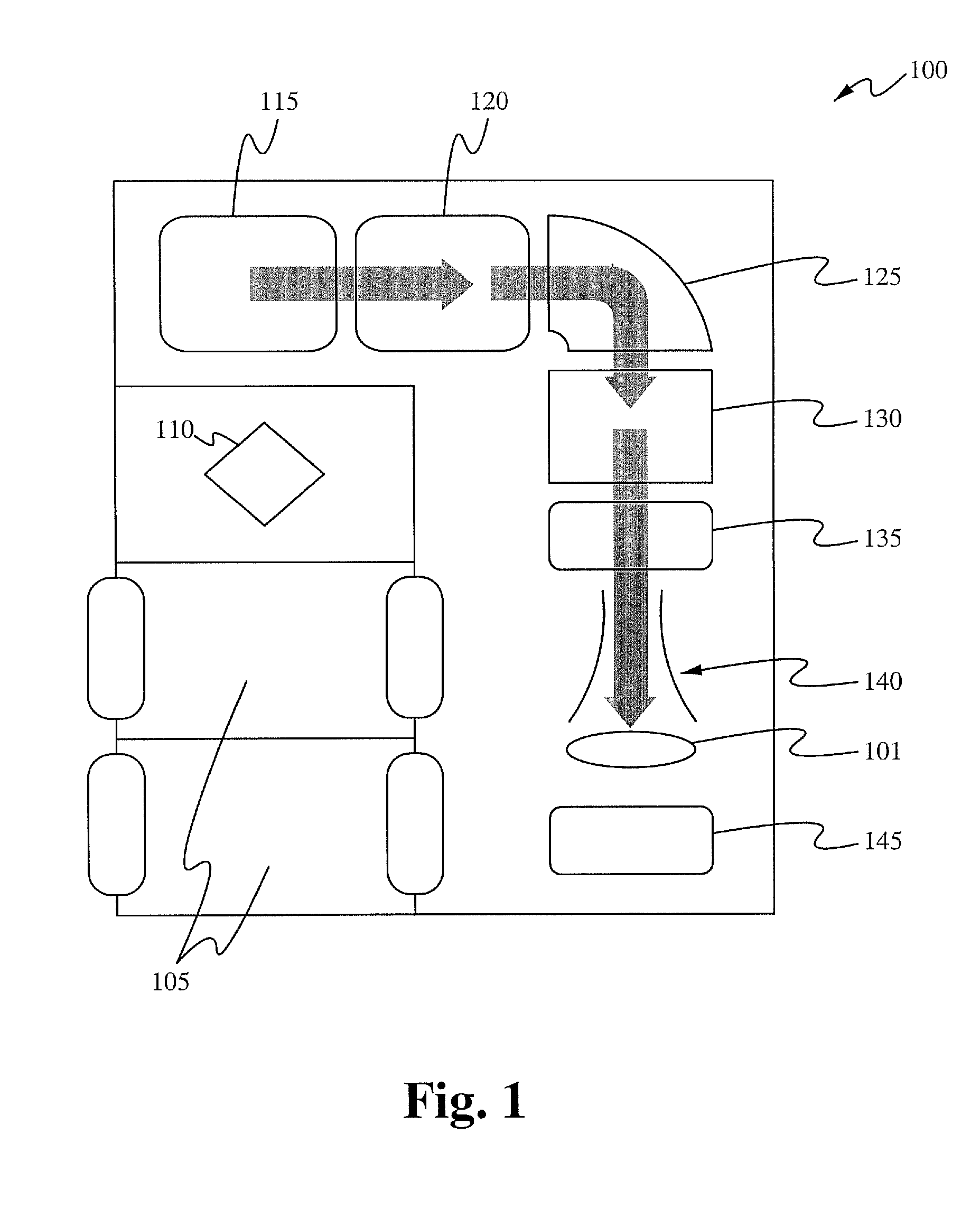

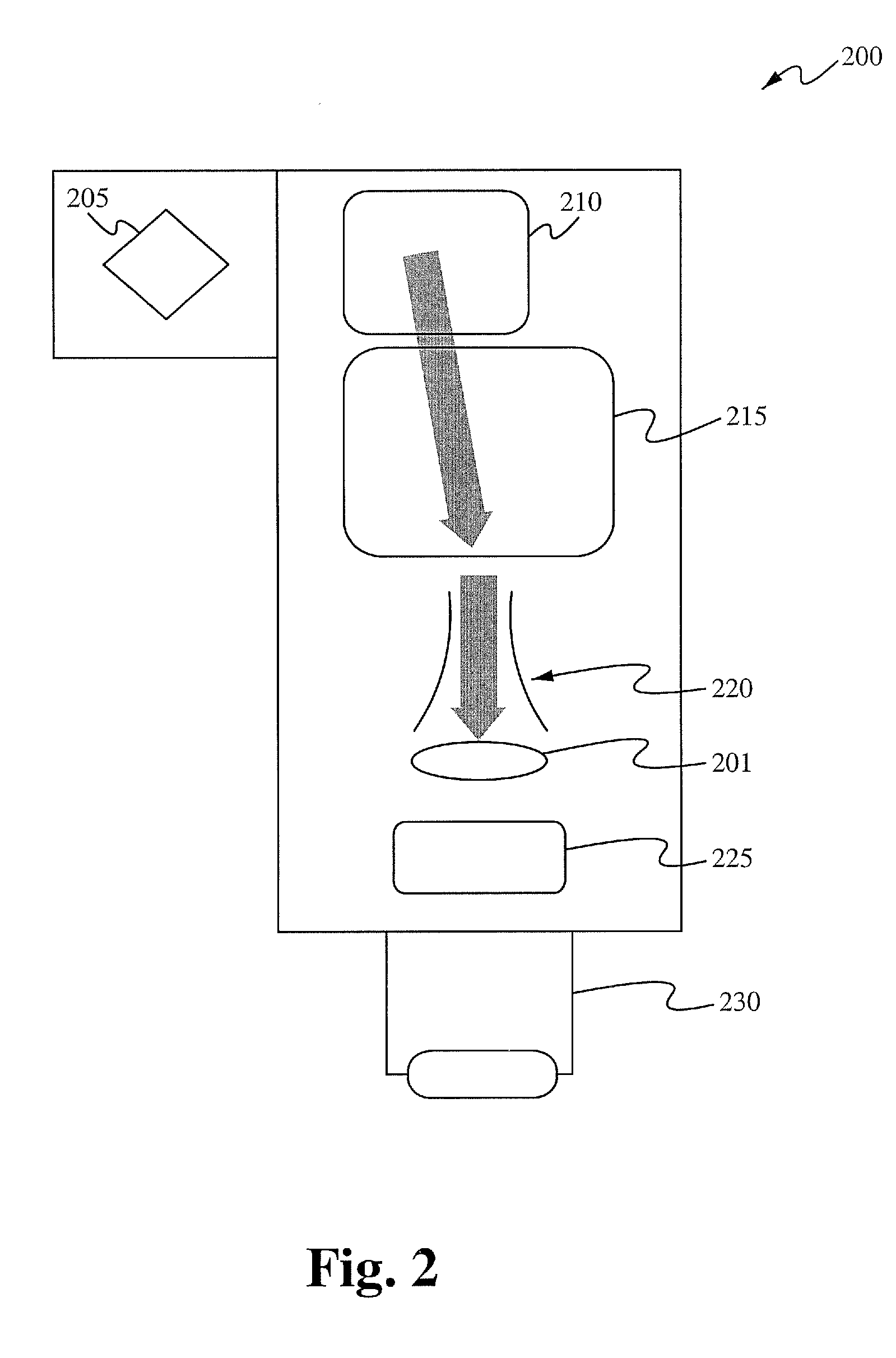

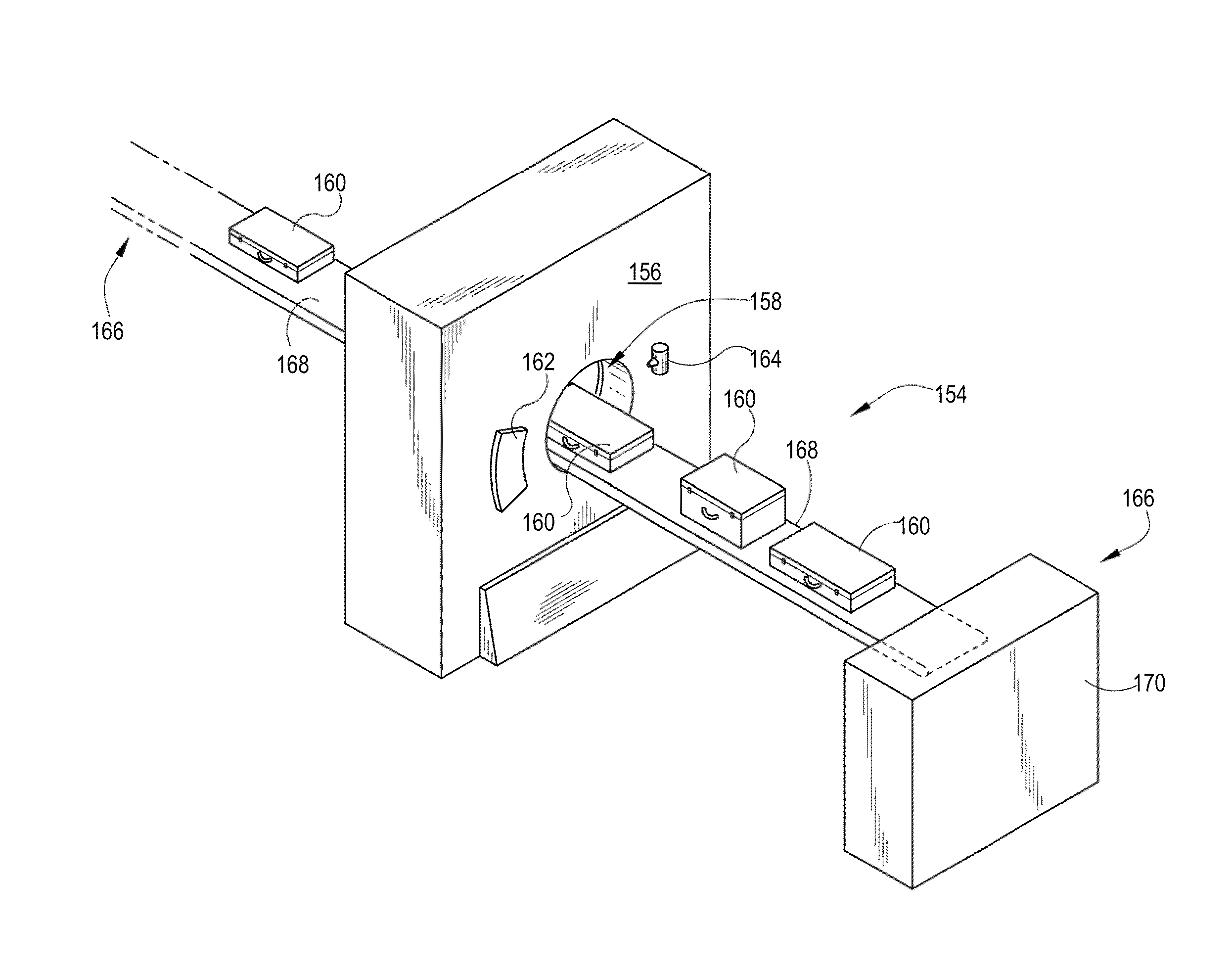

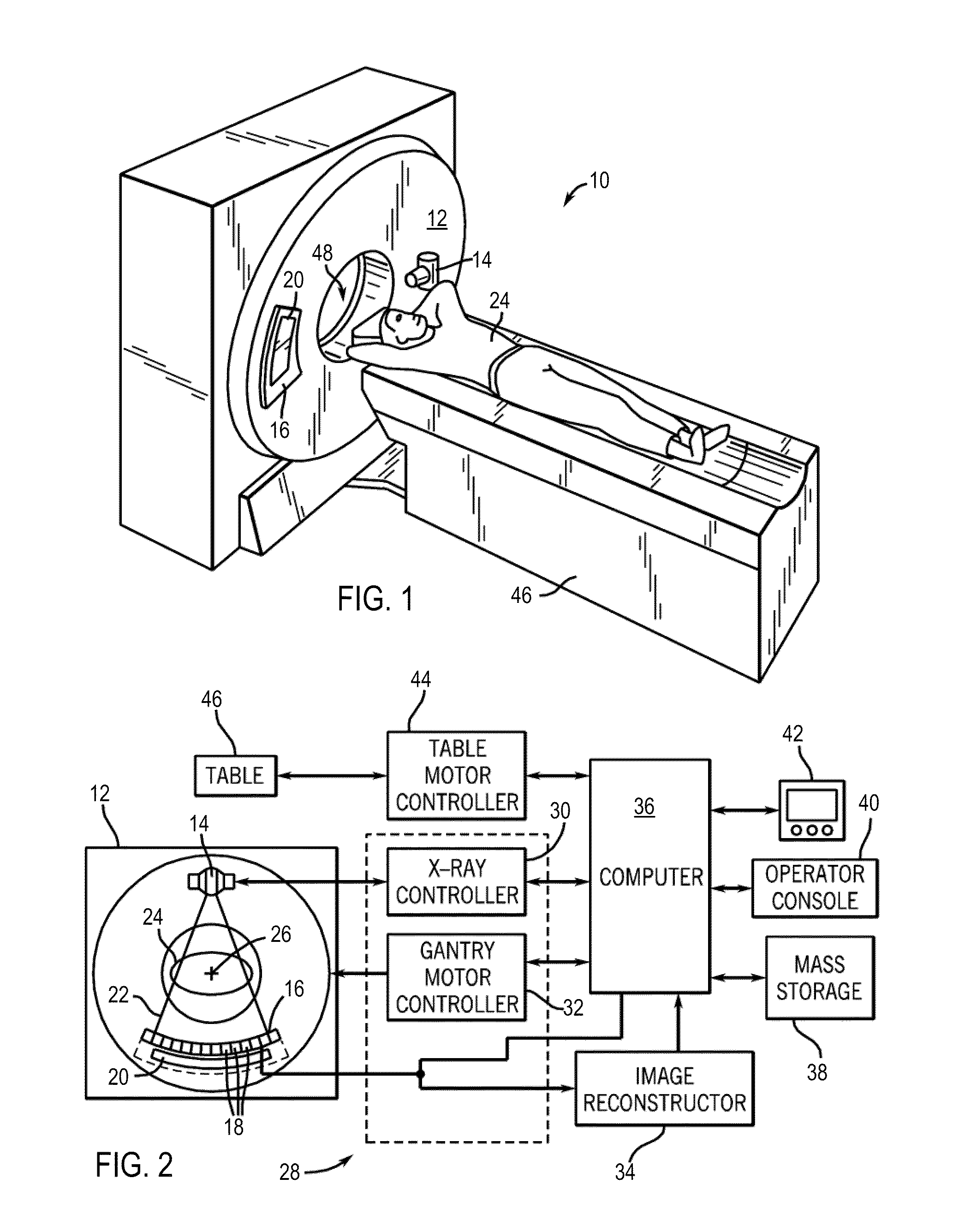

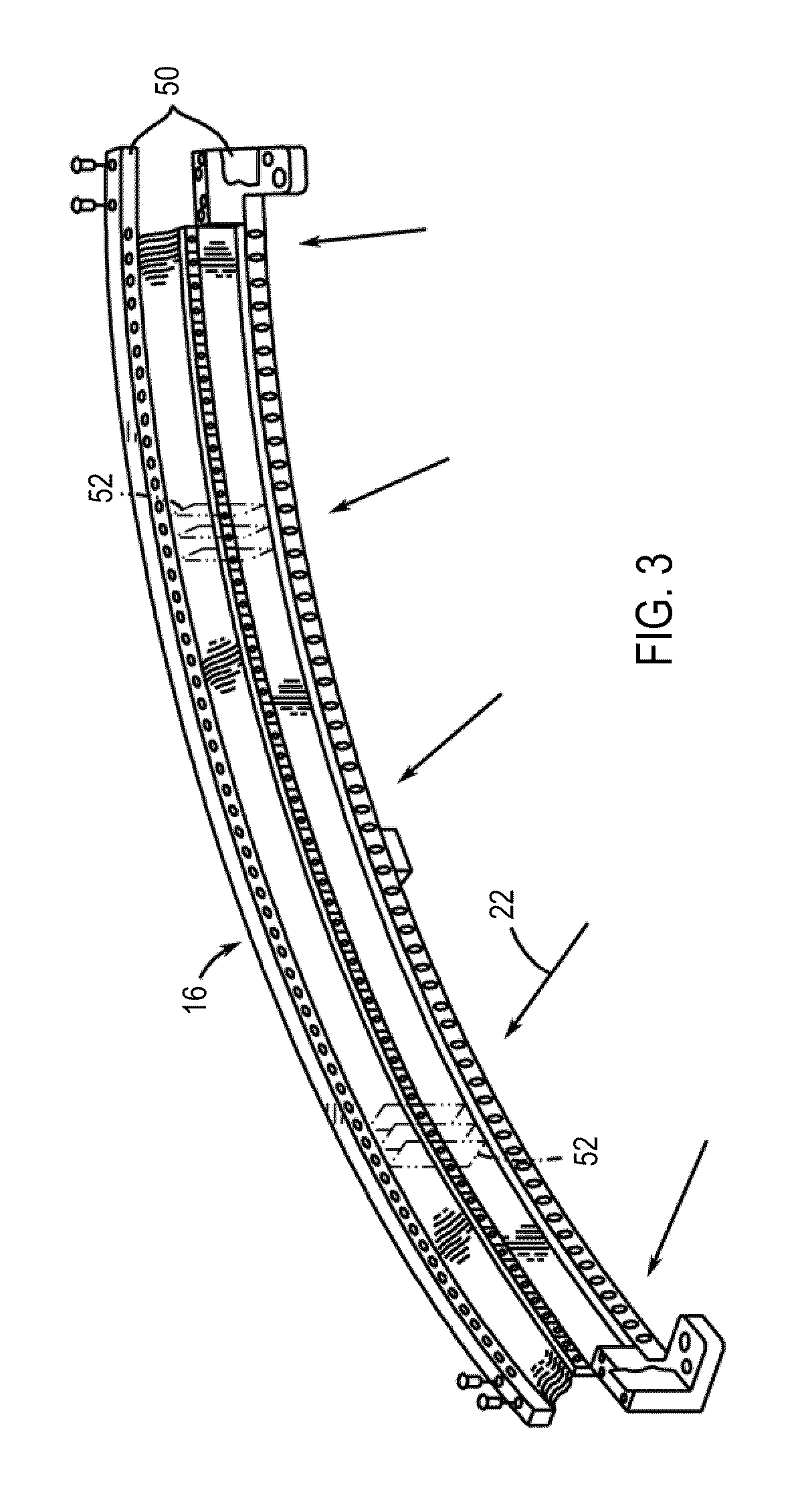

Application specific implant system and method for use in solar cell fabrications

ActiveUS20090309039A1Stability-of-path spectrometersBeam/ray focussing/reflecting arrangementsSolar cellSingle ion

Solar cells and other semiconductor devices are fabricated more efficiently and for less cost using an implanted doping fabrication system. A system for implanting a semiconductor substrate includes an ion source (such as a single-species delivery module), an accelerator to generate from the ion source an ion beam having an energy of no more than 150 kV, and a beam director to expose the substrate to the beam. In one embodiment, the ion source is single-species delivery module that includes a single-gas delivery element and a single-ion source. Alternatively, the ion source is a plasma source used to generate a plasma beam. The system is used to fabricate solar cells having lightly doped photo-receptive regions and more highly doped grid lines. This structure reduces the formation of “dead layers” and improves the contact resistance, thereby increasing the efficiency of a solar cell.

Owner:INTEVAC

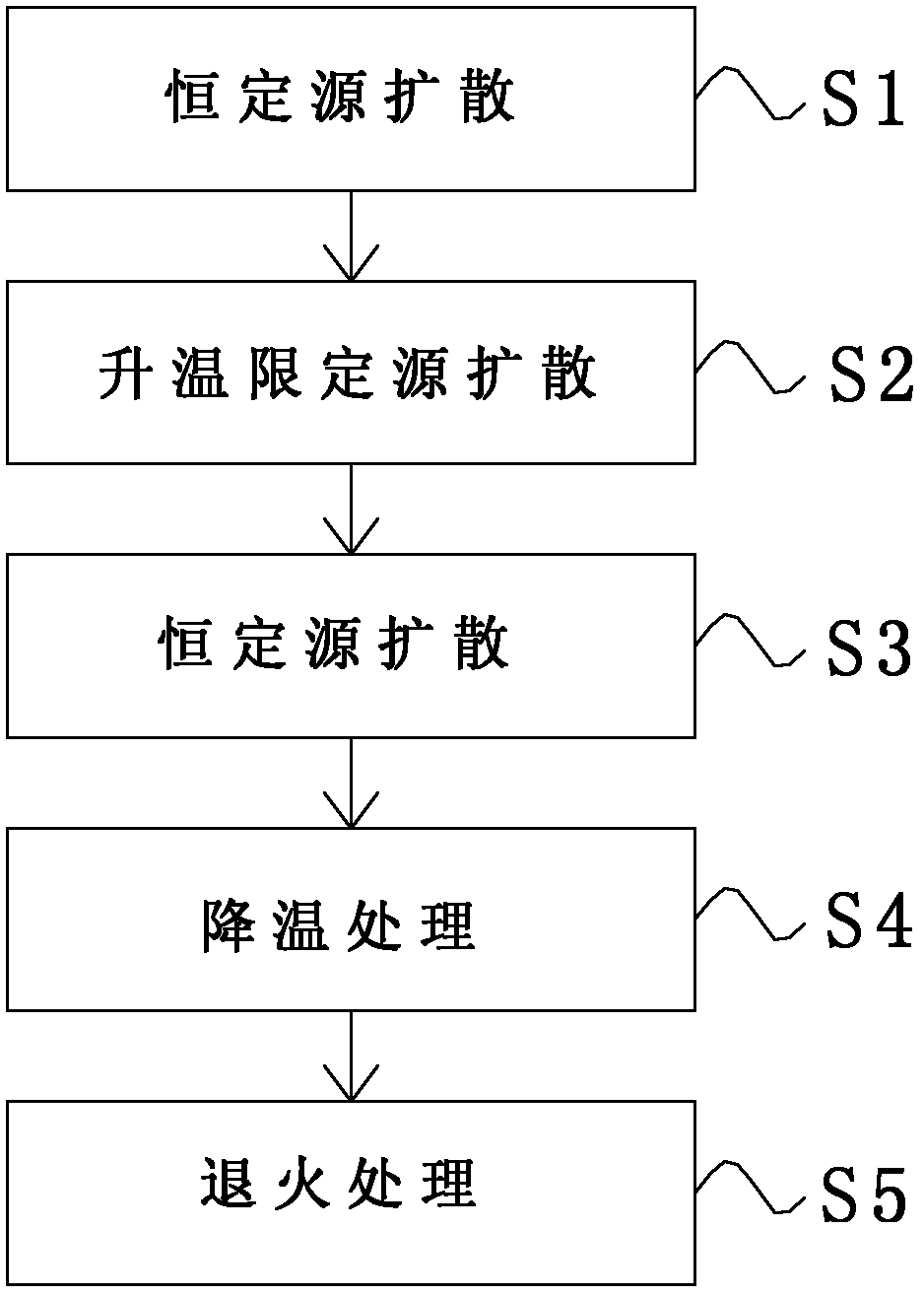

Solar cell homogenizing annealing process

InactiveCN102810598AReduce heat damageImprove conversion efficiencyFinal product manufactureSemiconductor devicesElectricityElectron hole

The invention relates to a solar cell homogenizing annealing process which includes the steps of pre-oxidation, constant-temperature predeposition, main diffusion variable-temperature propelling, cooling, annealing, boat returning and the like. Crystal lattices are repaired by means of constant-temperature annealing to reduce thermal defects caused by high-temperature diffusion, reduce electricity leakage and promote Uoc and Isc. Further, secondary propelling can be achieved by means of the annealing process to further reduce 'dead layers', activate phosphorus atoms and improve carrier (electron-hole pair) density, and cell conversion efficiency can be finally improved by more than 2%-3%.

Owner:JIANGSU SHUNFENG PHOTOVOLTAIC TECH CO LTD

Method for preparing selective emitter by one-time diffusion

InactiveCN101794845ALow deposition temperatureLow costFinal product manufactureSemiconductor devicesDeposition temperatureMetallic electrode

The invention relates to the technical field of production methods of solar cells, in particular to a method for preparing a selective emitter by one-time diffusion, which sequentially comprises the following process steps: making texture on a silicon wafer, carrying out uniform heavy diffusion, depositing silicon nitride film on the surface of the silicon wafer after diffusing, and printing corrosive slurry in a non-metallic electrode region of the silicon wafer so as to etch the silicon nitride film; and finally, etching the silicon in the non-metallic electrode region with an acid solution or alkali solution to obtain a shallow diffusion region, and the electrode region being a heavy diffusion region. The heavy diffusion process can achieve double-sided gettering, the deposition temperature of the silicon nitride film is low, the whole process is simple and easy to control, the surface is not damaged and has no dead layer, and the cost is low.

Owner:TRINA SOLAR CO LTD

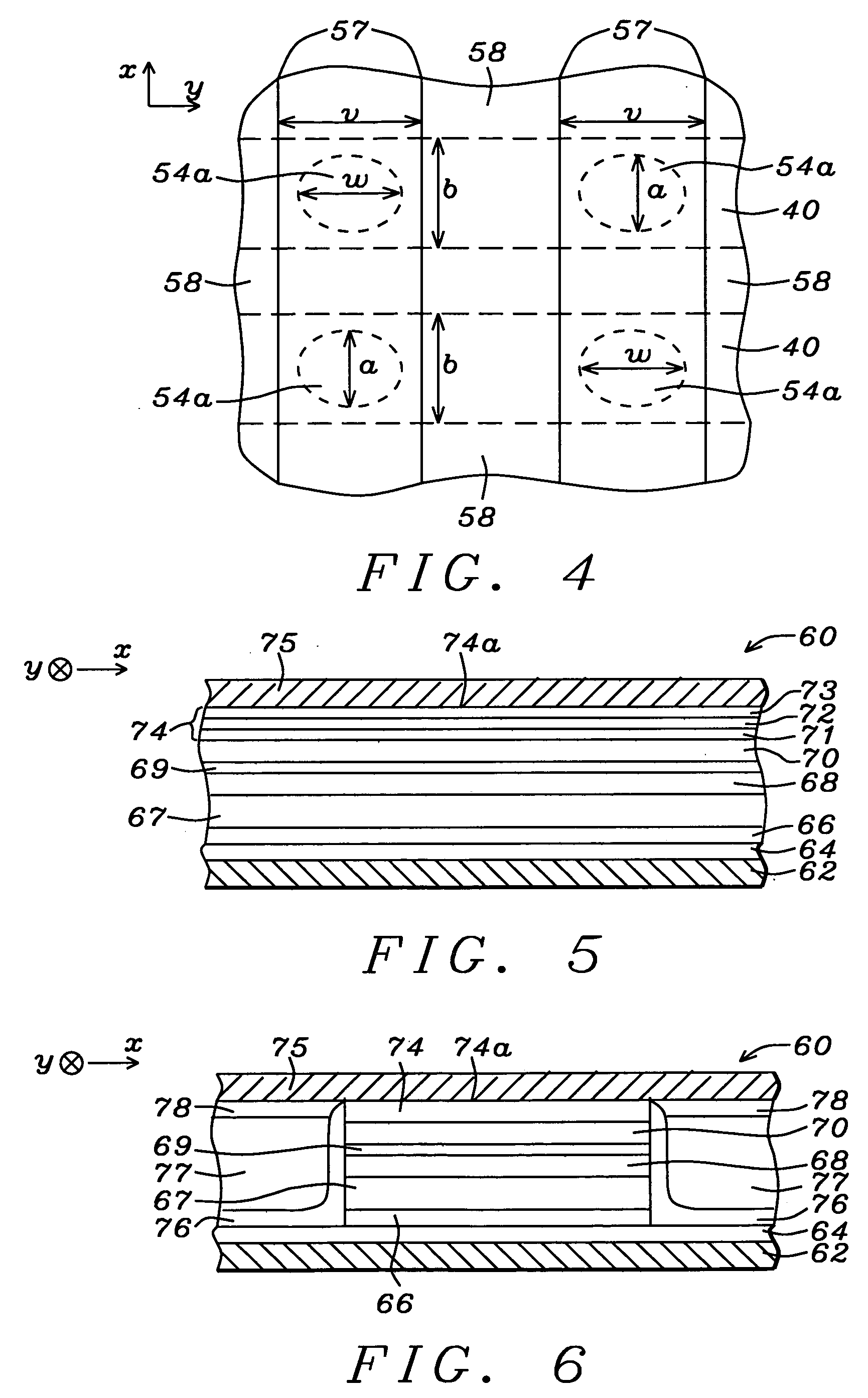

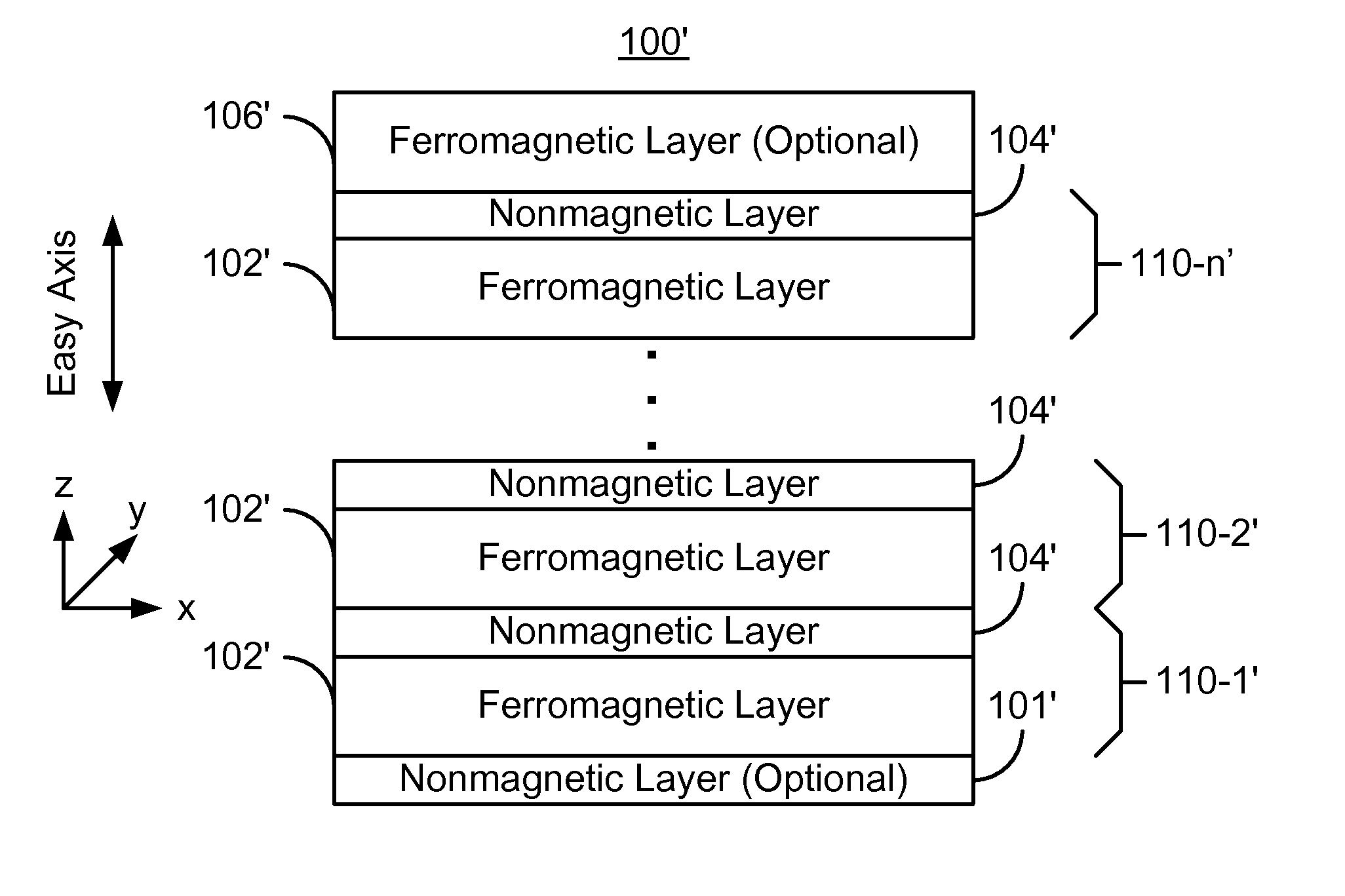

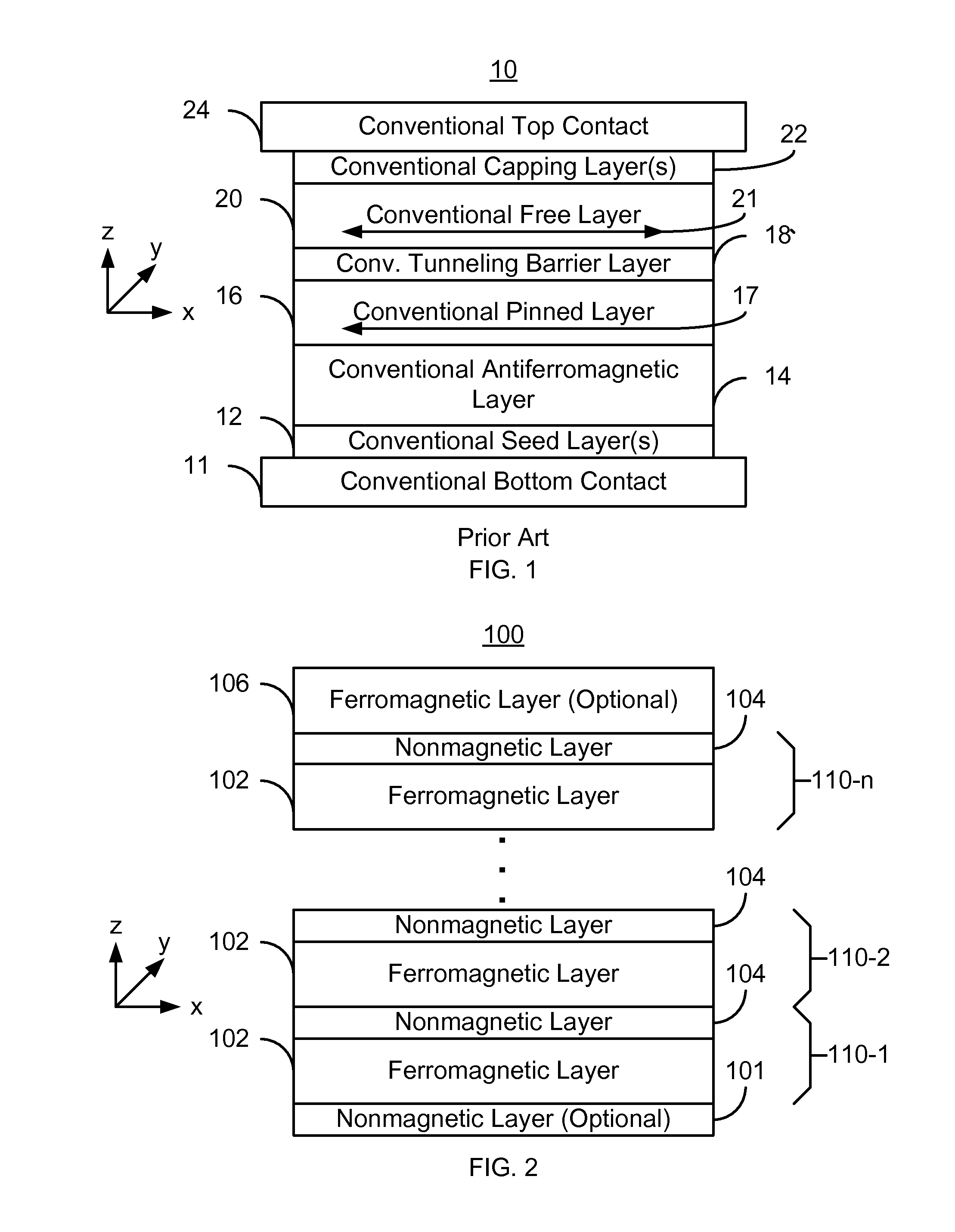

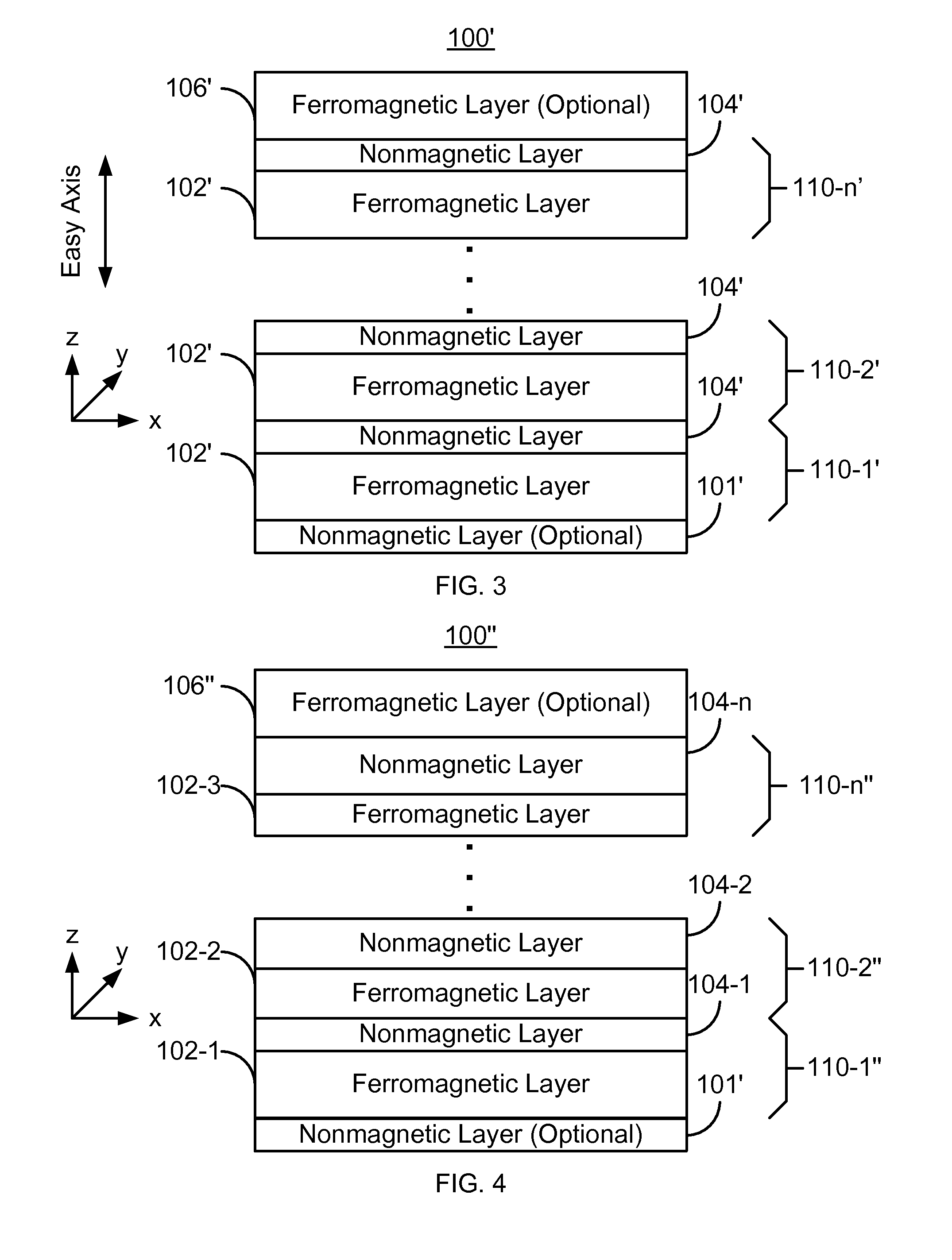

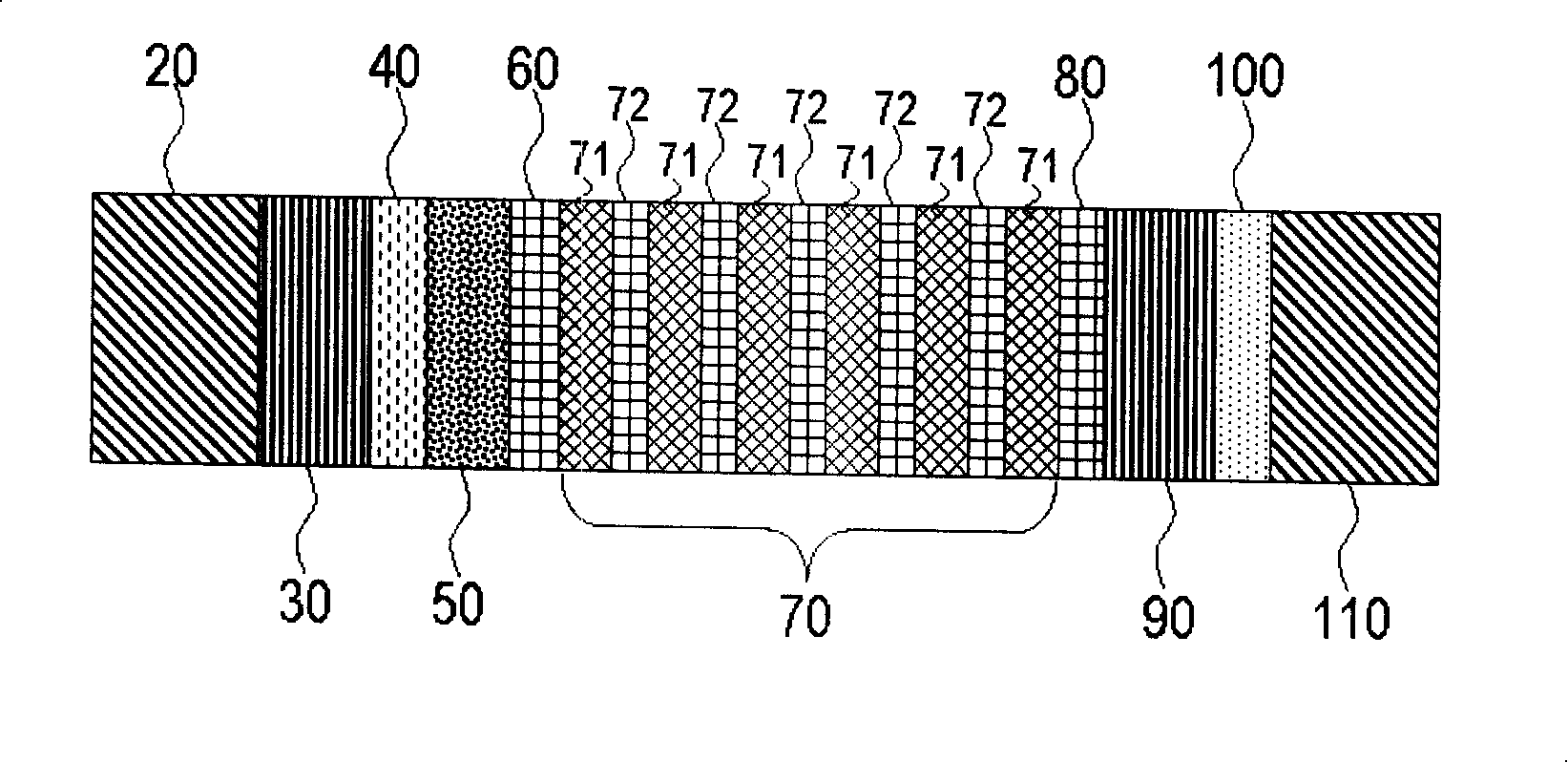

Magnetic tunneling junction elements having magnetic substructures(s) with a perpendicular anisotropy and memories using such magnetic elements

ActiveUS8546896B2NanomagnetismMagnetic-field-controlled resistorsPerpendicular anisotropyNon magnetic

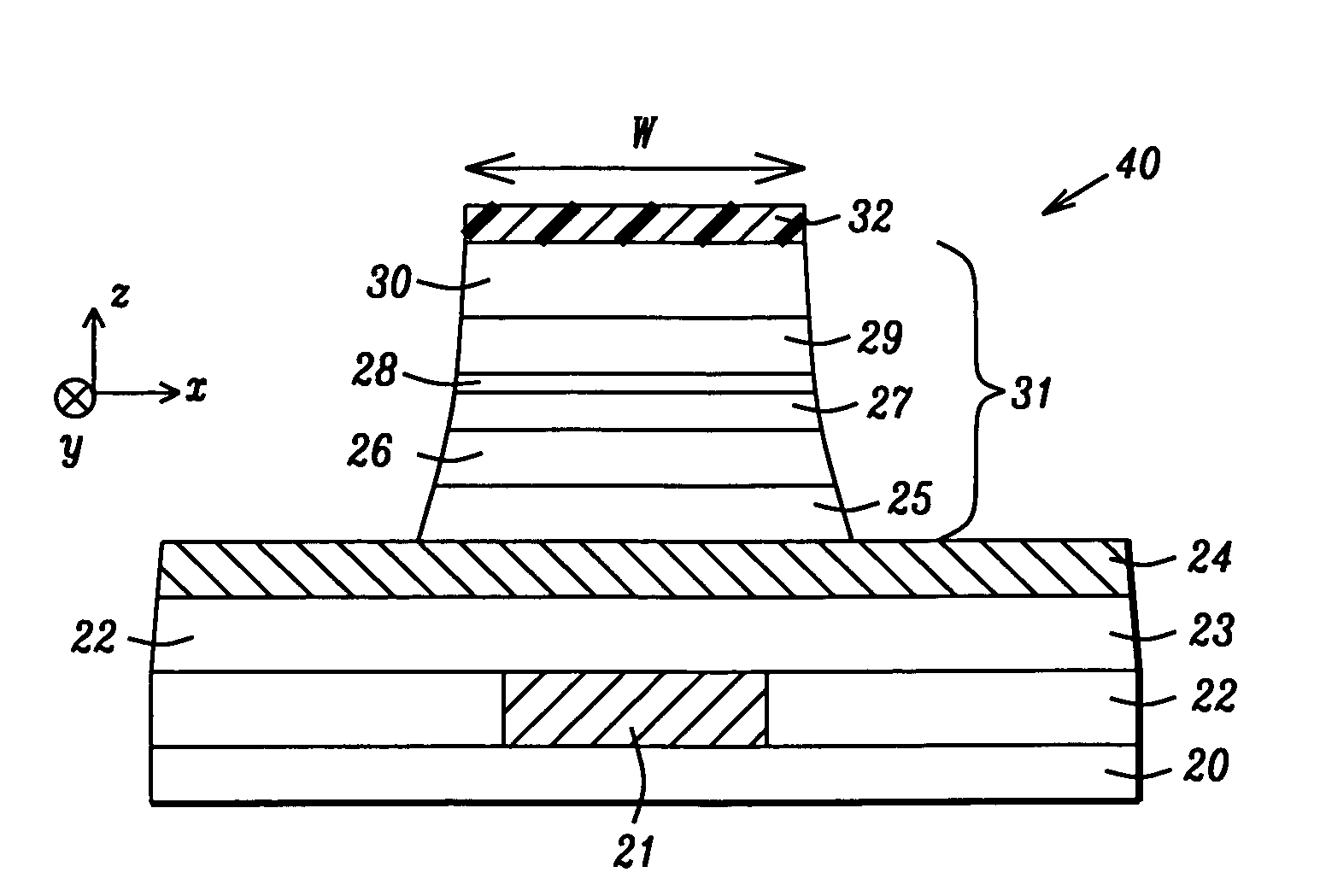

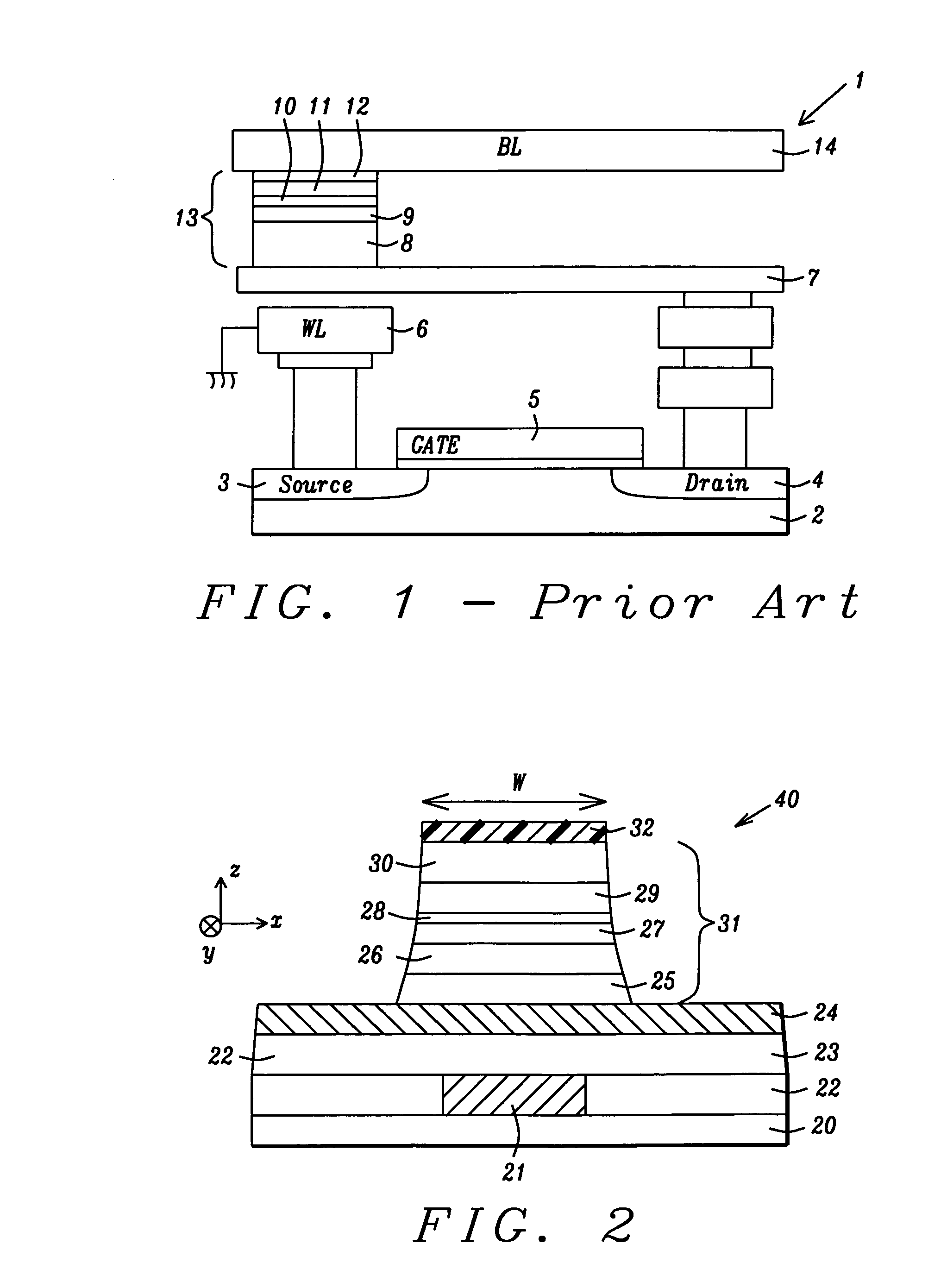

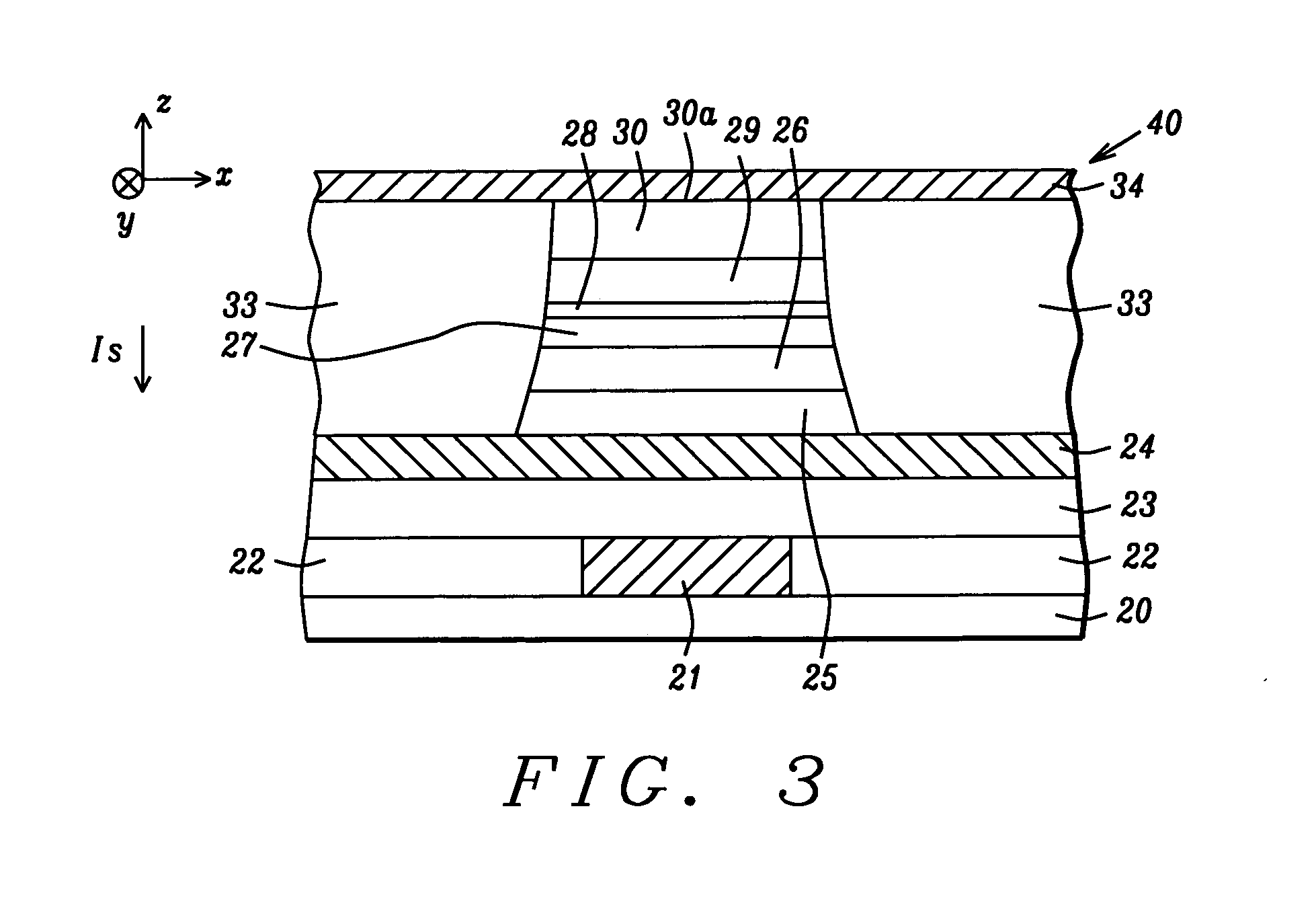

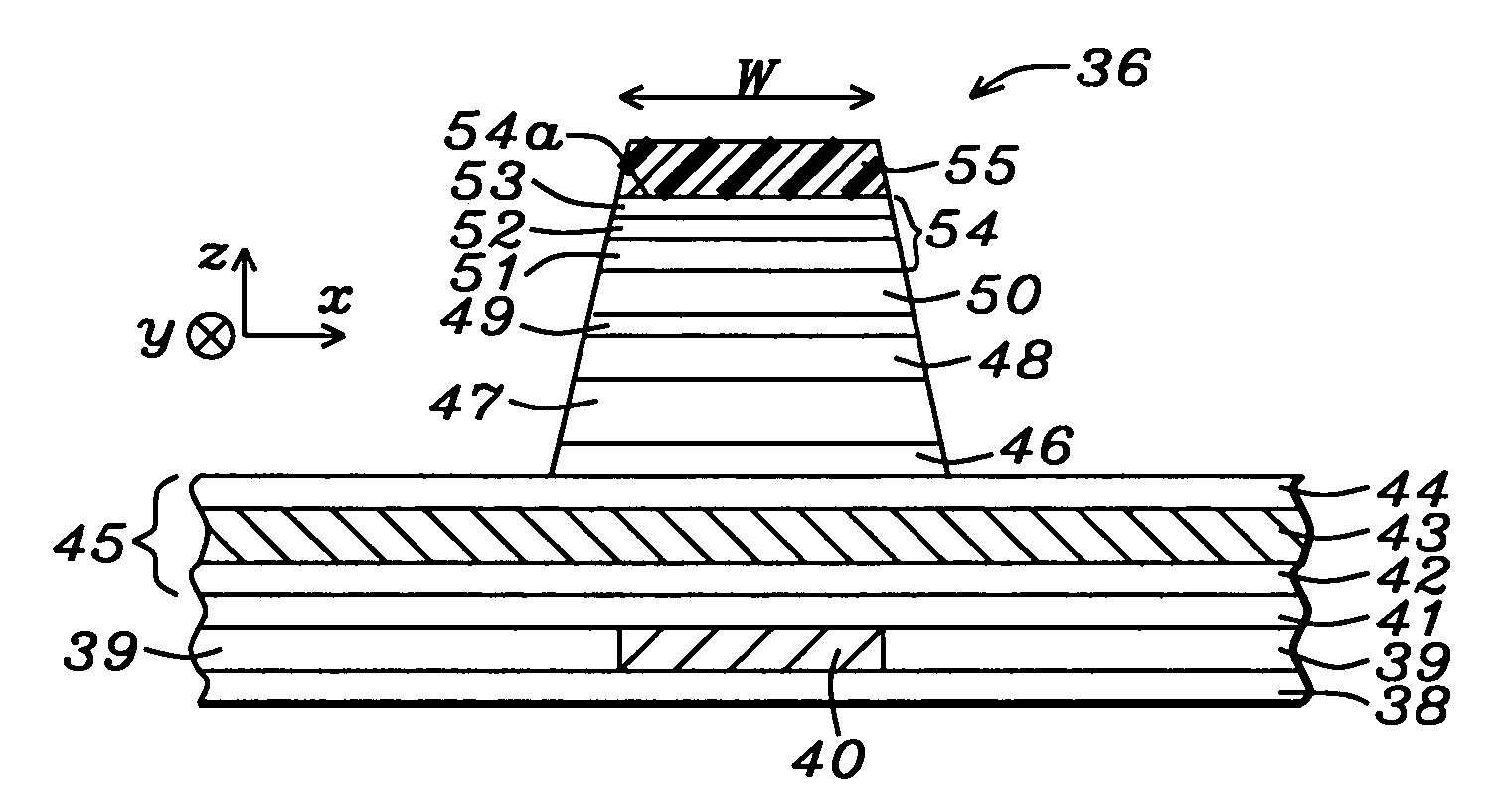

A method and system for providing a magnetic substructure usable in a magnetic device, as well as a magnetic element and memory using the substructure are described. The magnetic substructure includes a plurality of ferromagnetic layers and a plurality of nonmagnetic layers. The plurality of ferromagnetic layers are interleaved with the plurality of nonmagnetic layers. The plurality of ferromagnetic layers are immiscible with and chemically stable with respect to the plurality of nonmagnetic layers. The plurality of ferromagnetic layers are substantially free of a magnetically dead layer-producing interaction with the plurality of nonmagnetic layers. Further, the plurality of nonmagnetic layers induce a perpendicular anisotropy in the plurality of ferromagnetic layers. The magnetic substructure is configured to be switchable between a plurality of stable magnetic states when a write current is passed through the magnetic substructure.

Owner:GRANDIS

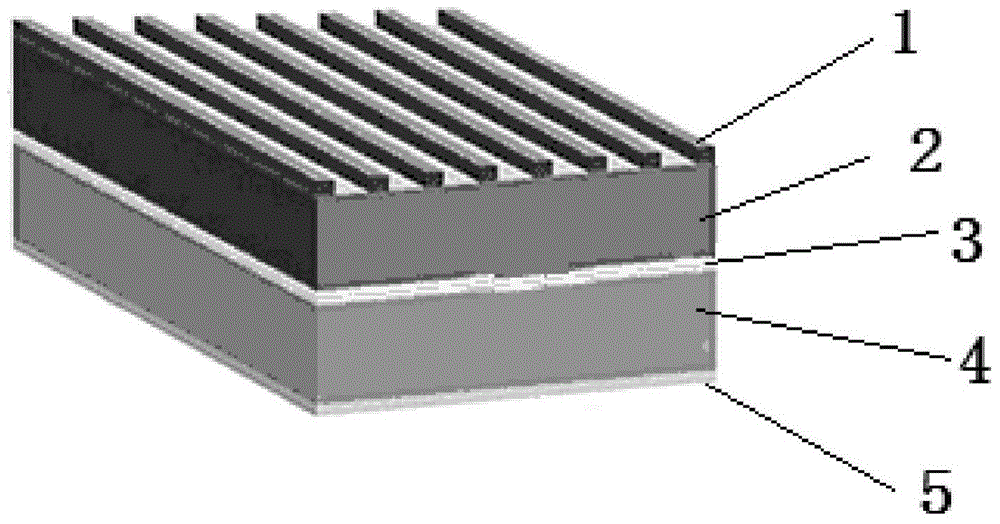

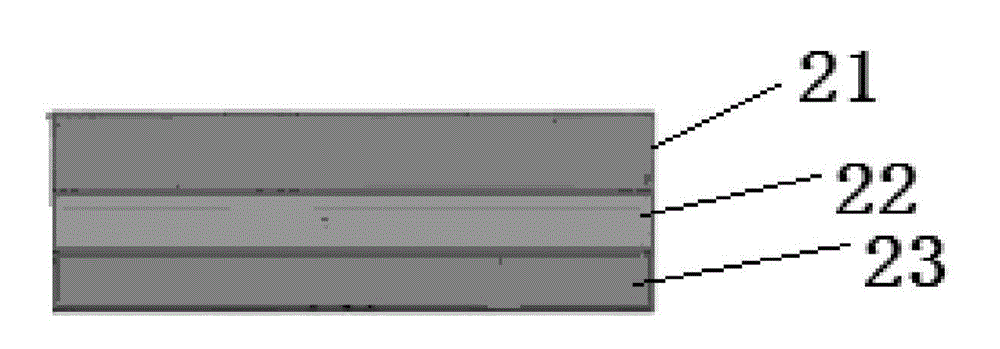

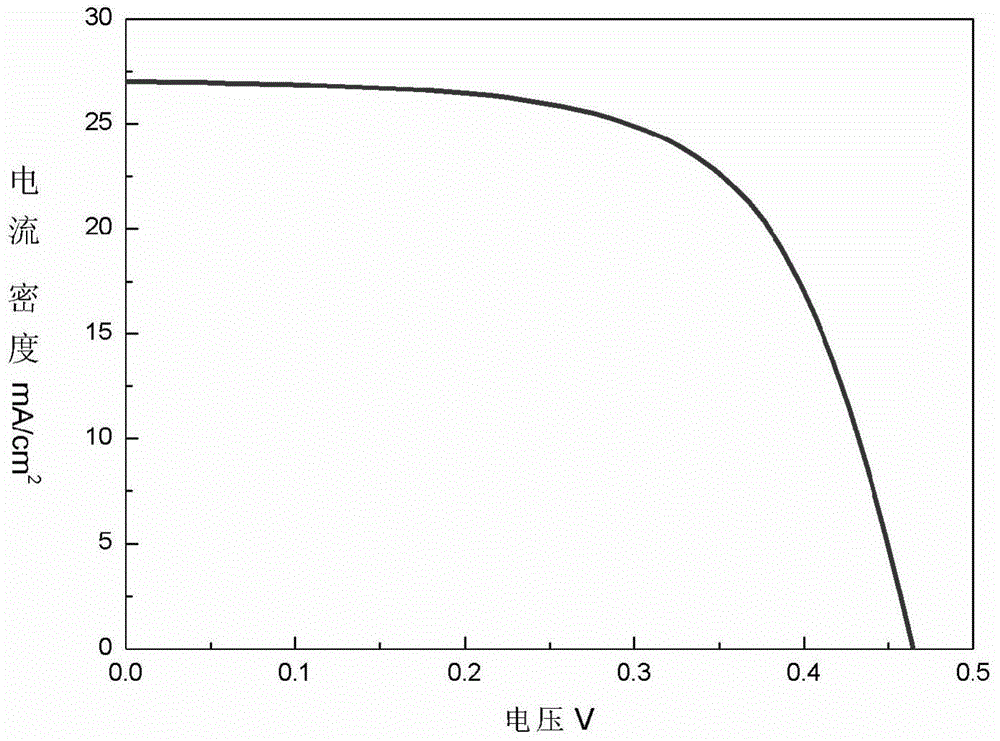

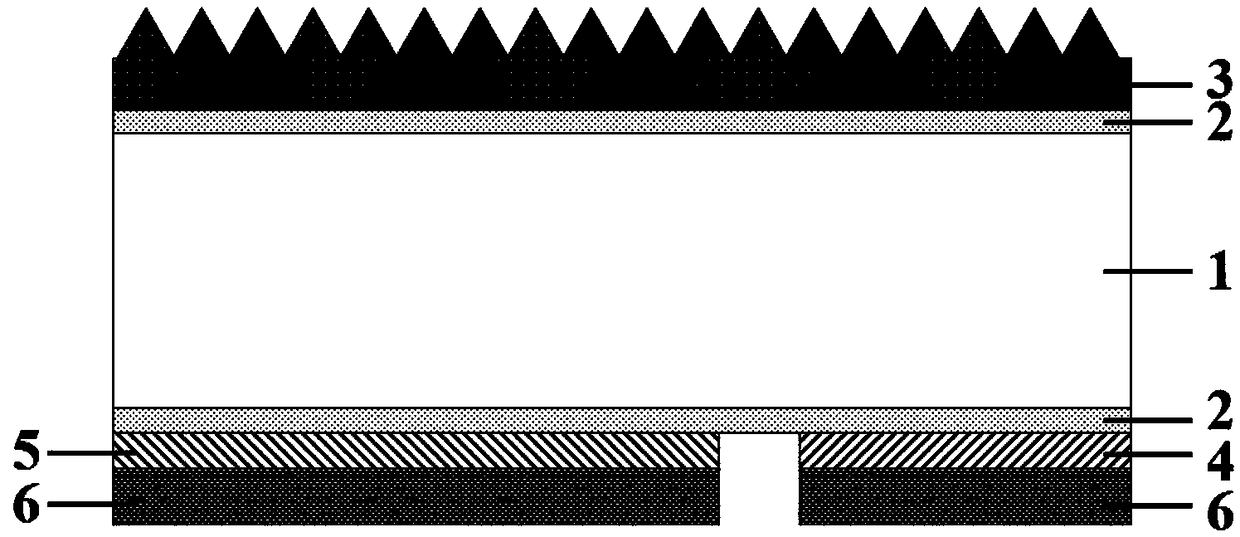

Solar battery with structure of oxide-metal multilayer film/silicon substrate

ActiveCN104916709ASimple structureReduce production processFinal product manufacturePhotovoltaic energy generationSolar batteryIon implantation

The invention discloses a solar battery with a structure of an oxide-metal multilayer film / a silicon substrate. The solar battery structure, from the top to the bottom, successively comprises: a silver electrode, an oxide-metal multilayer film, a passivation layer, a silicon substrate and a full aluminum back electrode. The oxide-metal multilayer film is obtained through compositing a first oxide film, a metal film and a second oxide film. The first oxide film or the second oxide film is a MoO3 film, a tin-doped In2O3 film, a fluorine-doped SnO2 film or an aluminum-doped ZnO film. The metal film is an Ag film, an Au film or an Al film. The solar battery can prevent the tradition thermal diffusion or can prevent the auger recombination and the dead layer phenomenon which are caused by the preparation emission electrode of the ion injection method. Furthermore, the invention also discloses a method for the solar battery with a structure of an oxide-metal multilayer film / a silicon base, which is less in the preparation procedures, applicable to the batch production and high temperature free during the whole preparation process.

Owner:江苏润阳悦达光伏科技有限公司

Heavy diffusion and light diffusion technology for manufacturing selective emitter solar battery

ActiveCN101494253AReduce contact resistanceIncrease the open circuit voltageFinal product manufactureSemiconductor devicesDiffusionSolar battery

The invention discloses a heavy diffusion technology and a light diffusion technology in the manufacture process of a selective emitter solar cell. The heavy diffusion technology is applied below and around an electrode grid line, while the light diffusion technology is applied to a non-electrode grid line area. A high doping deep diffusion area is formed below and around the electrode grid line and a low doping shadow diffusion area is formed in the non-electrode grid line area by changing temperature, air flow quantity and technological time of the two diffusion technologies. The technologies solve the problem that the traditional one-step diffusion technology cannot reduce contact resistance on the surface of a silicon slice and a dead layer simultaneously, and have great meaning to the improvement of the overall performance of a crystalline silicon solar cell.

Owner:JA SOLAR TECH YANGZHOU +2

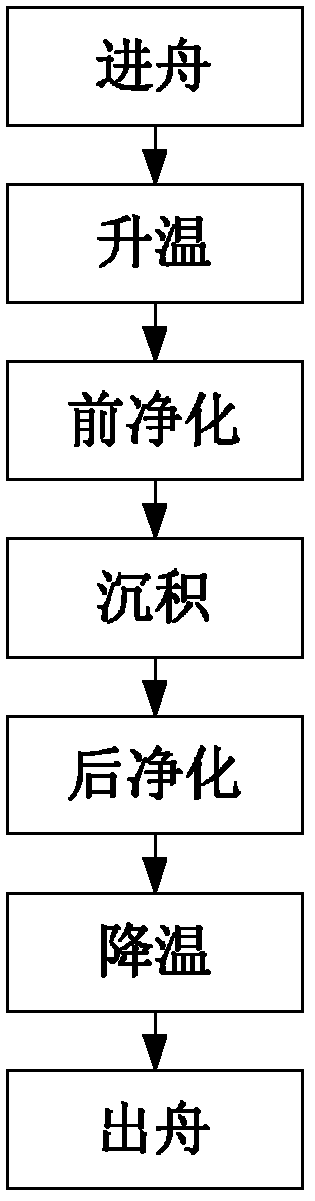

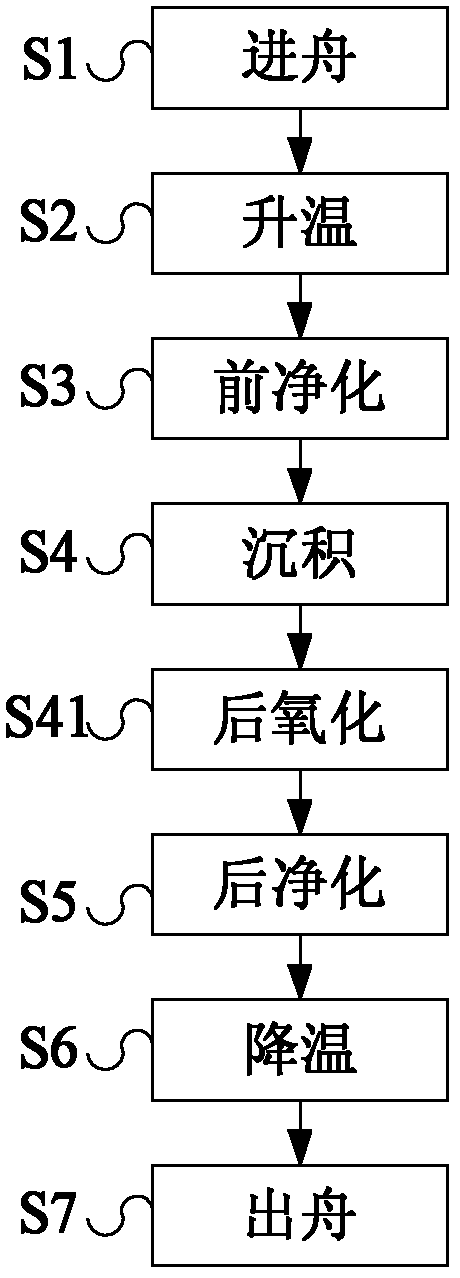

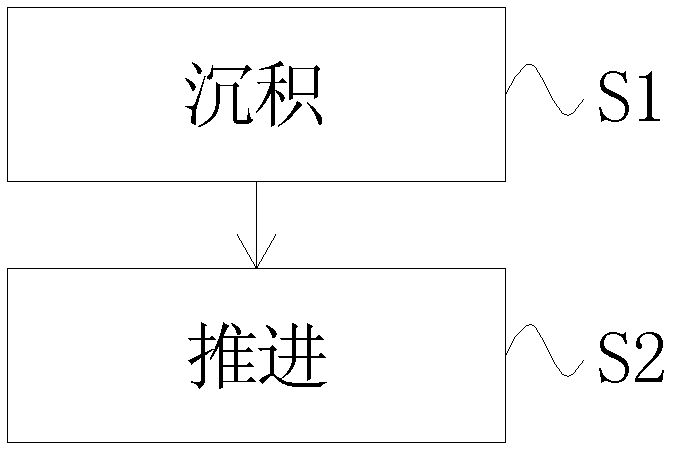

Method for reducing dead layer of solar cell

ActiveCN103367521AImprove spectral responseIncreasing the thicknessFinal product manufactureSemiconductor devicesChemical treatmentCompound (substance)

The invention provides a method for reducing a dead layer of a solar cell, and the method comprises the steps: 1) boat entering; 2) temperature rise; 3) pre-purification; 4) deposition; 5) post-purification; 6) temperature reduction; 7) boat exiting. The method also comprises: 41) post-oxidation between the step 4) and the step 5) i.e. feeding oxygen for a preset time at a preset temperature by a preset flow or carrying out the post-oxidation step during the step 5). According to the invention, the post-oxidation treatment is added and a certain amount of oxygen is let in after deposition and before the post-purification or in the process of the post-purification. Another layer of oxide film is formed between an oxide film, formed during the pre-purification, and a PN junction. The thickness of the oxide film is increased after the PN junction is formed. Phosphorus atoms react with oxygen after passing through the oxide film and diffusing towards a silicon wafer so as to further reduce the thickness of phosphorus on the surface of the PN junction and decrease the dead layer. Meanwhile, the oxide film is removed after chemical processing to reduce the thickness of the PN junction, so as to effectively improve spectrum response of a cell.

Owner:YINGLI ENERGY CHINA

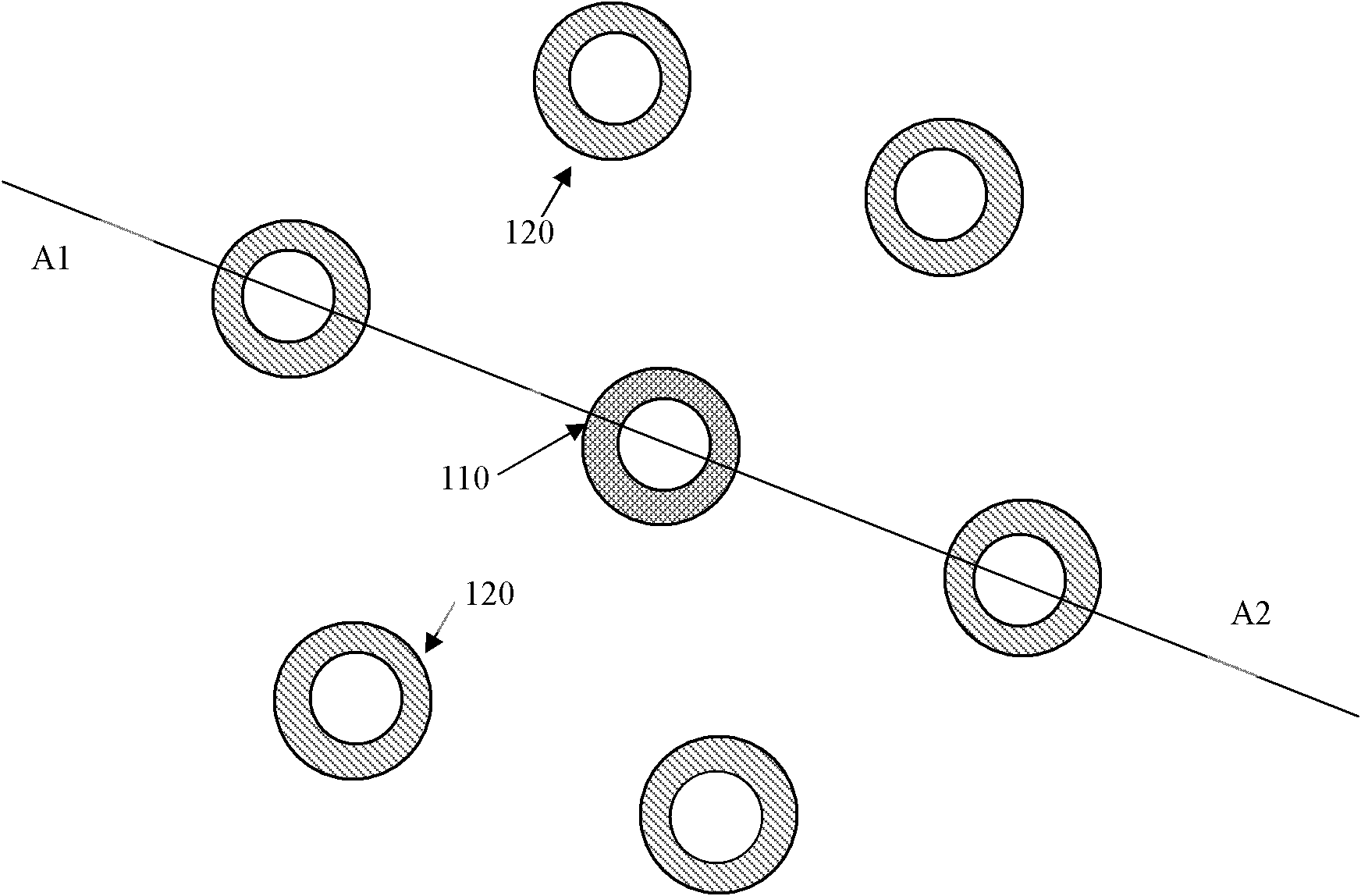

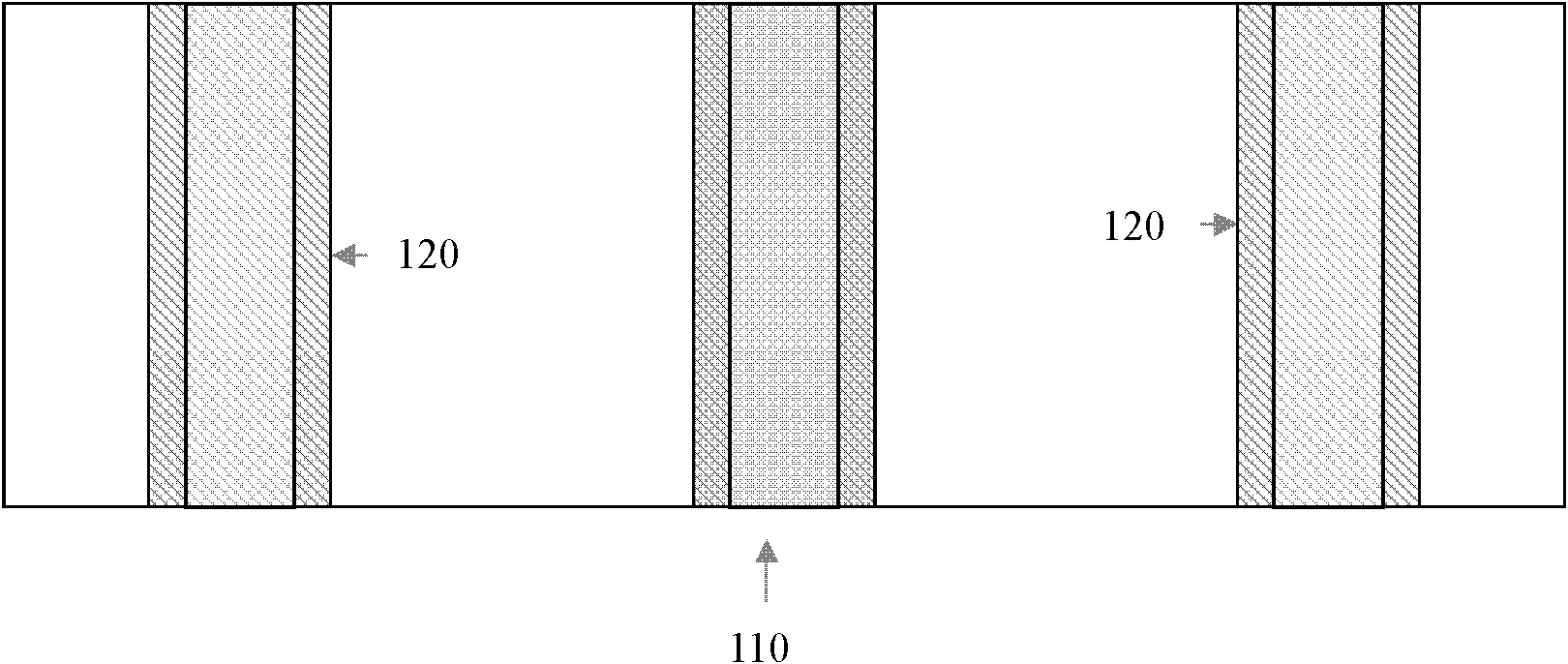

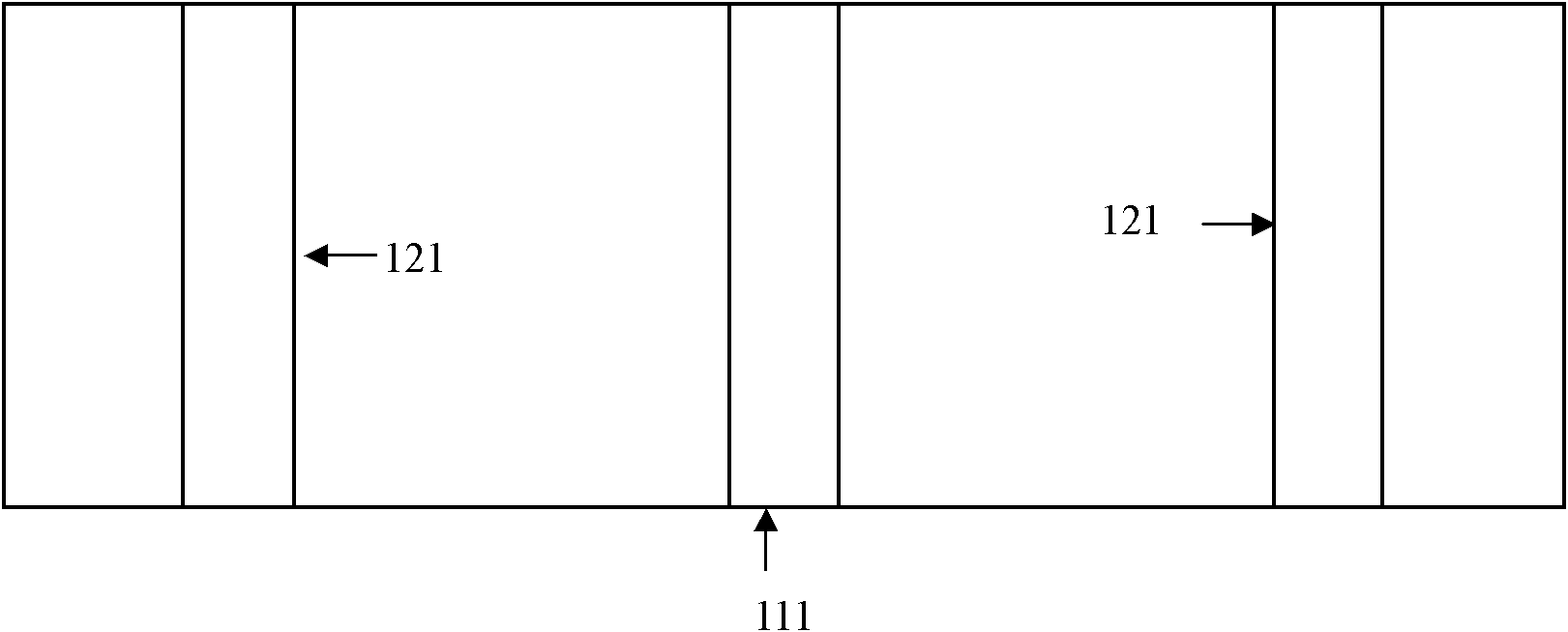

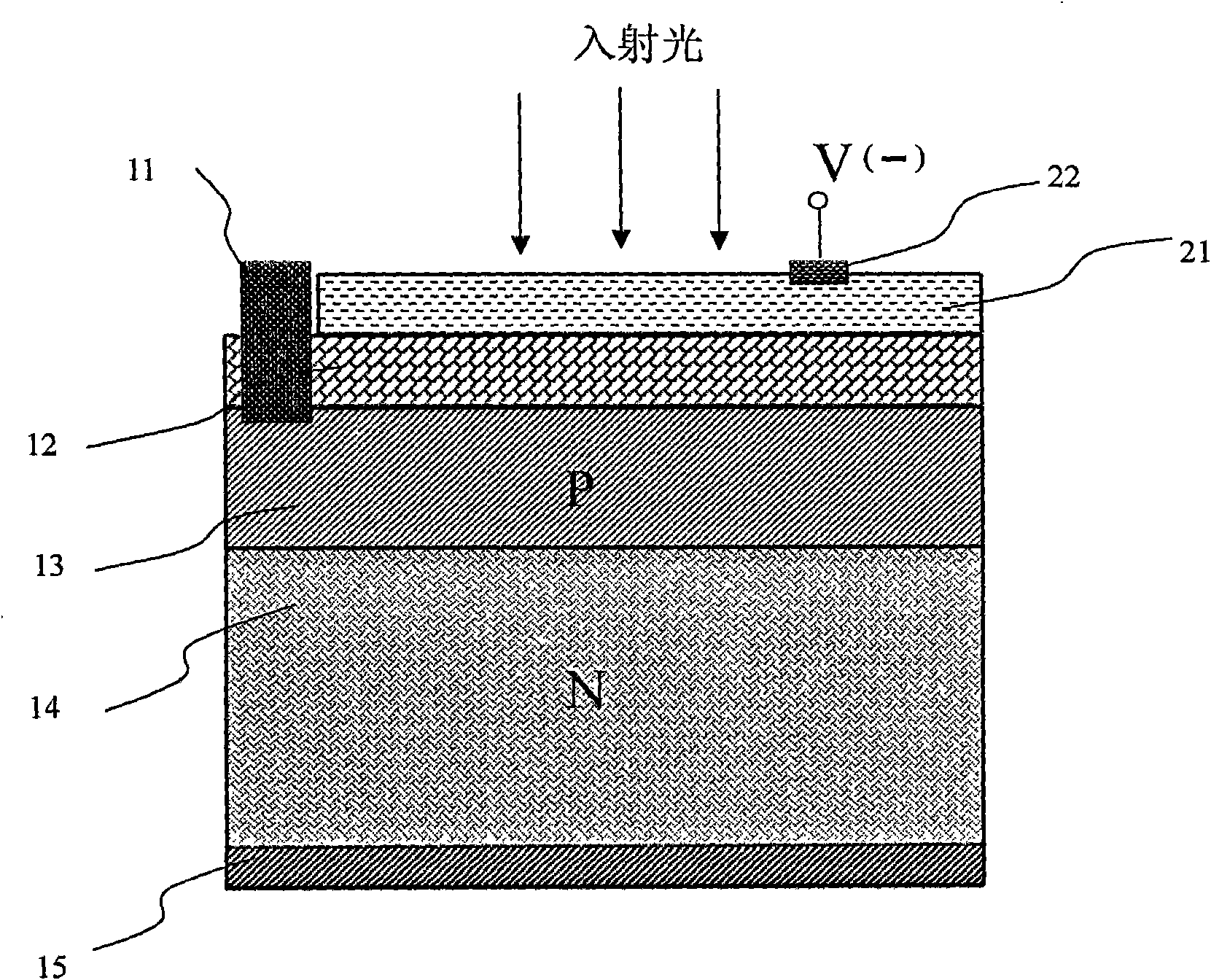

Semiconductor radiation sensing device and manufacturing method thereof

InactiveCN102214723AHigh-resolutionLow detection limitFinal product manufactureSemiconductor devicesLower limitSemiconductor sensor

The invention relates to the field of semiconductor sensors and discloses a semiconductor radiation sensing device and a manufacturing method thereof. The sensing device comprises at least one radiation sensing unit, wherein each radiation sensing unit comprises a first substrate, a first columnar electrode and a second columnar electrode; the first substrate comprises a first surface and a second surface; the first columnar electrode comprises first metal posts and N-type doped silicon surrounding the first metal posts; the second columnar electrode comprises more than two second metal postsand P-type doped silicon surrounding the second metal posts; the first columnar electrode and the second columnar electrode are embedded into the first substrate and pass through the first surface and the second surface of the substrate; the more than two metal posts are arranged in an equilateral polygon mode; and the first columnar electrode is arranged at the geometric center of the equilateral polygon. According to the invention, the thin dead layer thickness of the sensing device, the smaller equivalent capacitance and the shorter signal drifting process can be realized, thus improving the energy resolution, reducing the response time and decreasing the lower limit of energy detection.

Owner:PEKING UNIV

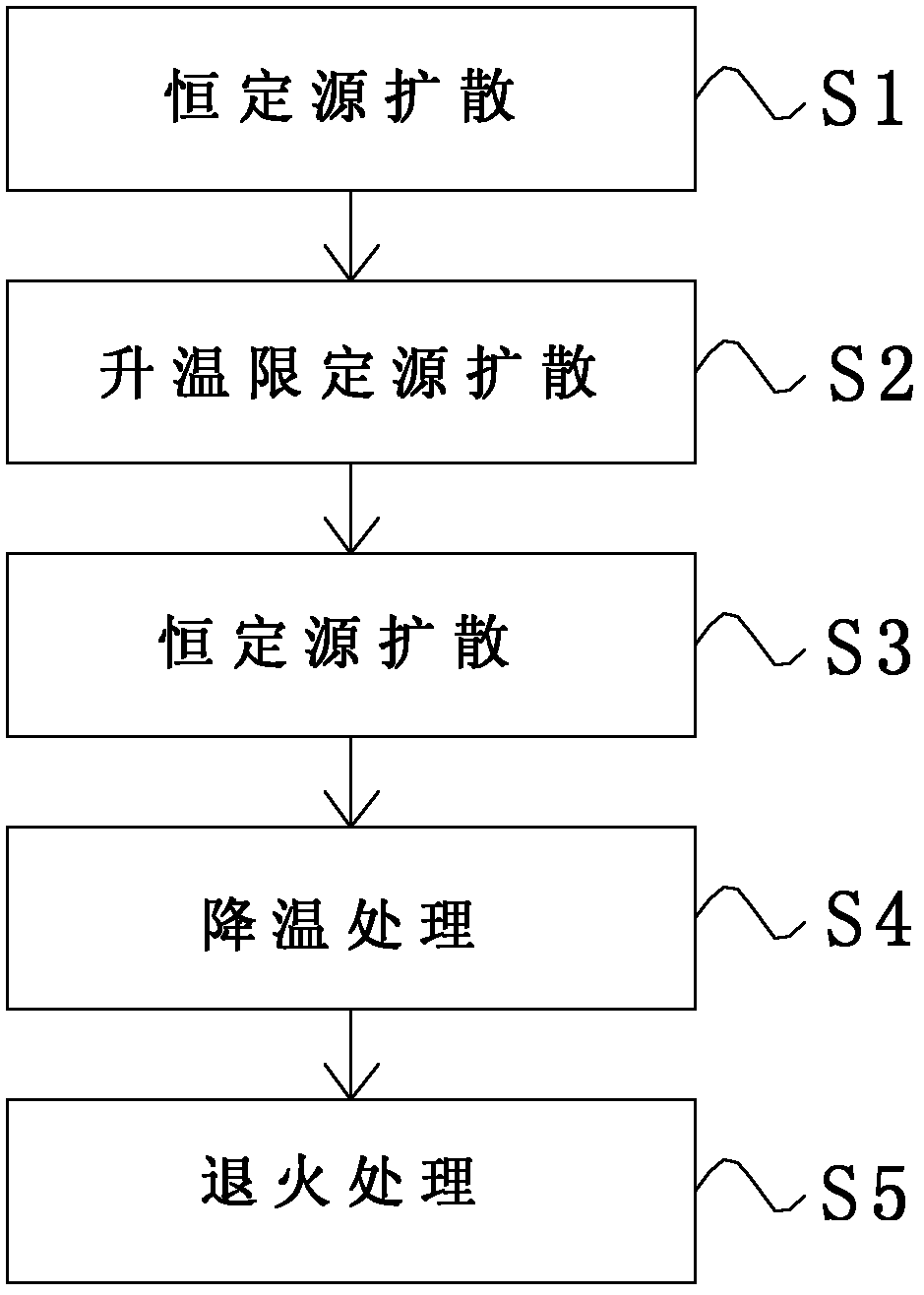

Polysilicon silicon chip double-diffusion manufacturing method

ActiveCN102586884ASolve the problem of "dead layer" on the surfacePolycrystalline material growthAfter-treatment detailsDiffusionDouble diffusion

The invention discloses a method for manufacturing a PN-node by carrying out double diffusion on a polysilicon silicon chip. The method comprises a step S1 of constant-source diffusion, a step S2 of heating limited-source diffusion and a step S3 of constant-source diffusion. In the invention, due to the step S3 of constant-source diffusion, the deposition of a phosphorus impurity on the surface of the polysilicon silicon chip is increased. Therefore, in the step S1, the phosphorus impurity which is deposited in one step can be correspondingly reduced, so that the excessive deposition of the phosphorus impurity is avoided. Moreover, the step S3 is carried out at a high temperature, and at the time, the solid solubility of polysilicon on phosphorus atoms is improved, the deposited phosphorus impurity does not need to be propelled, the dissolved amount of the phosphorus impurity in polysilicon is controlled by controlling the deposition of the phosphorus impurity, and a dead zone generated due to excessive deposition and secondary propelling is avoided. According to the method for manufacturing the PN-node by carrying out the double diffusion on the polysilicon silicon chip, which is provided by the invention, the aim of solving the problem of a dead layer on the surface, which is generated after the PN-node is manufactured by the polysilicon silicon chip, can be fulfilled.

Owner:YINGLI ENERGY CHINA

Shallow concentration diffusion process for crystalline silicon solar cell

InactiveCN103151421AImprove HarmonyIncrease short circuit currentFinal product manufactureSemiconductor devicesPower flowCrystalline silicon

The invention relates to a shallow concentration diffusion process for a crystalline silicon solar cell. Based on an existing process, improvement is carried out. The shallow concentration diffusion process comprises the three steps of oxidation, sedimentation and constant temperature. A positive-negative (P-N) node of the cell is obtained. During sedimentation and constant temperature advancing processes, diffusion concentration is controlled to be reduced, and a diffusion step is eliminated. Therefore, a dead layer formed after diffusion is eliminated, the integrating degree of the P-N node and a sizing agent is increased, a short-circuit current the solar cell is increased by 0.2-0.25A, and efficiency of a cell piece is increased by more than 3 percent.

Owner:QINGHAI JUNENG POWER

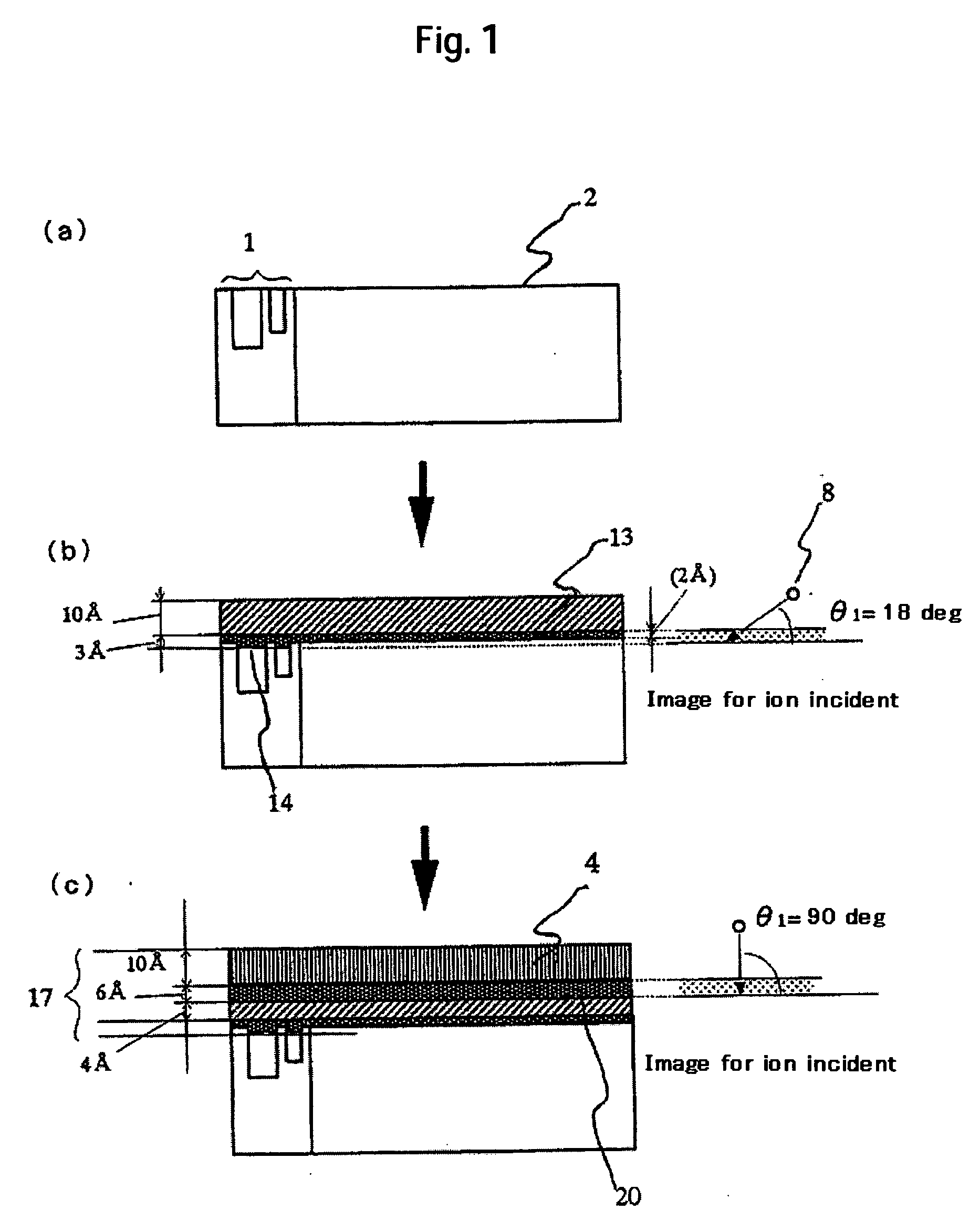

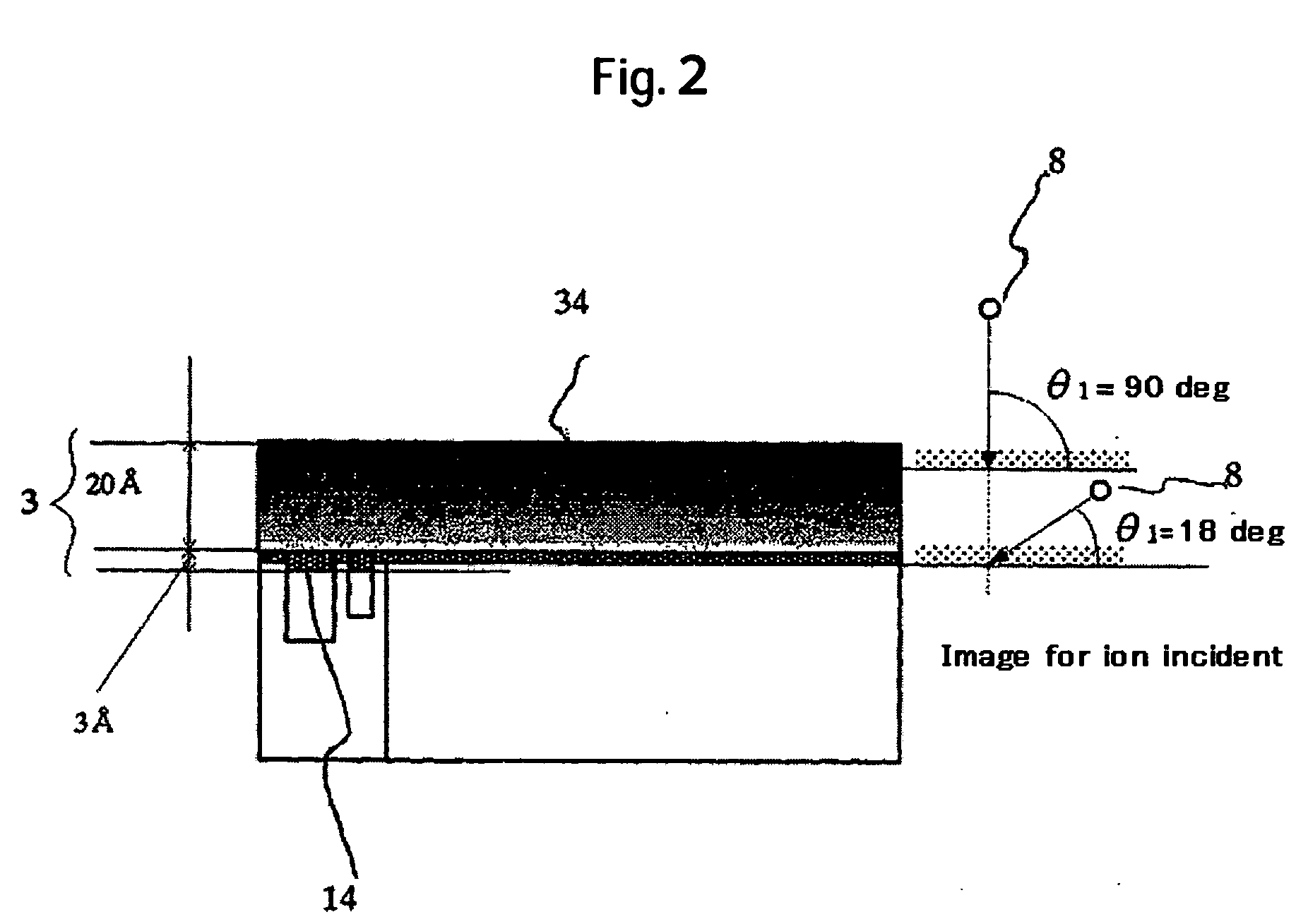

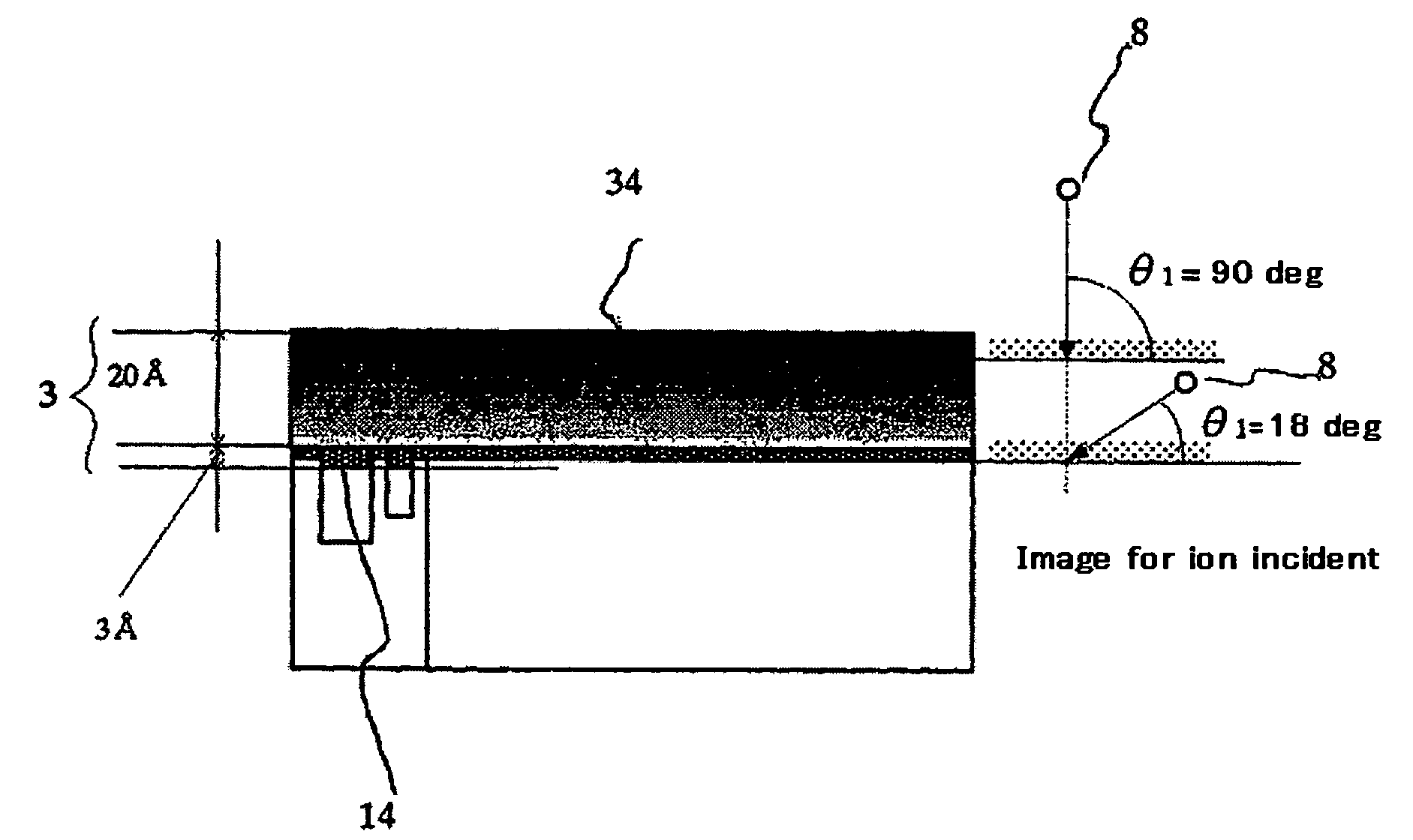

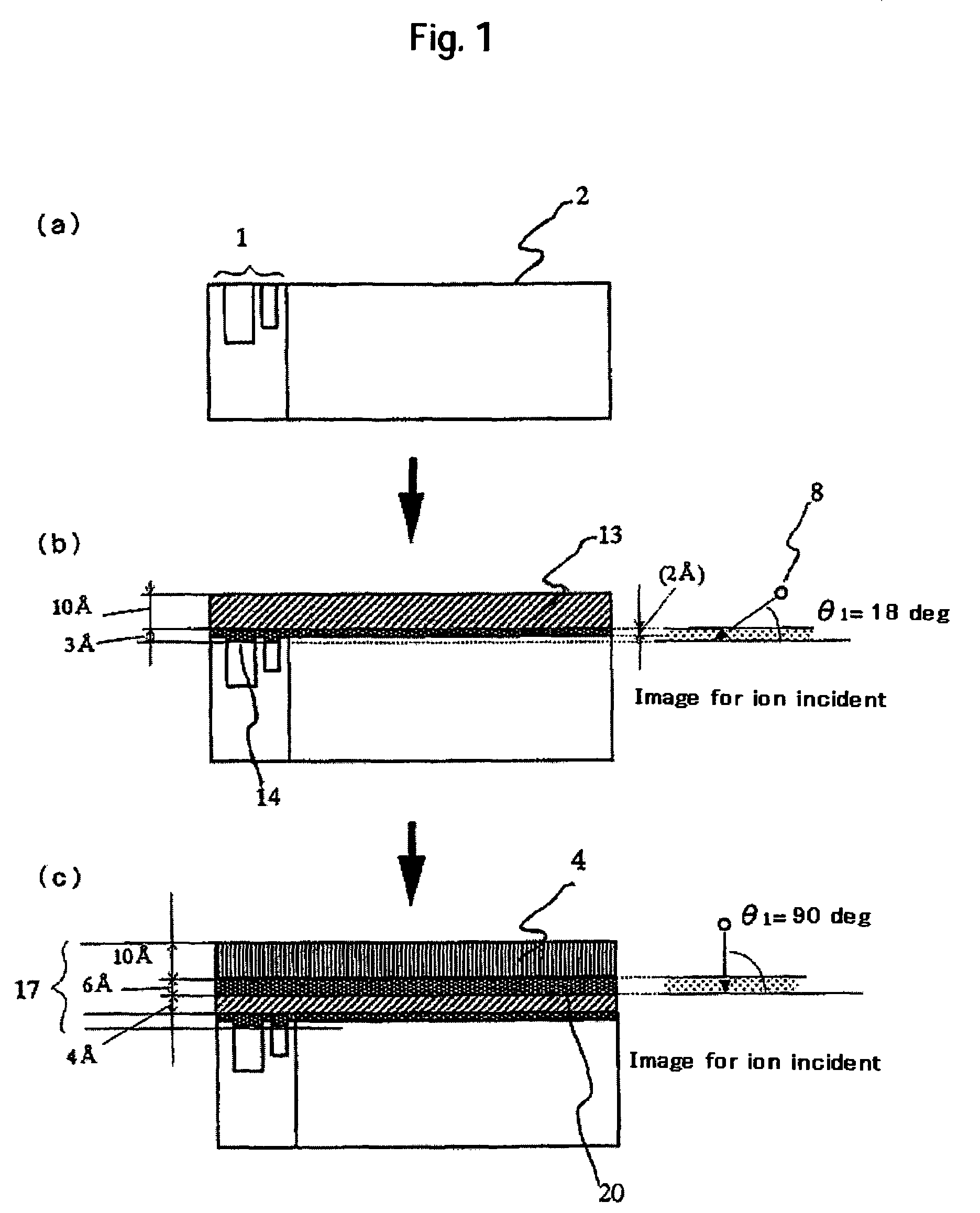

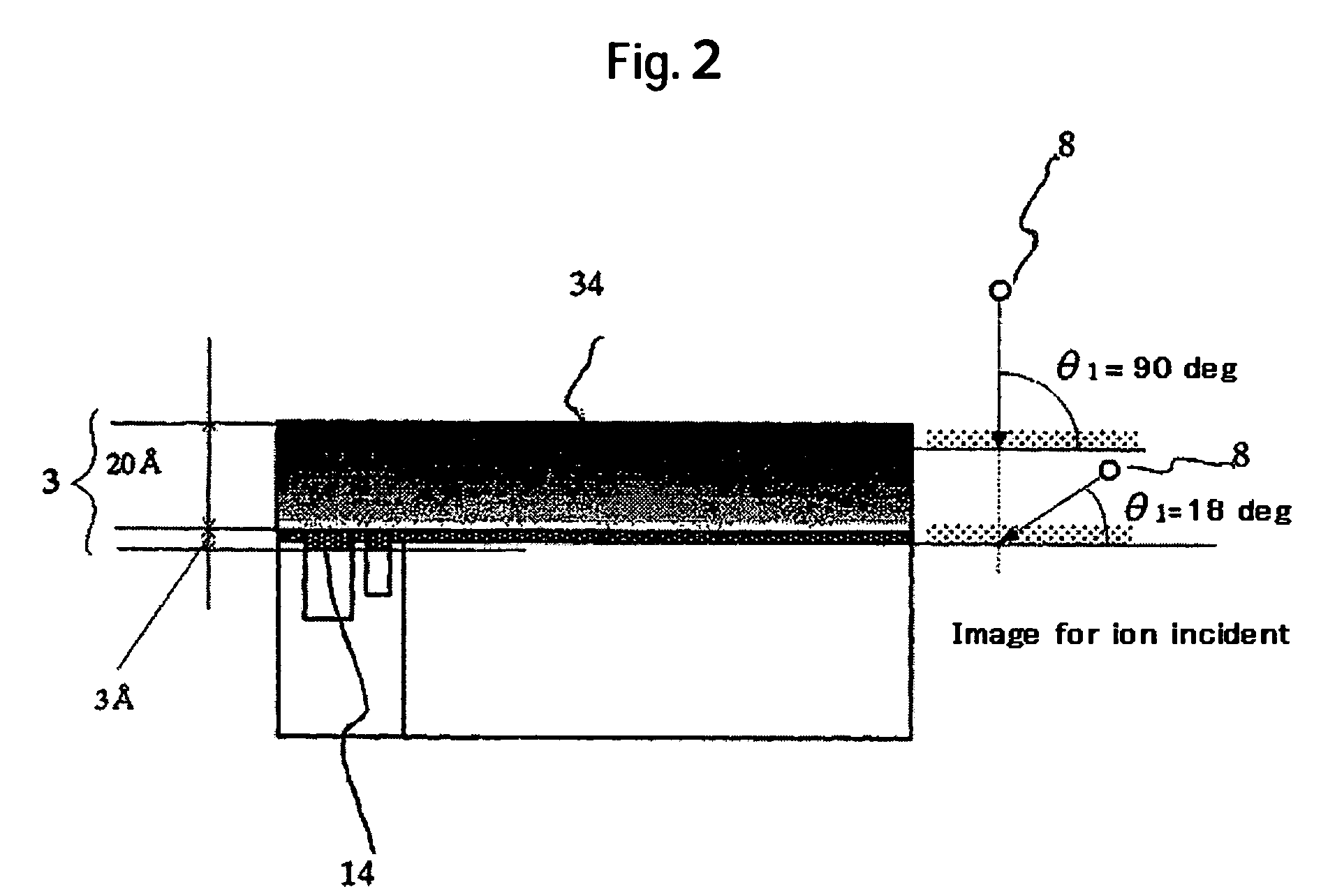

Magnetic head with air bearing surface protection film and manufacturing method thereof

InactiveUS20060072246A1Reduce thicknessReduce film thicknessManufacture head surfaceFluid-dynamic spacing of headsCarbon filmAir bearing

To promote reduction in thickness of an air bearing surface protective film of a magnetic head, a magnetic head having an air bearing surface protective film consisting only of a thin carbon film while excluding formation of a dead layer by ion incidence as less as possible to the read / write device, and a manufacturing method therefore, are provided. In an embodiment, an air bearing surface protective film of a magnetic head comprises a thin carbon film, in which the mass density a lowermost layer of the air bearing surface protective film on the side of a magnetic device is made lower compared with a thin carbon film constituting other adjacent layers. Further, the manufacturing method comprises deposition under the control of time for the incident angle of ion flow to a substrate to be processed and deposition under the control of time for the ion flow energy to a substrate to be processed

Owner:WESTERN DIGITAL TECH INC

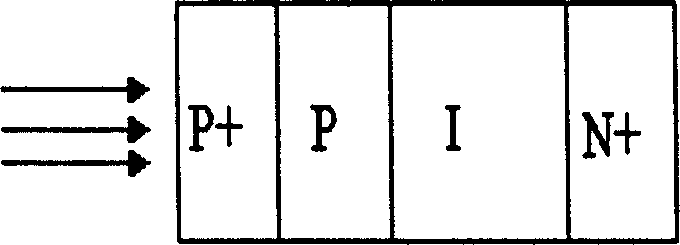

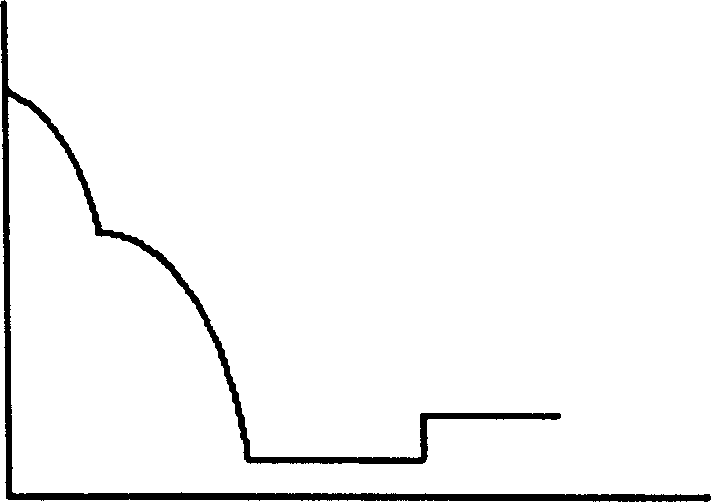

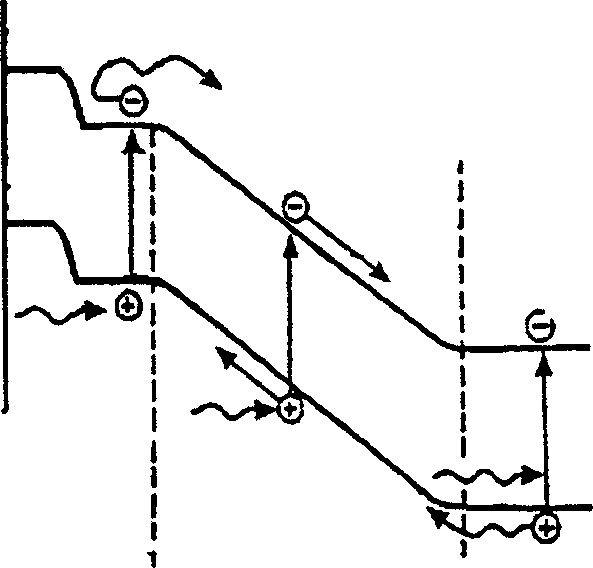

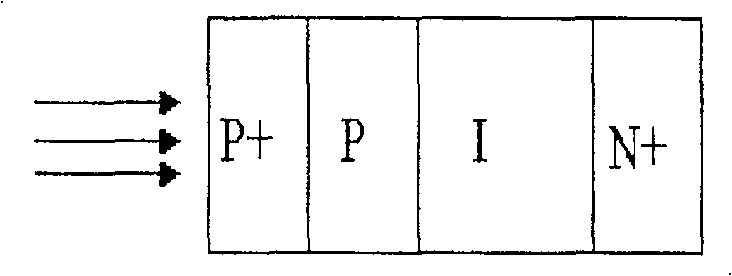

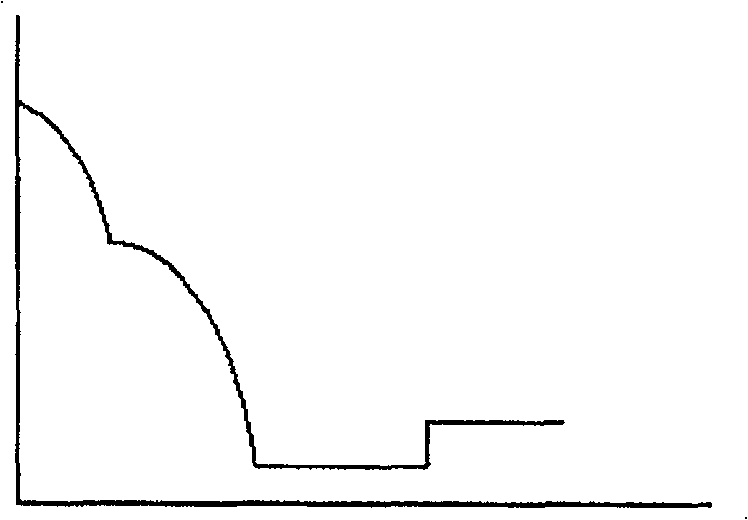

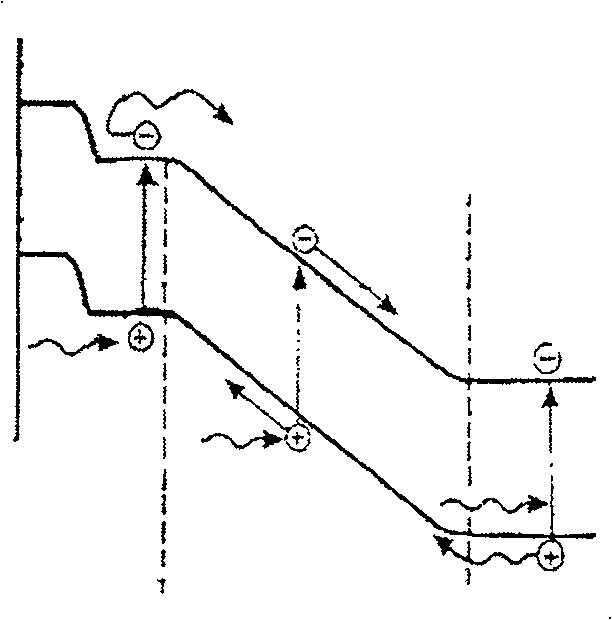

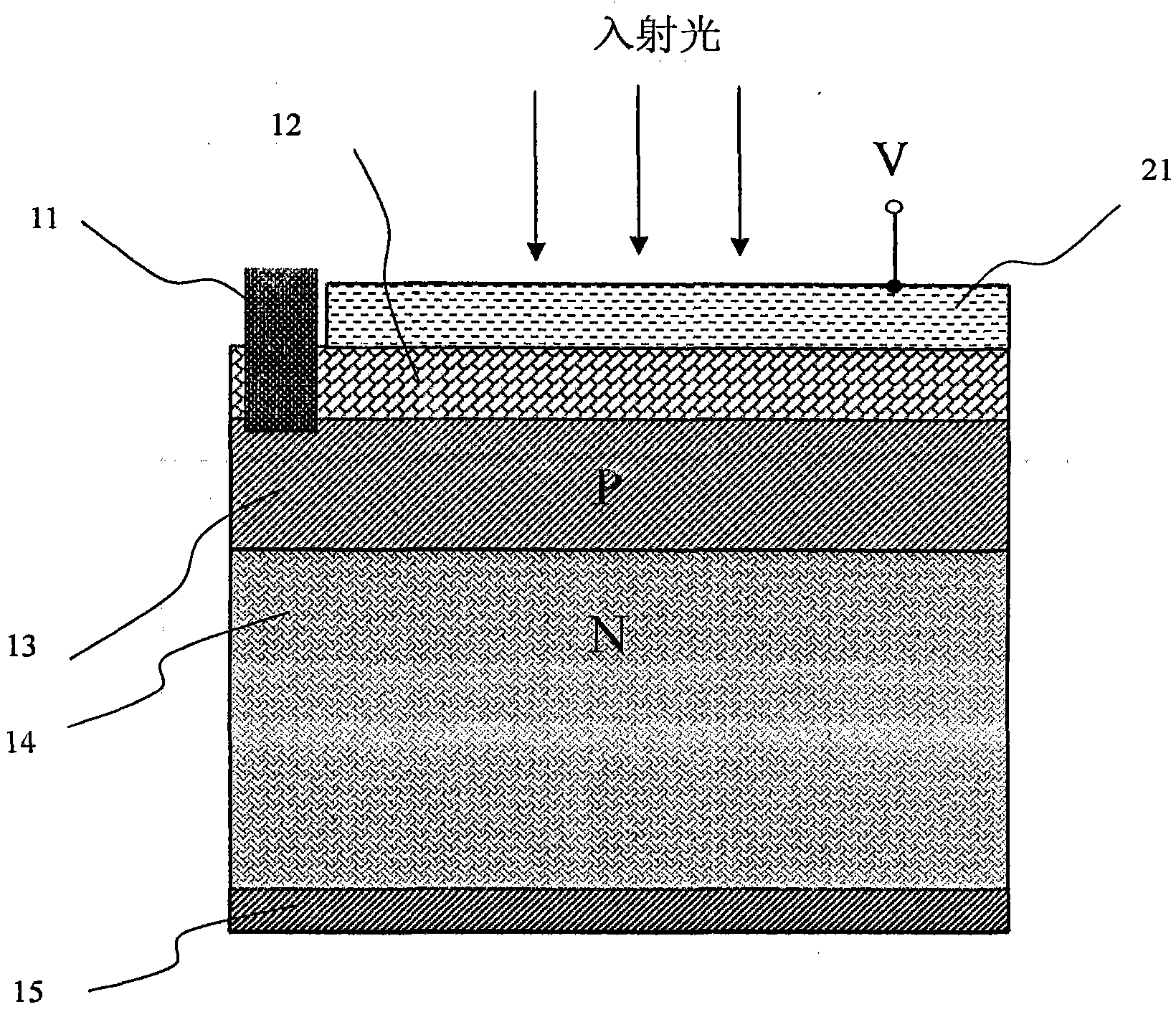

Photoelectric detector for 650nm optical fiber communication and its producing method

This invention relates to a photoelectric detector use in 650nm fiber communication compose of four layers of heavy doped p+ surface layer / P layer / light doped N- epitaxial layer / heavy doped N+ substrate in following steps: growing a material, oxidizing, photo etching the oxide film, diffusing the P type, evaporating the photo etched Al, forming an electrode with alloy, evaporating the O photo etched anti-reflection film and evaporating the back electrodes with good property of 1-v, small dark current and high light response. The heavy doped p+ surface layer is thin to reduce the 'dead layer' thickness and enables most part of incident light to pass through the p+ layer and inject into P layer and one layer to generate effective photo-generated carriers to improve the performance of the emitting region and increase the short wave quantum efficiency.

Owner:XIAMEN SAN U OPTRONICS

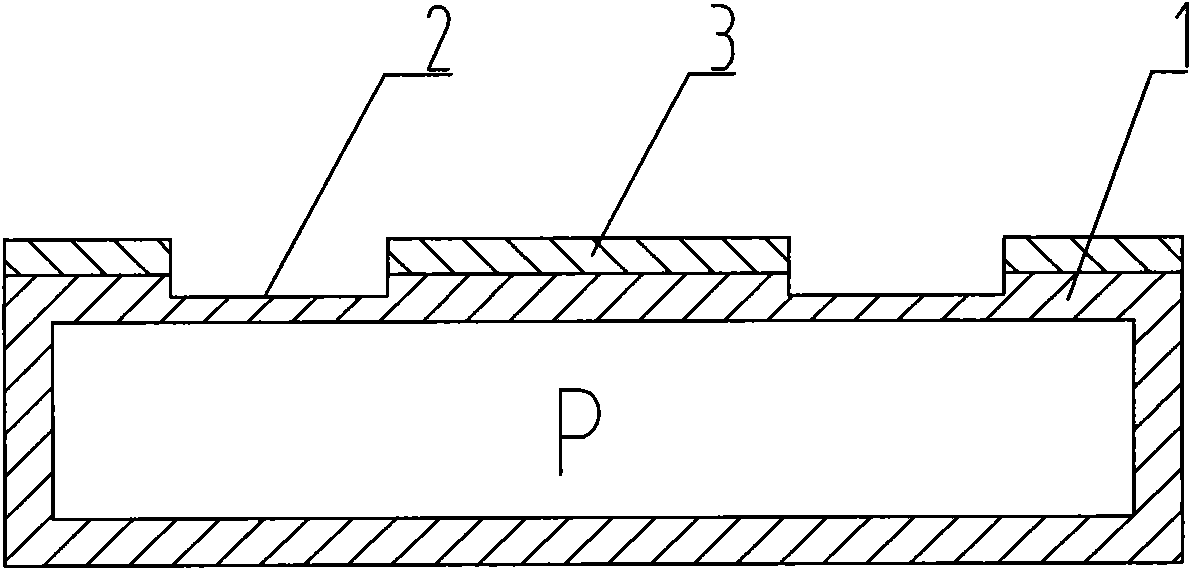

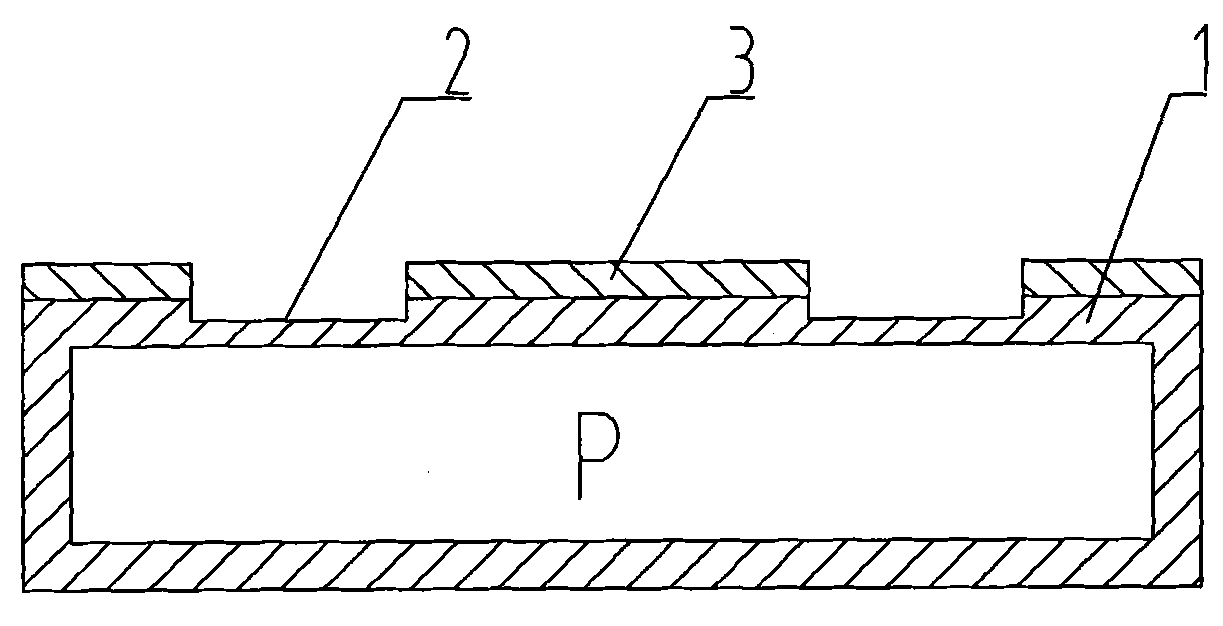

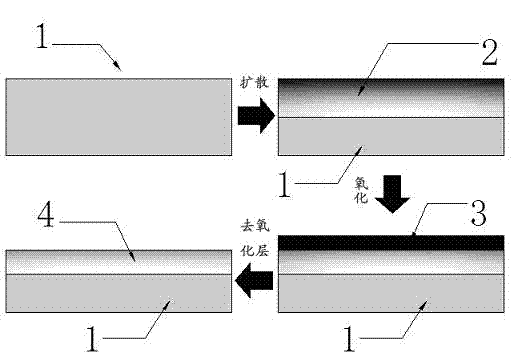

Process for manufacturing emitter of solar cell

InactiveCN102881766AExtend your lifeImprove conversion efficiencyFinal product manufactureSemiconductor devicesSurface concentrationP–n junction

The invention discloses a process for manufacturing an emitter of a solar cell, which comprises the following steps: step A, manufacturing a PN junction on the surface of a matrix silicon wafer (1) by a diffusion process to form a surface impurity distribution layer (2); step B, oxidizing the surface impurity distribution layer (2) obtained in step A to quickly grow an oxidation layer (3) distributed uniformly on the surface of the surface impurity distribution layer (2); and step C, removing the oxidation layer (3) in step B. The process avoids the phenomenon that the ordinary diffusion process cannot avoid generating a 'dead layer', further reduces the surface concentration, improves the minority carrier lifetime and the conversion efficiency of the cell, and reduces the production cost of the solar cell.

Owner:TIANWEI NEW ENERGY HLDG

Apparatus for reducing photodiode thermal gain coefficient and method of making same

ActiveUS20110024711A1Semiconductor/solid-state device testing/measurementSolid-state devicesDiffusionSemiconductor materials

An apparatus for reducing photodiode thermal gain coefficient includes a bulk semiconductor material having a light-illumination side. The bulk semiconductor material includes a minority charge carrier diffusion length property configured to substantially match a predetermined hole diffusion length value and a thickness configured to substantially match a predetermined photodiode layer thickness. The apparatus also includes a dead layer coupled to the light-illumination side of the bulk semiconductor material, the dead layer having a thickness configured to substantially match a predetermined thickness value and wherein an absolute value of a thermal coefficient of gain due to the minority carrier diffusion length property of the bulk semiconductor material is configured to substantially match an absolute value of a thermal coefficient of gain due to the thickness of the dead layer.

Owner:GENERAL ELECTRIC CO

Back contact crystalline silicon heterojunction solar cell and preparation method thereof

InactiveCN108321241APrevent heat from spreadingAvoid absorptionFinal product manufacturePhotovoltaic energy generationHeterojunctionMetal electrodes

The invention discloses a back contact crystalline silicon heterojunction solar cell. The solar cell comprises a silicon substrate, a first passivation layer, a second passivation layer, an antireflection film, a metal oxide reflector, a metal electrode and a LiFx film. The first passivation layer is deposited on the upper surface of the silicon substrate. The antireflection film is deposited on the upper surface of the first passivation layer. The second passivation layer is deposited on the lower surface of the silicon substrate. The metal oxide reflector is deposited on one end of the lowersurface of the second passivation layer. The LiFx film is deposited on the other end of the lower surface of the second passivation layer. The metal electrode is evaporated on the lower surface of the metal oxide reflector and the LiFx film. A gap is arranged between the metal oxide reflector and the LiFx film. The metal oxide reflector is the positive electrode of the solar cell. The metal electrode is the negative electrode of the solar cell. The metal oxide reflector is arranged so that the problems of parasitic absorption, auger recombination and "dead layer" caused by the emitter can beavoided.

Owner:SUN YAT SEN UNIV

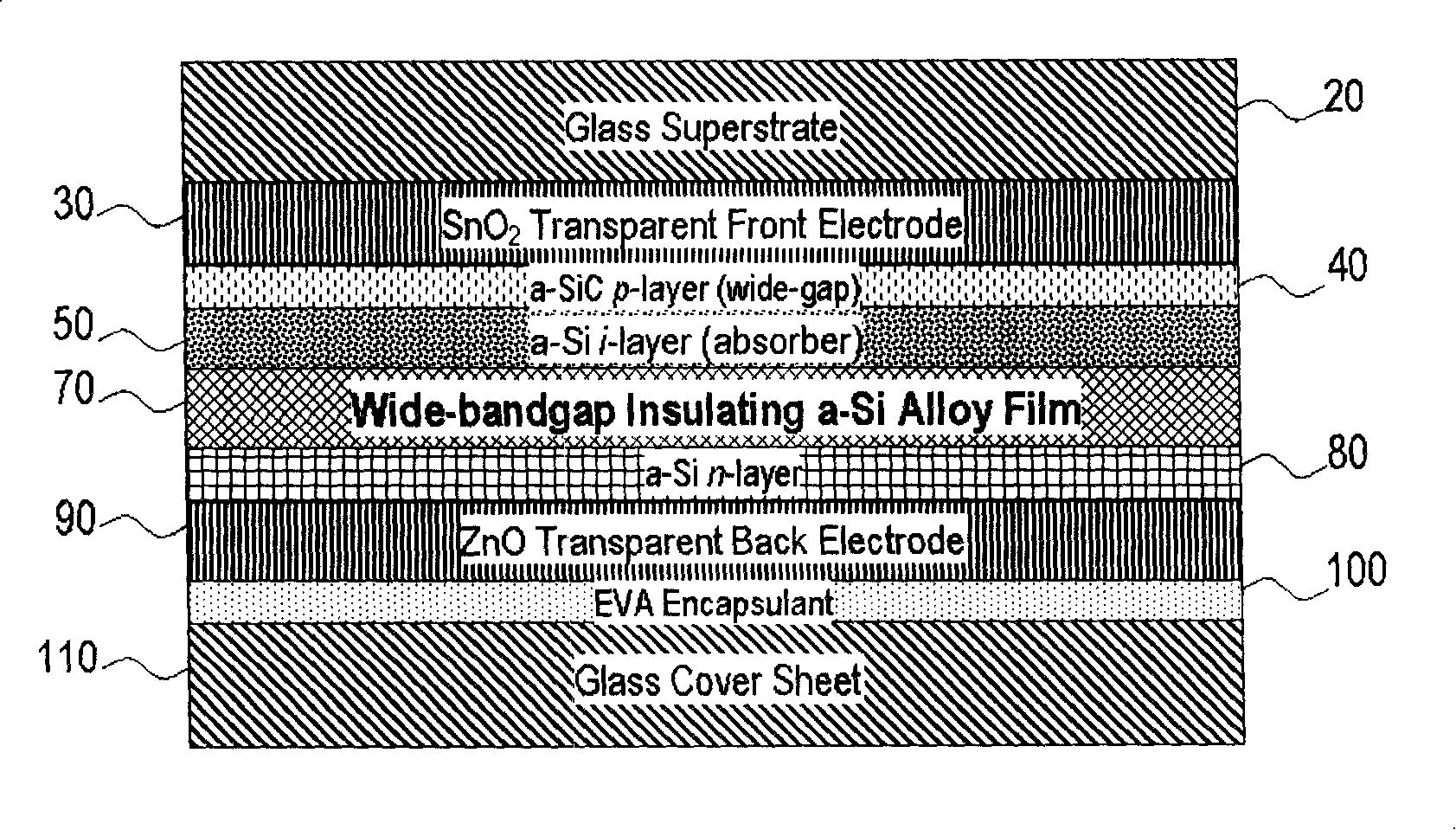

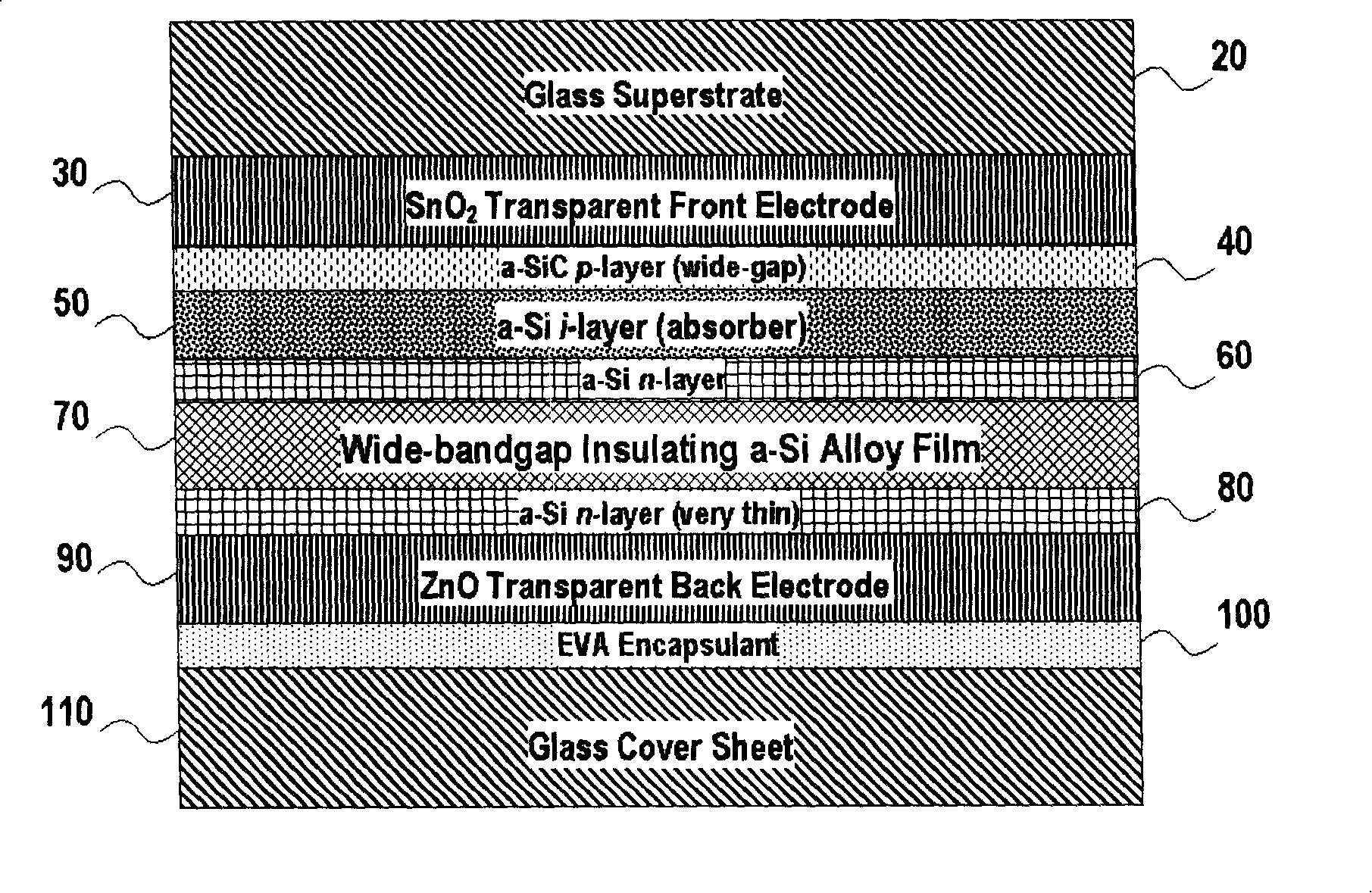

Passivation method for shunt bug of non-crystal silicon film light voltage module

InactiveCN101236999AFewer shunt defectsIncrease output powerClimate change adaptationPhotovoltaic energy generationHigh resistanceAlloy

The present invention provides a method for restraining shunt defects of a p-i-n type large area photovoltaic module based on a hydrogenated amorphous silicon film, and the module comprises a comparatively thin i layer. An amorphous silicon alloy based film having wide band gap and high resistance is arranged between an active photovoltaic layer and a conductive back electrode to perform a barrier function upon the leakage of current. Shunt barrier material with strong light transmittance is a virtual film or is called a 'dead layer', which does not participate to photoelectrical power conversion directly. Shunt passivation films, like amorphous silicon devices which can be massively produced, are capable of realizing simple and quick production in plasma reinforcing chemical vapor deposition devices. The method especially contributes to enhancing the performance, product rate and reliability of perspective type or partial transparent film silicon photovoltaic modules applied to the application of building integrated photovoltaic.

Owner:BEIJING XINGZHE MULTIMEDIA TECH

Removing method of diffusing dead layers of crystalline silicon solar cell

ActiveCN102623568AReduce compoundingImprove photoelectric efficiencyFinal product manufactureSemiconductor devicesHigh concentrationSlurry

Owner:CSI CELLS CO LTD +1

Phosphorus gettering process of silicon chip

InactiveCN101667605BImprove electrical performance parametersIncreased average life expectancyFinal product manufactureSemiconductor devicesEtchingSurface oxidation

The invention relates to a phosphorus gettering process of silicon chips in the manufacture of solar cells, which comprises the following steps: putting sueded silicon chips into a diffusion furnace for pre-deposition, removing a phosphorosilicate glass layer after diffusion, soaking the silicon chips through distributed processing in a hydrofluoric acid solution, and removing oxide layers from the surfaces of the silicon chips; then putting the silicon chips after washing into the diffusion furnace for secondary diffusion processing, taking the silicon chips out from the diffusion furnace after the processing of the secondary diffusion working procedure, cooling the silicon chips to room temperature, and measuring the square resistance of the silicon chips. The invention can effectively decrease heavily doped 'dead layers' and greatly prolong the average minority carrier lifetime of the silicon chips; after the processes including etching, PECVD, silk screen sintering and the like are finished according to the normal process of a cell chip, the average transformation efficiency of the made cell chip is further improved, and the cell chip has better electrical performance parameters.

Owner:无锡尚品太阳能电力科技有限公司

Magnetic head with air bearing surface protection film and manufacturing method thereof

InactiveUS7551398B2Reduce thicknessLow mass densityManufacture head surfaceRecord information storageCarbon filmAir bearing

To promote reduction in thickness of an air bearing surface protective film of a magnetic head, a magnetic head having an air bearing surface protective film consisting only of a thin carbon film while excluding formation of a dead layer by ion incidence as less as possible to the read / write device, and a manufacturing method therefore, are provided. In an embodiment, an air bearing surface protective film of a magnetic head comprises a thin carbon film, in which the mass density a lowermost layer of the air bearing surface protective film on the side of a magnetic device is made lower compared with a thin carbon film constituting other adjacent layers. Further, the manufacturing method comprises deposition under the control of time for the incident angle of ion flow to a substrate to be processed and deposition under the control of time for the ion flow energy to a substrate to be processed.

Owner:WESTERN DIGITAL TECH INC

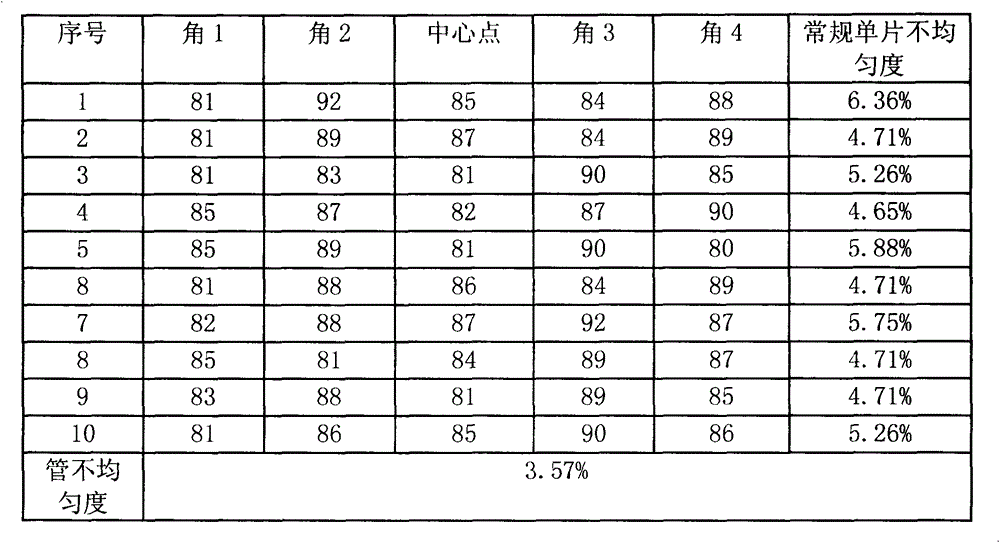

Diffusion low surface concentration efficiency enhancing technology

InactiveCN107086176AReduced bandgap shrinkageReduce concentrationFinal product manufactureSemiconductor/solid-state device manufacturingSurface concentrationDiffusion

The invention relates to the technical field of solar cell panel manufacturing, and particularly relates to a diffusion low surface concentration efficiency enhancing technology comprising the following steps of step 1) chip loading and chip conveying; step 2) temperature rising; step 3) pre-oxidation; step 4) the first time of diffusion; step 5) the first time of propulsion; step 6) the second time of diffusion; step 7) the second time of propulsion; step 8) cooling; and step 9) boat unloading. Pre-oxygen is increased and pre-oxidation is enhanced so that the passivation effect before diffusion can be enhanced; diffusion is optimized and step time and temperature are promoted, and the principle of low temperature and slow promotion is adopted so that the thermal damage caused by high temperature can be reduced; the diffusion N2-POCl3 flow is adjusted, the silicon chip surface phosphorous concentration is reduced, forbidden band contraction of the heavy doping effect is reduced, the dead layer is reduced and surface recombination is reduced; meanwhile, the diffusion step O2 flow is changed, the obstruction of the diffusion step O2 on phosphorous diffusion is reduced, the square resistance uniformity is enhanced and the conversion efficiency is enhanced.

Owner:TONGWEI SOLAR HEFEI

Diffusion post treatment technique of crystalline silicon solar cell

InactiveCN104701425ACharacteristics will not change significantlyPromote decompositionFinal product manufactureSemiconductor/solid-state device manufacturingPartial oxidationMicroscopic scale

The invention discloses a diffusion post treatment technique of a crystalline silicon solar cell. After furnace tube diffusion, oxidation treatment is conducted on a silicon wafer through light rapid heat treatment, and a layer of oxidation film is formed on the surface of the silicon wafer. According to the diffusion post treatment technique of the crystalline silicon solar cell, diffused peroxidation is adopted, a serious dead layer can be changed into an oxide layer, and in the process of subsequent wet chemical cleaning, the oxide layer can be corroded and stripped by HF, so that partial diffusion dead layer is effectively removed, and recombination of minority carriers on the surface of the cell can be reduced; meanwhile, by means of the peroxidation treatment after the furnace tube diffusion, the concentration distribution of phosphorus or boron which is locally uneven in the microscopic scale can be improved, the uniformity of p-n knots is improved, and the cell efficiency is improved. According to the diffusion post treatment technique of the crystalline silicon solar cell, low temperature quick oxidation is adopted, an oxidation layer can be formed in a very short period, the defect does not occur in the silicon wafer, and the phosphor doping curve can not be affected obviously.

Owner:CHANGZHOU SHICHUANG ENERGY CO LTD

Maskless etch-back method applicable to selective emitter solar cell

ActiveCN102709403AImprove surface passivation qualityReduce compoundingFinal product manufactureSemiconductor devicesSolar cellSilicon

The invention relates to a maskless etch-back method applicable to a selective emitter solar cell. The maskless etch-back method is characterized in that silicon slices with high / low doping concentration difference are formed by a selective emitter etching-back method, and doped layers on the surfaces of high / low doping-concentration areas are removed at the same time; the etch-back target sheet resistance of the high doping concentration area is 30-60OPS, and the sheet resistance of the low doping concentration area is 80-120OPS. Thus, the high-doping concentration area is etched back to effectively reduce a surface dead layer, so the surface passivation quality of a non-metal coverage area is improved under the condition that metal-semiconductor contact is not affected, the recombination of the surface and an emission layer is reduced and shortwave photon response is improved, so as to improve the performance of the cell.

Owner:SUZHOU TALESUN SOLAR TECH CO LTD

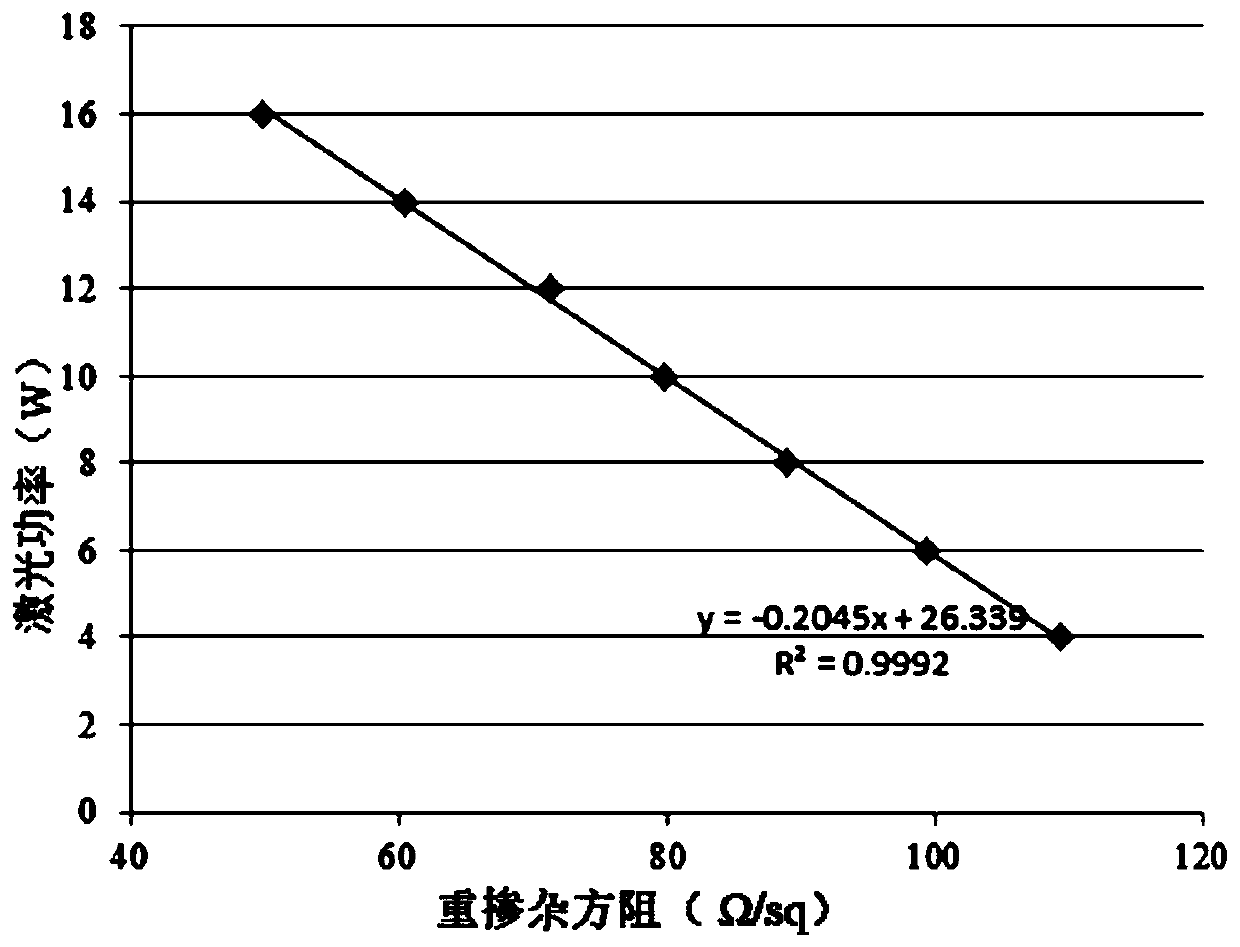

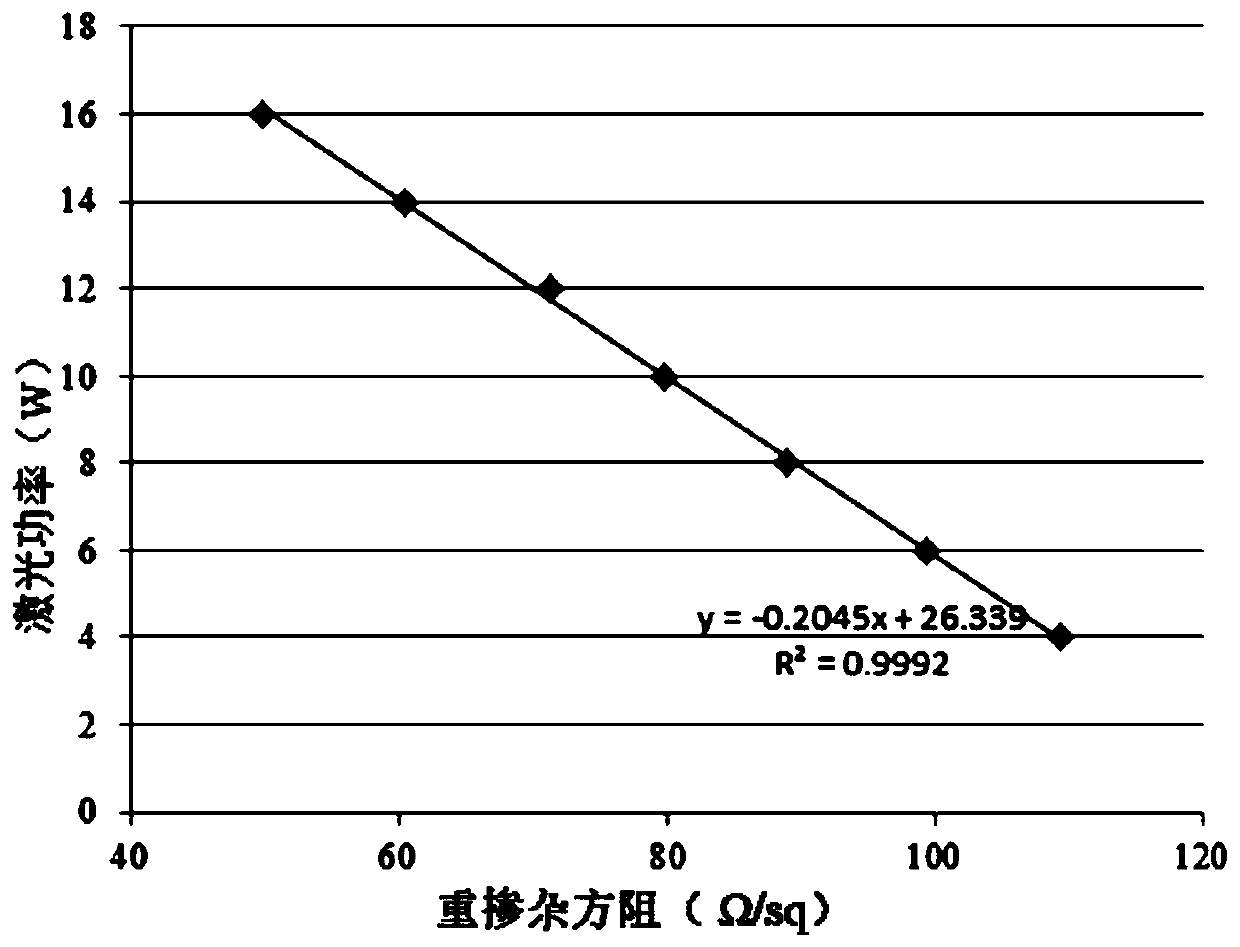

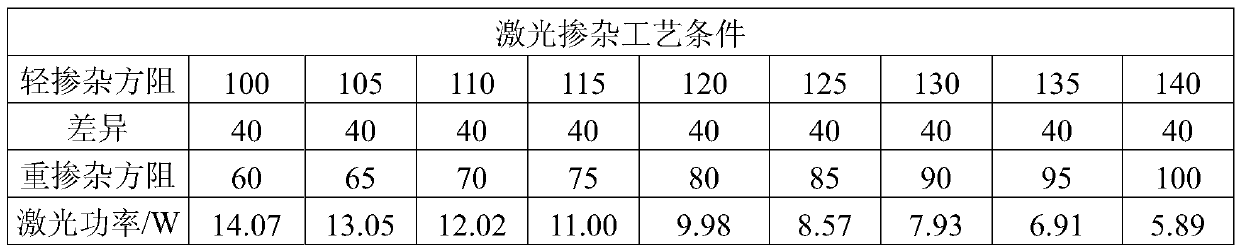

Selective emitter, preparation method thereof, solar cell using selective emitter, and application of solar cell

ActiveCN109713064AIncrease the open circuit voltageIncrease short circuit currentPhotovoltaic energy generationSemiconductor devicesSolar cellProcess conditions

The invention provides a selective emitter, a preparation method of the selective emitter, a solar cell using the selective emitter and an application of the solar cell. The difference between lightly-doped sheet resistance of a light receiving region and heavily-doped sheet resistance of a non-light receiving region of the selective emitter is a fixed value, and the fixed value is 40 + / -10 ohm / sq. The open-circuit voltage and the short-circuit current can be improved and the dead layer effect can be reduced by preparing the selective emitter, so that the light conversion efficiency is improved. The preparation method of the selective emitter is low in price, high in yield, simple in process condition, easy to operate and suitable for industrial large-scale production application. The prepared solar cell has high light conversion efficiency, greatly reduces the production cost, and can be applied to the field of photovoltaics as an energy cell.

Owner:YANCHENG CANADIAN SOLAR INC +1

Photoelectric detector for 650nm optical fiber communication and its producing method

This invention relates to a photoelectric detector use in 650nm fiber communication compose of four layers of heavy doped p+ surface layer / P layer / light doped N- epitaxial layer / heavy doped N+ substrate in following steps: growing a material, oxidizing, photo etching the oxide film, diffusing the P type, evaporating the photo etched Al, forming an electrode with alloy, evaporating the O photo etched anti-reflection film and evaporating the back electrodes with good property of 1-v, small dark current and high light response. The heavy doped p+ surface layer is thin to reduce the 'dead layer' thickness and enables most part of incident light to pass through the p+ layer and inject into P layer and one layer to generate effective photo-generated carriers to improve the performance of the emitting region and increase the short wave quantum efficiency.

Owner:XIAMEN SAN U OPTRONICS

Technology for improving short wave responsibility of semiconductor photoelectric detector

InactiveCN102376816AImprove responsivenessFinal product manufactureSemiconductor devicesEffective surfacePhotovoltaic detectors

The invention belongs to the technical field of a semiconductor photoelectric detector, relating to a technology for improving short wave responsibility of the semiconductor photoelectric detector. The technology comprises the following steps of: adding a transparent conductive thin film layer on the surface of a transparent insulating medium mask layer on the front surface of the semiconductor photoelectric detector, so that a novel structure of the photoelectric detector of a TCOS structure is formed by the transparent conductive thin film layer (TC), the mask layer (O) on the front surface of the detector and the semiconductor (S) below the mask layer; and applying a voltage to the transparent conductive mask layer as a working boost voltage of the semiconductor photoelectric detector to change the surface potential of the semiconductor, a surface energy band and a surface space charge area, reduce the effective surface recombination rate of photo-production minority carriers near the surface of the semiconductor, and remove a 'dead layer' area. Therefore, most of the photo-production minority carriers of the short waves are collected to be a photo-production current, and the short wave responsibility of the semiconductor photoelectric detector is improved. In particular, the technology can be used for effectively improving the short wave responsibility of a high-silicon semiconductor blue-green photoelectric detector or blue-violet photoelectric detector.

Owner:石郧熙