Process for manufacturing emitter of solar cell

A solar cell and manufacturing process technology, applied in sustainable manufacturing/processing, circuits, electrical components, etc., to improve conversion efficiency, reduce production costs, and be simple and easy to operate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

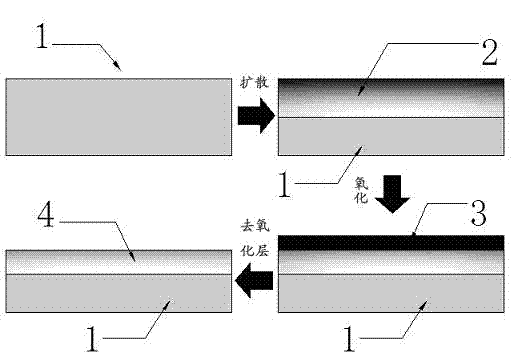

[0043] Such as figure 1 shown.

[0044] Step A: using a diffusion process to form a PN junction on the surface of the substrate silicon wafer 1 to form a surface impurity distribution layer 2;

[0045] Step B: performing oxidation treatment on the surface impurity distribution layer 2 in step A, and rapidly growing a uniformly distributed oxide layer 3 on the surface of the surface impurity distribution layer 2;

[0046] Step C: removing the oxide layer 3 in step B.

Embodiment 2

[0048] Such as figure 1 shown.

[0049] Step A: using a diffusion process to form a PN junction on the surface of the substrate silicon wafer 1 to form a surface impurity distribution layer 2; the diffusion process is: select POCL 3 Diffusion from a liquid source. The POCL 3 The method of liquid source diffusion is: use high-purity nitrogen to pass into liquid POCL 3 Bottom bubbling such that the bubbling carries POCL 3 Pass into the high-temperature furnace tube to react with oxygen and silicon wafers to form P atoms that diffuse into the surface of silicon wafers to form N-type layers.

[0050] Step B: Oxidize the surface impurity distribution layer 2 in step A, and rapidly grow a uniformly distributed oxide layer 3 on the surface of the surface impurity distribution layer 2; the oxidation treatment method is high temperature wet oxygen oxidation. The process of high-temperature wet oxygen oxidation is as follows: the substrate silicon wafer 1 treated in step A is plac...

Embodiment 3

[0053] The difference between this embodiment and implementation 1 and embodiment 2 is:

[0054] The square resistance of the base silicon wafer after step A is 5 ohm-30 ohm lower than that of the base silicon wafer after step B.

[0055] The square resistance of the base silicon wafer 1 after step B is in the range of 60ohm-120ohm.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More