Silicon carbide MOSFET device and preparation method thereof

A silicon carbide and device technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as large leakage current of MOSFETs, increasing cell area of silicon carbide MOSFET devices, and large Schottky contact area area. , to improve the freewheeling capacity, prevent the Schottky contact area from being too large, and reduce the production cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

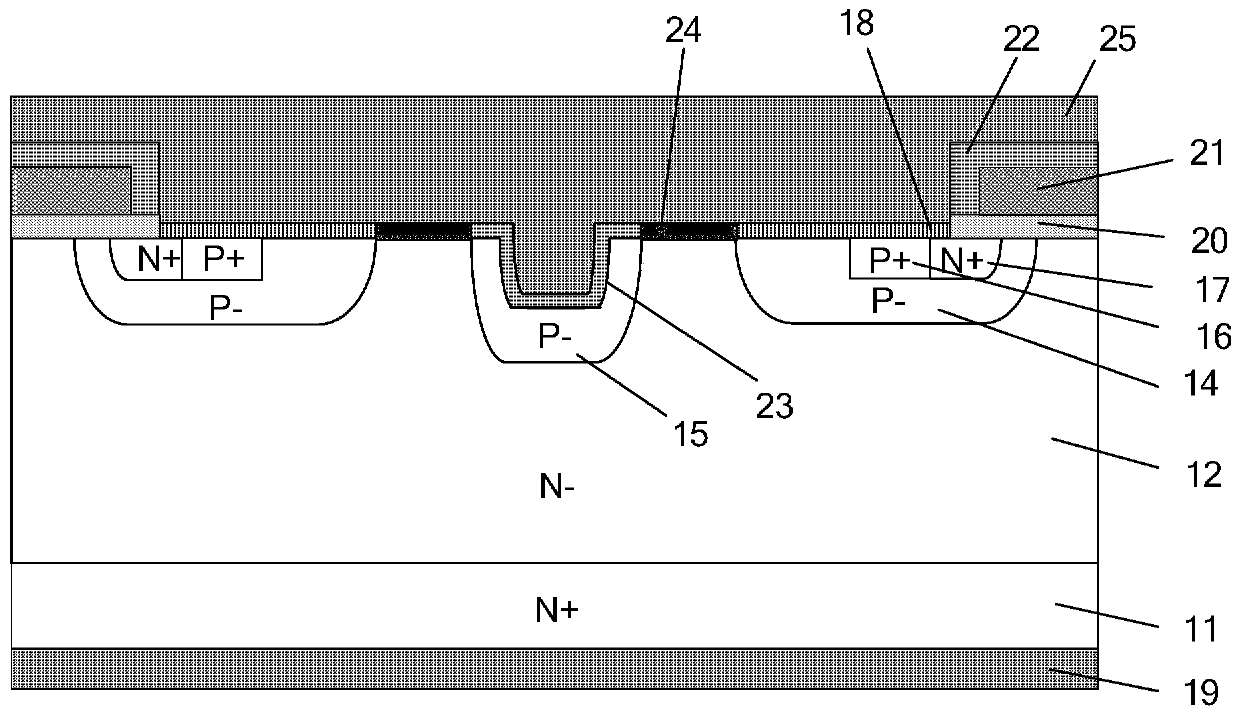

[0052] This embodiment provides a silicon carbide MOSFET device integrating a trench junction barrier Schottky diode, and its structural cross-sectional schematic diagram is as follows figure 1 shown.

[0053] The device includes a drain electrode from bottom to top (the drain electrode includes figure 1 Metal shown in 19), N+ substrate 11 and N- epitaxial layer 12. The N-epitaxial layer 12 has a first P-well region 14, and the first P-well region 14 has a P+ region 16 and an N+ region 17 (the depth of the first P-well region 14 is greater than the depth of the N+ region 17 and the P+ region 16). The number of the first P-well region 14 is more than two, and usually can be more.

[0054] The device further includes: a first metal 18 forming a first ohmic contact with the upper surface of the P+ region 16 and part of the upper surface of the N+ region 17 . In addition, the first metal 18 also forms a corresponding good ohmic contact with the upper surface of part of the firs...

Embodiment 2

[0083] This embodiment provides a silicon carbide MOSFET device integrating a trench junction barrier Schottky diode, and its structural cross-sectional schematic diagram is as follows Figure 7 shown.

[0084] The device includes a drain electrode from bottom to top (the drain electrode includes Figure 7 Metal 39 shown in), N+ substrate 31 and N- epitaxial layer 32; N- epitaxial layer 32 has a first P- well region 34, and there are P+ region 36 and N+ region 37 in the first P-well region 34 ( At this time, the depth of the first P-well region 34 is greater than the depth of the N+ region 37 and the P+ region 36). The number of the first P-well regions 34 is more than two.

[0085] The device also includes: a first metal 38, the first metal 38 forms a first ohmic contact with the upper surface of the P+ region 36 and part of the upper surface of the N+ region 37 (the first metal 38 also covers part of the first P- well region 34 upper surface, but the contact between them ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More