Silicon carbide UMOSFET device integrated with TJBS

A silicon carbide and device technology, used in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problem of weak internal freewheeling capability of silicon carbide UMOSFET devices, increasing the complexity and cost of circuit systems, and incapable of device freewheeling. and other problems, to achieve the effect of improving the avalanche resistance, improving the breakdown characteristics, and improving the performance of the device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

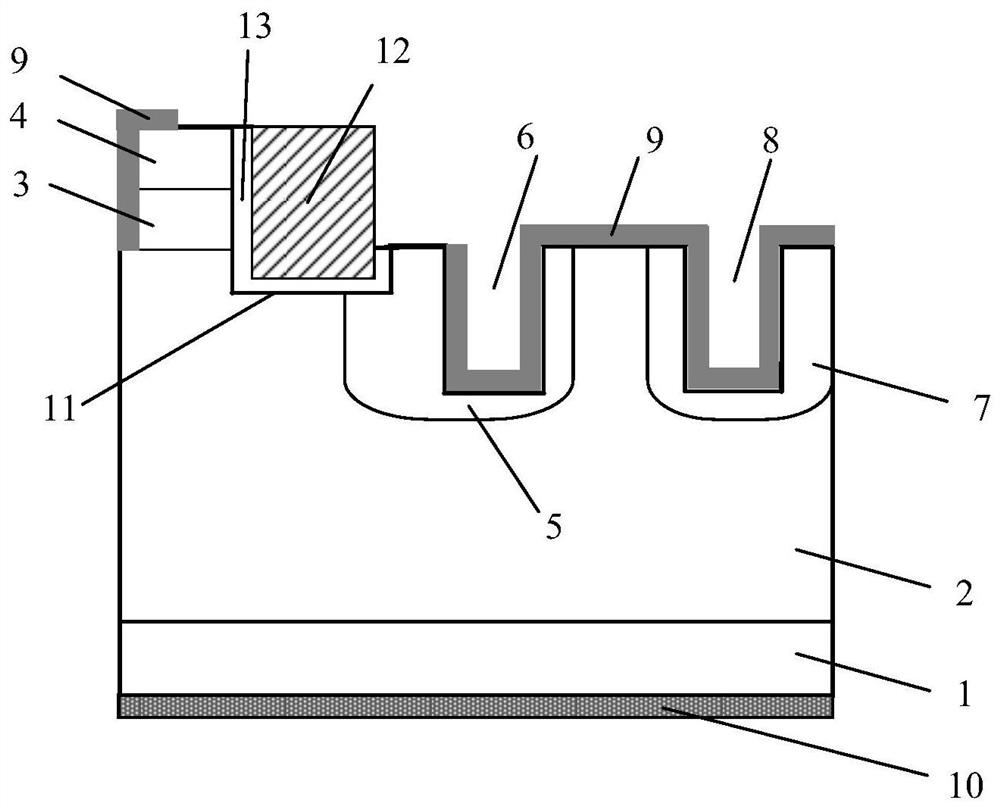

[0036] See figure 1 , figure 1 It is a schematic structural diagram of a silicon carbide UMOSFET device integrating TJBS (Trenched Junction Barrier schottky) provided by an embodiment of the present invention. As shown in the figure, the silicon carbide UMOSFET device integrating TJBS in this embodiment includes:

[0037] N+ substrate region 1;

[0038] The N- epitaxial region 2 is arranged on the N+ substrate region 1;

[0039] The P-well region 3 is arranged on the N-epitaxial region 2;

[0040] The N+ injection region 4 is arranged on the P-well region 3;

[0041] The first P+ implantation region 5 is located inside the N- epitaxial region 2, and the first P+ implantation region 5 is provided with a first trench 6;

[0042] The second P+ implantation region 7 is located inside the N- epitaxial region 2 and is spaced apart from the first P+ implantation region 5, and a second trench 8 is arranged in the second P+ implantation region 7;

[0043] The gate is arranged adj...

Embodiment 2

[0066] See Figure 2a-Figure 2i , Figure 2a-Figure 2i It is a process schematic diagram of a silicon carbide UMOSFET device integrating TJBS provided by an embodiment of the present invention, and the preparation method includes the following steps:

[0067] Step a: Form N- epitaxial region 2 on N+ substrate region 1 by means of epitaxial growth, such as Figure 2a shown.

[0068] First, the thickness is 350 μm, and the doping concentration is 5×10 18 cm -3 The SiC substrate was cleaned by RCA standard, and then epitaxially grown on the N+ substrate region 1 with a thickness of 10 μm and a doping concentration of 6×10 15 cm -3 N-Epi region 2.

[0069] Step b: Etching to form a thinner N-epitaxial region 2, such as Figure 2b shown.

[0070] A mask layer is deposited on the upper surface of the N- epitaxial region 2, and a mask pattern is formed by a photolithography etching process, and then etched by an ICP etching method such as Figure 2b The N-epitaxial region 2 ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Depth | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

| Depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More