Patents

Literature

100results about How to "Reduce peak electric field" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

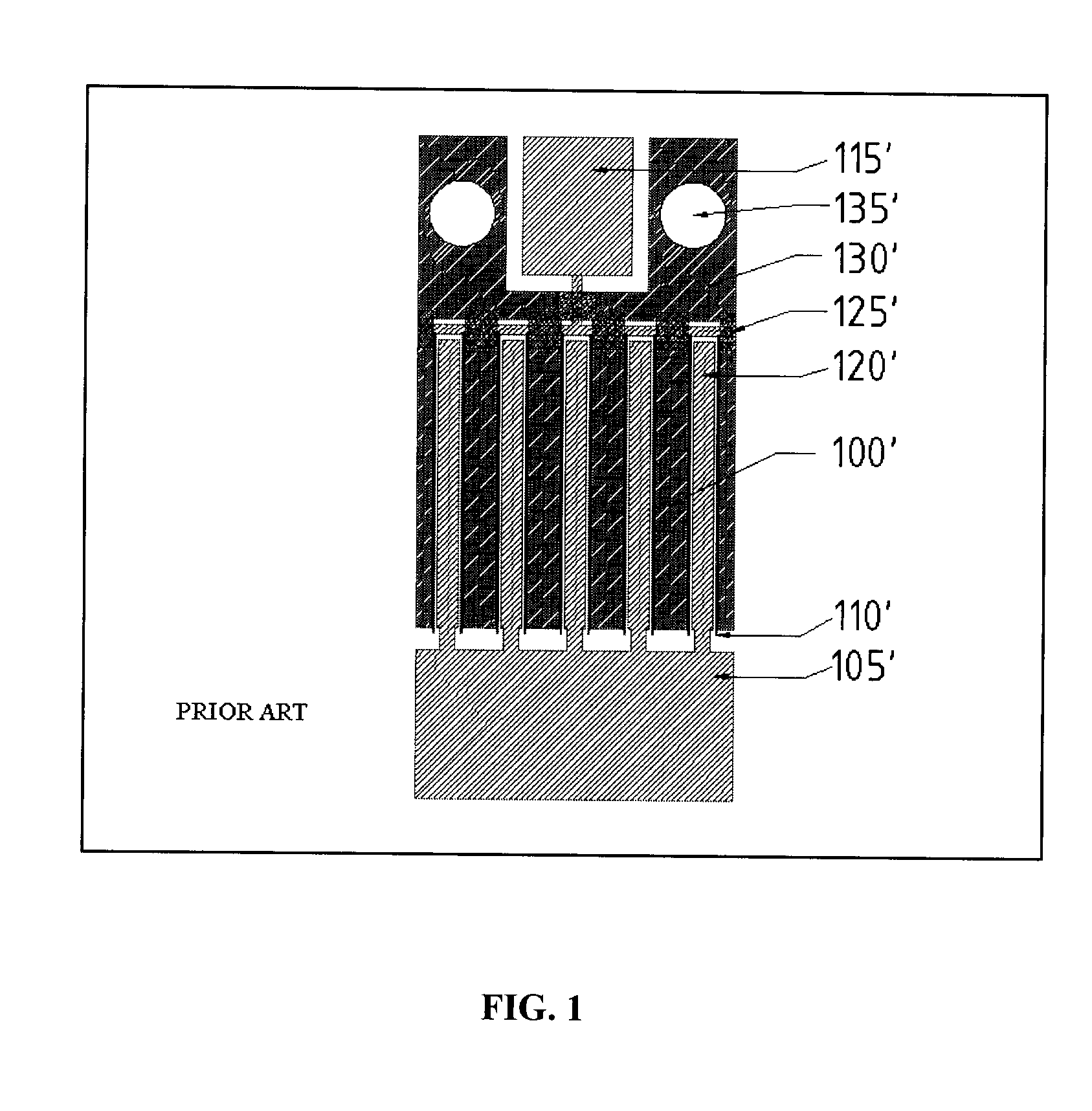

High voltage semiconductor devices

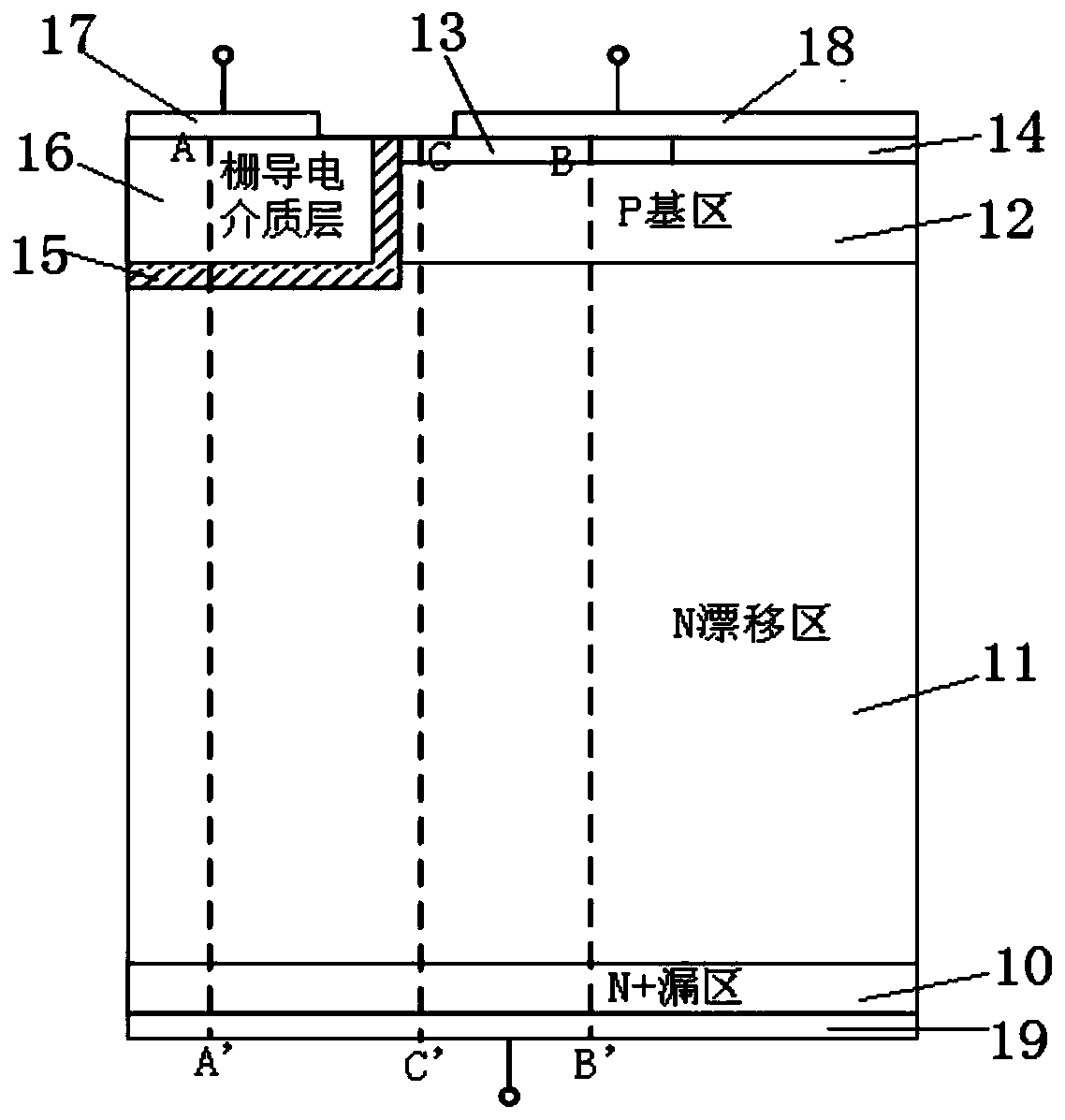

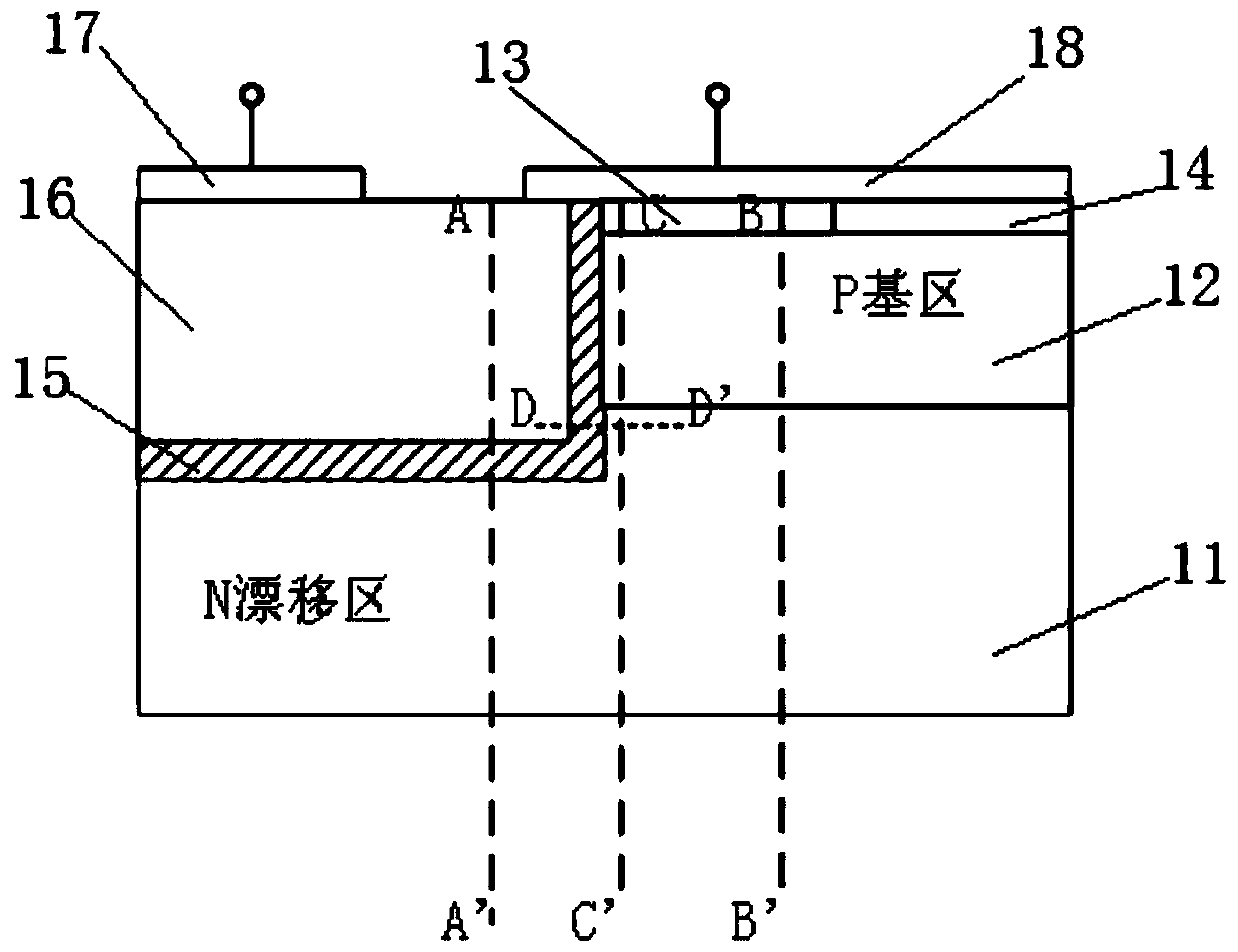

InactiveUS20170243937A1Well formedReduce peak electric fieldTransistorThyristorDevice materialEngineering

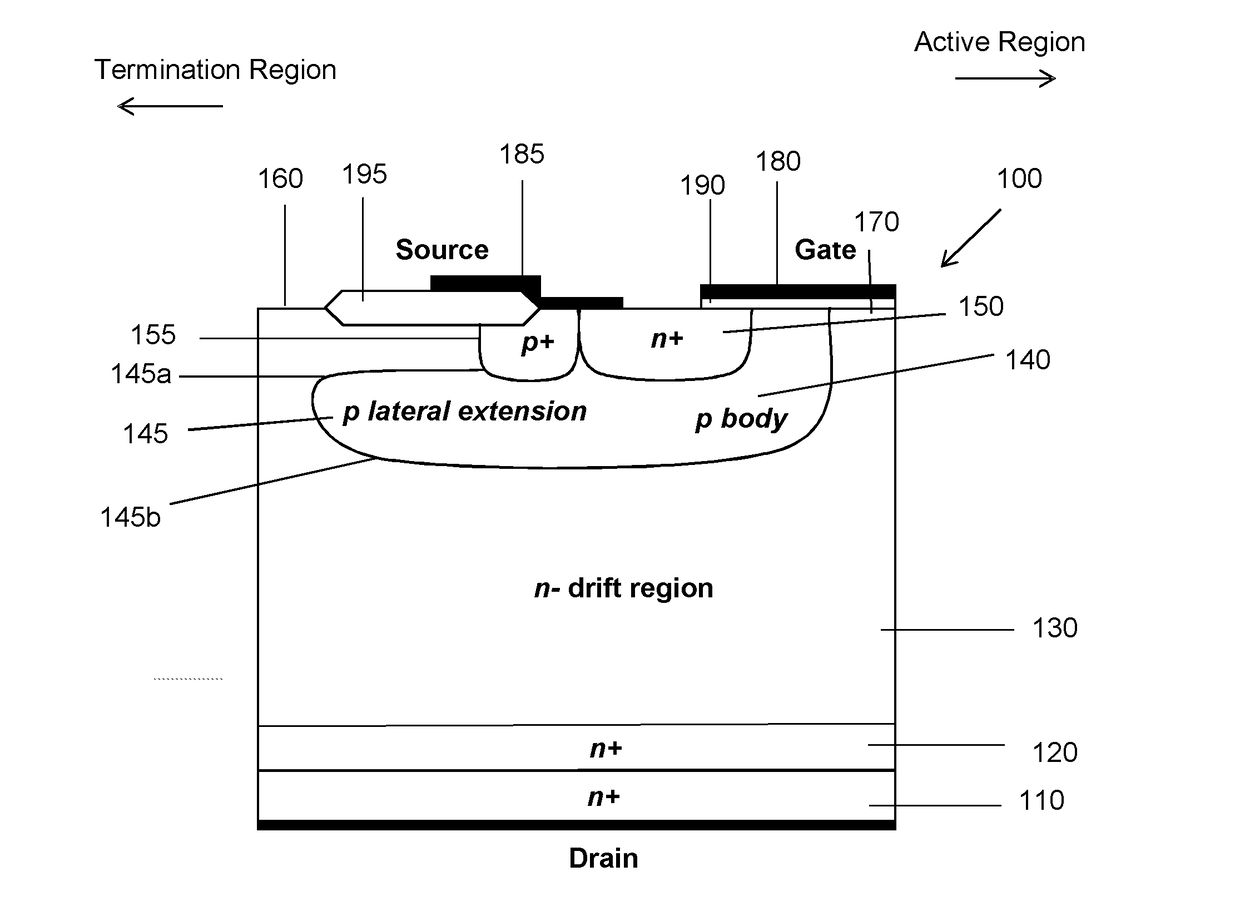

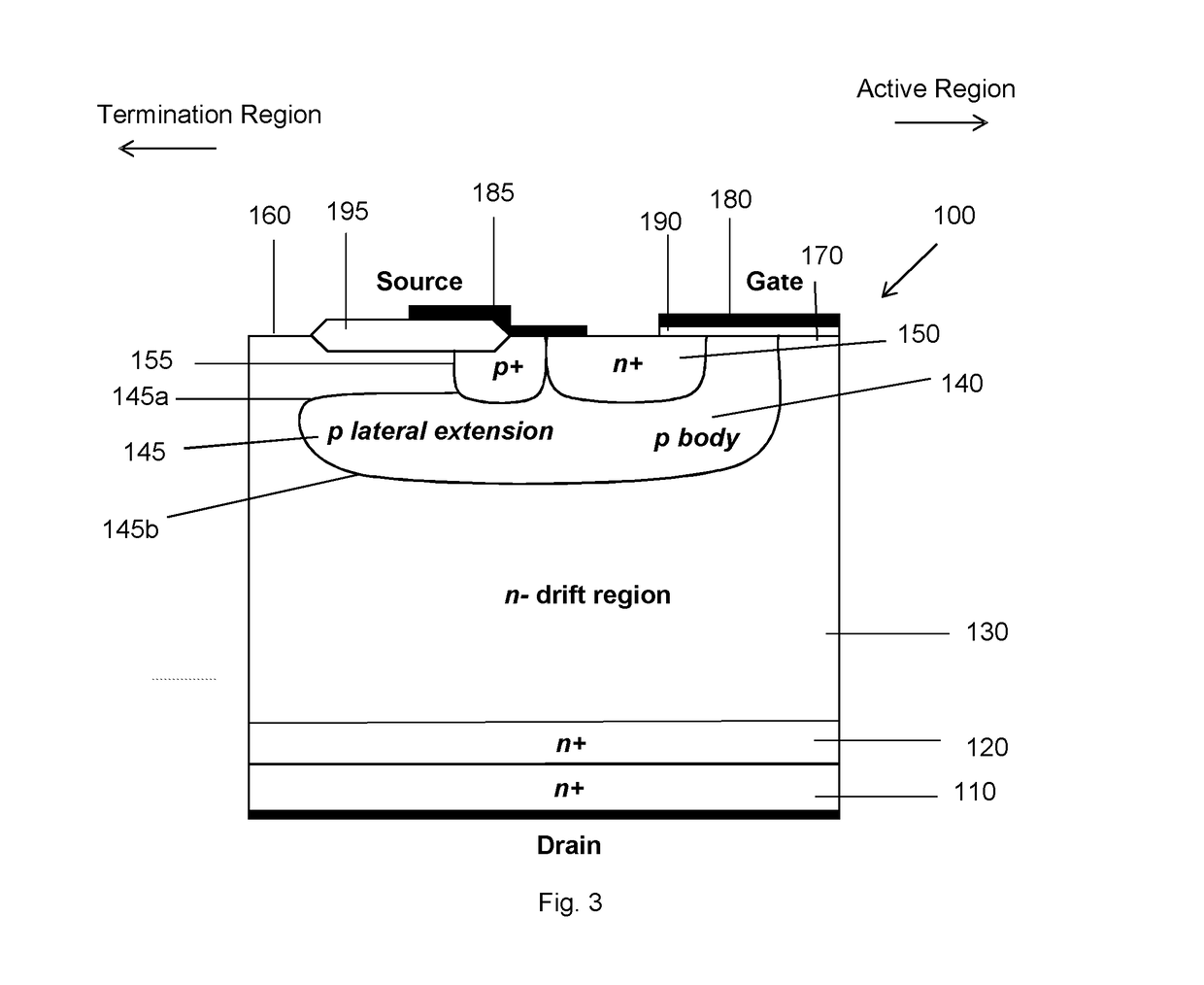

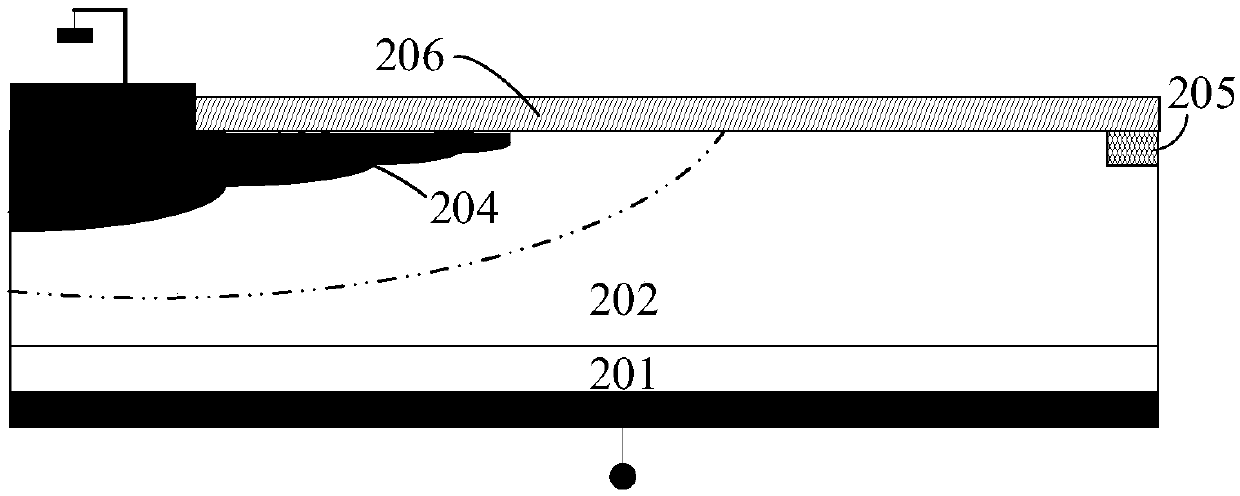

We disclose a high voltage semiconductor device comprising a semiconductor substrate of a second conductivity type; a semiconductor drift region of the second conductivity type disposed over the semiconductor substrate, the semiconductor substrate region having higher doping concentration than the drift region; a semiconductor region of a first conductivity type, opposite to the second conductivity type, formed on the surface of the device and within the semiconductor drift region, the semiconductor region having higher doping concentration than the drift region; and a lateral extension of the first conductivity type extending laterally from the semiconductor region into the drift region, the lateral extension being spaced from a surface of the device.

Owner:ANVIL SEMICON

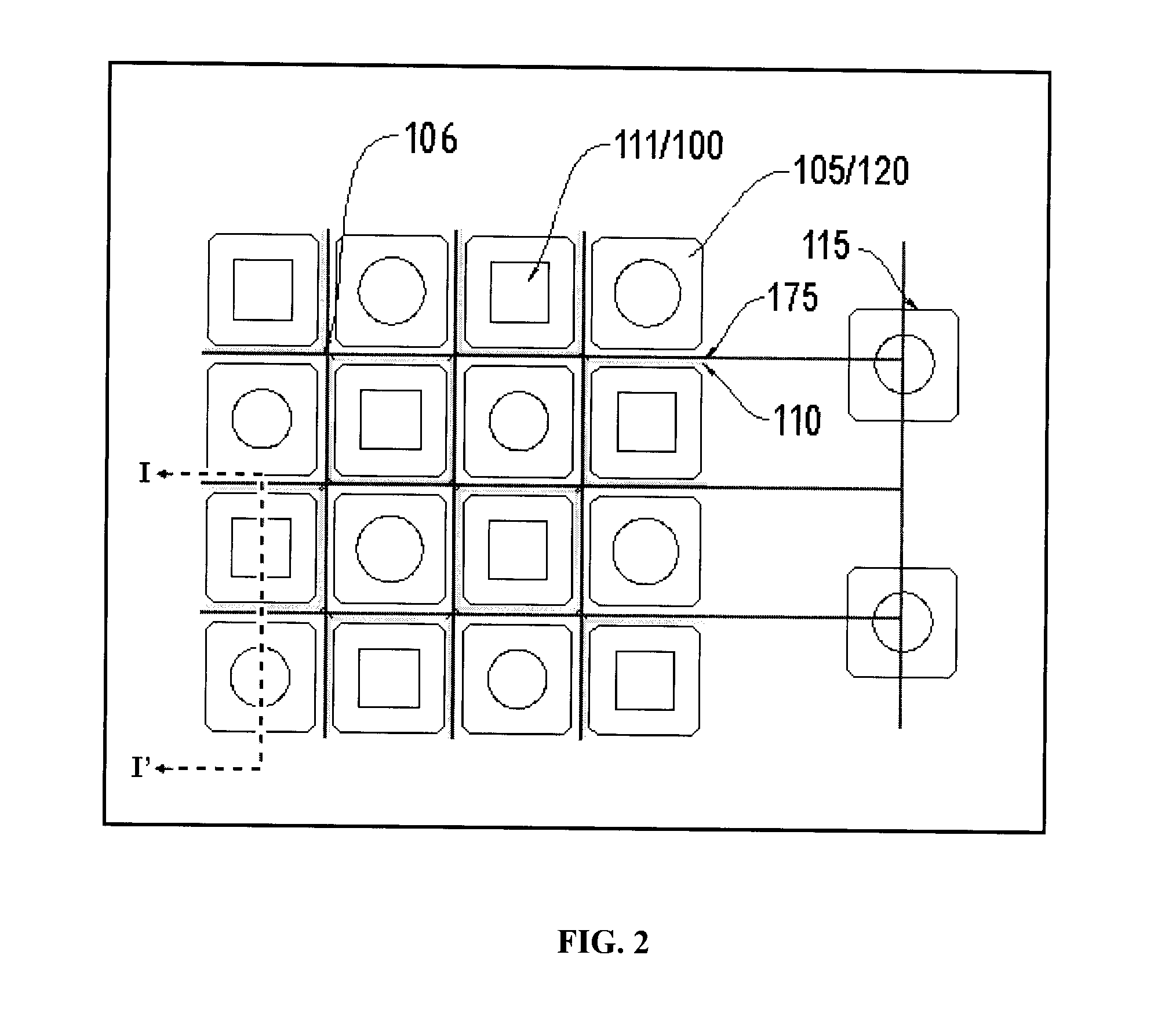

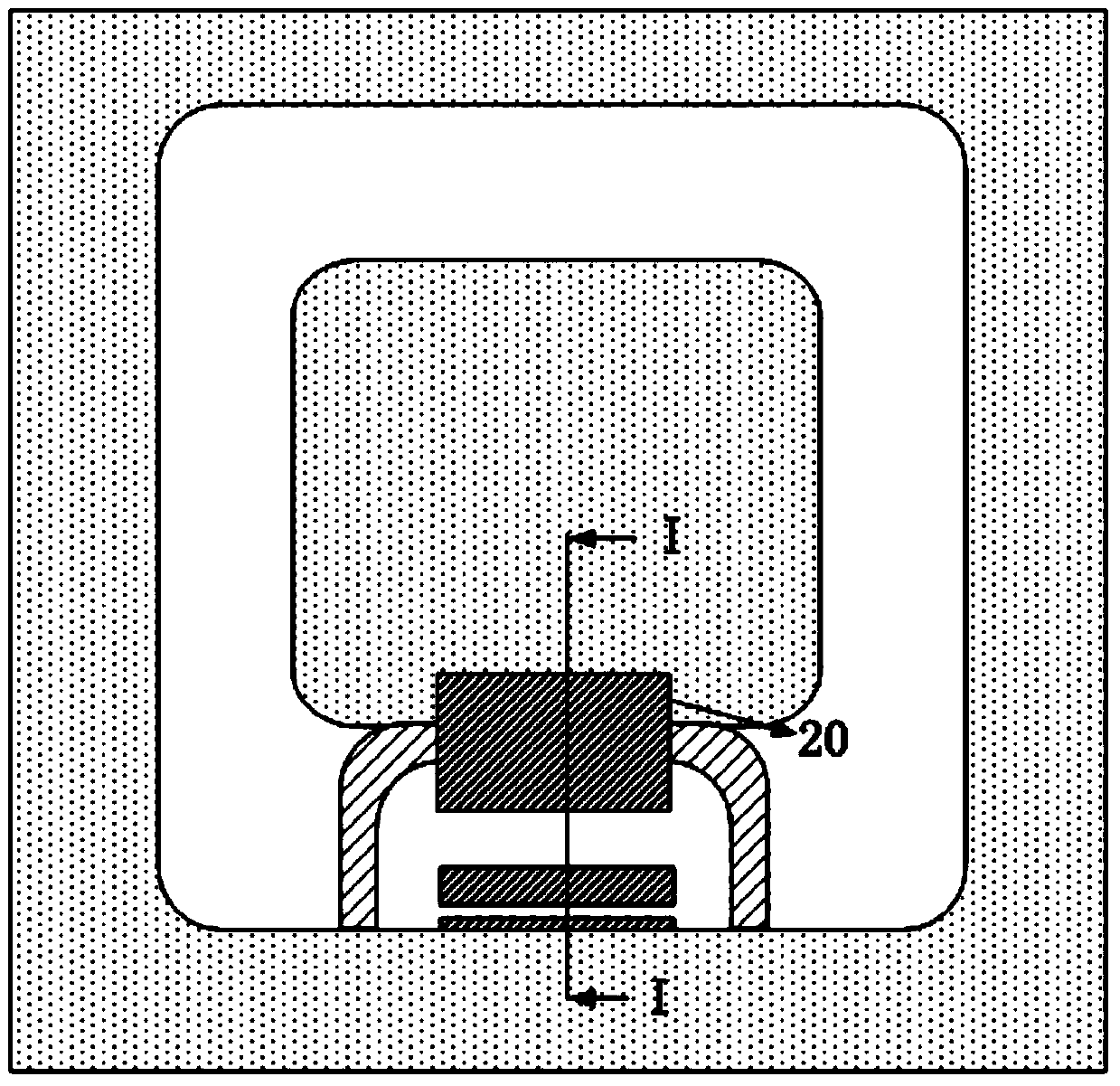

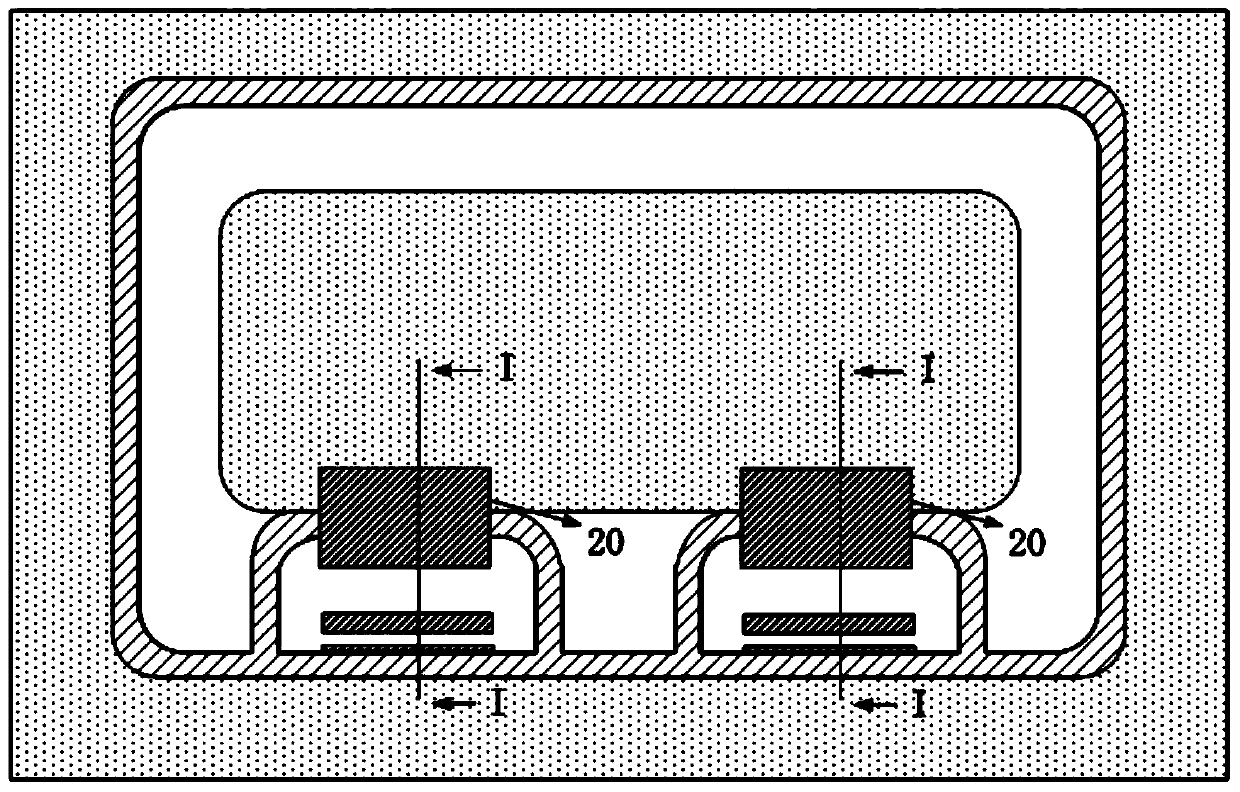

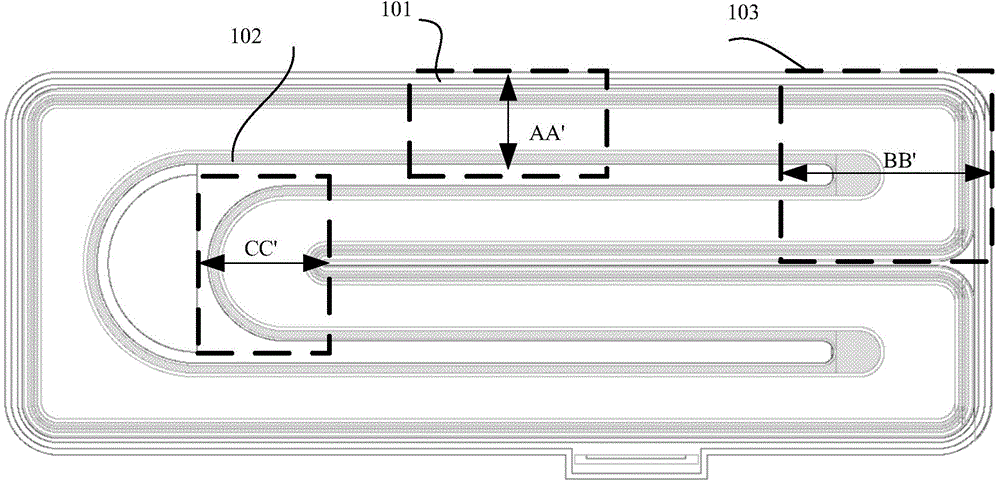

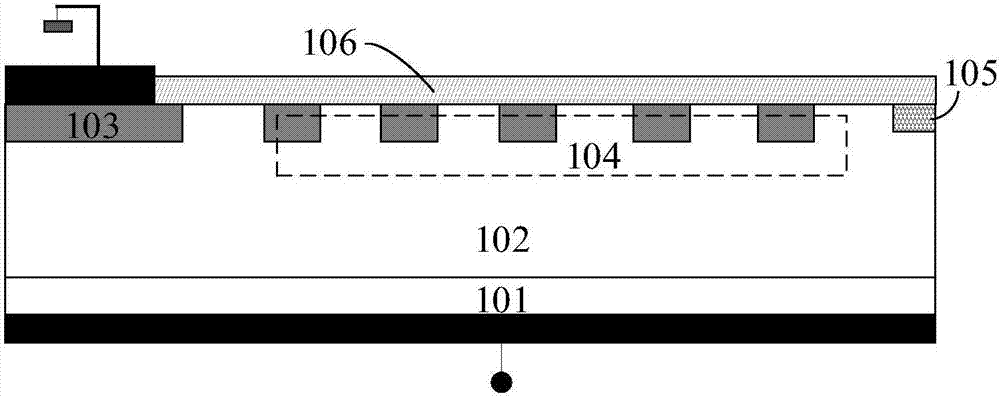

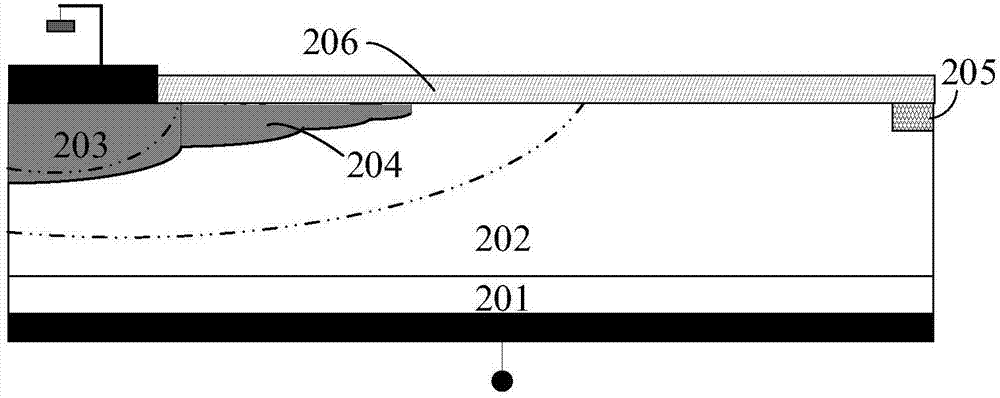

Island matrixed gallium nitride microwave and power switching transistors

ActiveUS20120138950A1Effective area ratioLarge gate widthTransistorSolid-state devicesMicrowavePower flow

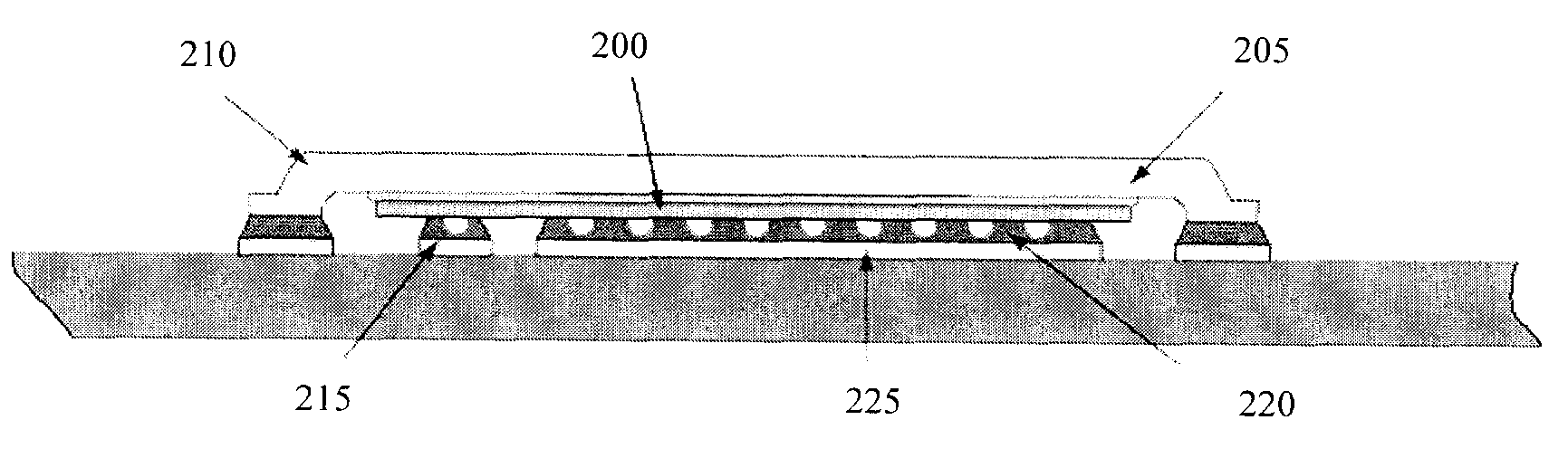

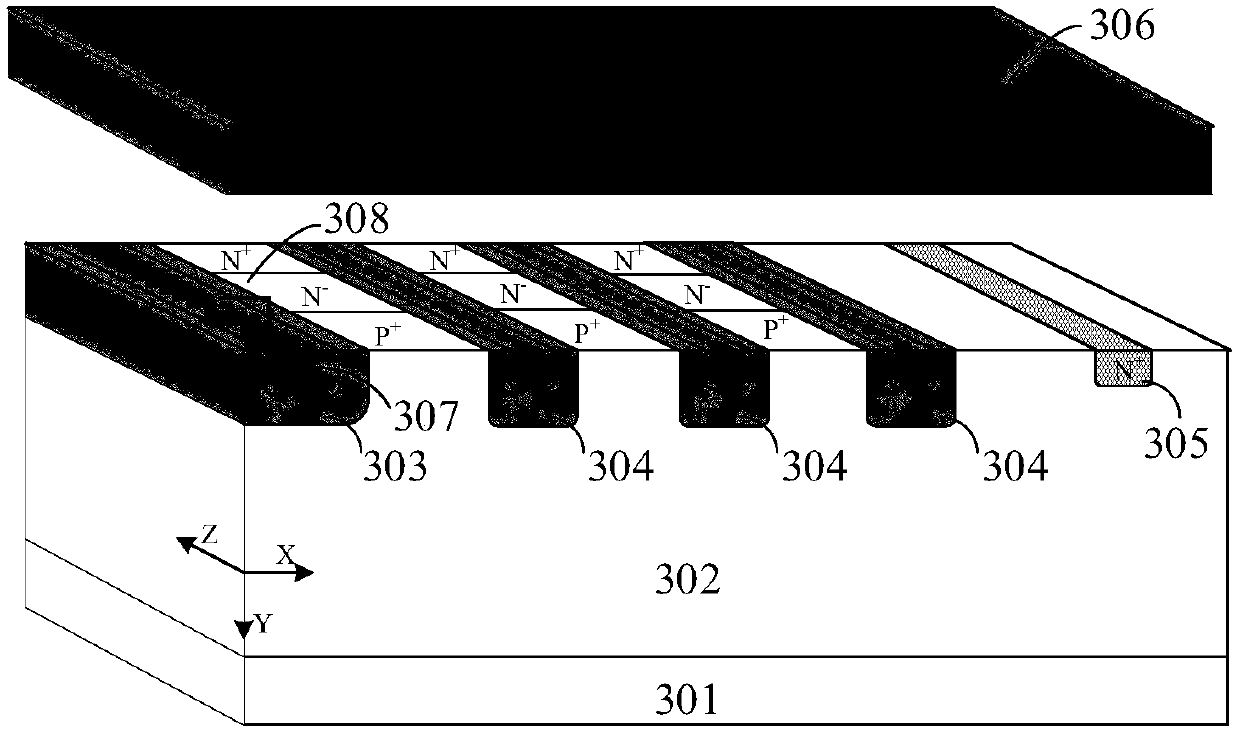

A gallium nitride (GaN) device that has greatly superior current handling ability per unit area than previously described GaN devices. The improvement is due to improved layout topology. The layout scheme, which uses island electrodes rather than finger electrodes, is shown to increase the active area density over that of conventional interdigitated structures. Ultra low on resistance transistors can be built using the island topology. Specifically, the present invention, which uses conventional GaN lateral technology and electrode spacing, provides a means to enhance cost / effective performance of all lateral GaN structures.

Owner:GAN SYST

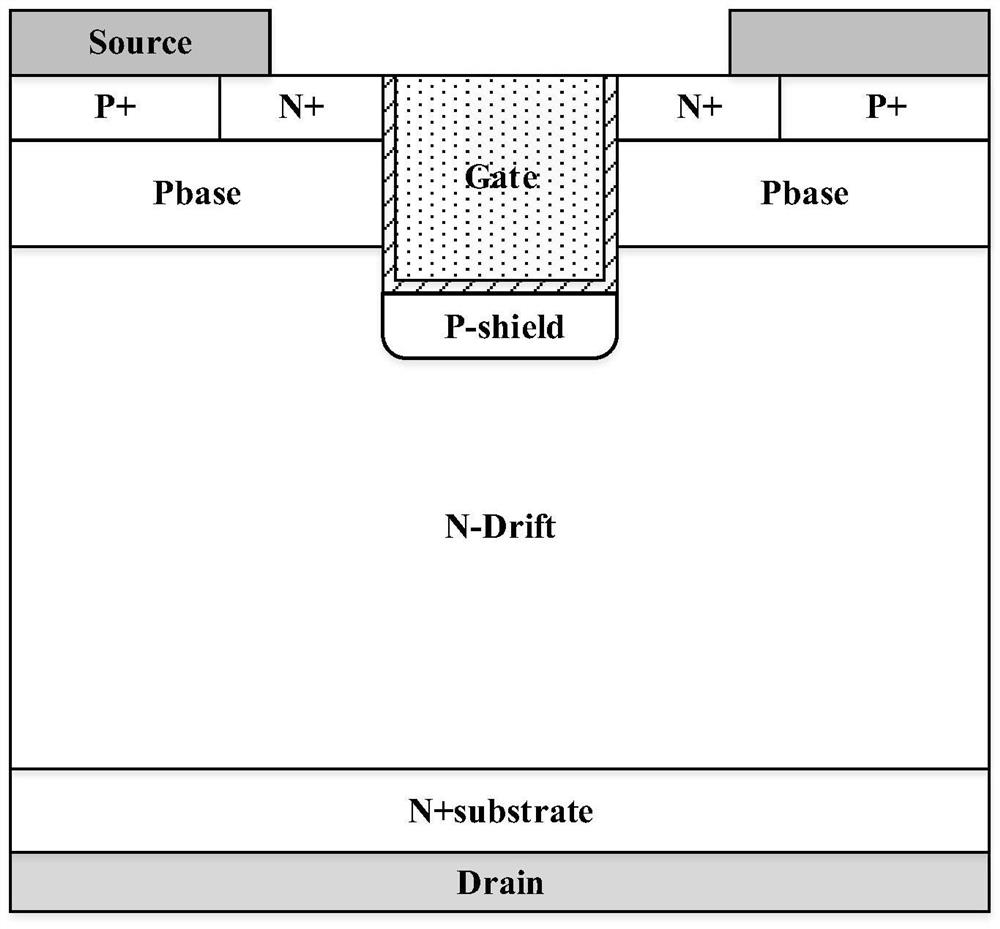

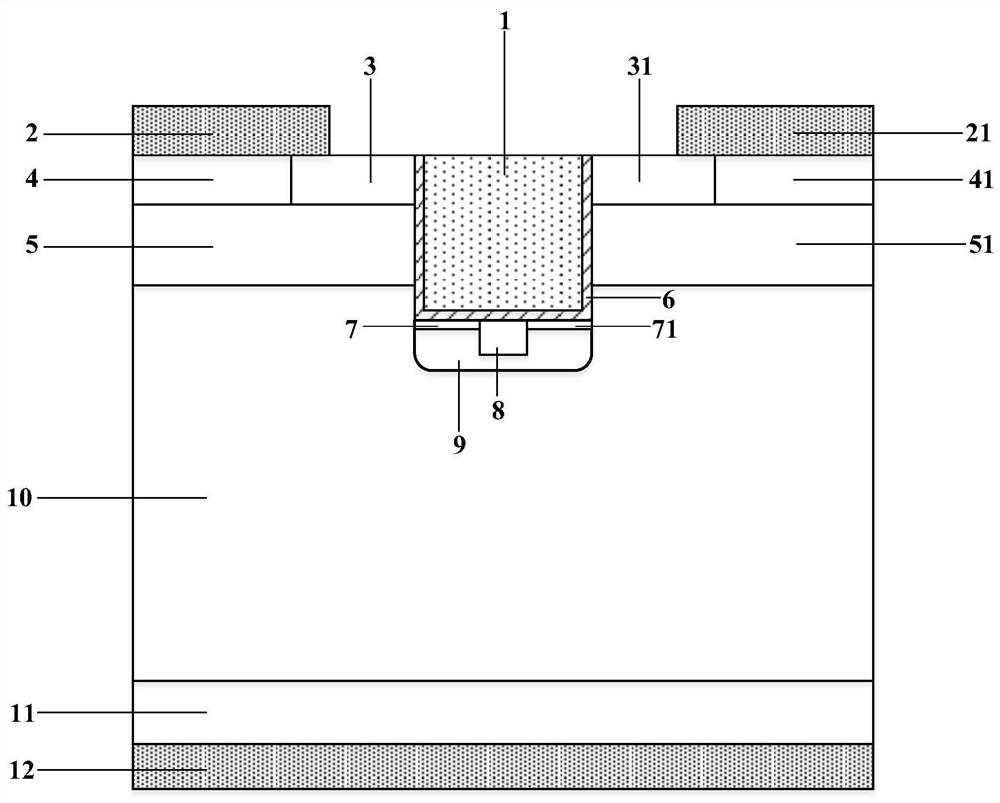

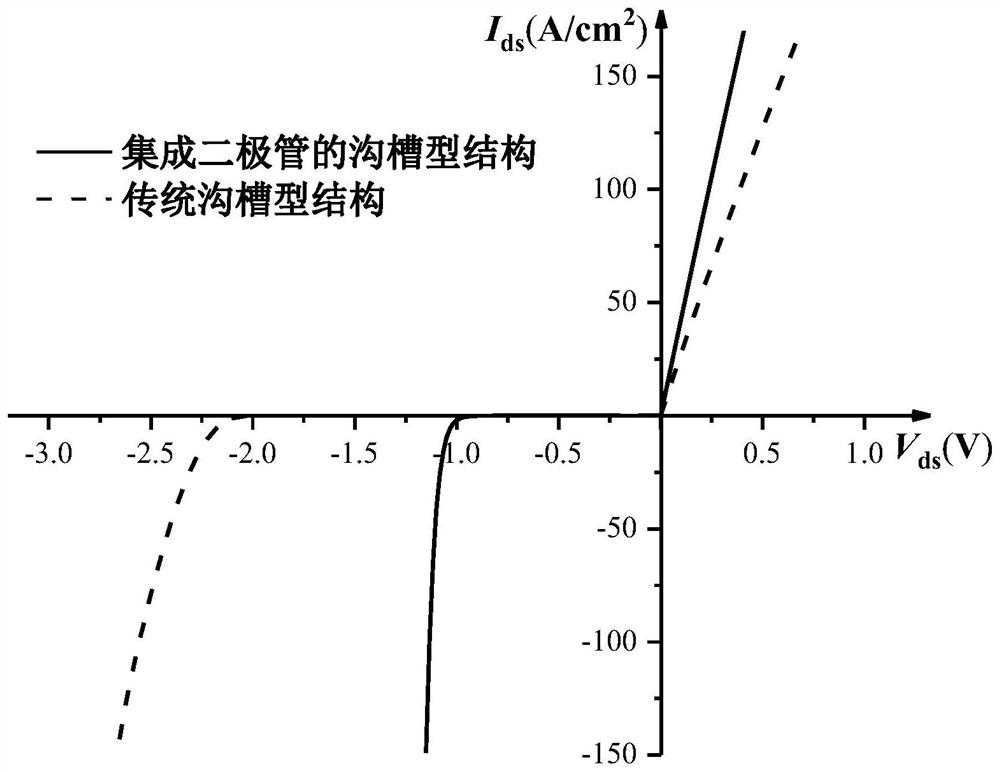

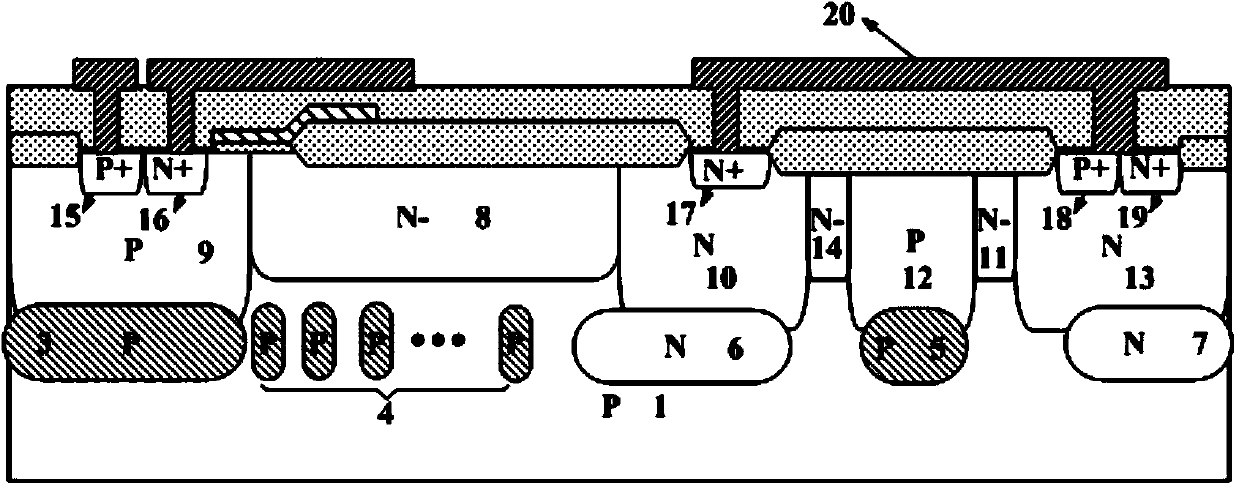

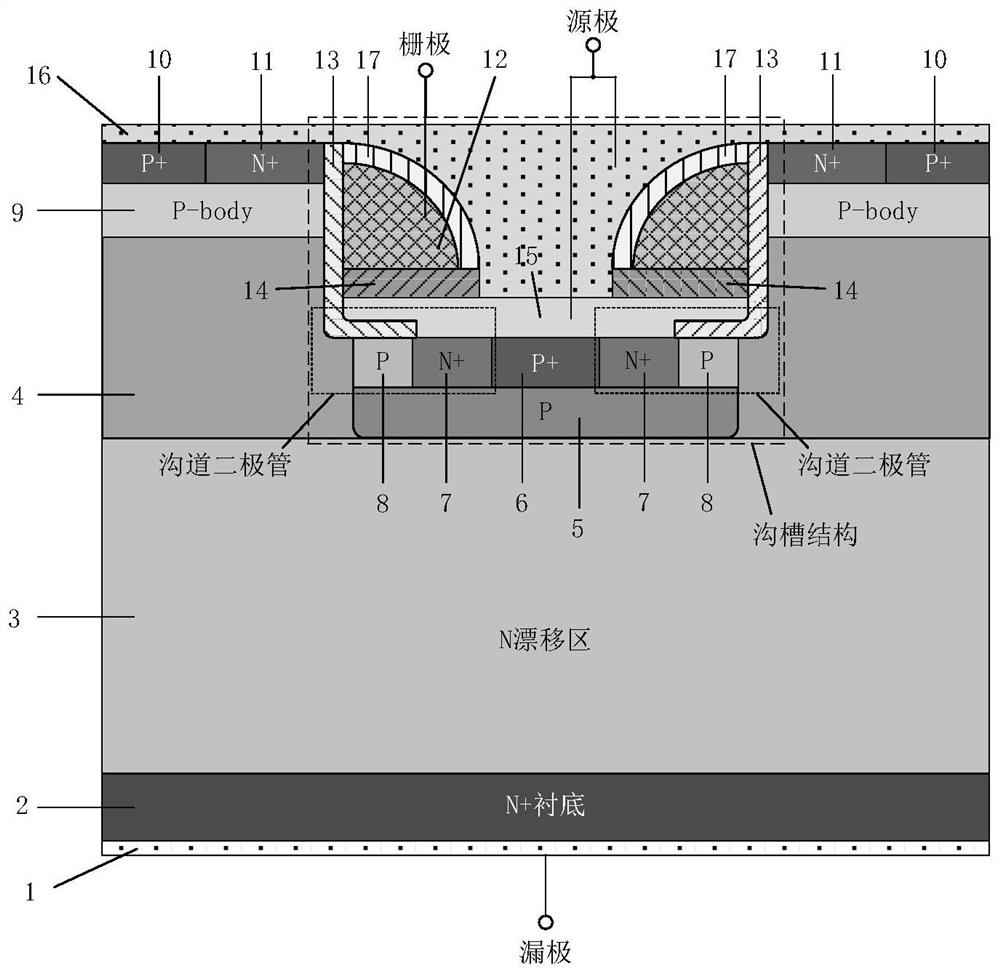

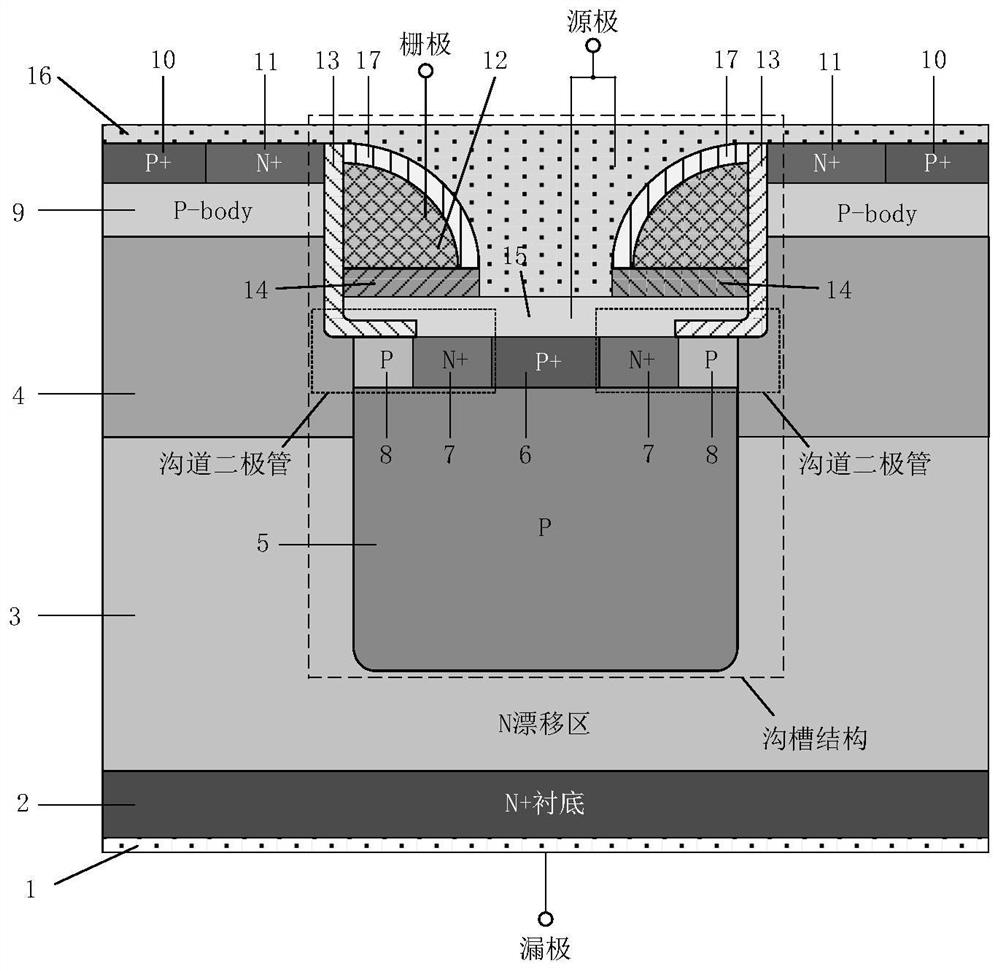

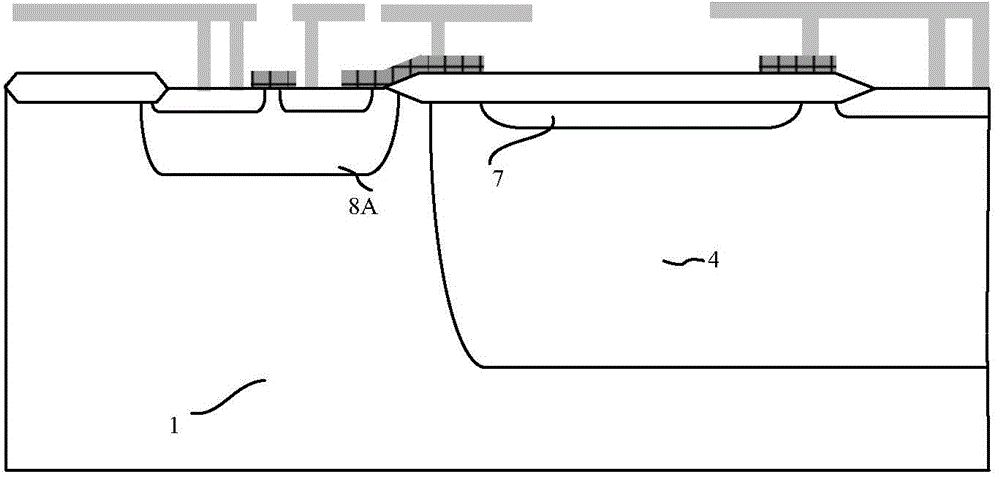

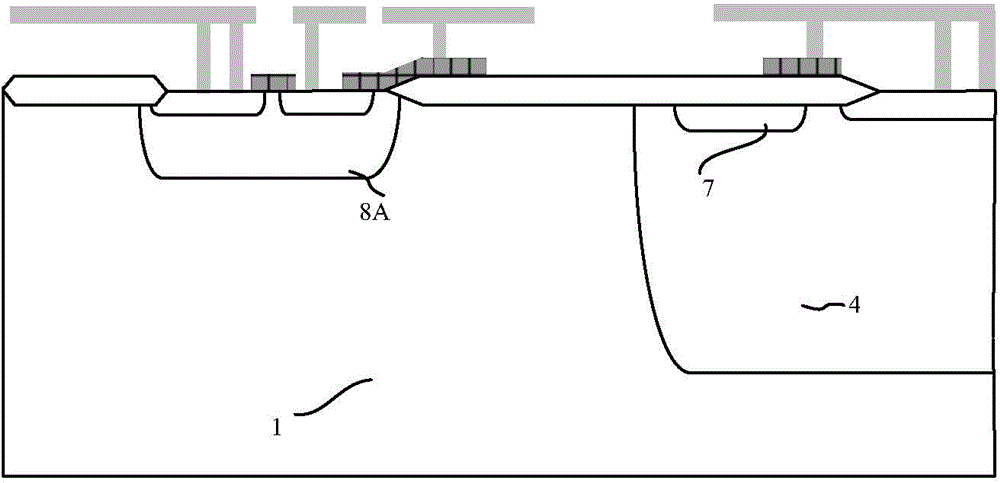

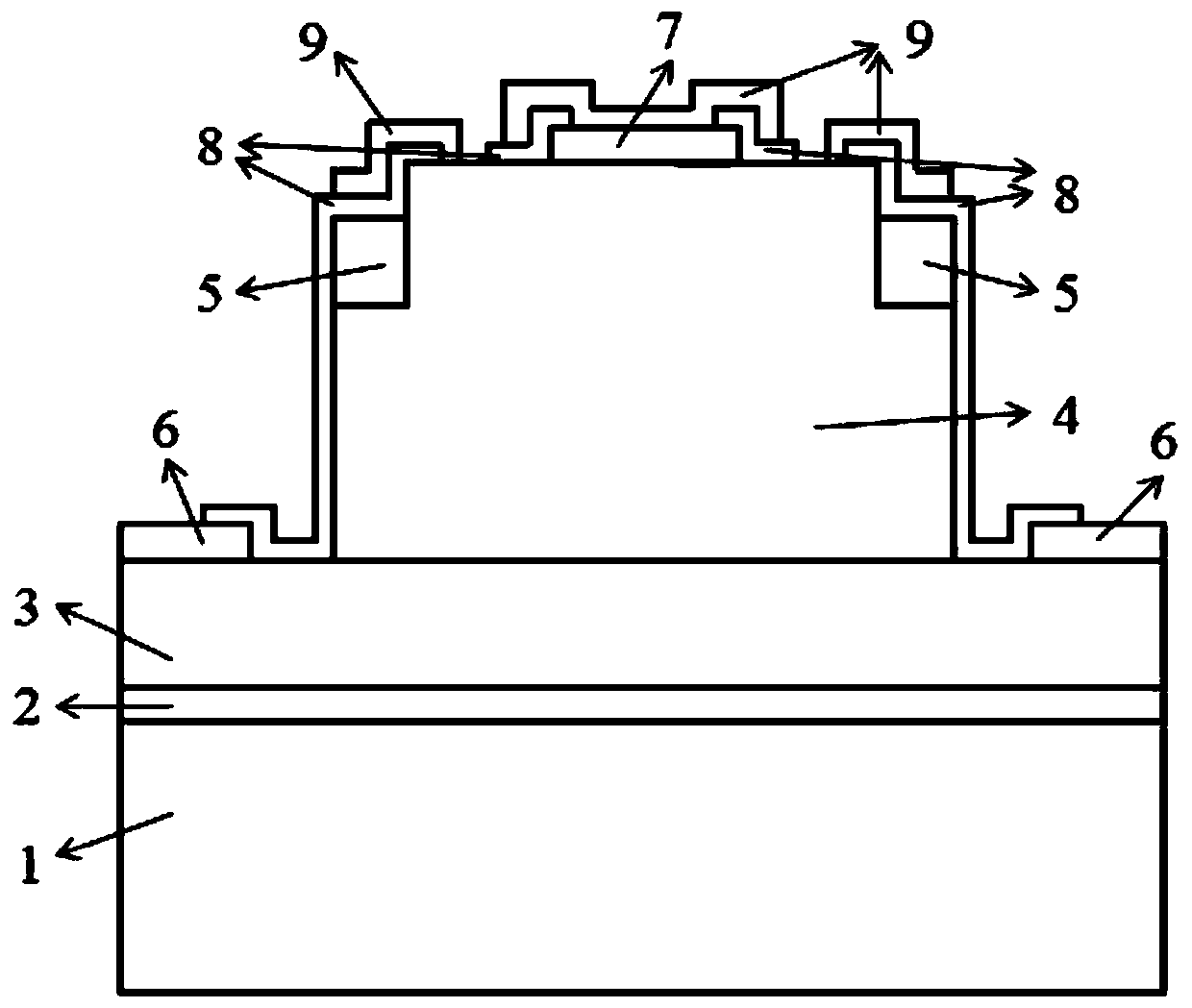

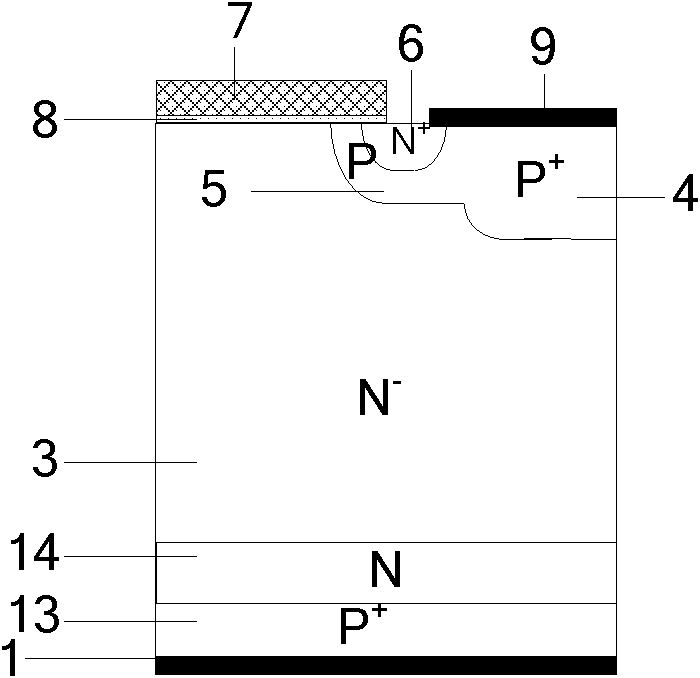

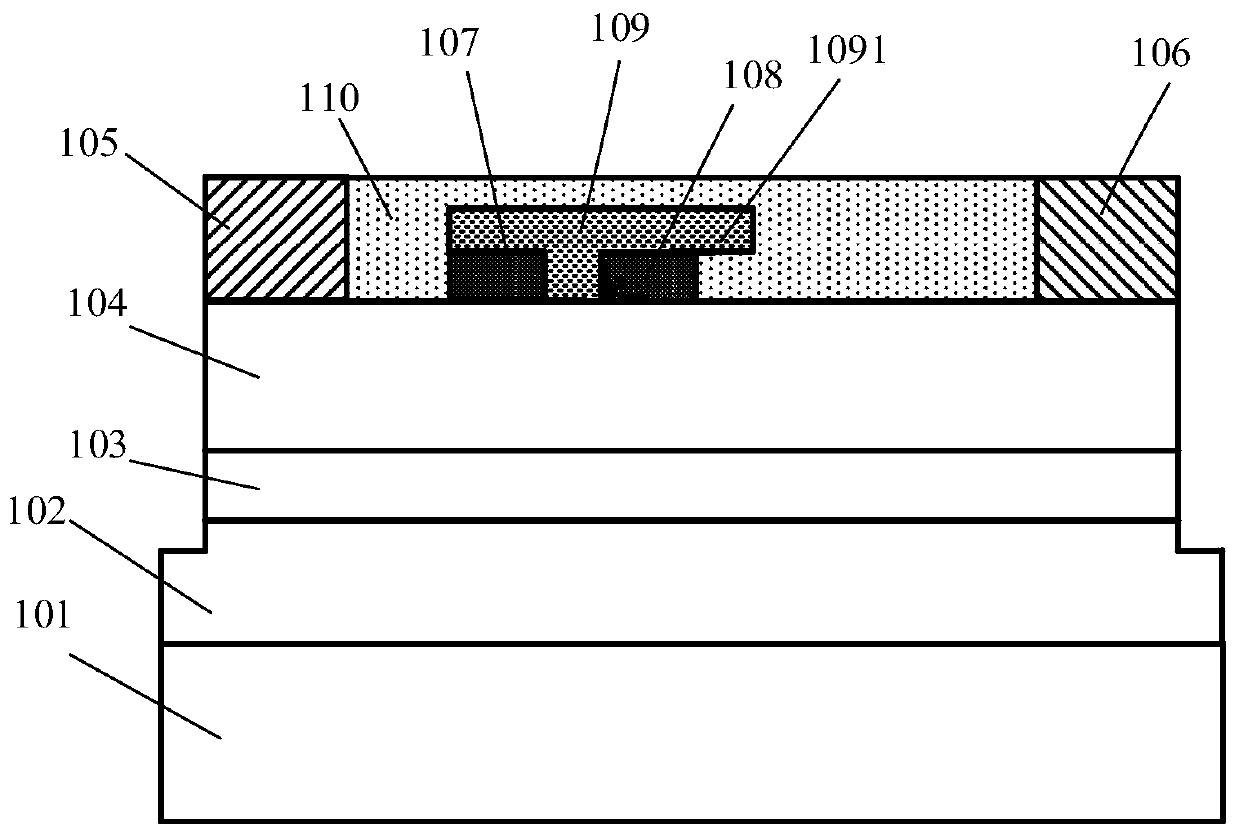

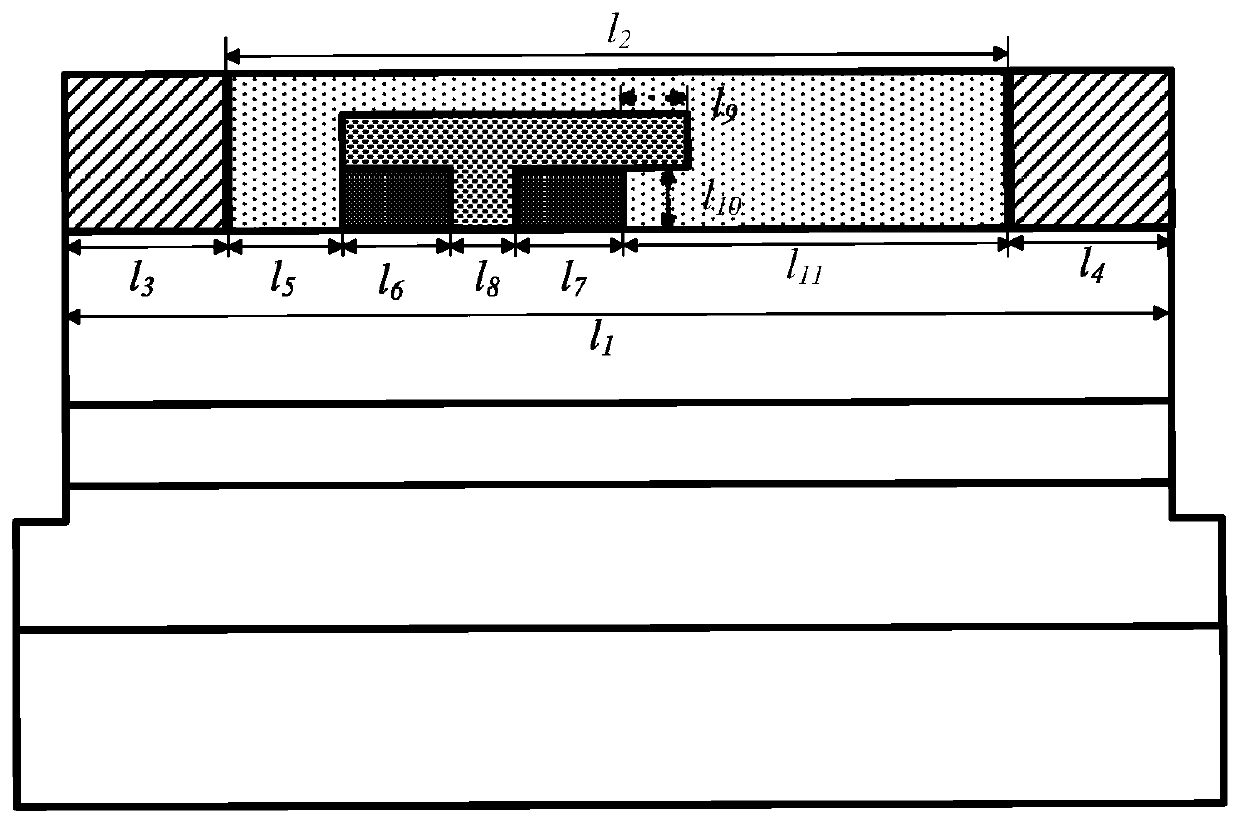

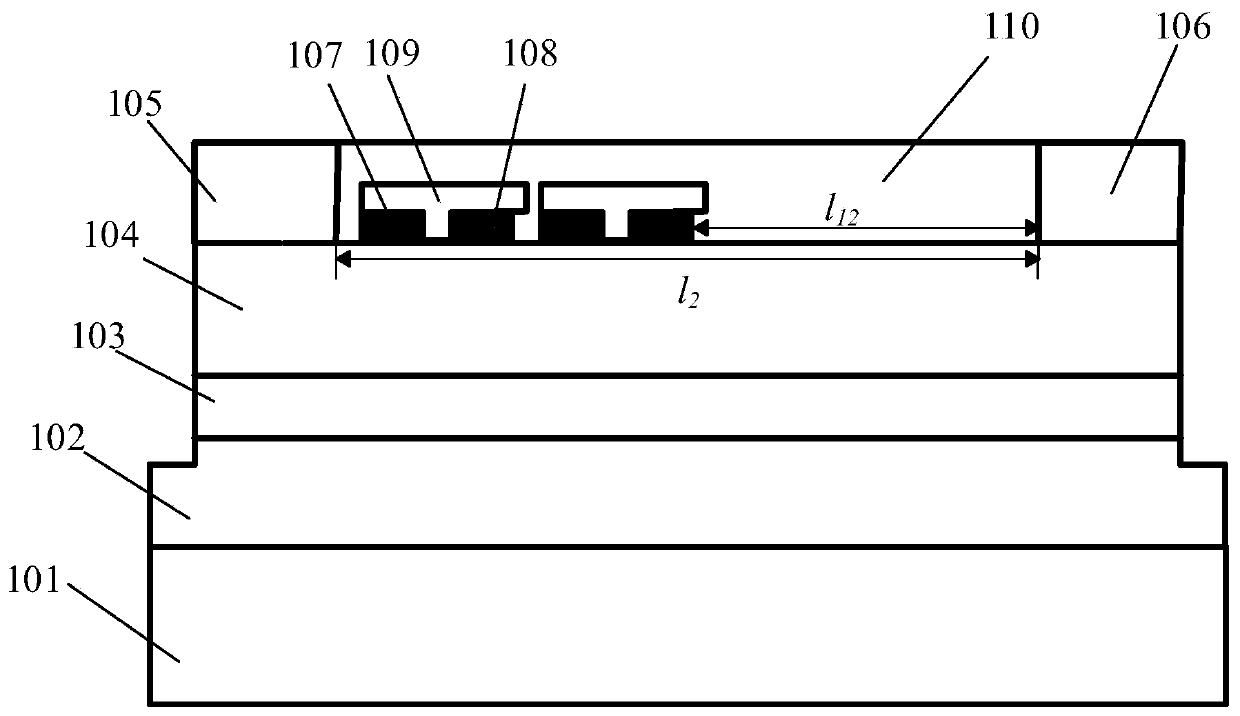

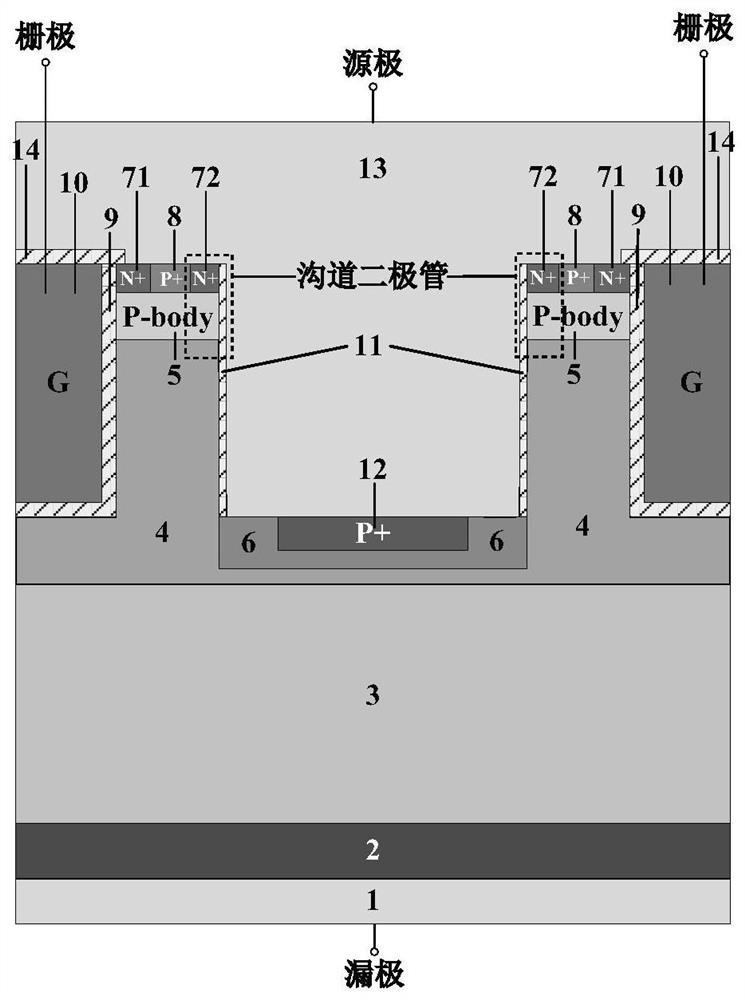

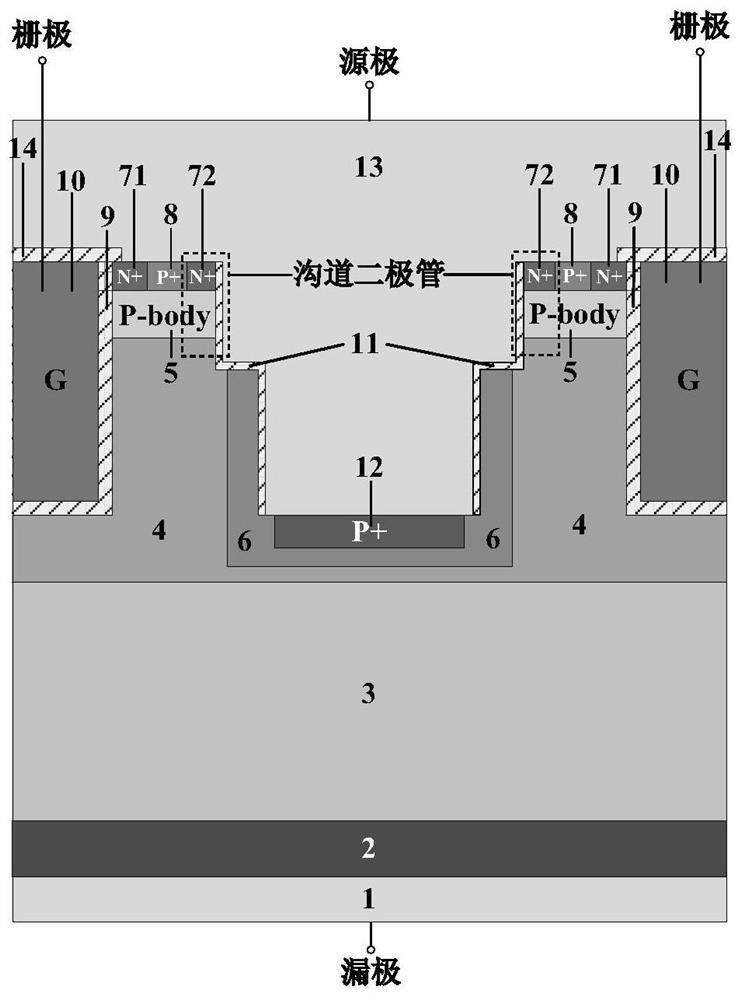

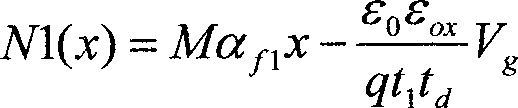

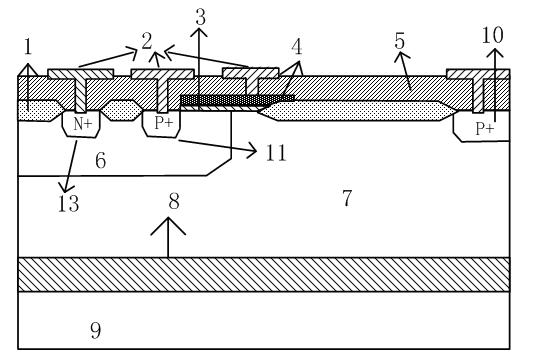

Silicon carbide MOSFET device with integrated diode and manufacturing method

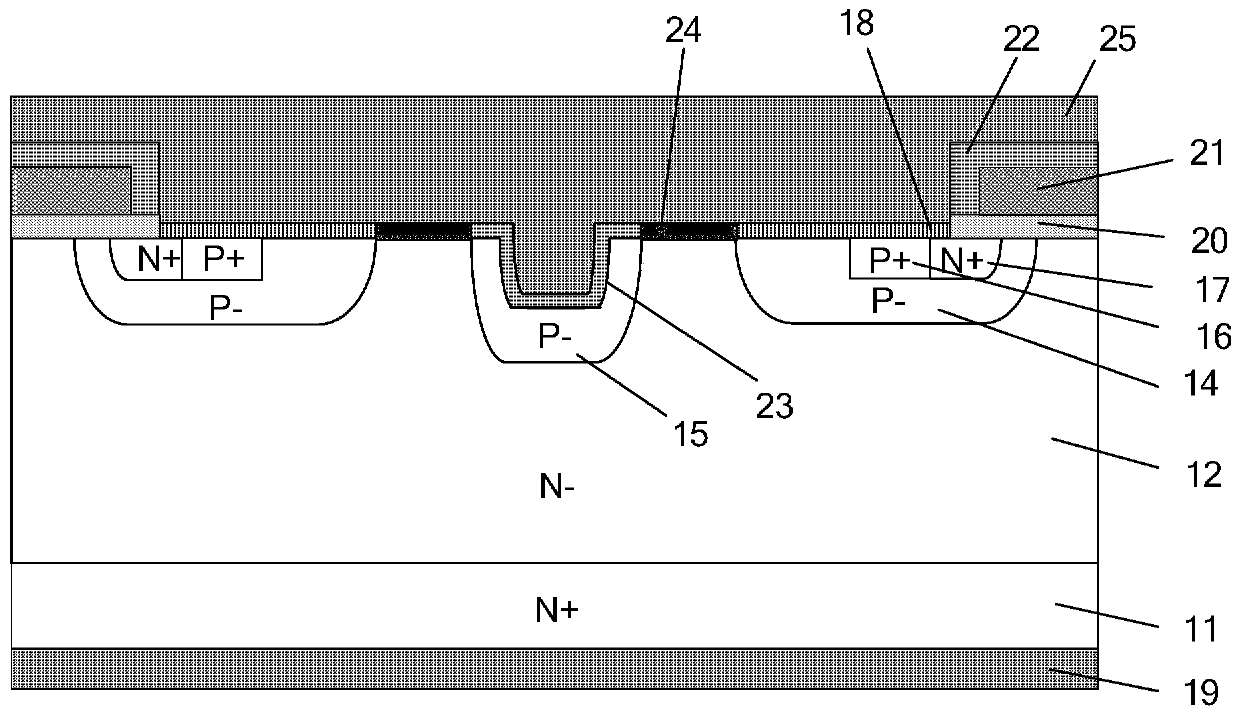

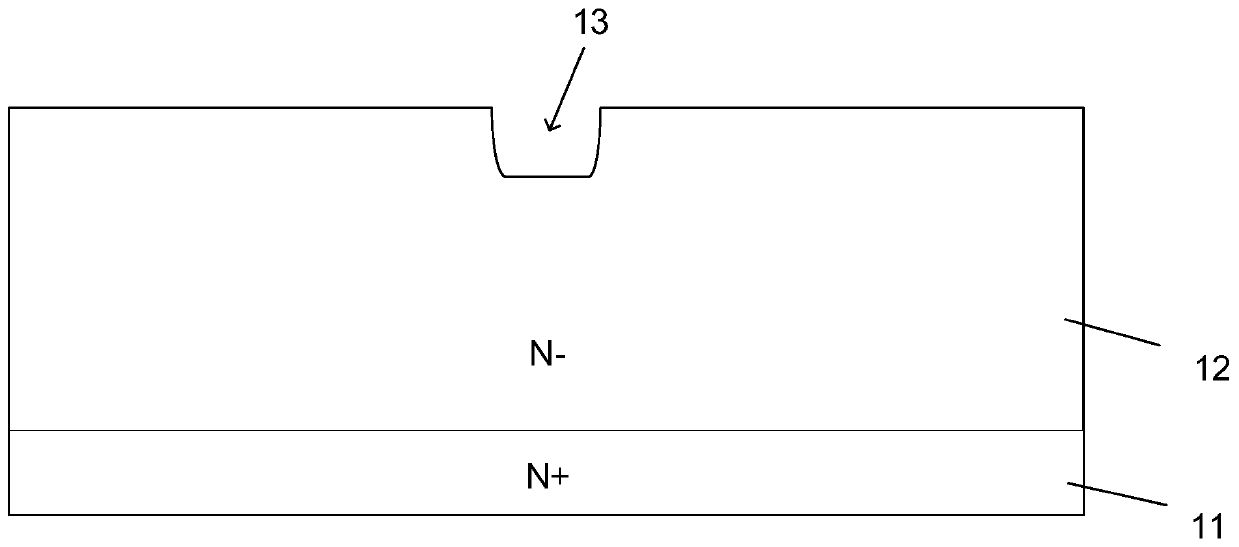

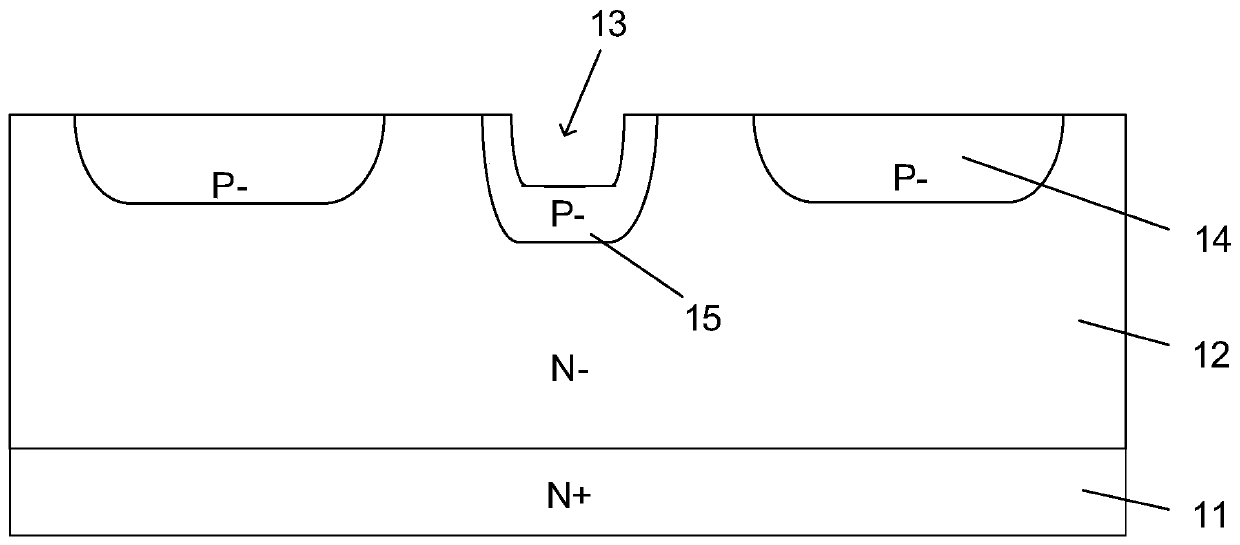

PendingCN114122139AReduce areaImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate dielectric

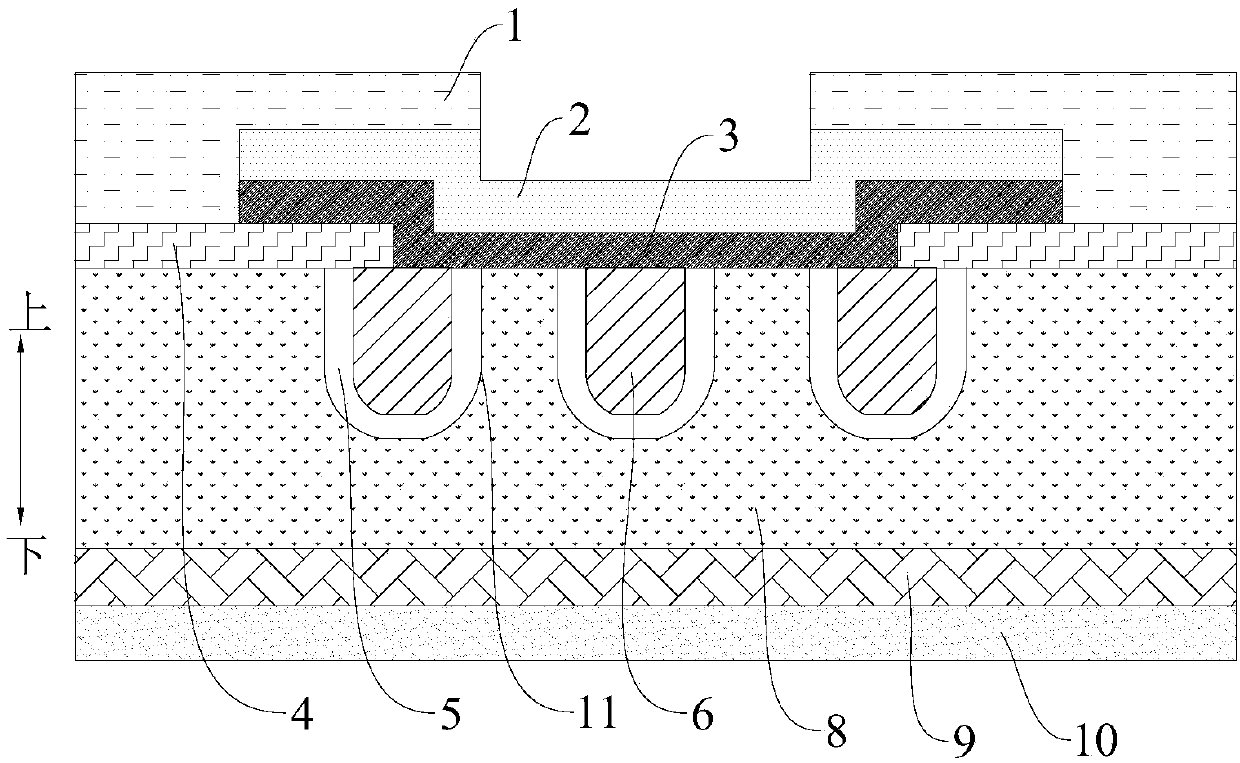

The invention provides a silicon carbide MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) device with an integrated diode and a manufacturing method. The device comprises a source ohmic contact region, a drain ohmic contact region, an N + substrate, an N-drift region, a P-type base region, a P + source region, an N + source region, a P-type shielding layer, a shielding layer N + source region, an N-type channel region, a gate dielectric layer and a polysilicon gate. According to the trench type silicon carbide MOSFET device provided by the invention, the chip area is greatly saved in a mode of integrating the diodes in the chip. The N-type channel region is introduced to the bottom of the trench, so that the electron barrier height at the interface of the oxide layer is adjusted, the third quadrant characteristic of the device is remarkably improved, the low third quadrant turn-on voltage is realized, and the bipolar degradation effect is avoided; multiple channels are connected in parallel, so that the forward current capability of the device is improved, and the on-resistance is reduced; and the P-type shielding layer wraps and protects the gate groove, so that the electric field of the gate oxide layer is reduced, and the reliability of the device oxide layer is enhanced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

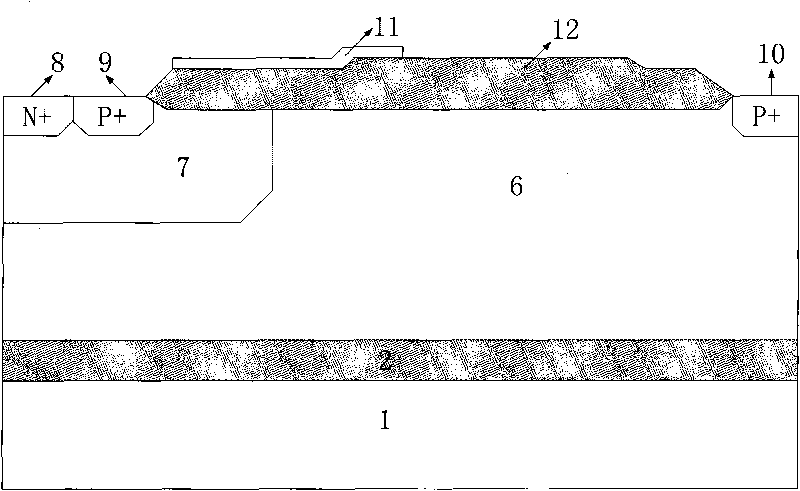

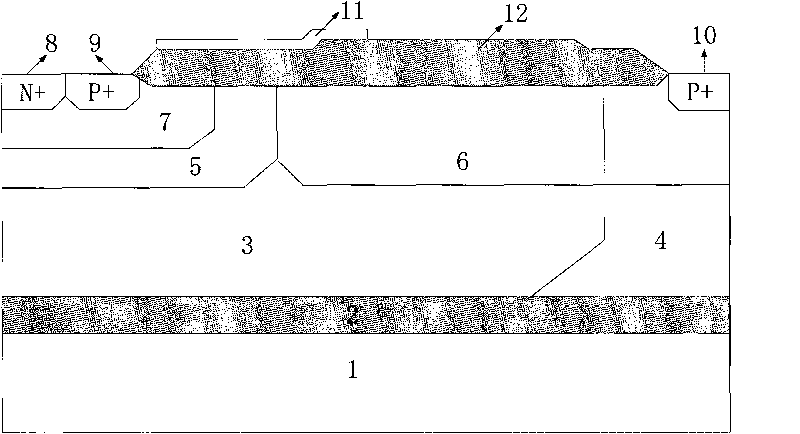

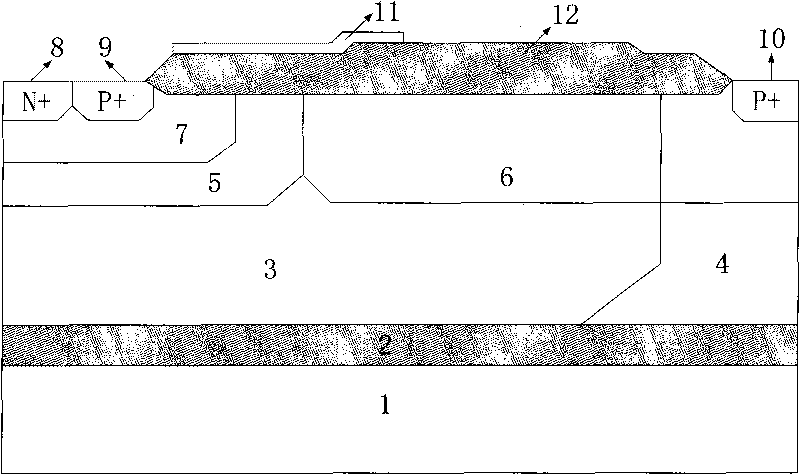

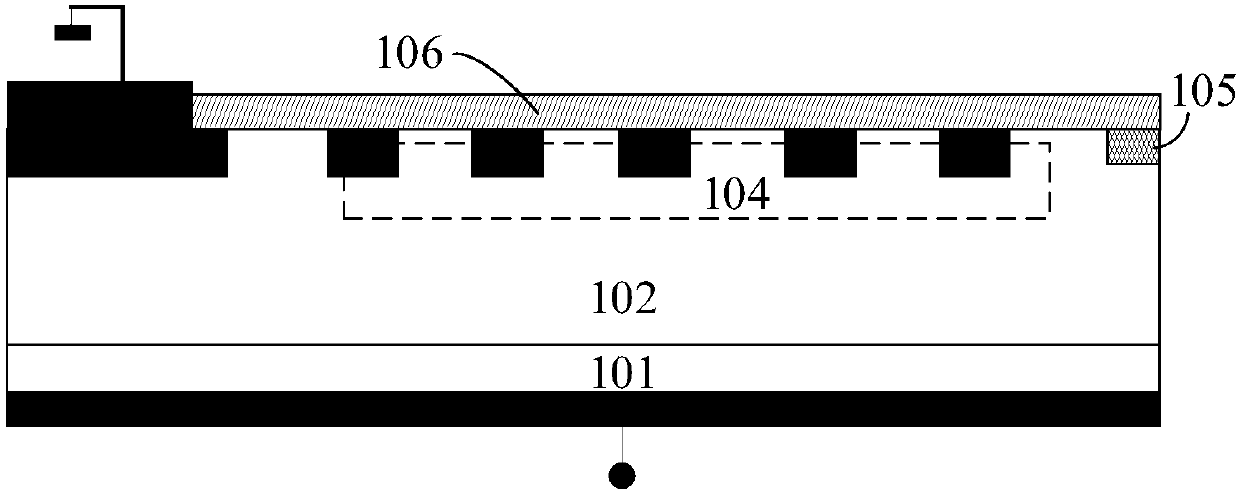

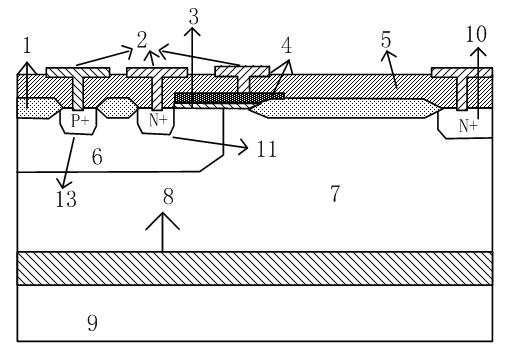

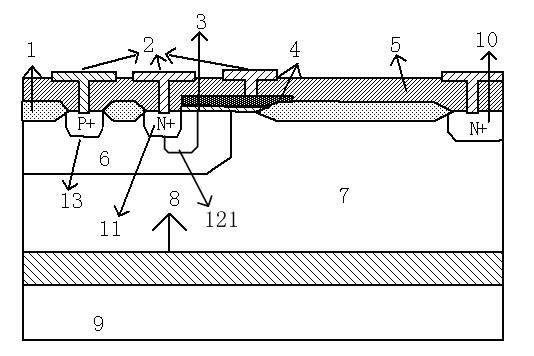

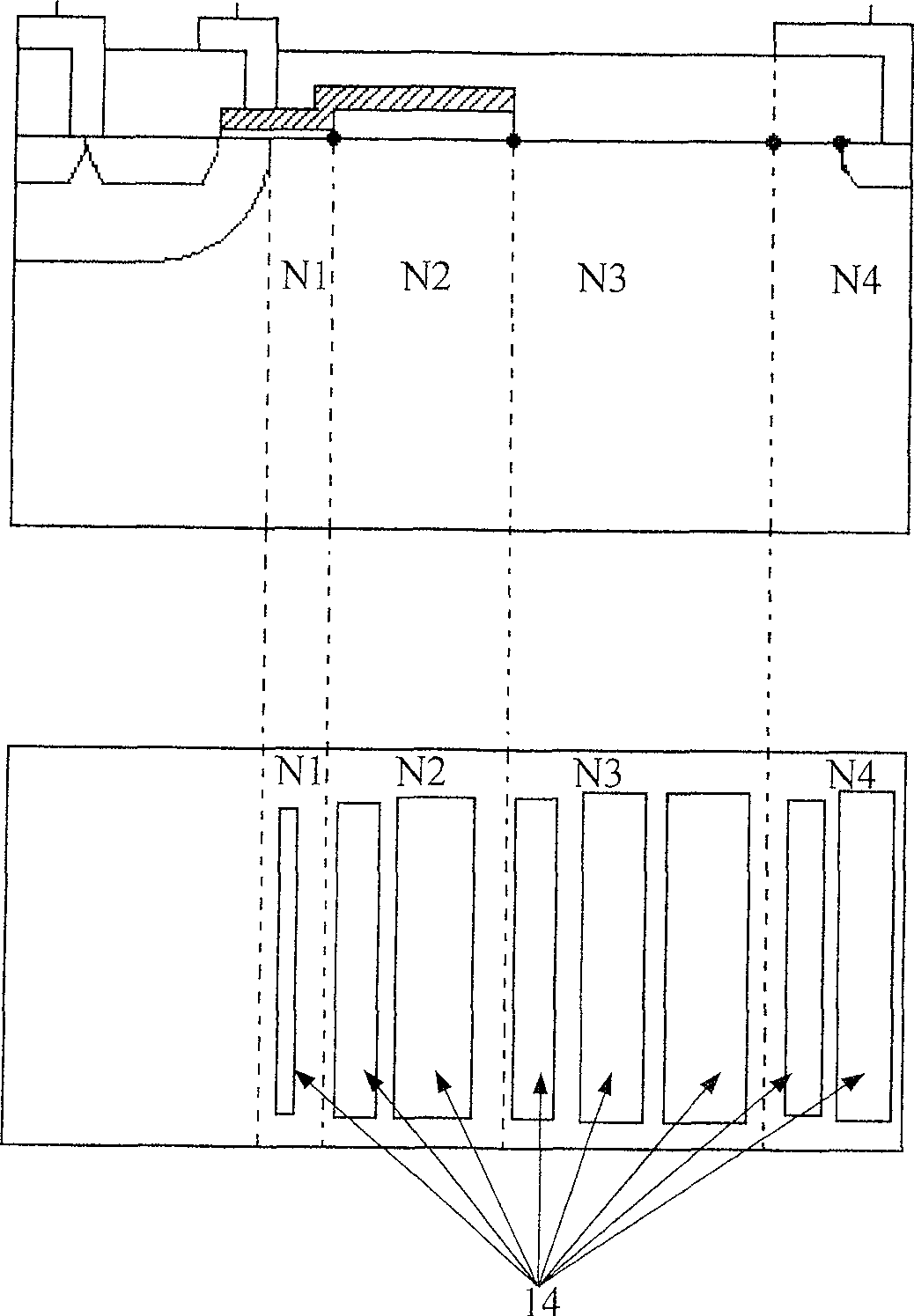

Isolation structure of high-voltage driving circuit

The invention discloses an isolation structure of a high-voltage driving circuit. The isolation structure comprises a P type substrate, wherein a first P type buried layer, a second P type intermittent island buried layer area, a third P type buried layer, a first N type buried layer and a second N type buried layer; the second P type intermittent island buried layer area is located between the first P type buried layer and the first N type buried layer; the third P type buried layer is located between the first N type buried layer and the second N type buried layer. According to the isolation structure, the problem that the peak value of the surface electric field of the transverse PN junction of RESURFLDMOS is overhigh is solved, and the reliability of the isolation structure is improved.

Owner:WUXI CHIPOWN MICROELECTRONICS

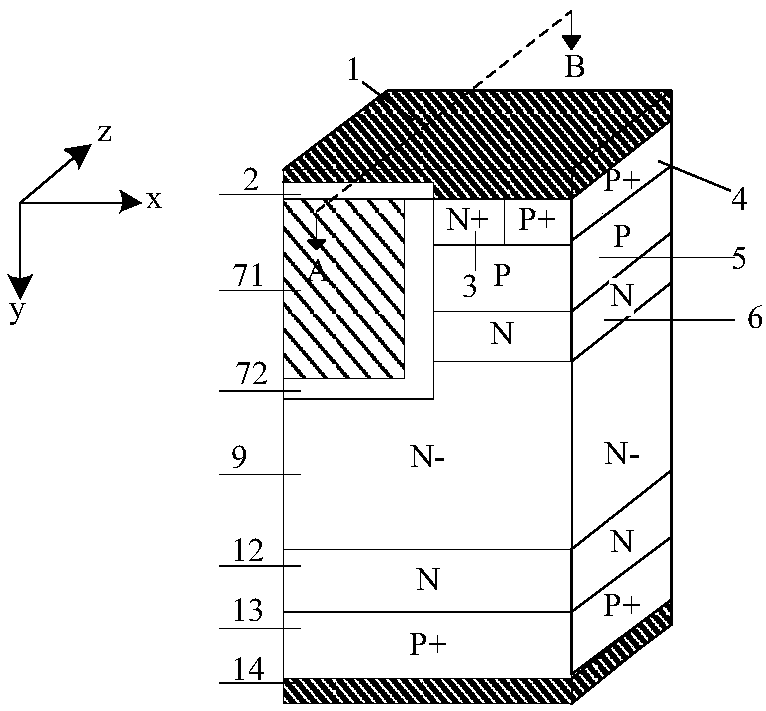

Transverse P-type double diffused metal oxide semiconductor transistor of silicon on insulator

ActiveCN101702409APrevent punch-throughSimple structureSemiconductor devicesHigh pressureSemiconductor

The invention relates to a transverse P-type double diffused metal oxide semiconductor transistor of silicon on an insulator, which comprises a semiconductor substrate, wherein a buried oxide layer is arranged on the semiconductor substrate, a high-voltage N-type well and a high-voltage P-type well are arranged on the buried oxide layer, an N-type well and a P-type drift region are arranged on the high-voltage N-type well, the P-type drift region extends to the upper half part of the high-voltage N-type well, and an N-type D well region is arranged on the N-type well, thereby forming a three-layered N-type well structure; meanwhile, a step structure exists in an oxide layer on the surface of an element, and the oxide layer on the P-type drift region is obviously thicker than other parts. The transverse P-type double diffused metal oxide semiconductor transistor can effectively improve the pressurization of the element and can prevent puncture between the drift region and a source region.

Owner:SUZHOU POWERON IC DESIGN

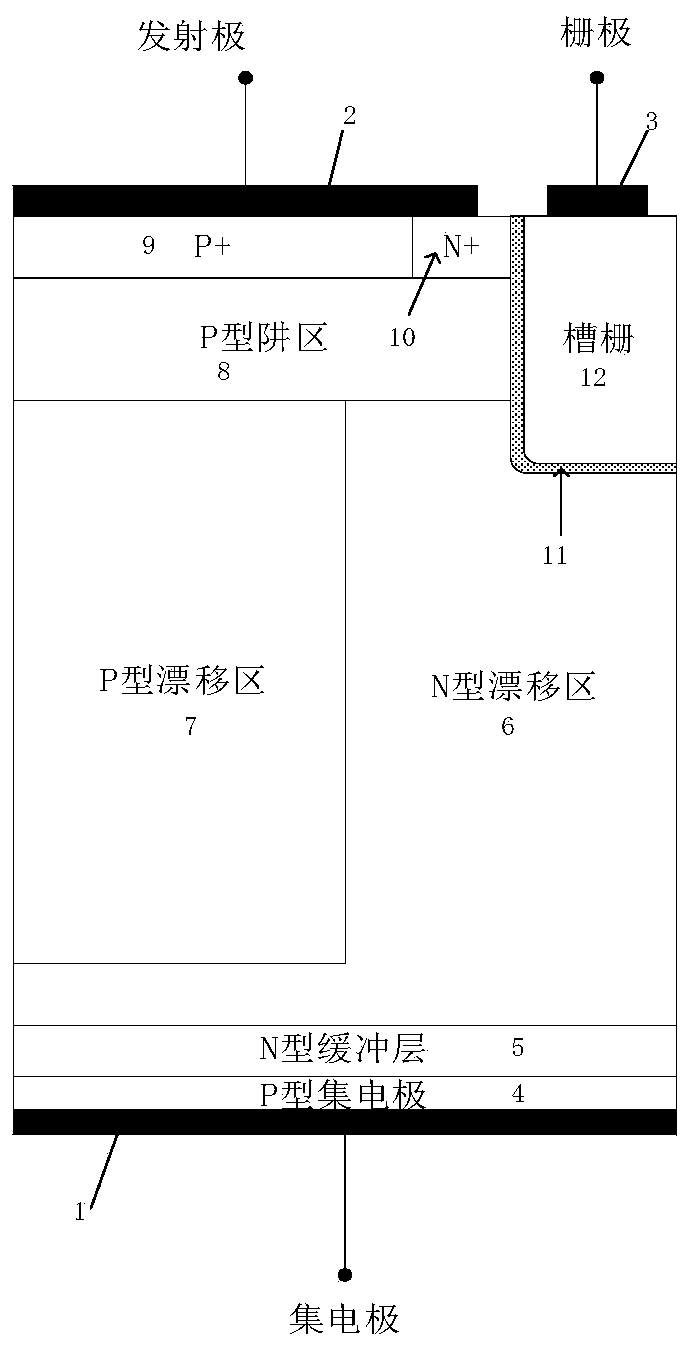

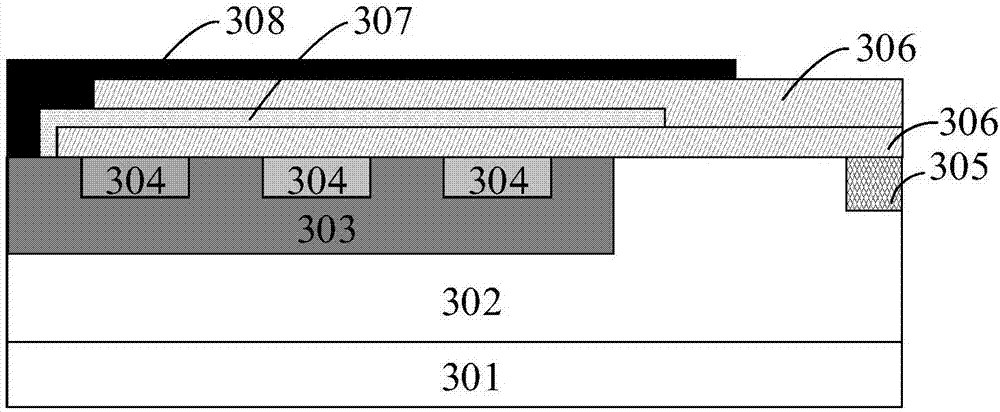

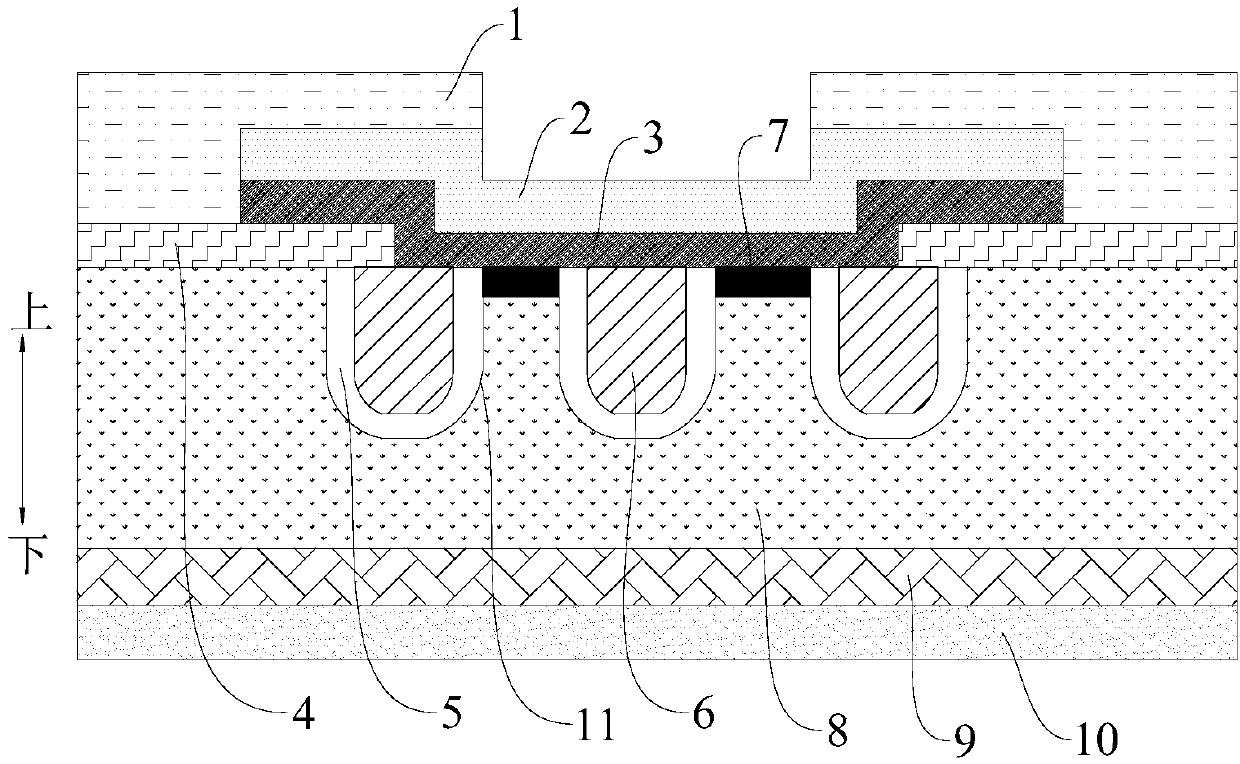

Trench gate charge storage type IGBT and manufacturing method thereof

ActiveCN108461537AIncreased injection enhancementImprove concentration distributionSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

The invention discloses a trench gate charge storage type IGBT, and belongs to the technical field of semiconductor power devices. A conventional trench gate structure is widened, and a side wall gateelectrode structure is employed for forming a mesa structure located below a base region. moreover, a shielding trench structure for shielding the electric field of a charge storage layer is introduced, thereby improving the carrier injection enhancement effect, and improving the compromise between a forwarding ON voltage drop Vceon and the OFF loss Eoff. The electric field concentration effect at the tip of the bottom of a trench is alleviated, and the breakdown voltage of a device is effectively improved. The gate capacitance of the device, especially the Miller capacitance CGC and the gatecharge QG, is reduced, the switching speed of the device is improved, the switching loss of the device is reduced, and the requirements for the capability of a gate drive circuit are reduced. The constraint on the doping concentration of an N-type charge storage layer and the withstand voltage of the device from the thickness are avoided, the saturation current density is reduced, and a short-circuit safe operating region (SCSOA) of the device is improved. Moreover, an EMI effect is effectively inhibited when the device is turned on. In addition, the manufacturing method is compatible with aconventional trench gate charge storage type IGBT manufacturing method.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

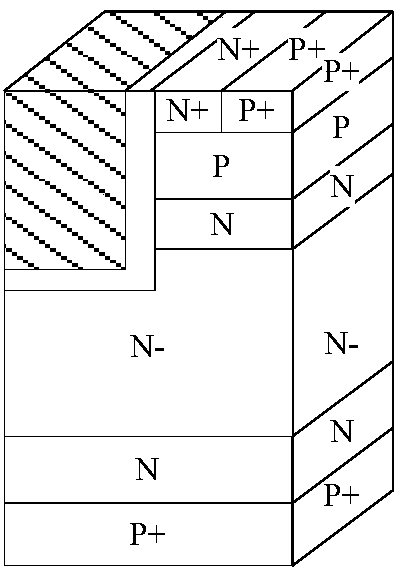

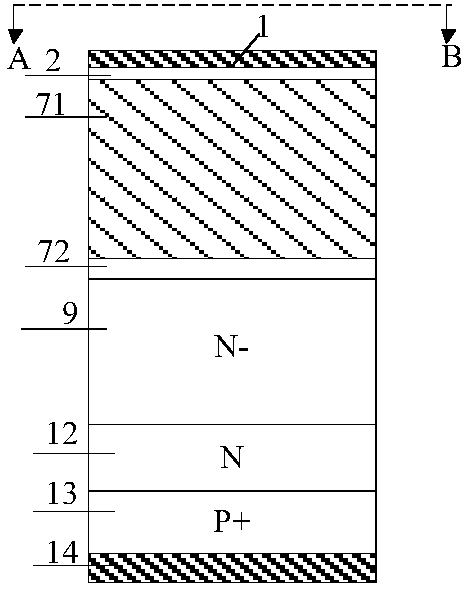

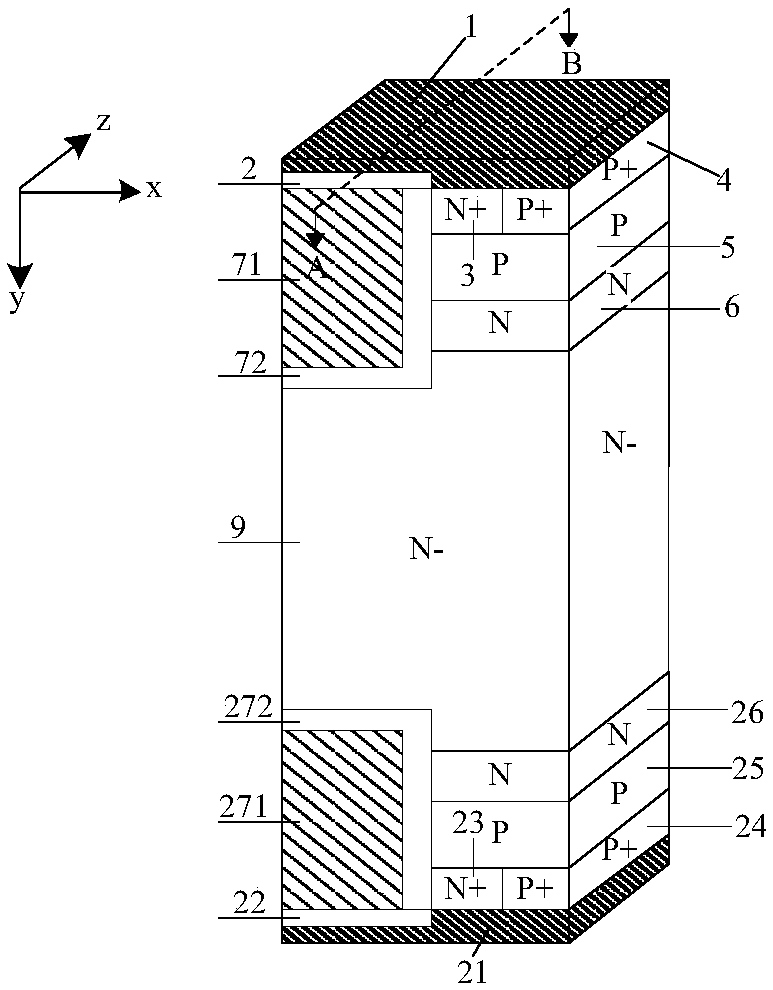

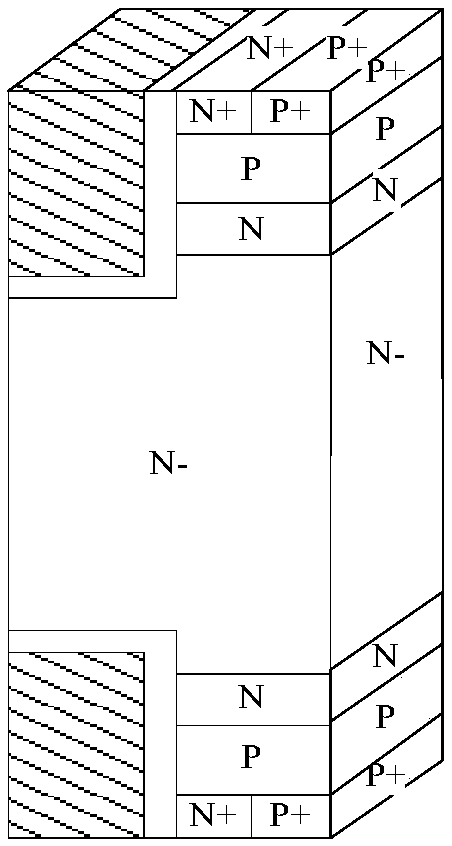

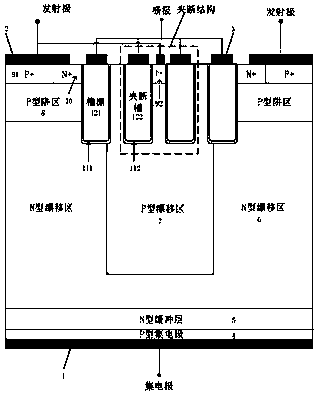

Bi-directional trench gate charge storage type IGBT (insulated-gate bipolar transistor) and manufacturing method thereof

ActiveCN108231878AImprove breakdown voltageFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceElectric field

The invention provides a bi-directional trench gate charge storage type IGBT (insulated-gate bipolar transistor) and belongs to the technical field of a semiconductor power device. By means of widening of a traditional trench gate structure, formation of a mesa structure below a base region by a side wall gate electrode structure as well as introduction of a shielding trench structure, carrier injection enhancement effect is increased while symmetric forward / reverse conduction and turn-off characteristics of the device are realized, and compromise between forward voltage drop Vceon and turn-off loss Eoff is improved; electric field concentration effect at a sharp corner of the bottom of a trench is reduced, and breakdown voltage of the device is effectively increased; gate capacitance of the device is reduced, so that switching speed of the device is increased, switching loss of the device is reduced, and the requirement for capacity of a gate driven circuit is reduced; limitation of doping concentration and thickness of an N-type charge storage layer to device withstand voltage is avoided; saturation current density is reduced, and a short circuit safe operating area of the deviceis improved; further, EMI (electro-magnetic interference) effect produced when the device is conducted is effectively inhibited. Besides, a manufacturing method is compatible with a traditional CSTBTmanufacturing method.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

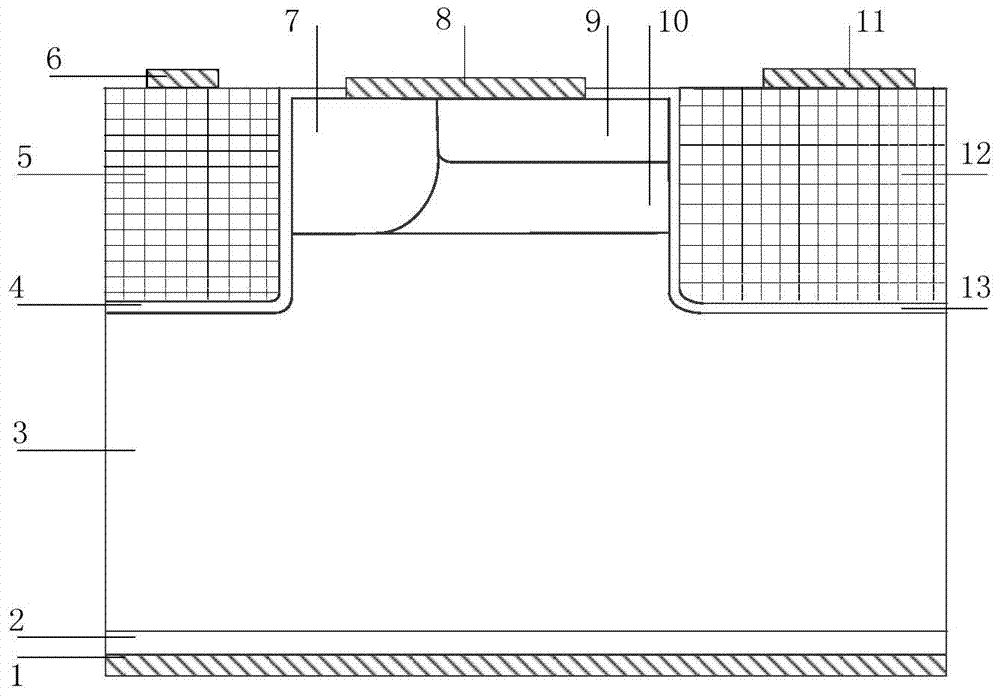

Silicon carbide fin-shaped gate MOSFET integrated with channel diode

ActiveCN113130627ASmall pressure dropImprove reliabilityEfficient power electronics conversionSolid-state devicesMOSFETCapacitance

The invention belongs to the technical field of power semiconductors, and particularly relates to a silicon carbide fin-shaped gate MOSFET integrated with a channel diode. The silicon carbide fin-shaped gate MOSFET is mainly characterized in that the silicon carbide fin-shaped gate MOSFET is of a groove structure, the channel diode is integrated at the bottom part of a groove region, when the device is in a reverse follow current working mode, the channel diode is conducted to realize a follow current function, reverse conduction voltage drop is reduced, conduction of a body diode is effectively inhibited, and influence caused by bipolar degradation is eliminated; a fin-shaped gate structure is adopted, so that a P region below the groove is effectively grounded, a peak electric field of an oxide layer at the bottom part of the groove is lower than a critical breakdown value, and the reliability of the device in a blocking working mode is improved; and two symmetrical fin-shaped gates located in the groove and the third conductive material located at the bottom part of the groove below the fin-shaped gates form a composite separation gate structure, so that the gate-drain capacitance is reduced, the switching loss is reduced, and the device has more advantages in high-frequency application.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

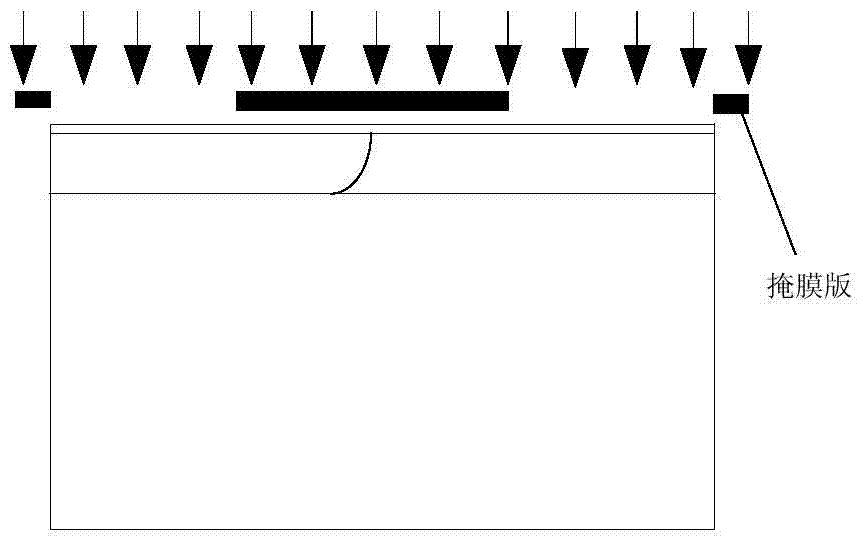

Non-punch-through type insulated gate bipolar transistor with side polysilicon electrode trench

InactiveCN103531621AImprove breakdown voltageLower threshold voltageSemiconductor devicesParasitic bipolar transistorSilicon dioxide

The invention discloses a non-punch-through type insulated gate bipolar transistor with a side polysilicon electrode trench, and relates to a bipolar transistor. The non-punch-through type insulated gate bipolar transistor is provided with a metalized collector electrode, a P type collector electrode region, an N- type drift region, a silicon dioxide side polysilicon oxide layer, a side polysilicon electrode, a metalized side polysilicon electrode, a P+ type body region, a metalized emitter electrode, an N+ type source region, a P type base region, a metalized gate electrode, a polysilicon gate electrode and a silicon dioxide gate oxide layer. A side polysilicon electrode technology is introduced in a traditional non-punch-through type insulated gate bipolar transistor with a trench; a mask plate does not need to be arranged and the junction depth of an original P+ type body region is expanded to be connected with the N- type drift region; a positive voltage is applied to Side-poly (the side polysilicon electrode trench), so that a reverse electric field can be generated, the shortcoming of electric field accumulation due to small bottom curve rate of the trench in Trench-NPT-IGBT (the non-punch-through type insulated gate bipolar transistor with the side polysilicon electrode trench) is overcome, and the peak electric field at the bottom of a trench gate is effectively reduced. Therefore, the non-punch-through type insulated gate bipolar transistor has the characteristics of higher breakdown voltage and lower threshold voltage.

Owner:XIAMEN UNIV

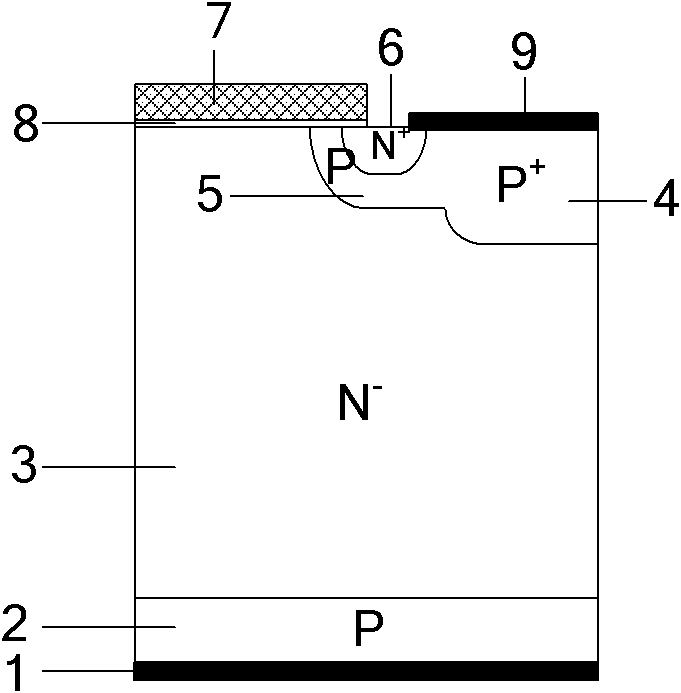

High voltage semiconductor device and manufacture method thereof

ActiveCN104835837AReduce sensitivityOptimizing Surface Field DistributionSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactHigh pressure

The invention provides a high voltage semiconductor device and a manufacture method thereof; the device comprises a first dope type semiconductor substrate, a second dope type epitaxial layer arranged on the semiconductor substrate, a second dope type high voltage well positioned in the epitaxial layer, a second dope type deep well positioned in the high voltage well, a first dope type reduced-field layer positioned on the surface of the epitaxial layer and / or in the epitaxial layer (wherein at least a part of the reduced-field layer is positioned in the deep well), a first dope type first well parallel to the high voltage well and positioned in the epitaxial layer, a second dope type source electrode ohmic contact zone arranged in the first well, a drain electrode ohmic contact zone arranged in the deep well, a grid electrode close to the source electrode ohmic contact zone and at least covering the epitaxial layer between the source electrode ohmic contact zone and the high voltage well. The high voltage semiconductor device and the manufacture method thereof can effectively reduce technical manufacture difficulty, improve device parameter characteristics, and improve device reliability.

Owner:HANGZHOU SILAN MICROELECTRONICS

Vertical GaN Schottky device structure with high breakdown voltage and low reverse electric leakage

ActiveCN111192928AImprove breakdown voltageReduce reverse leakage currentSemiconductor devicesEtchingHigh field

The invention discloses a vertical GaN Schottky device structure with high breakdown voltage and low reverse electric leakage. The vertical GaN Schottky device structure comprises a first conductive type highly-doped GaN layer, a first conductive type low-doped GaN layer, a second conductive type NiO filling layer, a SiO2 and Si3N4 mixed dielectric layer, a floating metal field plate, an ohmic cathode, a Schottky anode, a sapphire substrate and an AlN nucleating layer. According to the device structure provided by the invention, a two-step etching process is applied, so that the operability problem of a deep etching technology is solved; the designed second conductive type NiO filling layer overcomes the technical problem of second conductive type doping of a GaN material, effectively shields a high electric field and protects a Schottky barrier, so that the reverse leakage current of the device is effectively reduced; the designed multi-field-plate structure effectively utilizes the advantage of high field plate contact area brought by a two-step etching process, weakens the fringe field concentration effect of the device, and effectively improves the reverse breakdown voltage ofthe device.

Owner:XI AN JIAOTONG UNIV

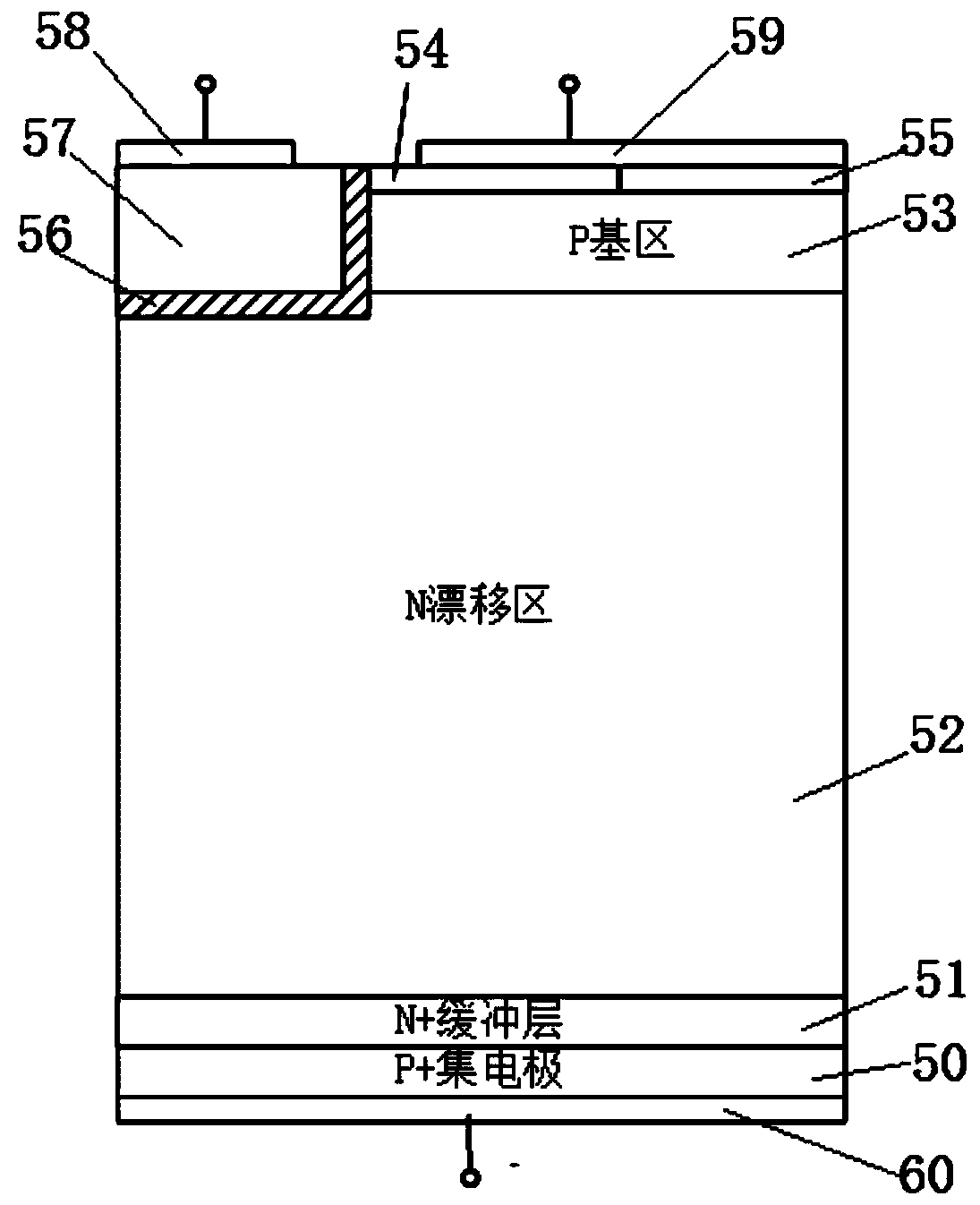

Groove-grid-type insulated gate bipolar transistor with body electrode

InactiveCN102194864AReduce peak electric fieldImprove breakdown voltageSemiconductor devicesElectric fieldInsulated-gate bipolar transistor

The invention discloses a groove-grid-type insulated gate bipolar transistor with a body electrode, belonging to the technical field of semiconductor power devices. In the invention, a groove-type polycrystalline silicon electrode is introduced into the traditional groove-grid-type insulated gate bipolar transistor; the defects of concentration of the electric field of the traditional groove-grid-type insulated gate bipolar transistor below a groove gate can be overcome through optimizing the voltage on the body electrode, thus effectively reducing the peak value electric field at the bottom of the groove gate, and improving the puncture voltage of the device; and when the device is in forward conduction, the voltage on the body electrode can form multiple sub accumulation layers outside a thick oxide layer of the body electrode, thus reducing the on-resistance, and lowering the on-state power losses in the forward conduction.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

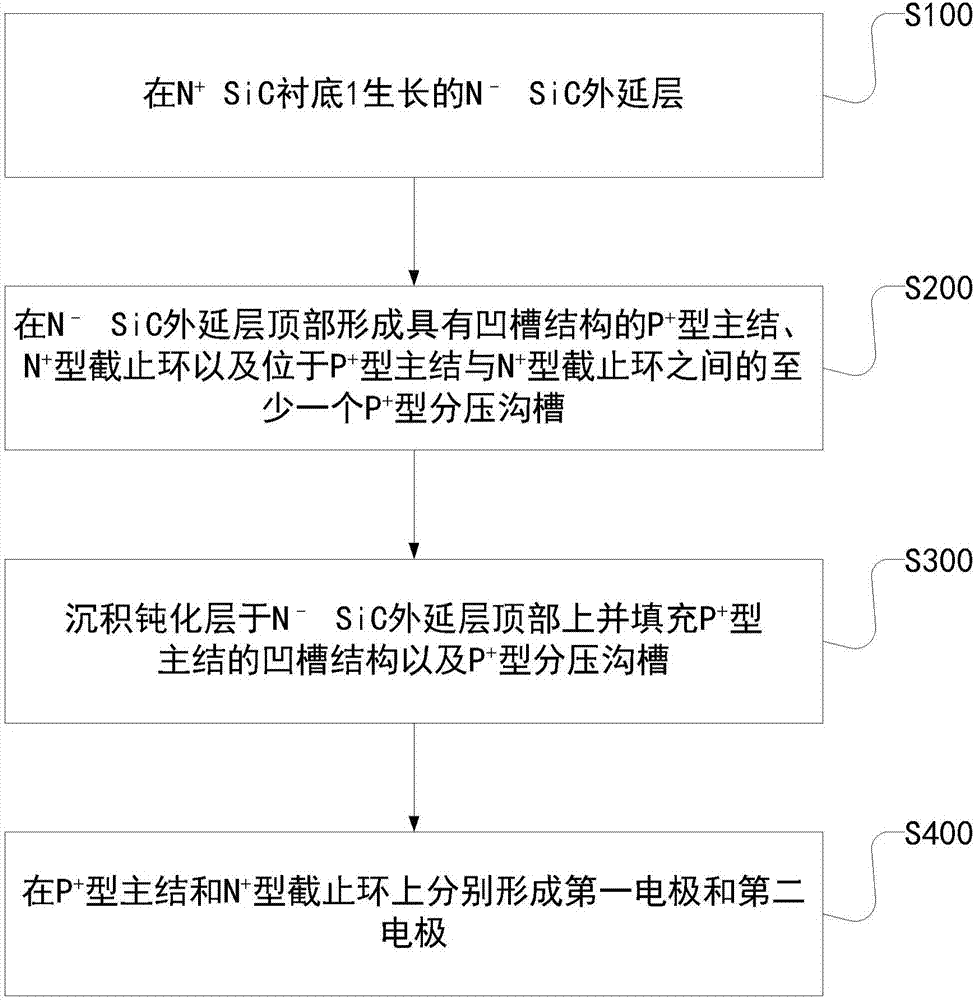

Silicon carbide power device terminal and manufacturing method thereof

InactiveCN107293599AImprove surface electric field distributionGuaranteed device withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesSic substrateOptoelectronics

The invention discloses a silicon carbide powder device terminal and a manufacturing method thereof. The silicon carbide power device terminal comprises a first heavily-doped or second heavily-doped SiC substrate, a first lightly-doped SiC epitaxial layer, a second heavily-doped main junction, a first doped stop ring and at least one second heavily-doped partial pressure groove, wherein the first lightly-doped SiC epitaxial layer grows on the first heavily-doped or second heavily-doped SiC substrate; the second heavily-doped main junction and the first doped stop ring are provided with groove structures, and formed on the top of the first lightly-doped SiC epitaxial layer; and the at least one second heavily-doped partial pressure groove is formed between the second heavily-doped main junction and the first doped stop ring.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

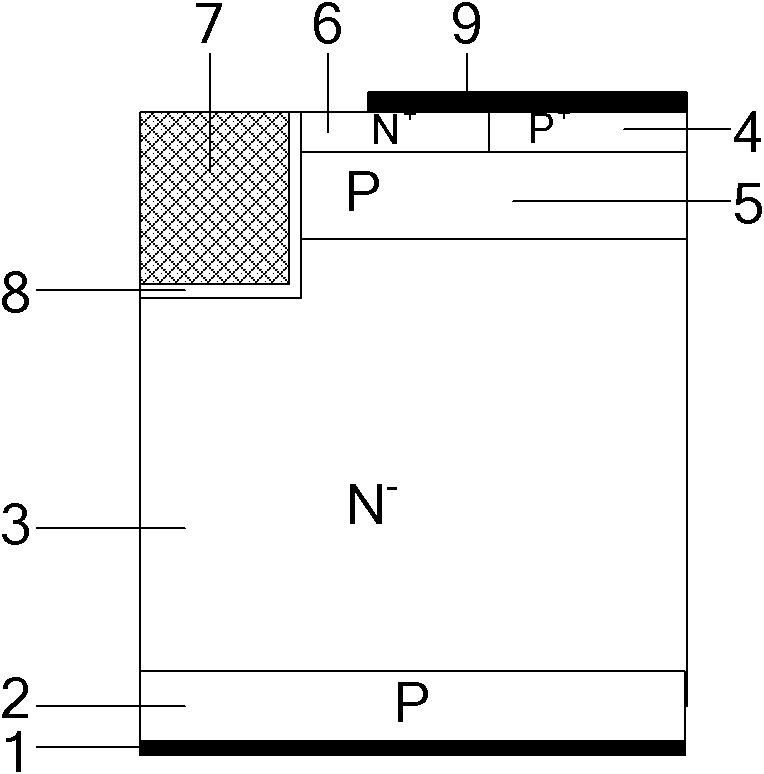

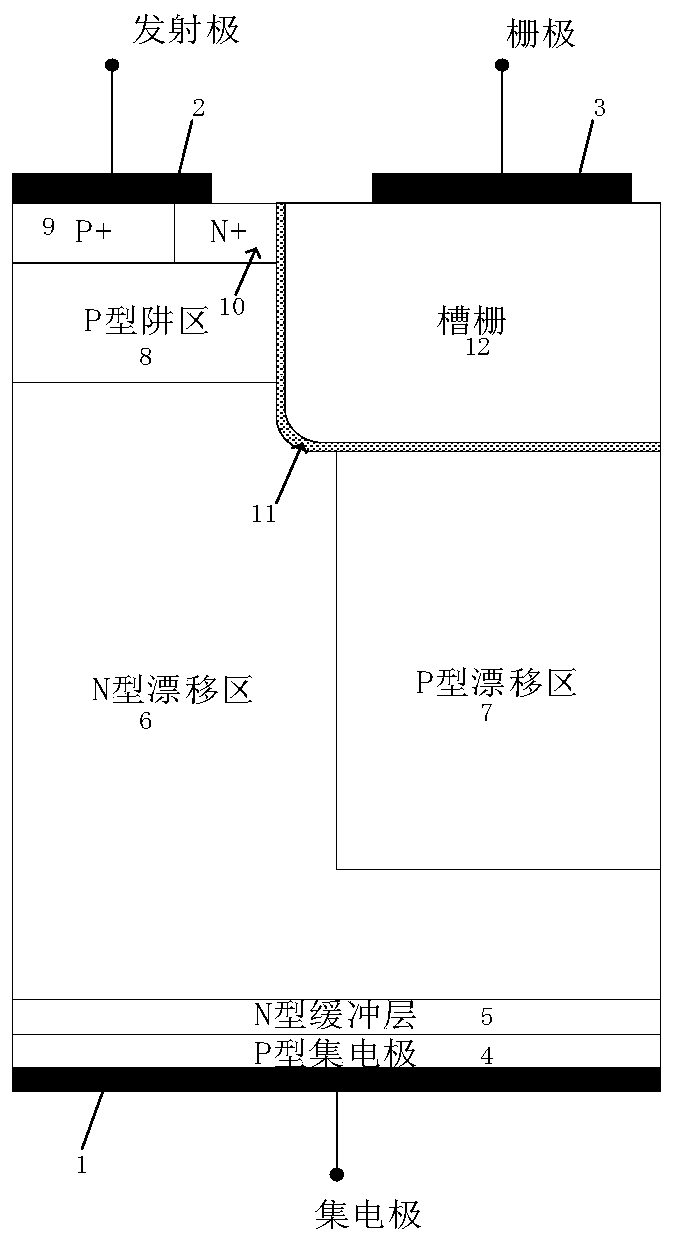

High withstand voltage and low loss super junction power device

ActiveCN110416294AReduce forward voltage dropHigh forward blocking voltageSemiconductor devicesVoltageSemiconductor

The invention belongs to the technical field of power semiconductors, and in particular relates to a high withstand voltage and low loss super junction power device. The device provided by the invention is characterized in that a pinch-off structure is arranged on a P-type drift region; the pinch-off structure is composed of pinch-off grooves and a P-type body contact region between the pinch-offgrooves; during forward conduction, the pinch-off structure pinches the middle P-type drift region, suppressing the collection of holes by the P-type drift region and improving the storage effect of carriers in the drift region; when the device is turned off, the P-type drift region is connected with an emitter through the P-type body contact region to be used as a hole extraction path to reduce the turn-off loss; when forward withstand voltage is applied, the P-type drift region contacts the emitter through the P-type body contact region, and the potential is 0; the P-type drift region has abetter auxiliary depletion effect; and the device has higher withstand voltage. Compared with a conventional super junction IGBT device, the device provided by the invention has lower on-voltage dropand better Von-Eoff discount. Compared with a P-column floating super junction IGBT device, the super junction IGBT device provided by the invention have higher forward withstand voltage.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Silicon carbide MOSFET device and preparation method thereof

PendingCN109755322AImprove freewheeling abilityReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETPower flow

The invention discloses a silicon carbide MOSFET device and a preparation method thereof. The silicon carbide MOSFET device comprises, form bottom to top, a leakage electrode, a N+substrate and N-epitaxial layer. The N-epitaxial layer is provided with first P-well areas, a first metal, second well areas and a second metal. The first P-well areas are provided with P+areas and N+areas; first ohmic contact is formed by the first metal, the upper surfaces of the P+areas and part of the upper surfaces of the N+areas; the second P-well areas are arranged between every two adjacent first P-well areas, the second P-well areas and the first P-well areas arranged on two side of the second P-well areas are all provided with first gaps, and grooves are encircled by the second P-well areas; and the second metal covers the surface of the groove to form second ohmic contact and the upper surface of the first gap to form Schottky contact. According to the silicon carbide MOSFET device, the flow-continuing ability is improved, and meanwhile the problem that the leakage current of the Schottky contact area in a high-pressure blockage mode is too large is solved.

Owner:厦门芯光润泽科技有限公司

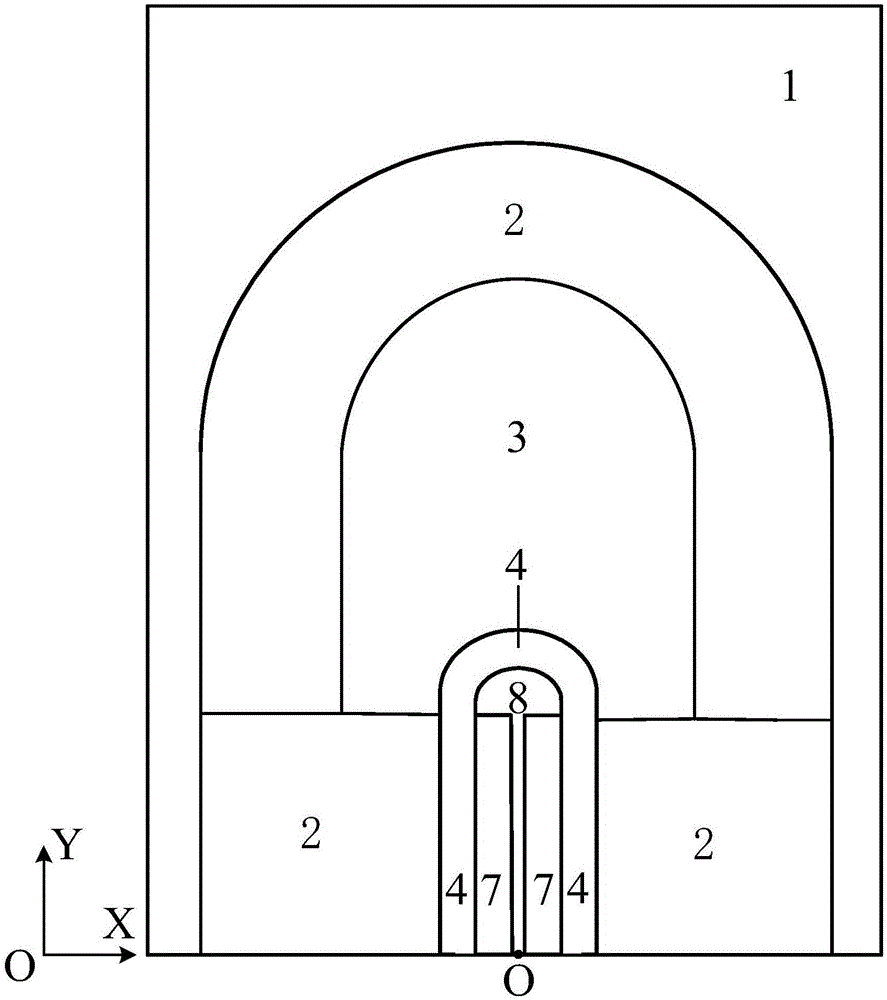

Junction terminal structure for transverse high voltage power device

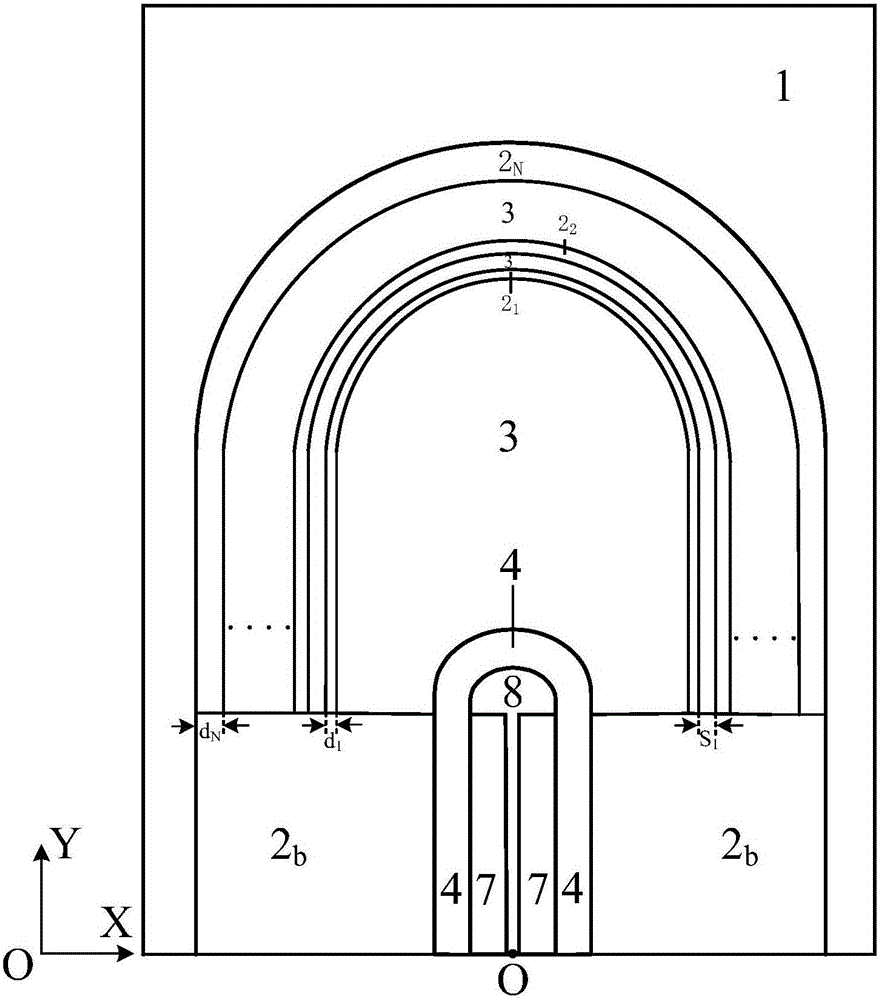

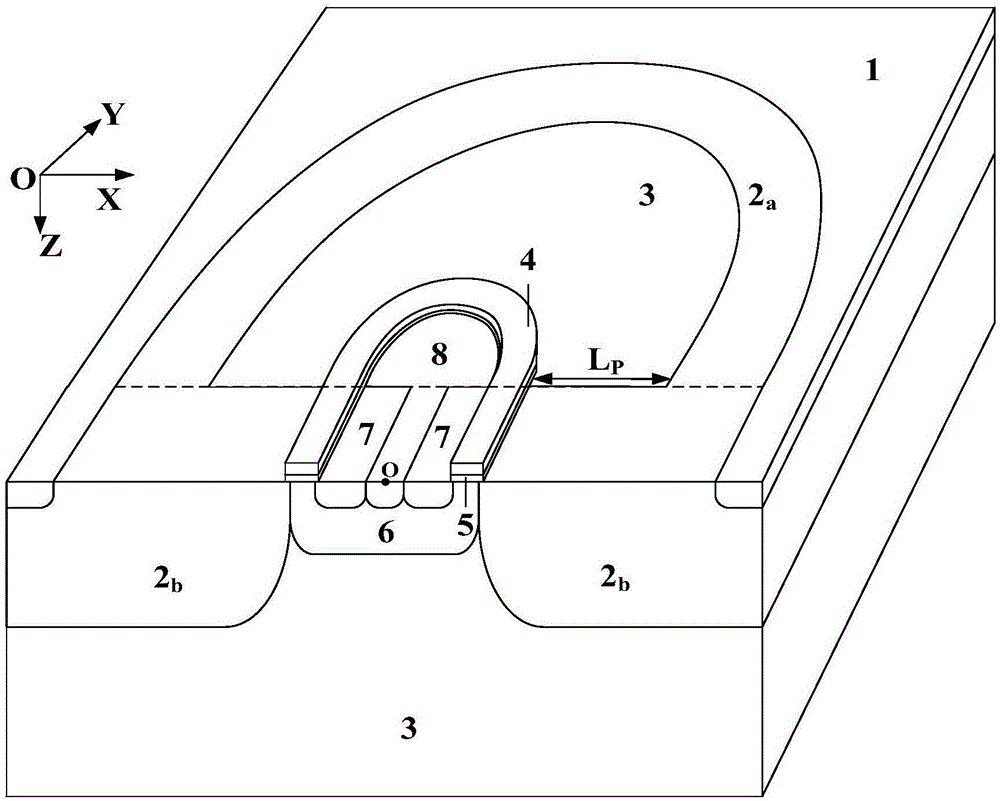

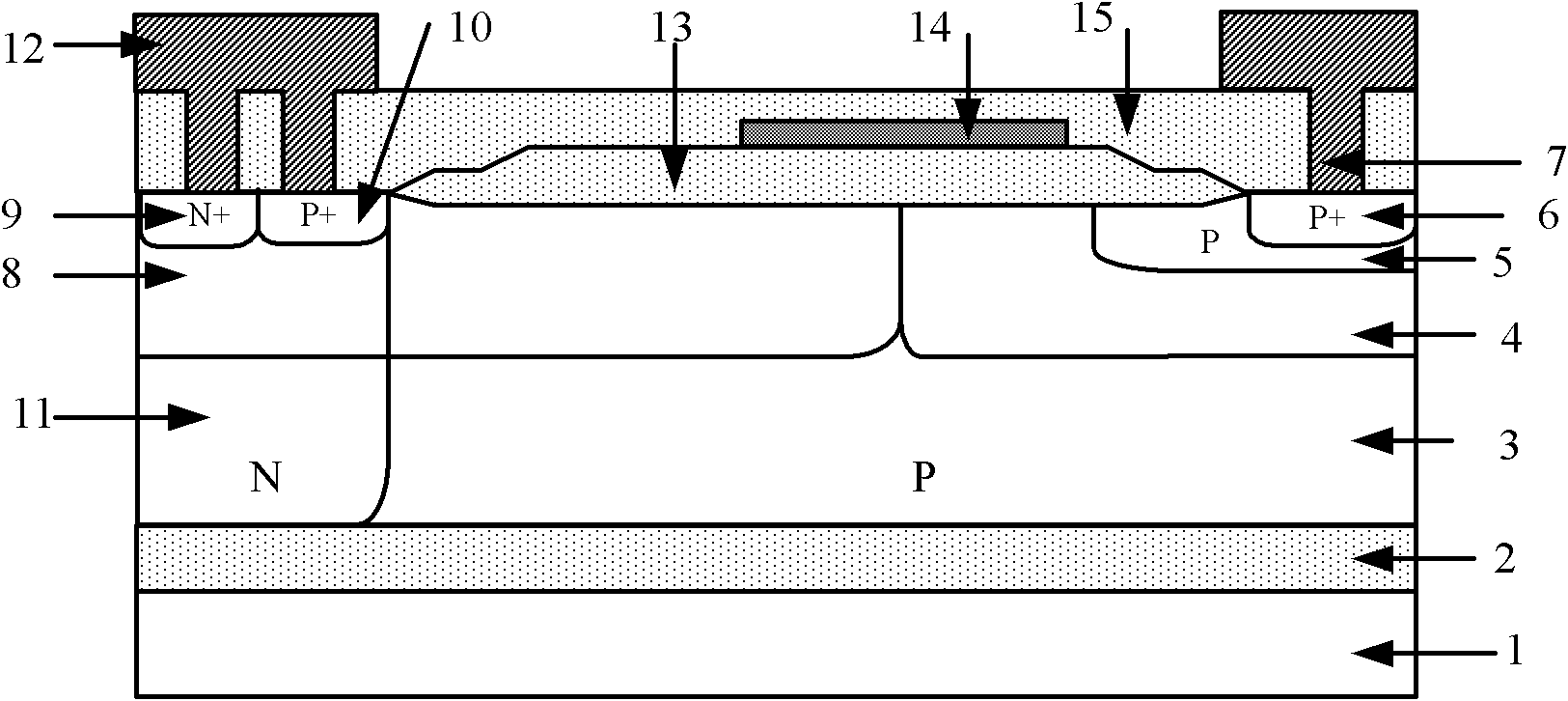

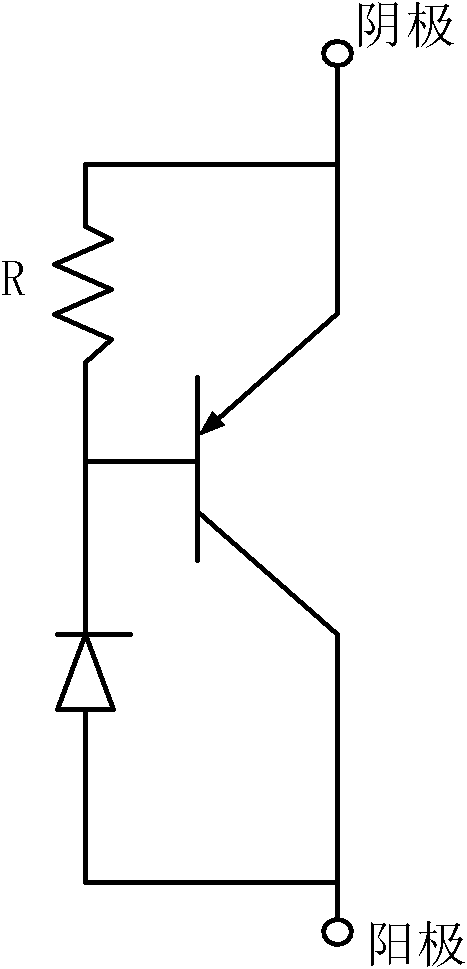

ActiveCN106252393AReduce doping concentrationReduce concentrationSemiconductor devicesHigh pressureGate oxide

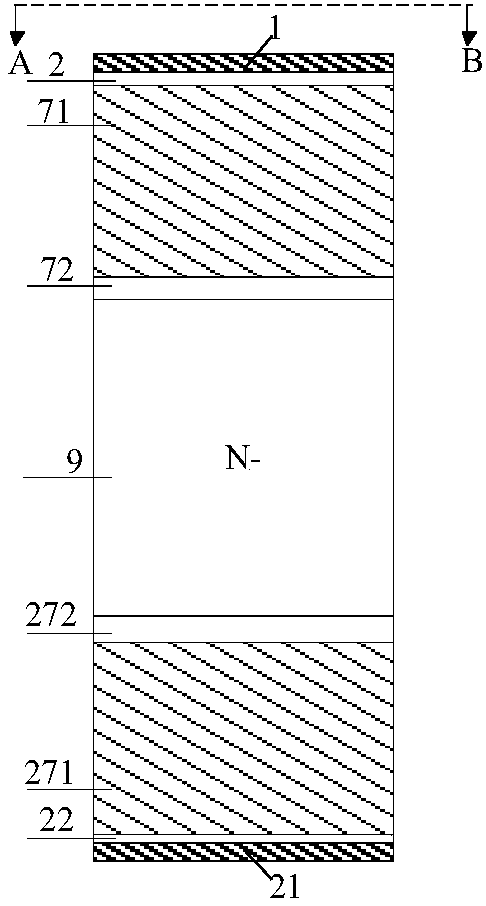

The invention provides a junction terminal structure for a transverse high voltage power device. The junction terminal structure comprises a linear junction terminal structure and a curvature junction terminal structure; the curvature junction terminal structure comprises a drain electrode N+ contact zone, an N type drift zone, a P type substrate, grid electrode polycrystalline silicon, a gate oxide layer, a P-well zone and a source electrode P+ contact zone; the N+ contact zone, the grid electrode polycrystalline silicon and the gate oxide layer in the curvature junction terminal structure are respectively connected with an N+ contact zone, a grid electrode polycrystalline silicon and a gate oxide layer in the linear junction terminal structure so as to form an annular structure; the N type drift zone is divided into N subzones which are 21, 22 ... 2N from an internal boundary to an external boundary; the drain electrode N+ contact zone encloses the subzones which are 21, 22 ... 2N. An N type dosage concentration at a junction between the N type drift zone and the P type substrate in a curvature junction terminal part in the junction terminal structure disclosed in the invention is much lower than that in a traditional structure, the N type drift zone can be effectively exhausted by the P type substrate, and therefore voltage resistance of a device can be well optimized.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

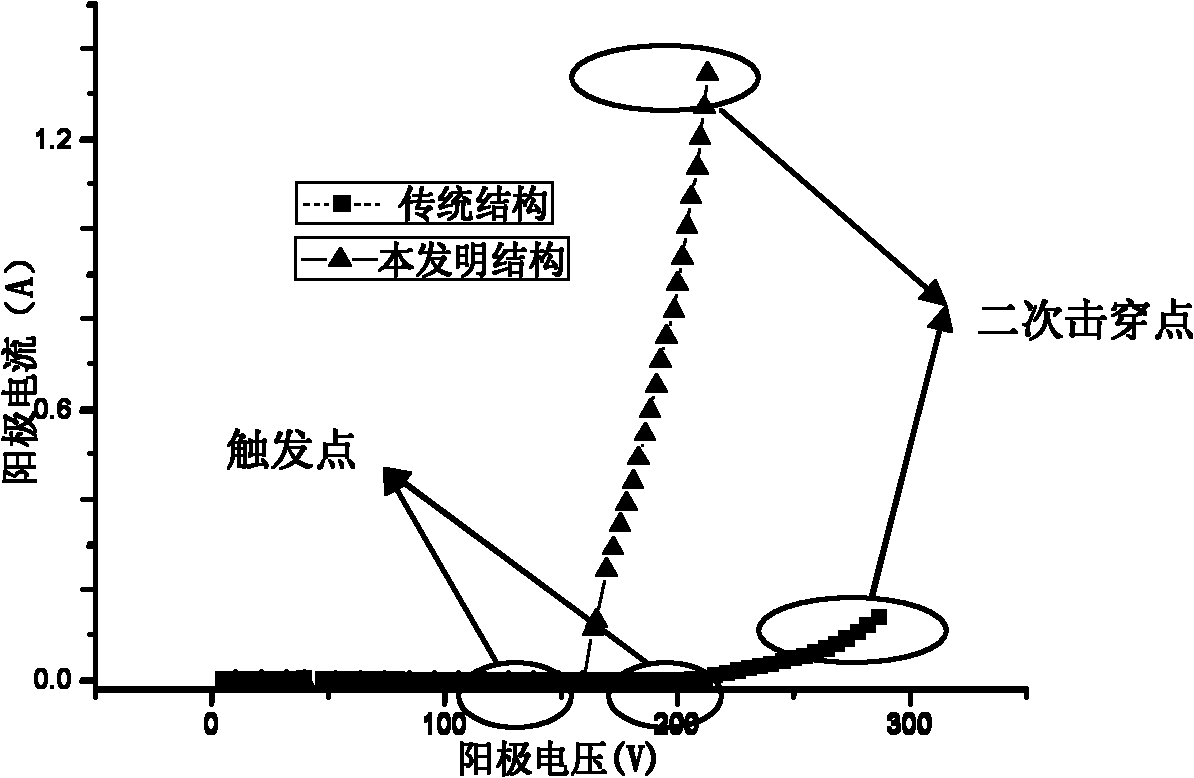

High-robustness back biased diode applied to high-voltage static protection

InactiveCN102130184AImprove robustnessDoes not change layout areaSemiconductor/solid-state device manufacturingSemiconductor devicesLow voltageHigh pressure

The invention discloses a high-robustness back biased diode applied to high-voltage static protection, comprising a P type substrate, wherein a buried oxide layer is arranged on the P type substrate; a P type epitaxial layer is arranged on the buried oxide layer; a first low-voltage P type well, a first low-voltage N type well and a second high-voltage N type well are arranged at the upper part of the P type epitaxial layer; a P type anode region is arranged in the first low-voltage P type well; an N type cathode region is arranged in the second high-voltage N type well and cathode metal is connected to the N type cathode region; and anode metal is connected to the P type anode region. The high-robustness back biased diode is characterized in that a P type cathode region connected to the cathode metal is arranged on the upper surface inside the second high-voltage N type well and is tightly attached to the right boundary of the N type cathode region; a second P type buffer well is arranged in the first low-voltage P type well; and the P type anode region is positioned in the second P type buffer well. By using the device, the trigger voltage in the static protection process can be effectively reduced and the secondary breakdown current of a lifting device is greatly improved, and thereby the high-robustness back biased diode has better robustness.

Owner:SOUTHEAST UNIV

Silicon carbide device terminal and manufacture method for the same

InactiveCN107507859AImprove pressure resistanceReduce peak electric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsSic substrate

The invention provides a silicon carbide device terminal and a manufacture method for the same. The manufacture method for the silicon carbide device terminal comprises steps of growing an N--SiC epitaxial layer on an N+-SiC substrate, preparing a P-Sic JTE area and an N type cutoff ring in the N-epitaxial layer, wherein the a shallow groove for depositing a first passivation layer is etched in the P-Sic JTE area and the N type cutoff ring is arranged on the outer edge of a device terminal, preparing a stacking layer structure on the surface of the N-Sic epitaxial layer, wherein the stacking layer structure comprises a second passivation layer, a polycrystalline silicon field plate, a third passivation layer and a metal field plate which are stacked successively from the bottom to the top, the polycrystalline silicon field plate and the metal field plate cover a P-SiC JTE area and part of the area between the P-SiC JTE and the N type cutoff ring, the metal field plate is directly arranged on the polycrystalline silicon field plate in part of the area where is away from one side of the N type cutoff ring and the polycrystalline silicon field plate is projected toward the outer edge direction of the device terminal on one side of the N type cutoff ring. The invention also provides a terminal of a silicon carbide device. The silicon carbide device terminal and the manufacture method for the same can improve charge resistance and reliability.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

AlGaN/GaN heterojunction Schottky diode device based on P-GaN cap layer and floating metal ring

ActiveCN110364574AUniform horizontal distributionPotential changes slowly laterallySemiconductor/solid-state device manufacturingDiodeHeterojunctionSchottky diode

The invention discloses an AlGaN / GaN heterojunction Schottky diode device based on a P-GaN cap layer and floating metal ring composite structure. The AlGaN / GaN heterojunction Schottky diode device comprises a substrate, and a GaN buffer layer, a channel layer, an AlGaN barrier layer and a passivation layer which are sequentially arranged on the substrate, an anode and a cathode are respectively arranged on two opposite sides of the upper surface of the AlGaN barrier layer, at least one combined structure is arranged on the AlGaN barrier layer between the anode and the cathode, and each combined structure comprises a first P-type GaN cap layer, a second P-type GaN cap layer and a floating metal ring; the first P-type GaN cap layer and the second P-type GaN cap layer are arranged on the AlGaN barrier layer at intervals, and the floating metal ring covers the upper surfaces of the first P-type GaN cap layer and the second P-type GaN cap layer and the AlGaN barrier layer between the firstP-type GaN cap layer and the second P-type GaN cap layer. The device adopts a structure combining the P-GaN cap layer and the floating metal ring, inhibits the electric field concentration effect, weakens the peak electric field, and ensures that the electric field is distributed more uniformly in the transverse direction, thereby reversely improving the breakdown voltage.

Owner:XIDIAN UNIV

High-performance MIS gate enhanced GaN-based high-electron-mobility transistor and preparation method thereof

ActiveCN111682064AIncrease transfer speedPrevent collapseSemiconductor/solid-state device manufacturingSemiconductor devicesHigh current densityHigh electron

The invention relates to a high-performance MIS gate enhanced GaN-based high-electron-mobility transistor and a preparation method thereof. The device comprises an AlGaN layer which is positioned on asubstrate, and the AlGaN layer is composed of an AlGaN barrier layer, a p-doped drift region and an n-doped drift region, wherein the p-doped drift region and the n-doped drift region are distributedon the two sides of the AlGaN barrier layer, the passivation layer is located between the source electrode and the drain electrode, and the groove extends into the barrier layer from the passivationlayer and fills the p-GaN region of the groove, the grid electrode located on the p-GaN region and the field plate. According to the invention, n / p doped layers with different gradients are formed onthe two sides of the barrier layer, and the current crowding in the source-drain direction is suppressed; meanwhile, p-GaN is connected below the grid electrode, the upper portion of the grid electrode makes contact with the field plate, charge congestion below the grid electrode is controlled, electron transport of the two-dimensional electron gas channel is smoother, and under the condition thathigh current density and high electron mobility of the device are guaranteed, adjustable and controllable improvement of breakdown voltage is achieved, on-resistance is reduced, and power characteristics and reliability of the device are improved.

Owner:SOUTH CHINA NORMAL UNIVERSITY

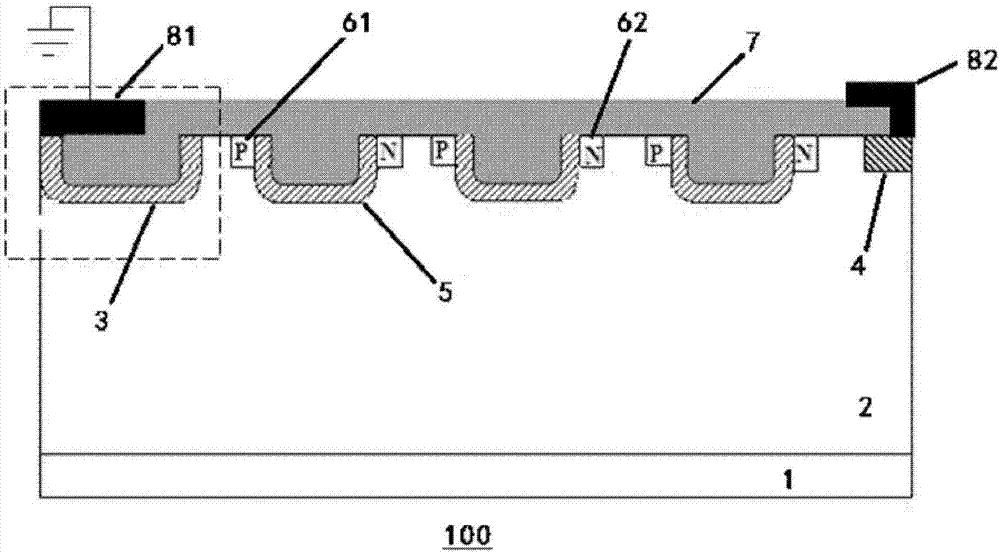

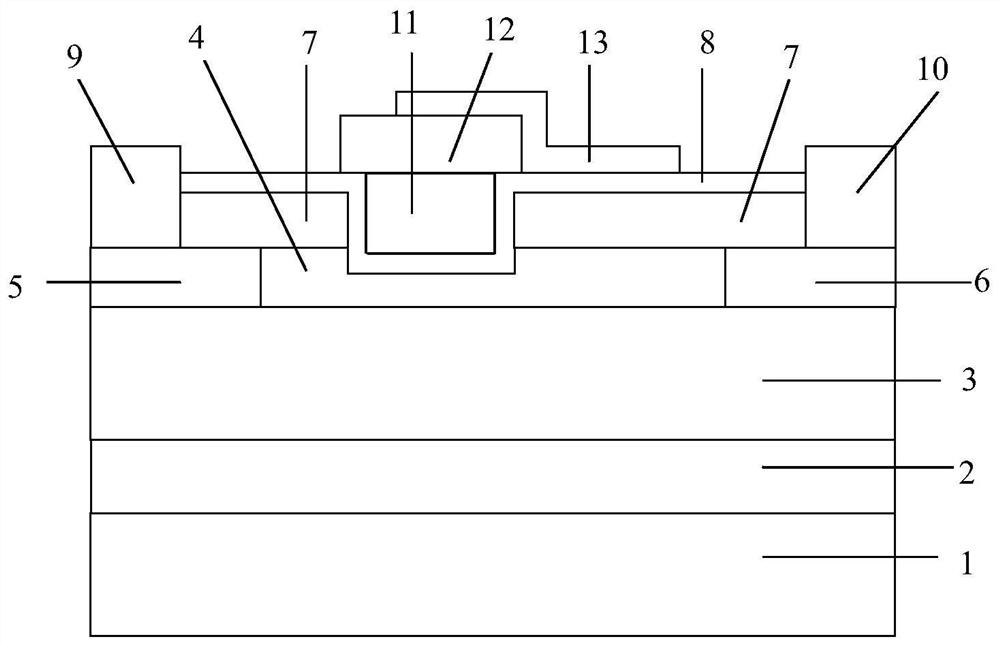

Silicon carbide double-groove MOSFET integrated with channel diode

ActiveCN113990923ASmall pressure dropImprove reliabilityEfficient power electronics conversionSolid-state devicesMOSFETCarbide silicon

The invention belongs to the technical field of power semiconductors, and particularly relates to a silicon carbide double-groove MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) integrated with an channel diode. The MOSFET is mainly characterized in that: firstly, a channel diode is integrated, when a device is in a follow current working mode, the channel diode is conducted to achieve a follow current function, conduction of a body diode is effectively restrained by reducing reverse conduction voltage drop, and meanwhile the influence caused by bipolar degradation is eliminated; and secondly, an electric field is modulated through a P-type region below the source groove, so that the peak of the electric field at the corner of silicon dioxide at the bottom of the gate groove is reduced, and the breakdown voltage and the reliability of the device in a blocking working mode are improved;.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Silicon carbide power device terminal and manufacturing method therefor

InactiveCN107658213AReduce peak electric fieldReduce areaSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsDielectric layer

The invention provides a manufacturing method of a silicon carbide power device terminal. The manufacturing method comprises the steps of 1, providing an N<+>-SiC substrate, and forming an N<->-SiC epitaxial layer on the N<+>-SiC substrate; 2, preparing P type main junctions, P type field limiting rings, a P-i-N structure and N type cut-off rings in the N<->-SiC epitaxial layer, wherein shallow grooves are etched in the P type main junctions and the P type field limiting rings, and the shallow grooves are filled with a dielectric layer; the P-i-N structure is positioned between the P type mainjunctions and the adjacent P type field limiting rings, and in the N<->-SiC epitaxial layer between adjacent P type field limiting rings; and the P-i-N structure comprises a P type doped region and an N type doped region which are distributed in a direction parallel to the terminal surface and parallel to the P type main junctions; and 3, depositing a passivation layer for covering the terminalsurface on the surface of the N<->-SiC epitaxial layer. The invention also provides the silicon carbide power device terminal. By virtue of the manufacturing method, the breakdown voltage and reliability of the device can be improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

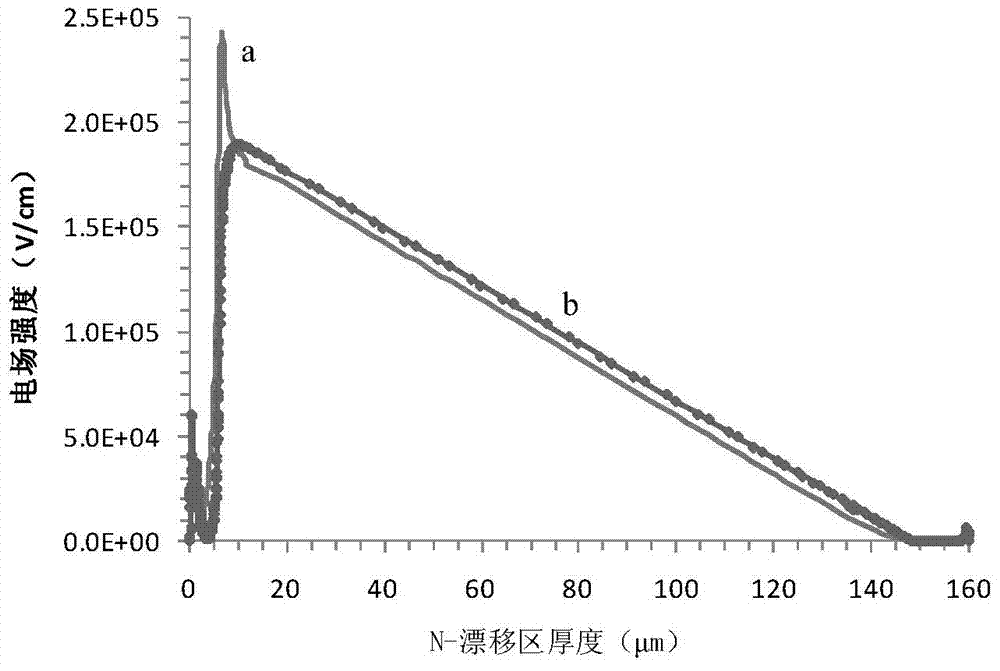

Trench type MOS structure Schottky diode and preparation method thereof

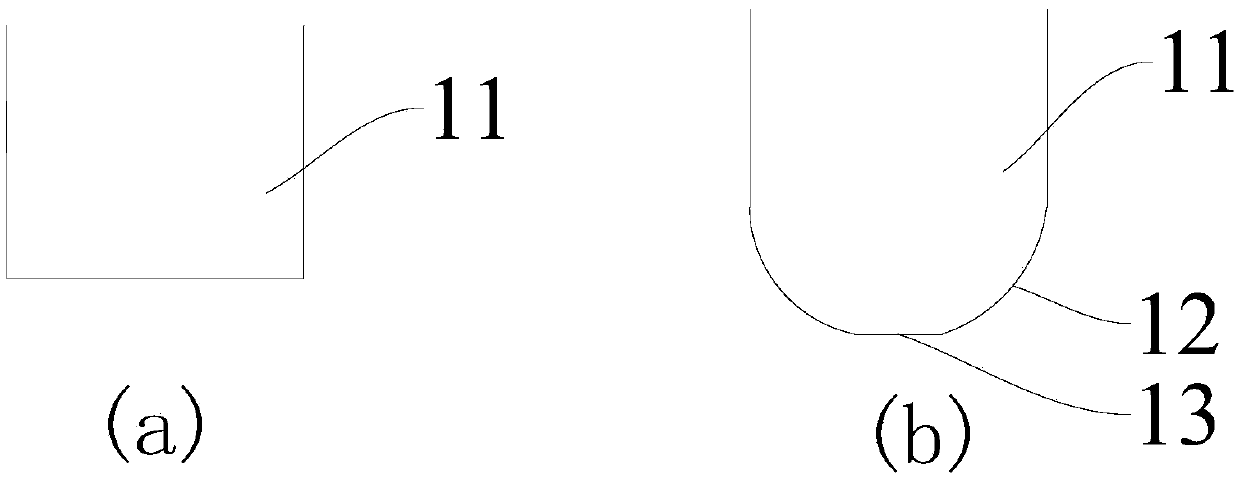

PendingCN111081754AImproved reverse blocking characteristicsThe reverse blocking feature does not affect theSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical field strengthImpurity doping

The invention provides a trench type MOS structure Schottky diode and a preparation method thereof. The trench type MOS structure Schottky diode comprises an N-type doped substrate, an N-type doped epitaxial layer arranged on the upper surface of the N-type doped substrate, and a plurality of trenches extending from the upper surface of the N-type doped epitaxial layer to the N-type doped epitaxial layer; doping concentration in the N-type doped epitaxial layer is gradually increased from top to bottom. Therefore, the impurity doping concentration of the N-type doped epitaxial layer in the Schottky diode is changed (the doping concentration in the N-type doped epitaxial layer is gradually increased from top to bottom); the electric field intensity distribution of the N-type doped epitaxiallayer can be changed, so that peak electric fields at the corners of the bottoms of the trenches are reduced; the reverse blocking characteristic of the Schottky diode and the forward conduction characteristic of the device are improved, namely, the reverse leakage current of the Schottky diode is reduced, and the reverse breakdown voltage of the Schottky diode is increased.

Owner:BYD SEMICON CO LTD +1

Longitudinal high voltage power semiconductor device structure with low relative dielectric constant buried layer

InactiveCN111554748AGuaranteed withstand voltage requirementsIncrease the on-resistanceSemiconductor devicesPower semiconductor deviceEngineering

The invention discloses a longitudinal high-voltage power semiconductor device structure with a low relative dielectric constant buried layer. The semiconductor device structure comprises an N drift region, a P base region and an N+ source region, wherein a gate oxide layer is deposited in a trench at the periphery of the P base region and the N+ source region, and a gate conductive dielectric layer is deposited on the gate oxide layer. The semiconductor device structure is characterized in that an insulating layer is additionally arranged in the N+ drift region below the gate oxide layer; theinsulating layer is made of an insulating material of which the relative dielectric constant is less than that of the gate oxide layer; and the material of the device is Si, SiC or GaN. By additionally arranging the insulating layer with a certain thickness below the trench, the electric field distribution between the gate and the drain can be adjusted, so that the electric field distribution ofthe internal region of the device is changed, the withstand voltage of the device is also improved, and the electric field distribution in the device is not only limited by the doping concentration ofa material any more.

Owner:陕西半导体先导技术中心有限公司

A high sustaining voltage n-type electrostatic protection semiconductor device

InactiveCN102280472AKirk effect inhibitionIncrease holding voltageSemiconductor devicesPolysilicon gateP type doping

A high sustaining voltage N-type electrostatic protection semiconductor device, comprising: a semiconductor substrate, on which a buried oxide layer is arranged, above which is an N-type doped semiconductor drift region, and a P well region is arranged on Above the N-type doped semiconductor drift region, while the field oxide layer, metal layer, gate oxide layer, polysilicon gate and oxide layer are arranged on the upper surface of the device, and the N-type source region and the P-type contact region are arranged in the P well , characterized in that: a P-type doped semiconductor region is also provided in the P well, and the P-type doped semiconductor region is located under the N-type source region and the gate oxide layer. The device can effectively increase the holding voltage during electrostatic protection, so the device has better anti-latch-up ability.

Owner:SOUTHEAST UNIV

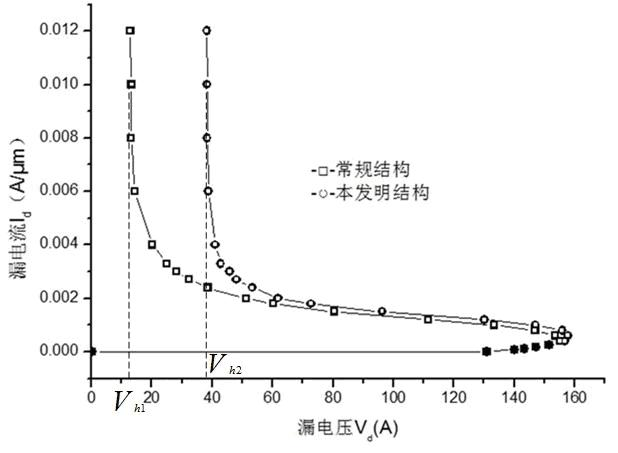

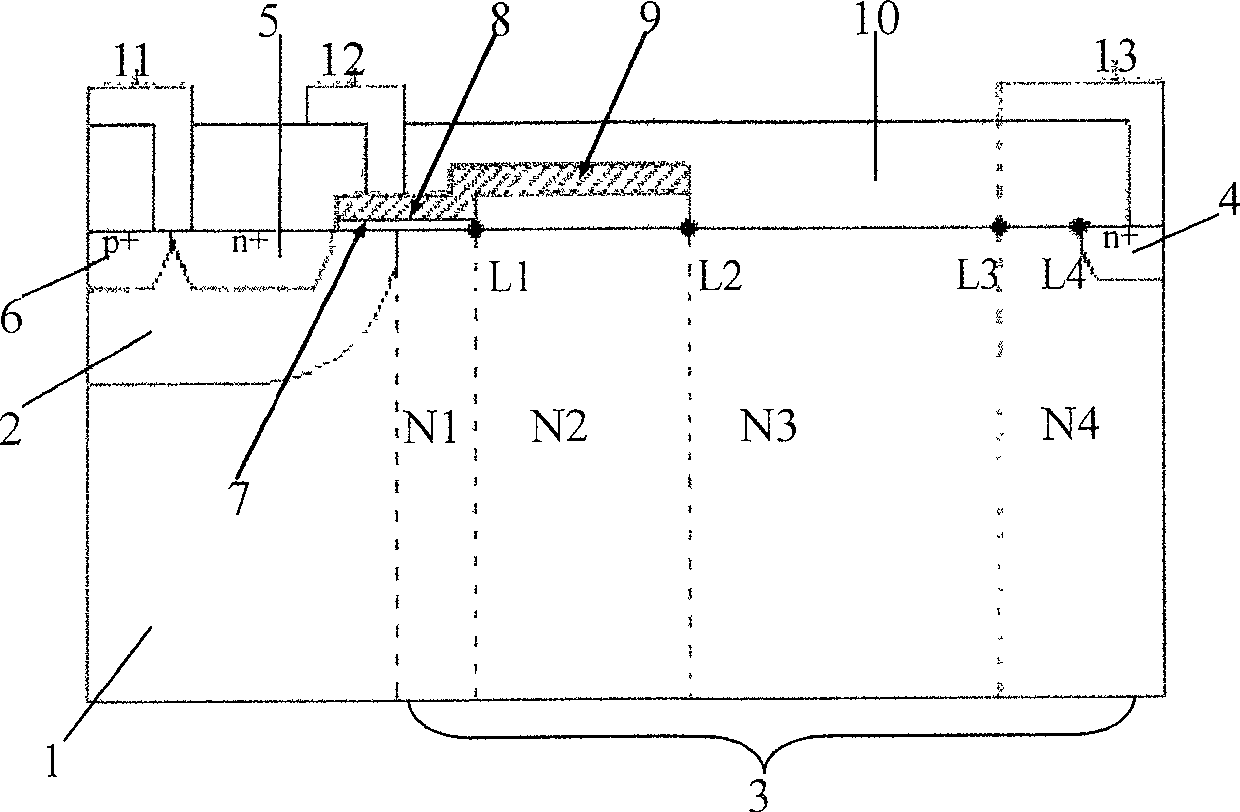

High voltage N-shape metal oxide semiconductor tube and its preparing method

InactiveCN100470840CIncrease concentrationReduce peak electric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryPolysilicon gate

This invention relates to a high pressure N-type MOS tube with linear dope, in which, a P-type trap and a N-type drift region are set on the N-type substrate, a P-type contact hole and a N-type source are set in the P-type trap, a N-type leak is set in the N-type drift region, a grid oxidation layer is set above the P-type trap and the N-type drift region, a polysilicon grid is set above the grid oxidation layer and above the interface of the trap and the drift region, a filed oxidation layer is set above the grid oxidation layer and the polysilicon grid, Al leads are connected on the contact hole, the N-type sourc, the polysilicon grid and the N-type leak, polysilicon field pole plates connected with the polysilicon grid are set in the field oxidation layer, the N-type drift region is composed of a first, second, third and fourth regions arrayed along the source and the leak orderly, the doped concentration becomes smaller from the fourth, third, second and the first region.

Owner:SOUTHEAST UNIV

A high sustaining voltage p-type electrostatic protection semiconductor device

InactiveCN102280471AKirk effect inhibitionIncrease holding voltageSemiconductor devicesPolysilicon gateSemiconductor

A high-maintenance voltage P-type electrostatic protection semiconductor device, comprising: a semiconductor substrate, a buried oxide layer is arranged on the semiconductor substrate, a P-type doped semiconductor drift region is placed on the buried oxide layer, and the N well region is arranged on Above the P-type doped semiconductor drift region, while the field oxide layer, metal layer, gate oxide layer, polysilicon gate and oxide layer are arranged on the upper surface of the device, and the P-type source region and N-type contact region are arranged in the N well , characterized in that an N-type doped semiconductor region is also provided in the N well, and the N-type doped semiconductor region is located under the P-type source region and the gate oxide layer. The device can effectively increase the holding voltage during electrostatic protection, so the device has better anti-latch-up ability.

Owner:SOUTHEAST UNIV

Lateral transistor with AlGaN/GaN heterojunction and production method of lateral transistor

ActiveCN109888009AImprove performanceBreak through the problem of substantial increase in on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSpontaneous polarizationGallium nitride

The invention provides a lateral transistor with an AlGaN / GaN heterojunction and a production method of the lateral transistor. A part of a drift region of the device is the AlGaN / GaN heterojunction.The AlGaN / GaN heterojunction forms a high-density two-dimensional electron gas (2DEG) at a heterojunction interface through spontaneous polarization and piezoelectric polarization effects, the 2DEG has a high migration rate in a heterojunction conducting channel, and therefore the lateral transistor provided with the AlGaN / GaN heterojunction has low conduction resistance. When the device is switched off, the 2DEG is exhausted, meanwhile a new electric field peak is introduced into the surface of the device, and therefore a peak electric field at a grid edge of the device is lowered. A galliumnitride material is formed through epitaxy on a substrate material, the heterojunction between a gallium nitride epitaxial layer and a substrate optimizes longitudinal electric field distribution of the transistor, and therefore the breakdown voltage of the device is increased.

Owner:XIDIAN UNIV

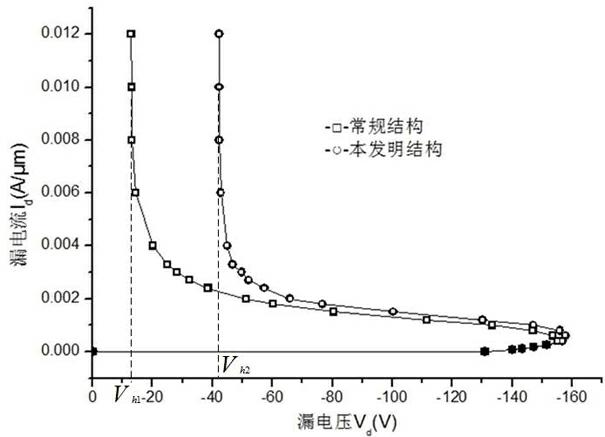

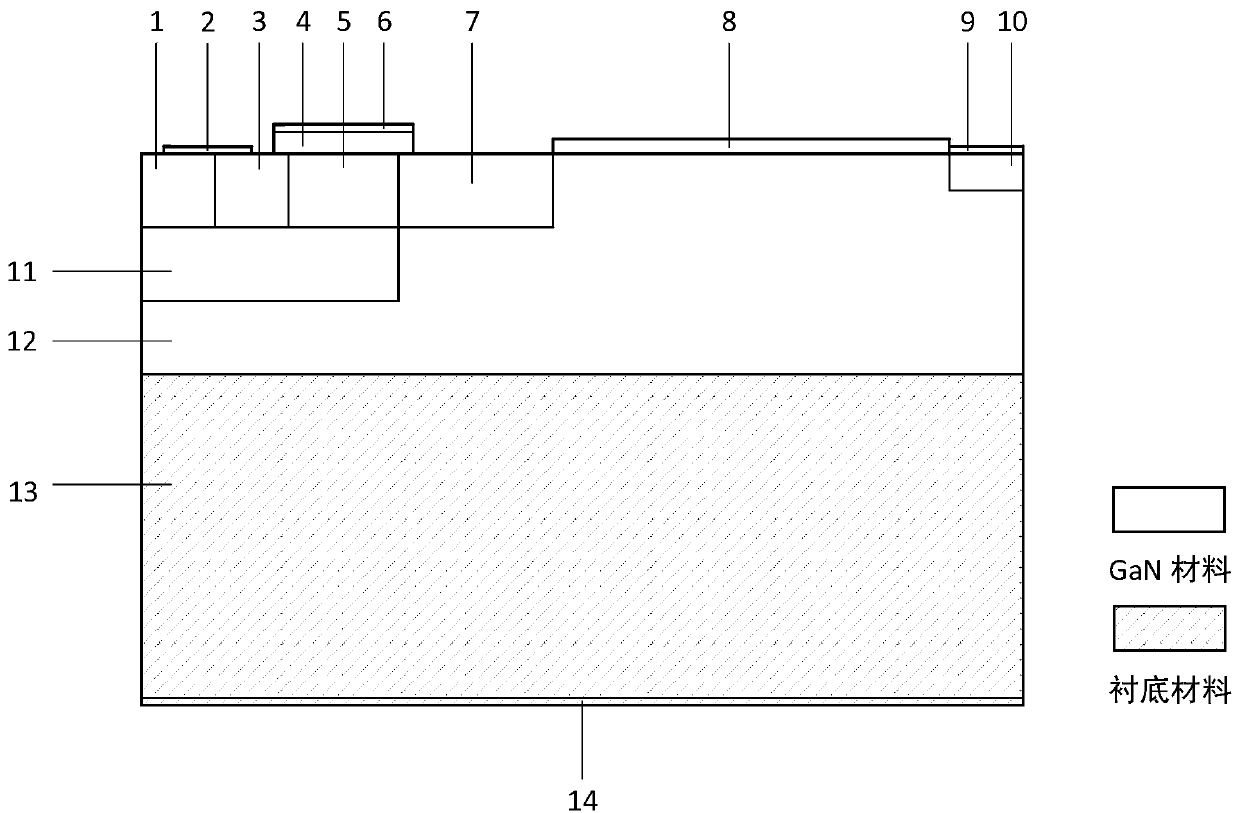

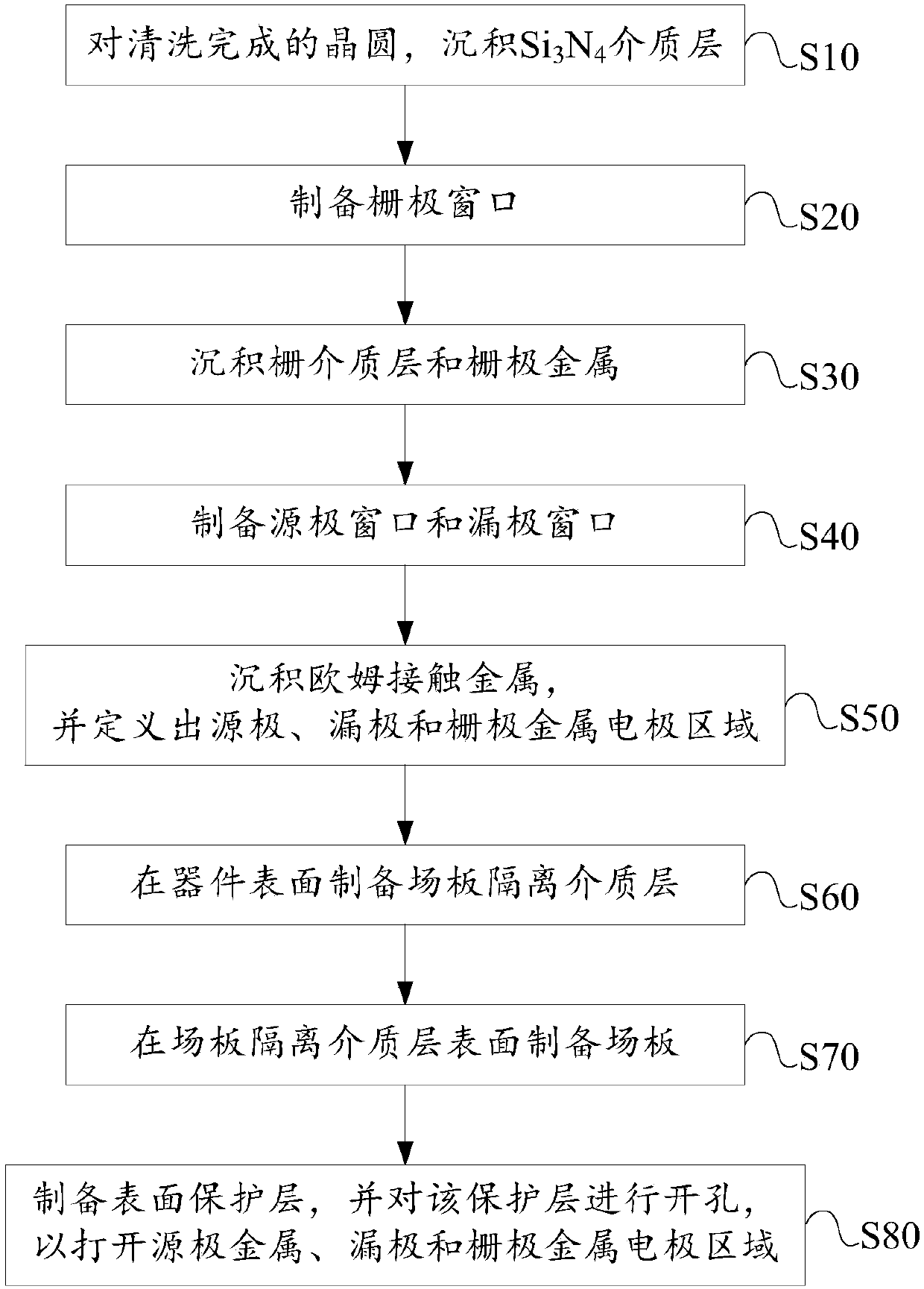

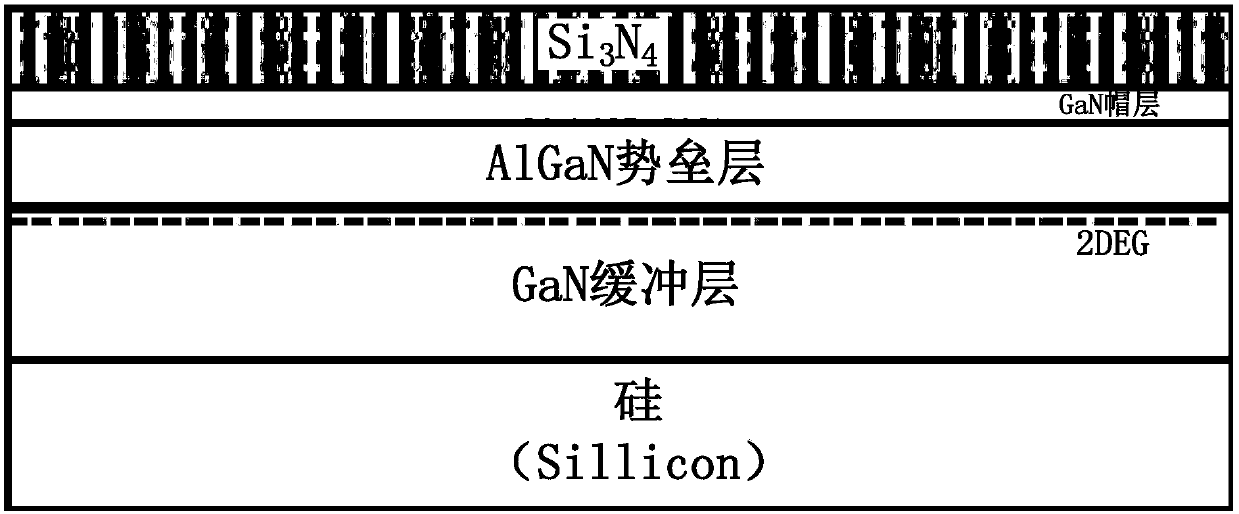

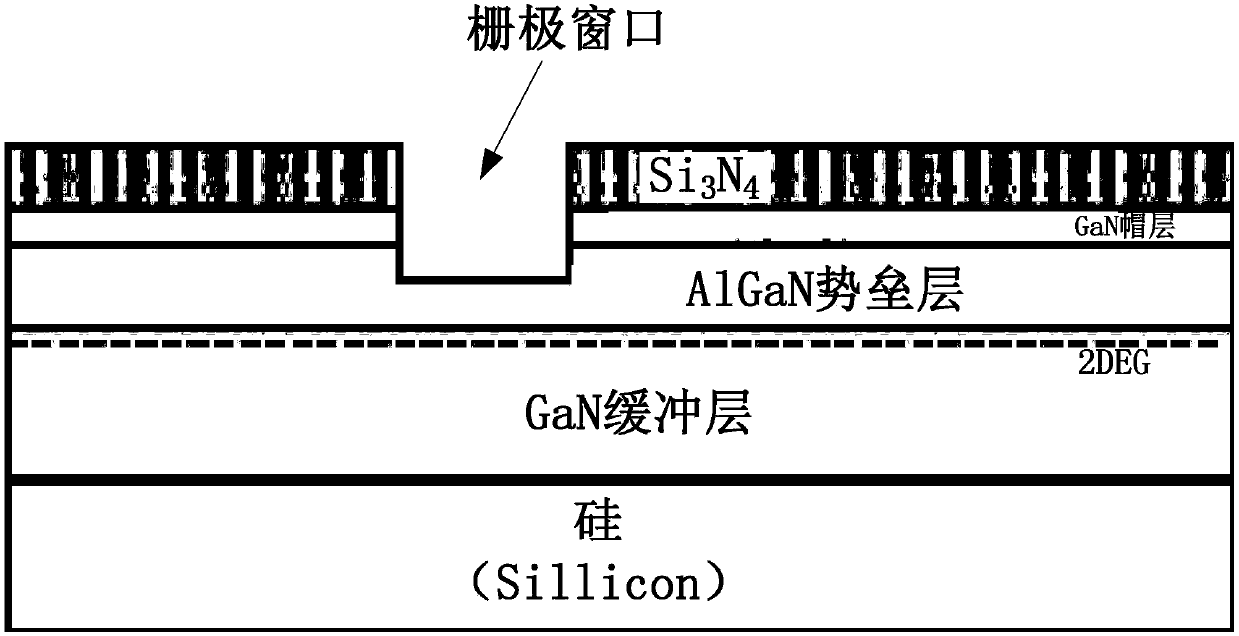

Method for improving voltage withstanding performance of MIS-HEMT and MIS-HEMT

InactiveCN107623031AGood pressure characteristicsImprovement and enhancement of withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricPeak value

The invention provides a method for improving voltage withstanding performance of a MIS-HEMT and the MIS-HEMT. The method comprises the following steps: for a cleaned wafer, depositing a Si3N4 dielectric layer; preparing a gate window; depositing a gate dielectric layer and gate metal; preparing a source window and a drain window; depositing ohm contact metal, and defining a source metal electrodearea, a drain metal electrode area and a gate metal electrode area; preparing a field plate isolation medium layer on the surface of the device; preparing a field plate on the surface of the field plate isolation medium layer; and preparing a surface protecting layer, and carrying out trepanning on the protecting layer to open the source metal electrode area, the drain metal electrode area and the gate metal electrode area. By introducing the field plate between a gate and a drain, electric field distribution in a channel is changed, and peak electric filed between the gate and the drain is reduced, thereby achieving a purpose of improving and increasing the voltage withstanding performance of the MIS-HEMT.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

Gallium nitride lateral transistor with AlGaN/GaN heterojunction and manufacturing method of gallium nitride lateral transistor

ActiveCN109817711AChange the electric field distributionReduce conduction lossSemiconductor/solid-state device manufacturingSemiconductor devicesHigh densityGallium nitride

The invention provides a gallium nitride lateral transistor with an AlGaN / GaN heterojunction and a manufacturing method of the gallium nitride lateral transistor. A partial drift region of the transistor is an AlGaN / GaN heterojunction; the AlGaN / GaN heterojunction forms high-density two-dimensional electron gas (2DEG) at the interface of the heterojunction through spontaneous polarization and piezoelectric polarization effects; and the two-dimensional electron gas has very high mobility, so that the novel gallium nitride lateral transistor with the AlGaN / GaN heterojunction has very low on-resistance. When the transistor is turned off, the 2DEG is exhausted; and meanwhile, a new electric field peak is introduced to the surface of the transistor, so that the peak electric field at the edge of the gate of the lateral transistor is reduced, and the breakdown voltage of the transistor is improved.

Owner:XIDIAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com