Method for improving voltage withstanding performance of MIS-HEMT and MIS-HEMT

A technology of MIS-HEMT and process method, applied in the field of semiconductor device manufacturing process, can solve the problems of large epitaxy defects, unfavorable application of high-density integrated circuits, and increase of device area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

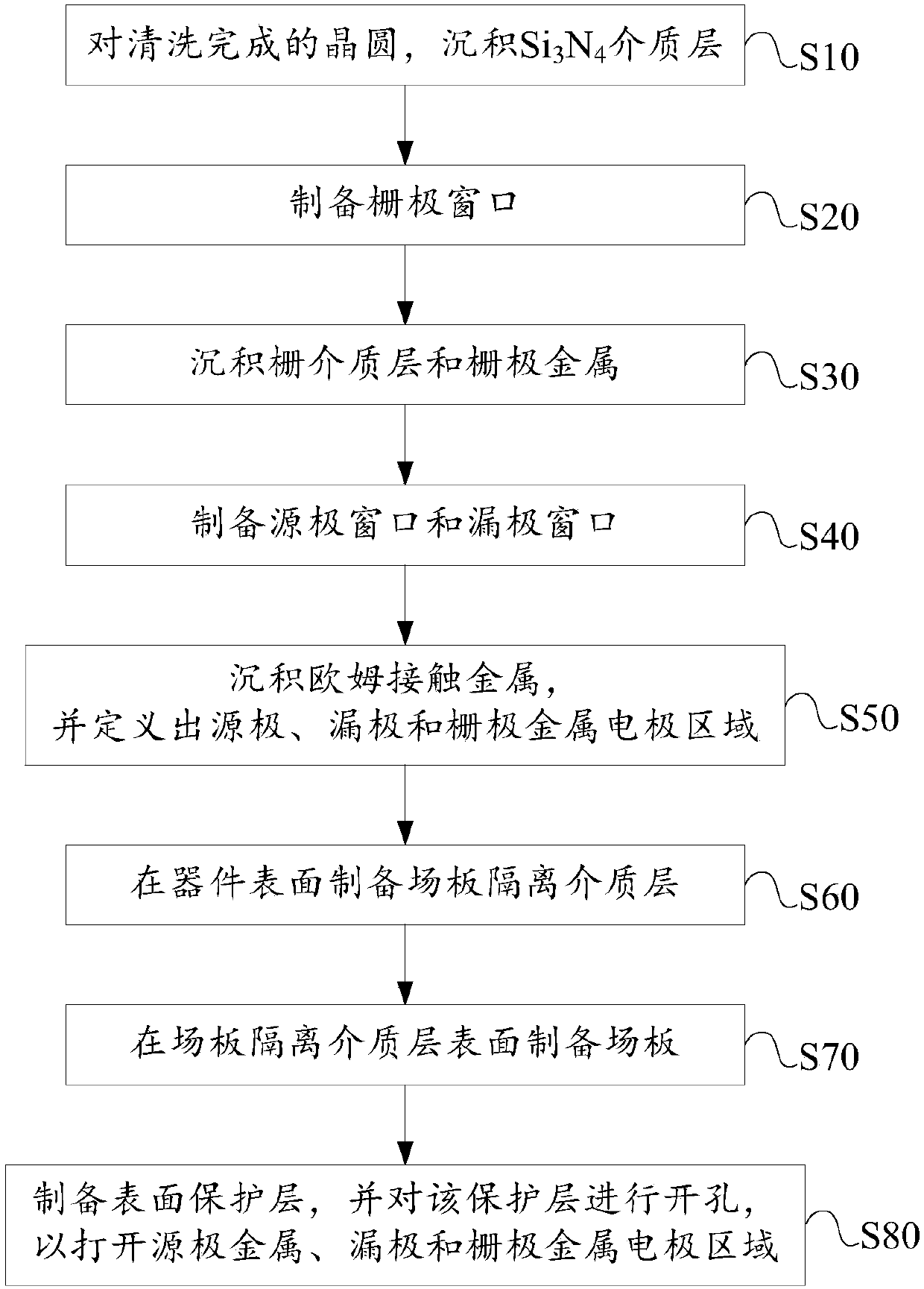

Method used

Image

Examples

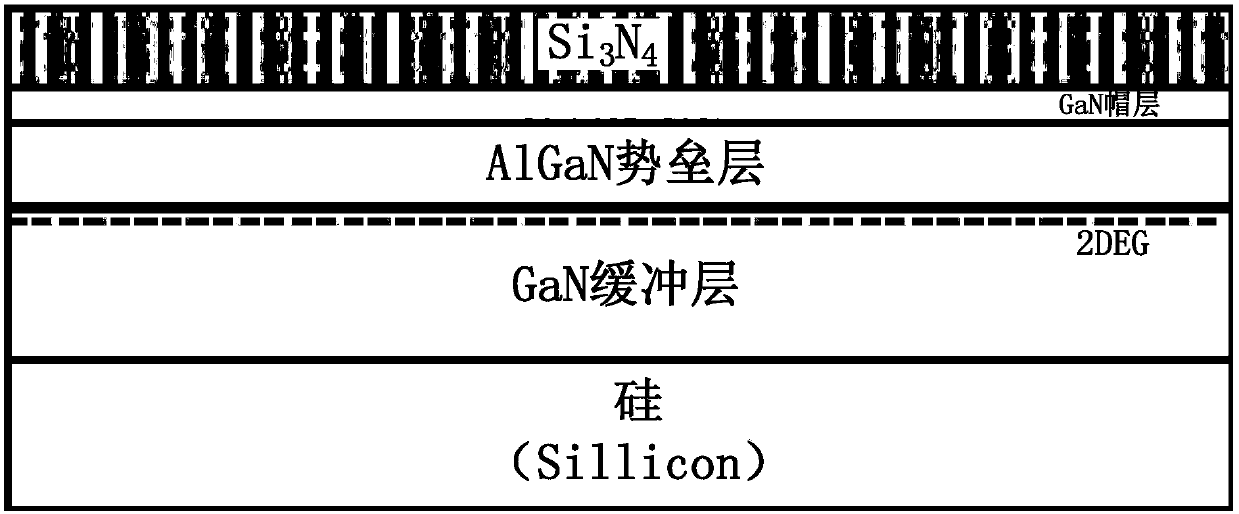

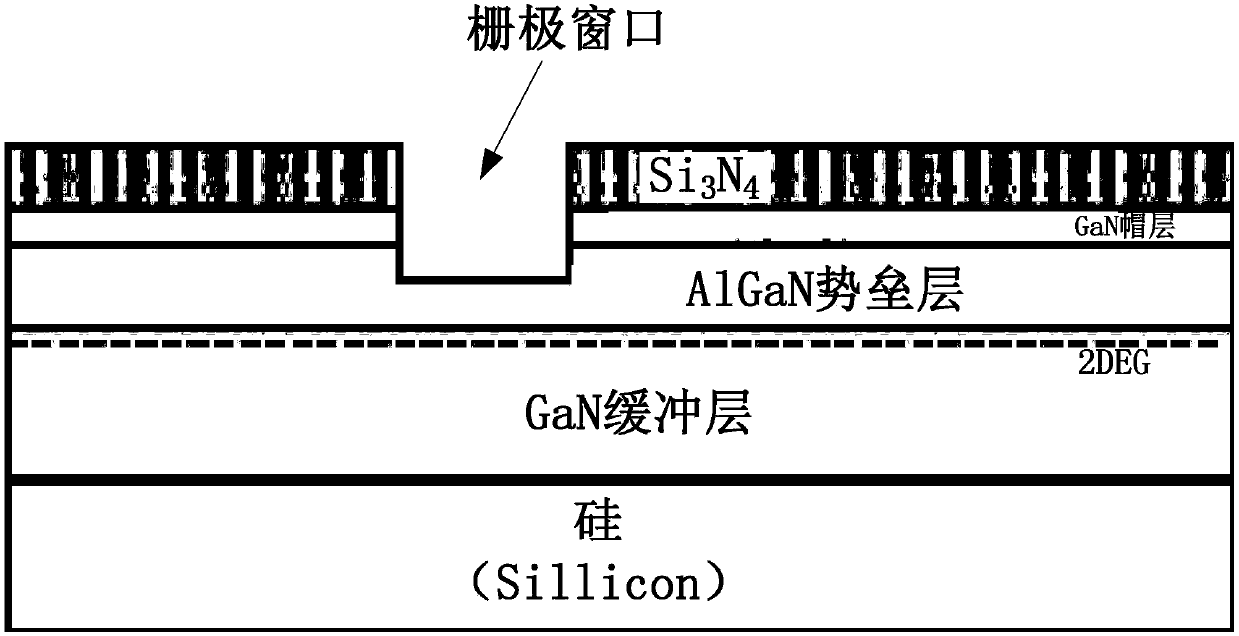

Embodiment Construction

[0043] The present invention will be further described in detail below through specific embodiments in conjunction with the accompanying drawings. Wherein, similar elements in different embodiments adopt associated similar element numbers. In the following embodiments, many details are described in order to enable the application to be better understood. However, those skilled in the art can easily recognize that some of the features can be omitted in different situations, or can be replaced by other elements, materials, and methods. In some cases, some operations related to the application are not shown or described in the description, this is to avoid the core part of the application being overwhelmed by too many descriptions, and for those skilled in the art, it is necessary to describe these operations in detail Relevant operations are not necessary, and they can fully understand the relevant operations according to the description in the specification and general technic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More