A high sustaining voltage p-type electrostatic protection semiconductor device

A technology with high maintenance voltage and electrostatic protection, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of design and application limitations of electrostatic protection, low maintenance voltage of P-type lateral double-diffused metal oxide semiconductor transistors, etc., to achieve Reduces the risk of latch-up, saves costs, and improves the effect of maintaining voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

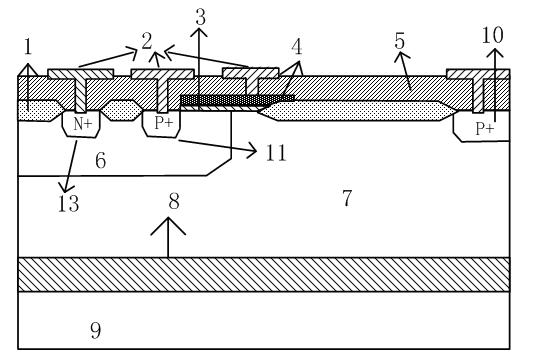

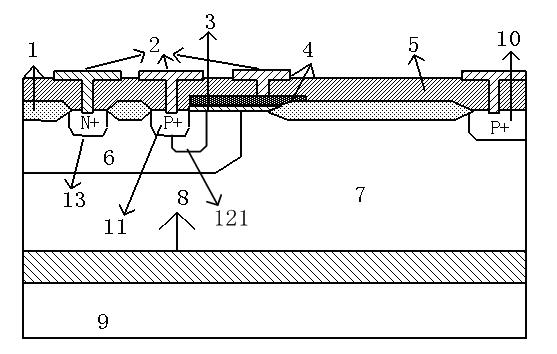

[0017] refer to figure 2 , a high sustain voltage P-type electrostatic protection semiconductor device, comprising: a semiconductor substrate 9, a buried oxide layer 8 is arranged on the semiconductor substrate 9, a P-type doped semiconductor region 7 is arranged on the buried oxide layer 8, and P-type doped semiconductor region 7 is provided with N well 6 and P-type drain region 10, is provided with P-type source region 11 and N-type contact region 13 on N well 6, is provided with gate oxide layer on the surface of N well 6 3 and the gate oxide layer 3 extends from the N well 6 to the P-type doped semiconductor region 7, and the P-type source region 11 on the surface of the N well 6, the N-type contact region 13 and the area other than the gate oxide layer 3 and the P-type doped A field oxide layer 1 is provided in the area other than the P-type drain region 10 on the surface of the semiconductor region 7, and a polysilicon gate 4 is provided on the surface of the gate oxide...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More