A high sustaining voltage n-type electrostatic protection semiconductor device

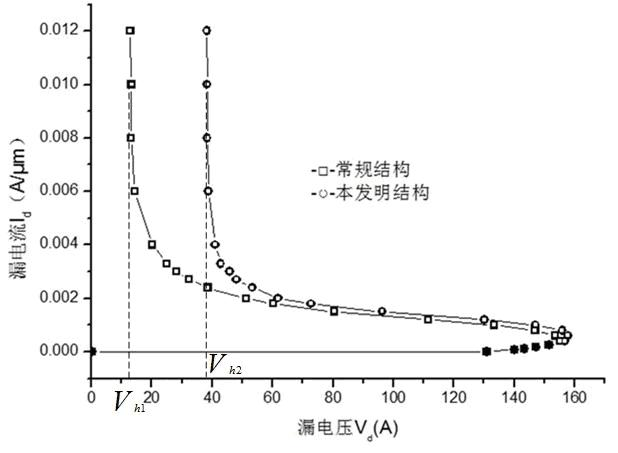

A technology with high sustaining voltage and electrostatic protection, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of low sustaining voltage of N-type lateral double-diffused metal oxide semiconductor transistors, design and application limitations of electrostatic protection, and achieve Reduces the risk of latch-up, saves costs, and improves the effect of maintaining voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

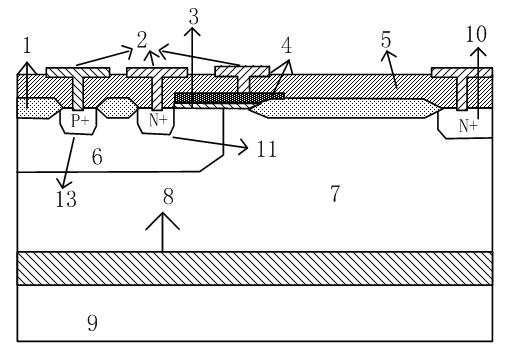

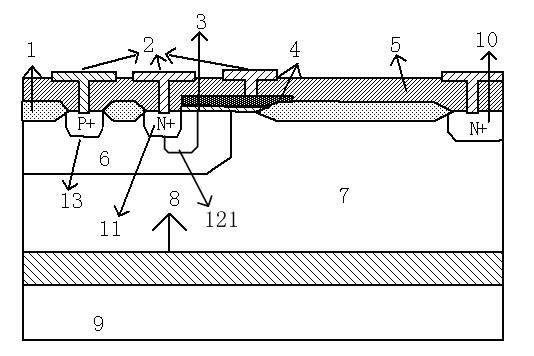

[0017] refer to figure 2 , a high sustain voltage N-type electrostatic protection semiconductor device, comprising: a semiconductor substrate 9, a buried oxide layer 8 is arranged on the semiconductor substrate 9, an N-type doped semiconductor region 7 is arranged on the buried oxide layer 8, and N-type doped semiconductor region 7 is provided with a P well 6 and an N-type drain region 10, an N-type source region 11 and a P-type contact region 13 are arranged on the P well 6, and a gate oxide layer is provided on the surface of the P well 6. 3 and the gate oxide layer 3 extends from the P well 6 to the N-type doped semiconductor region 7, and the N-type source region 11 on the surface of the P well 6, the P-type contact region 13 and the area other than the gate oxide layer 3 and the N-type doping A field oxide layer 1 is provided in the area other than the N-type drain region 10 on the surface of the semiconductor region 7, and a polysilicon gate 4 is provided on the surface...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More