Patents

Literature

224 results about "Design Error" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

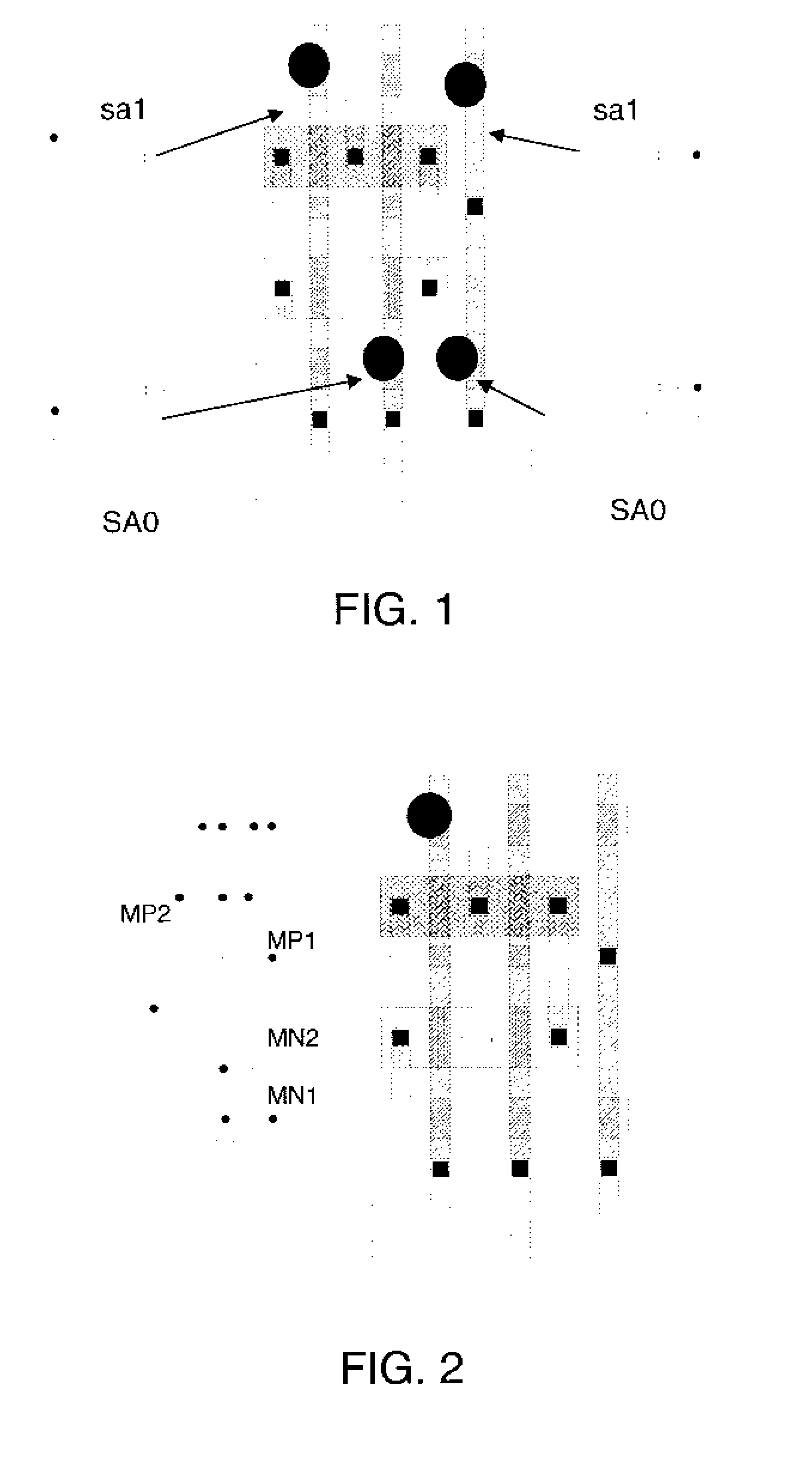

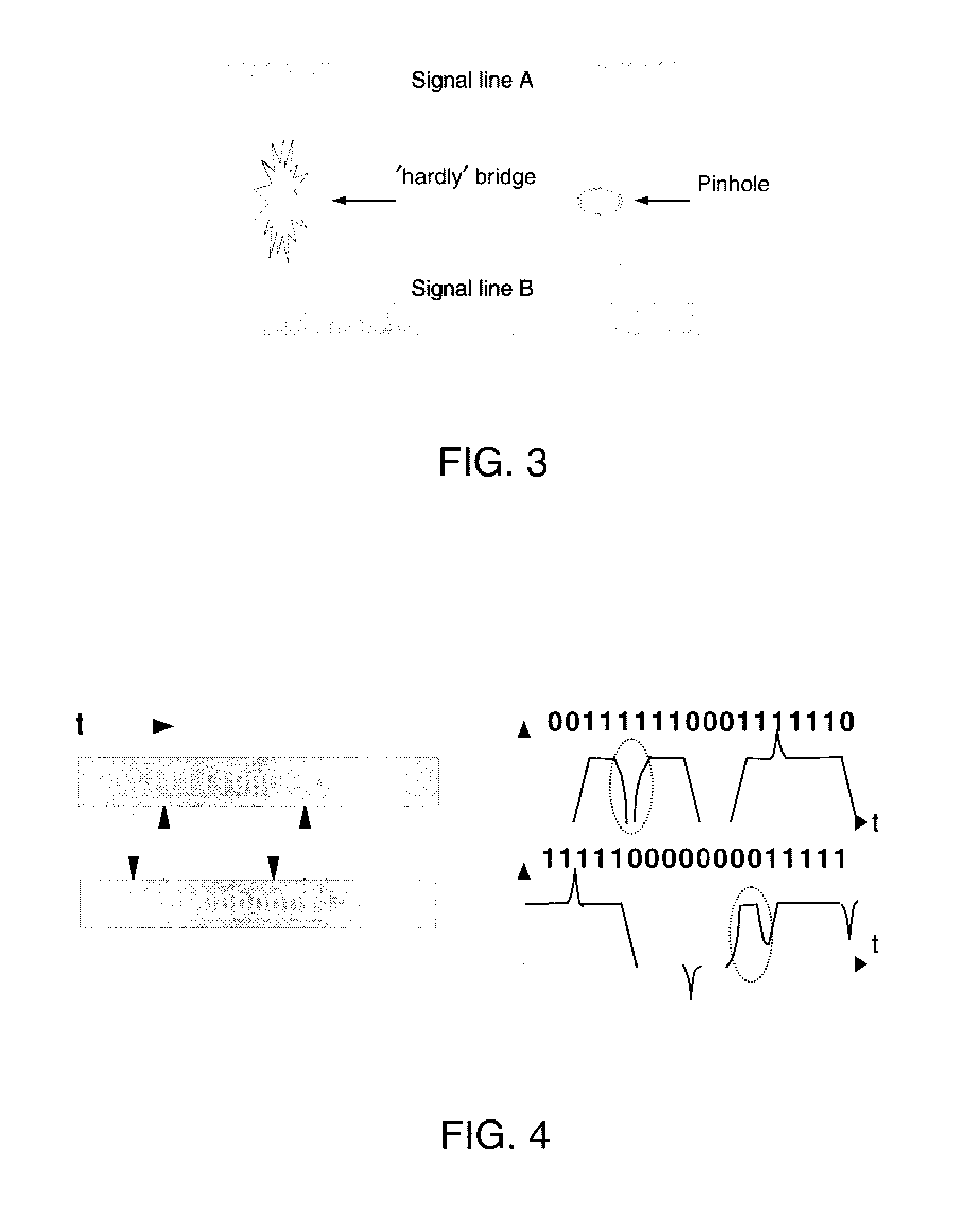

Design verification for asymmetric phase shift mask layouts

InactiveUS6185727B1Photo-taking processesOriginals for photomechanical treatmentComputer Aided DesignPhase shifted

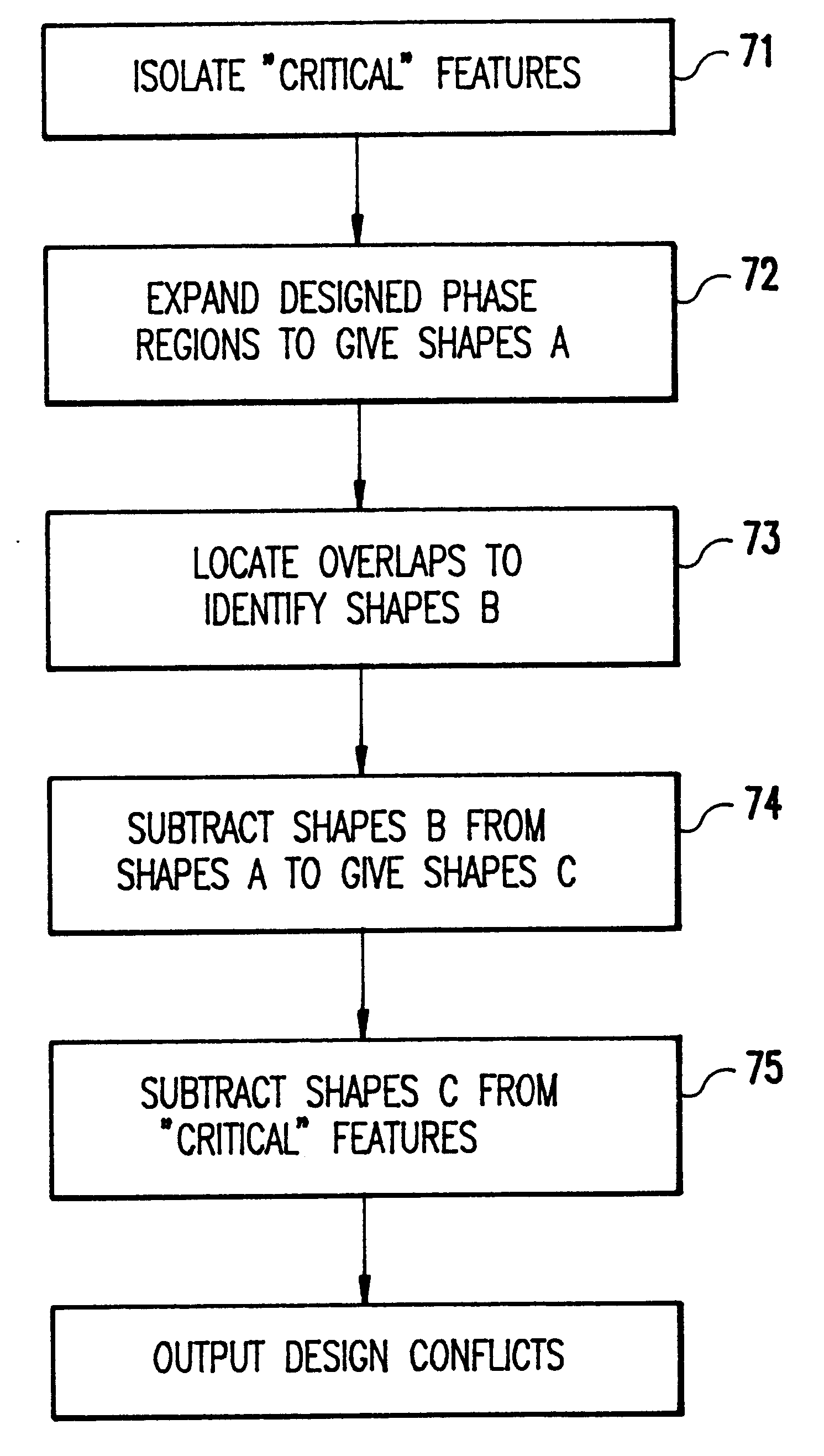

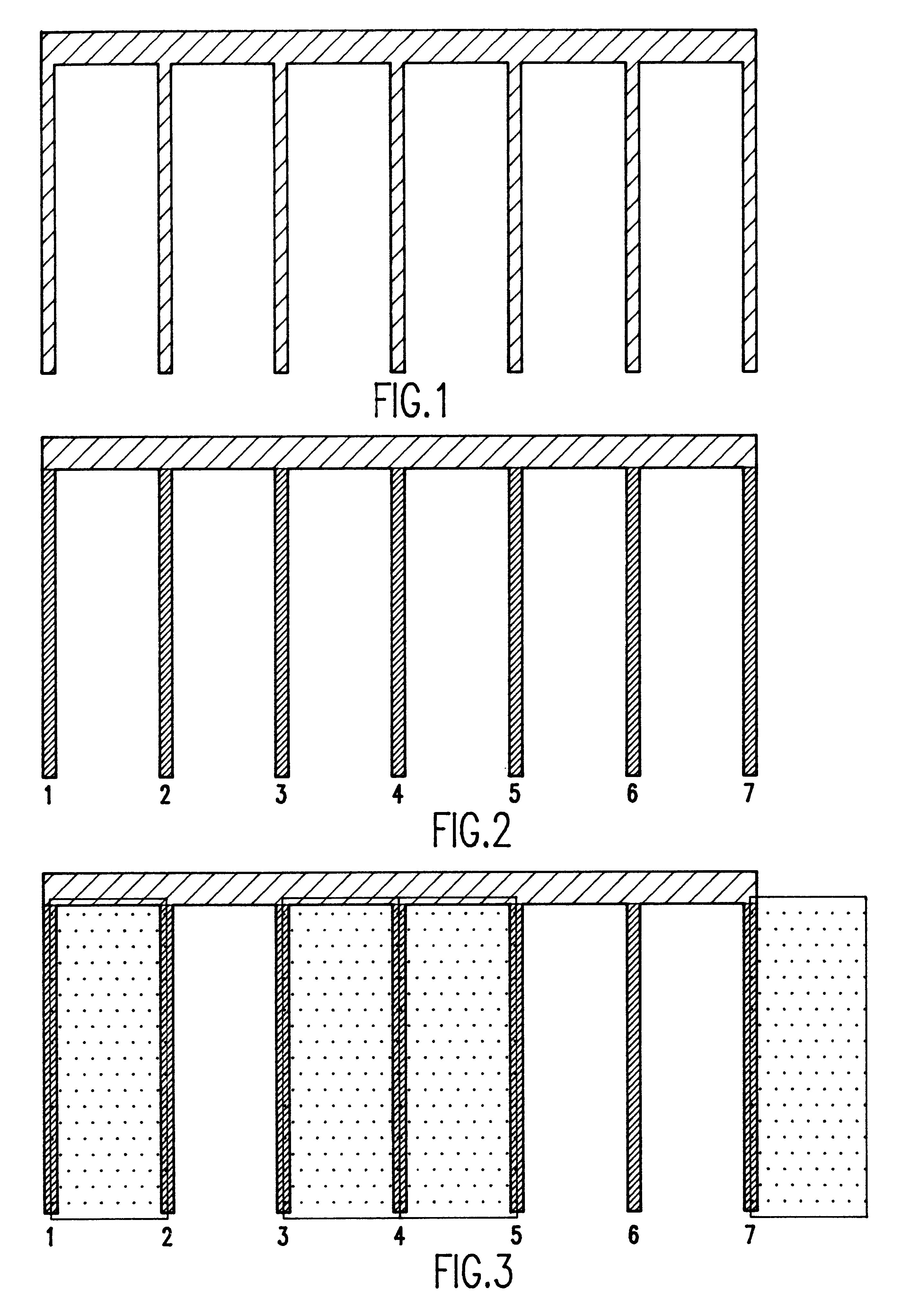

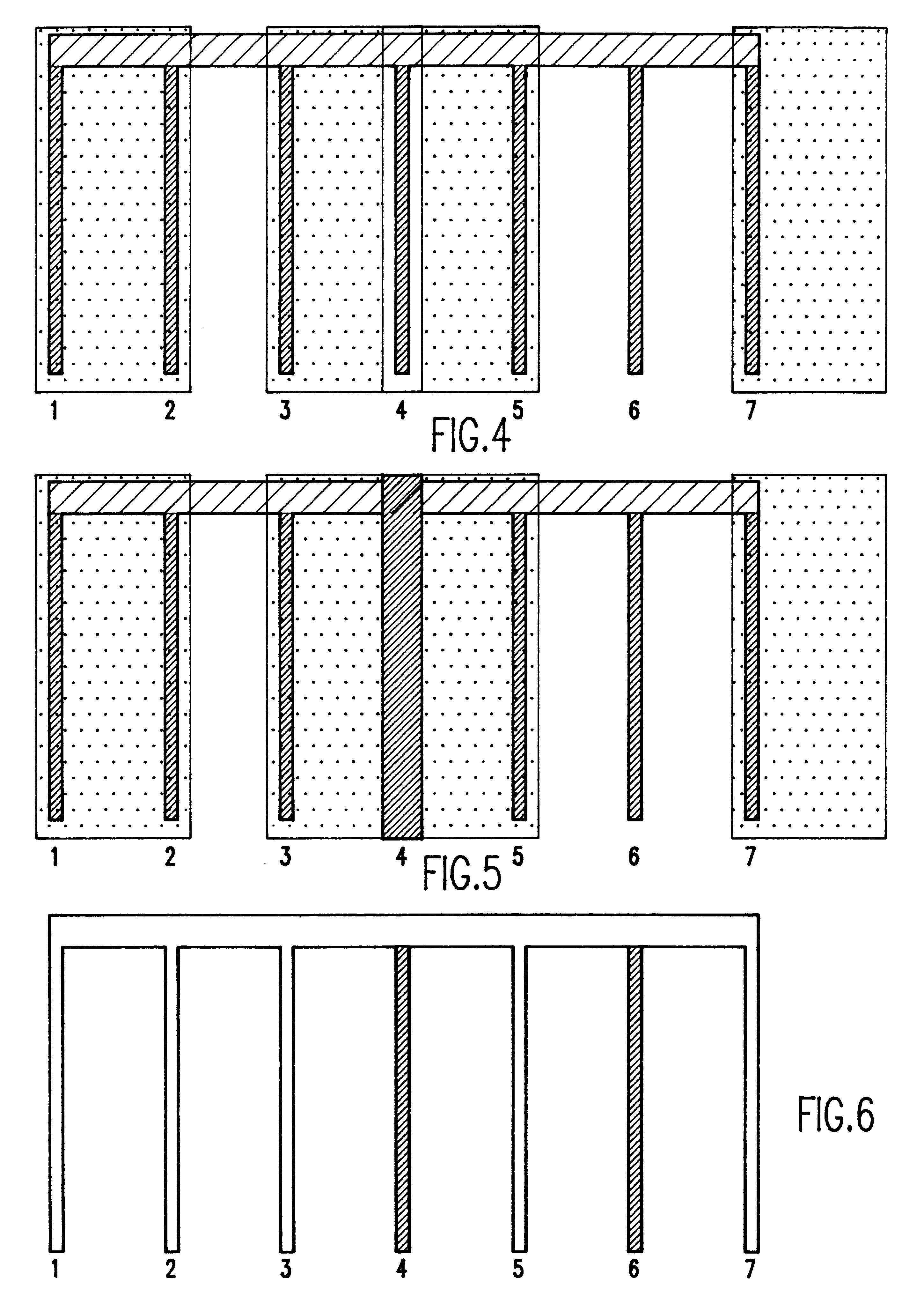

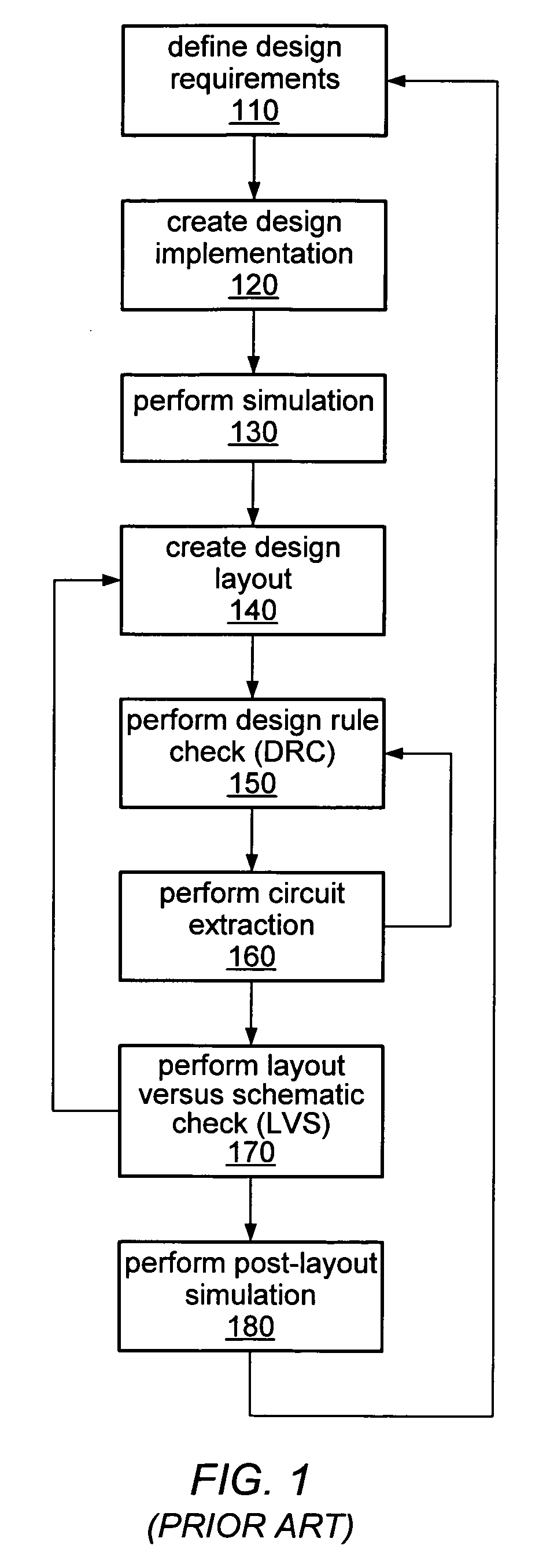

A checking routine verifies a phase shifted mask (PSM) design based on fundamental principles of PSM and utilizing only basic shape manipulation functions and Boolean operations found in most computer aided design (CAD) systems. The design verification system checks complete chip designs for the two possible design errors that can cause defective masks by eliminating the phase transition; namely, placing a 180° phase region on both sides of a critical feature or completely omitting the phase region adjacent to certain critical features.

Owner:IBM CORP

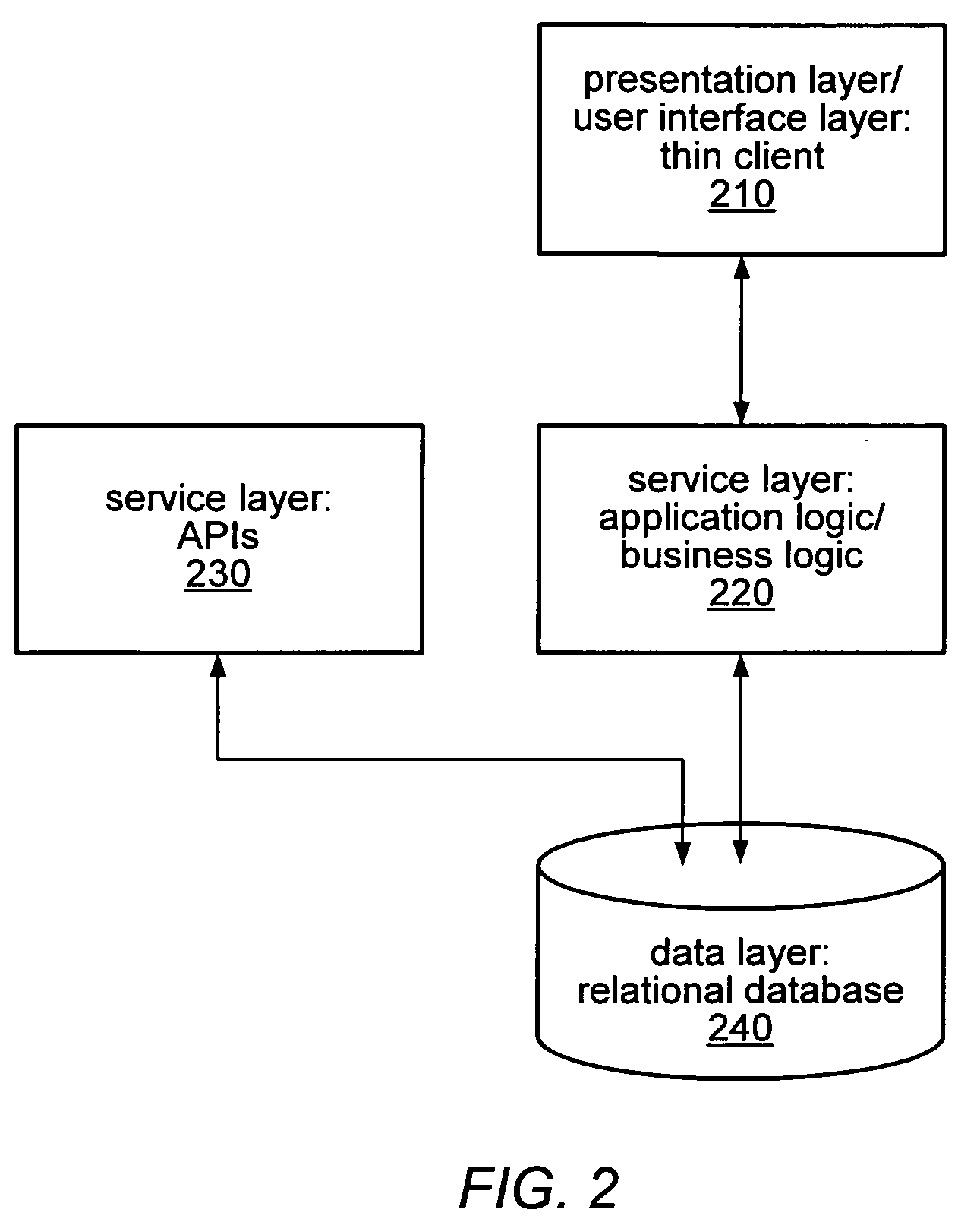

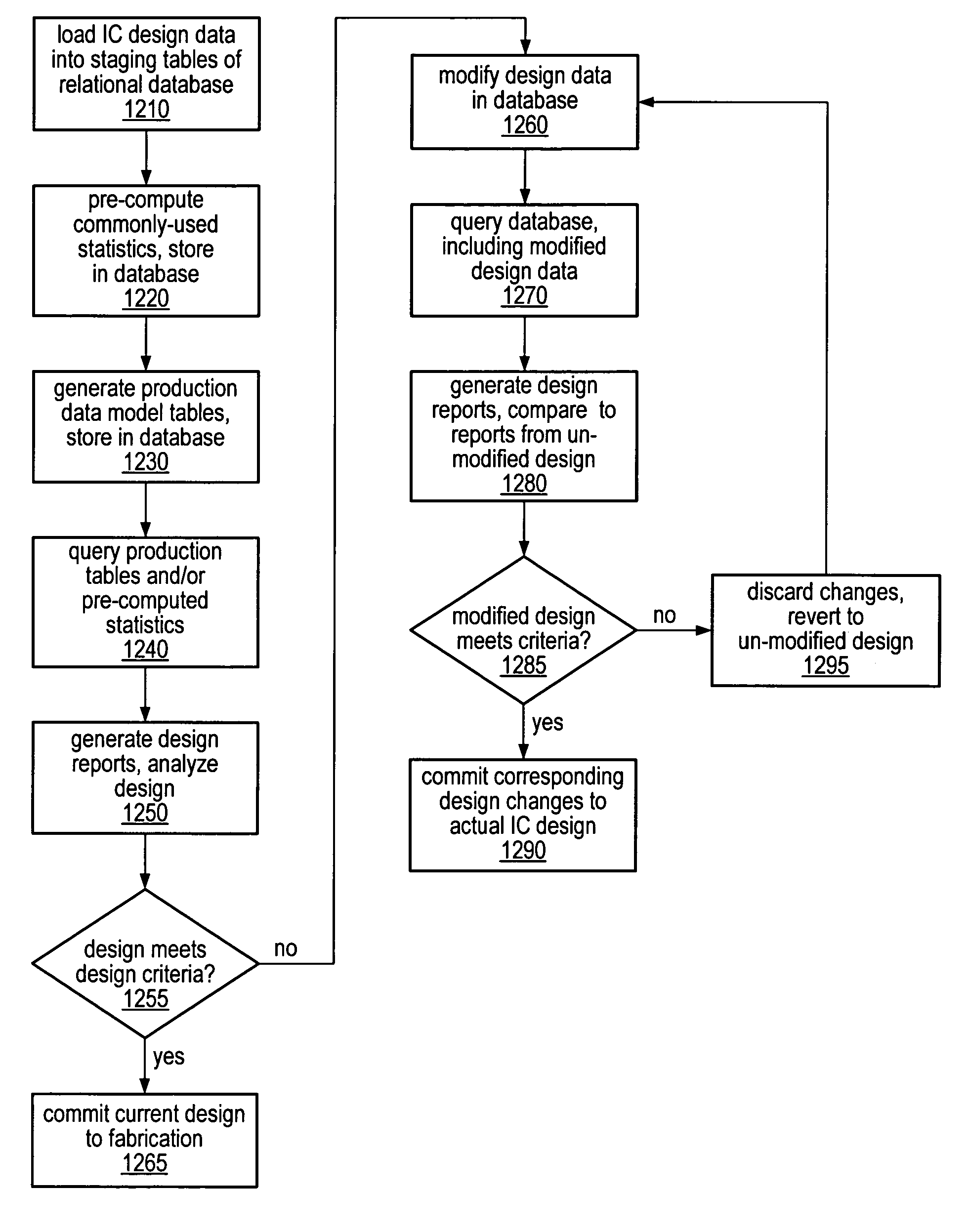

Application of a relational database in integrated circuit design

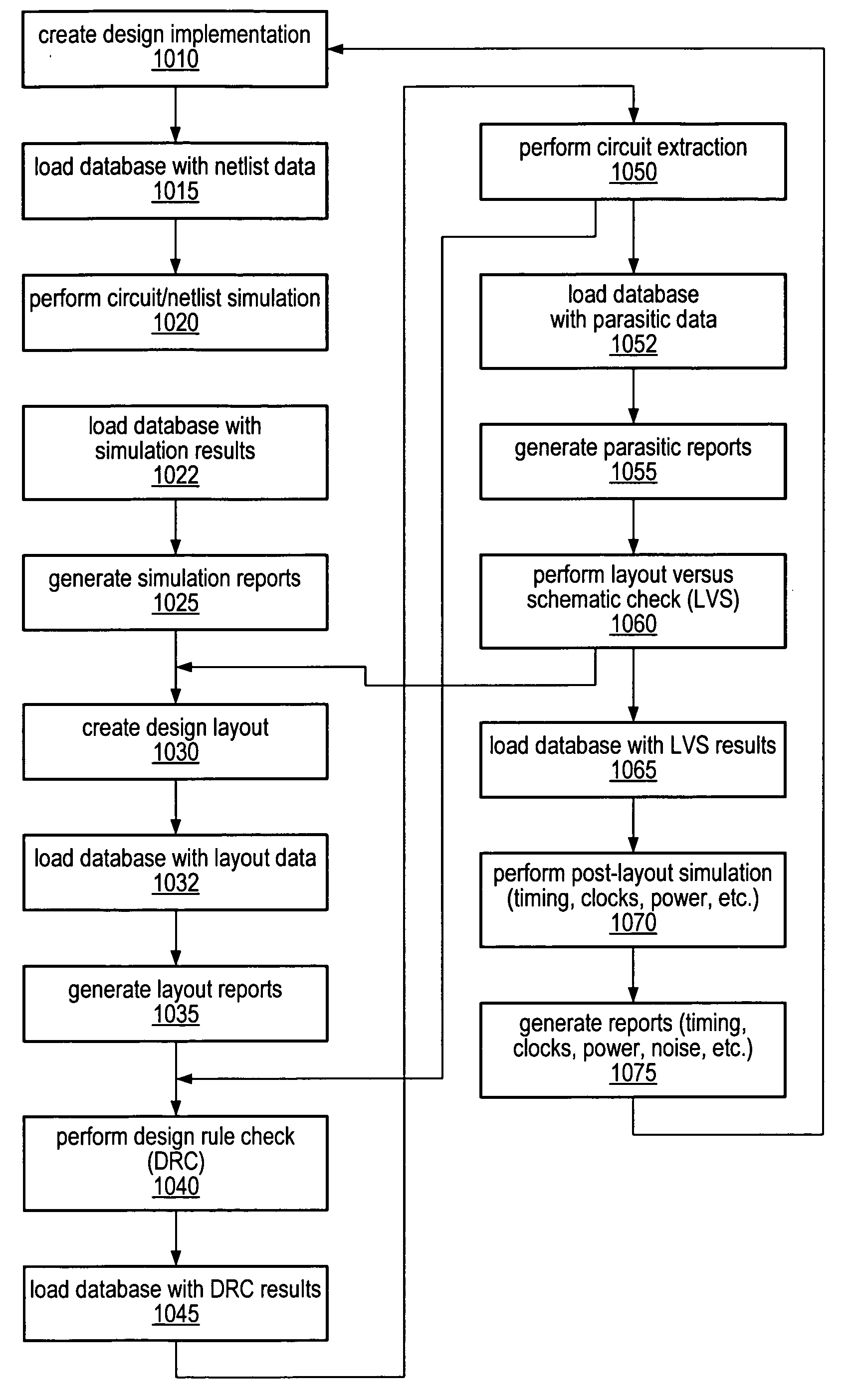

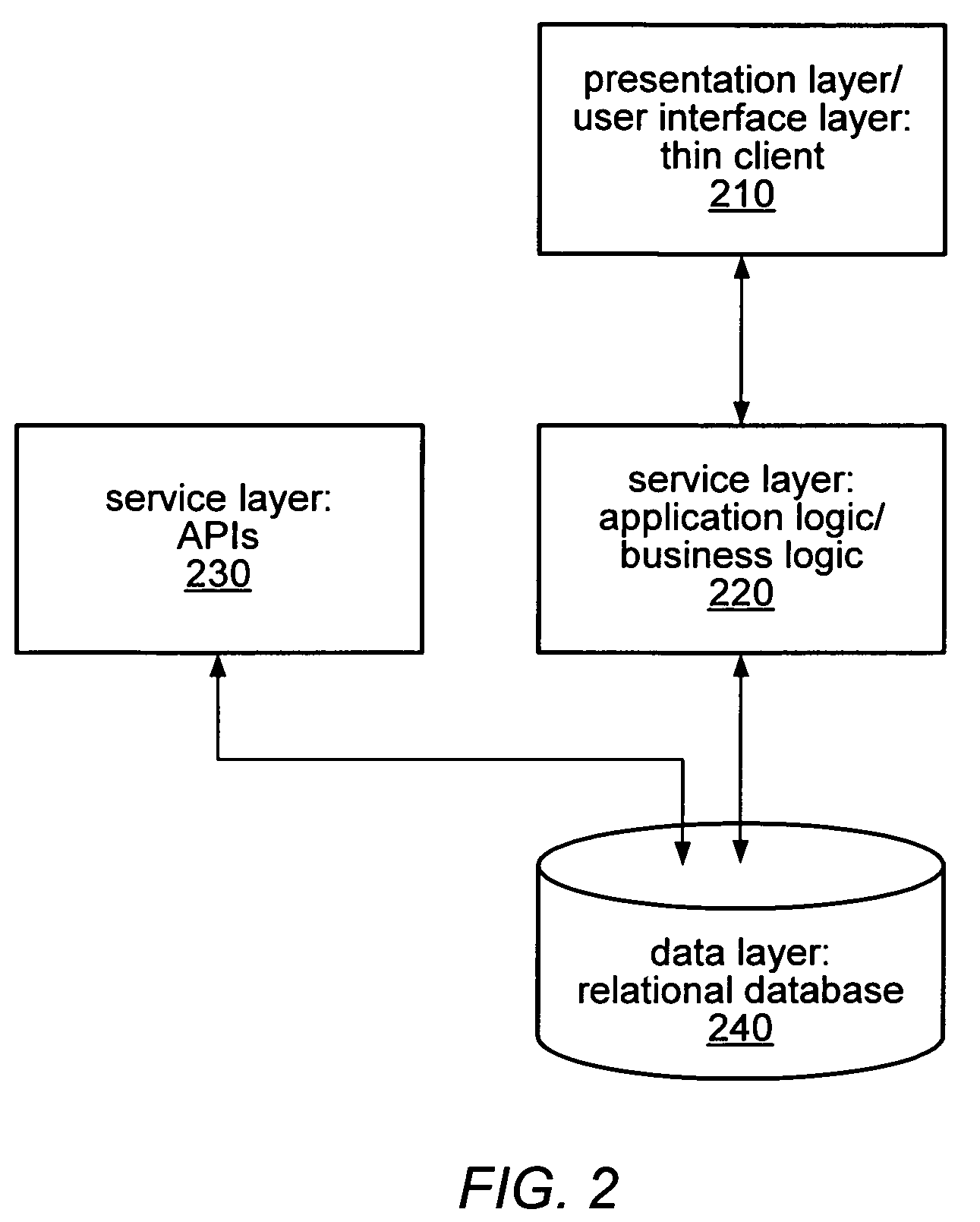

A relational database may be integrated into an integrated circuit design and analysis environment as the persistent data store for data associated with the design. This design data may include two or more abstractions of the design, such as layout data models and timing data models, in some embodiments. Design data may be partitioned in the database and indexed according to various attributes. The use of a relational database may facilitate cross-probing of design data corresponding to different abstractions of the design. The relational database may be queried to produce design reports and to identify design errors or weaknesses. Reports may be graphical or tabular, and may be displayed, printed, stored, or posted for viewing. Proposed modifications to a design may be investigated by modifying data in the relational database, rather than in the actual design. Design reports may be re-generated and compared with corresponding reports for the un-modified design.

Owner:ORACLE INT CORP

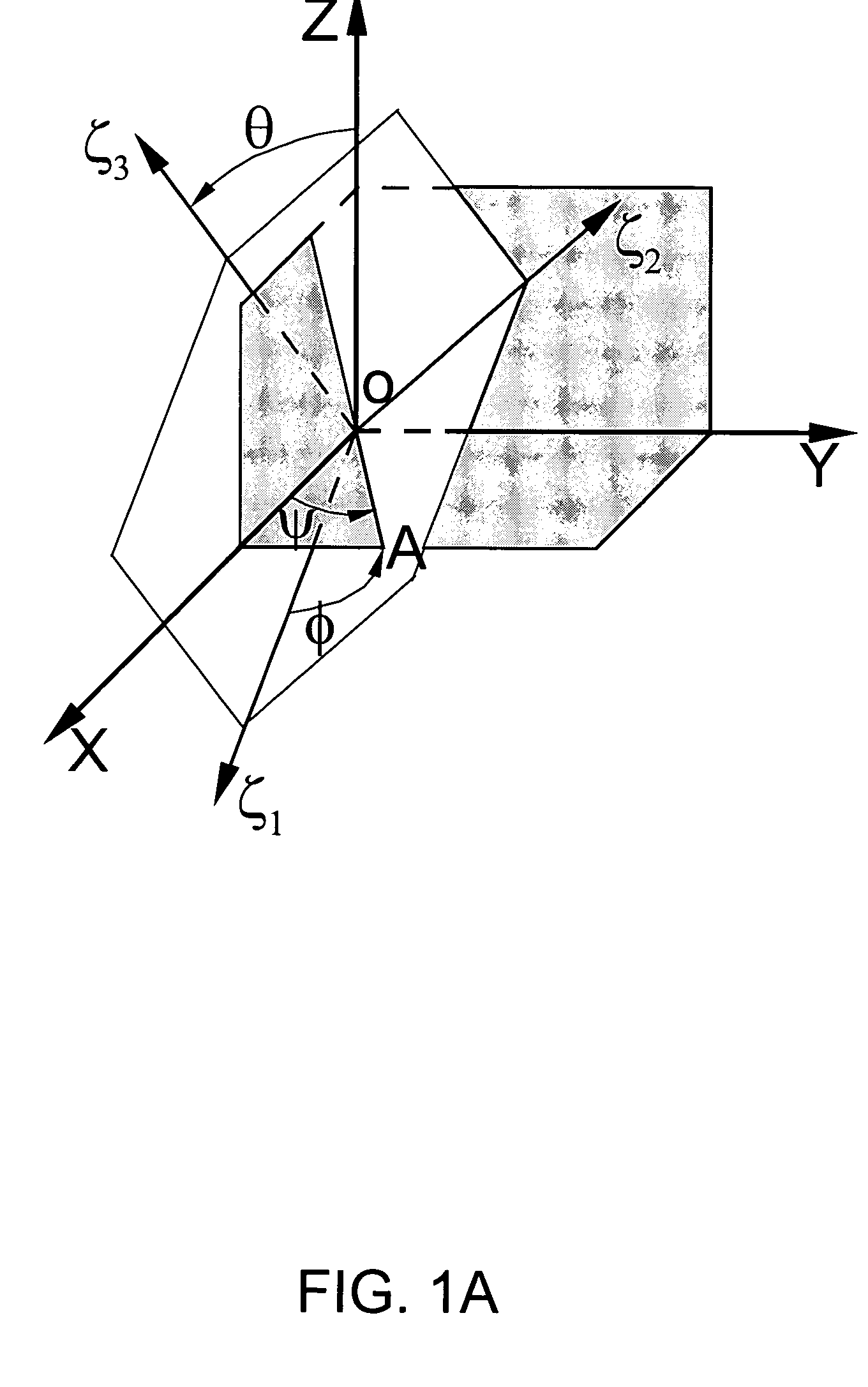

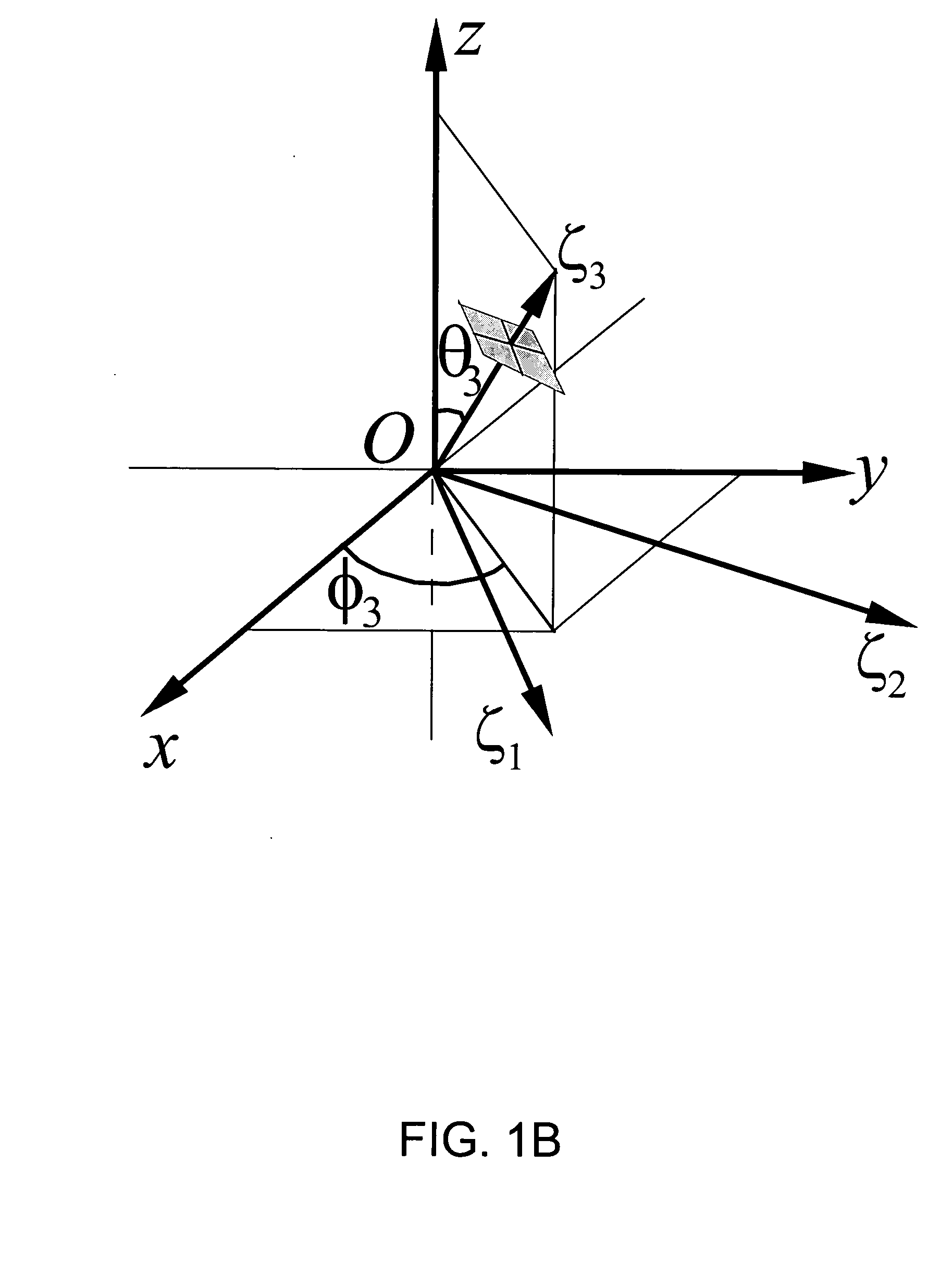

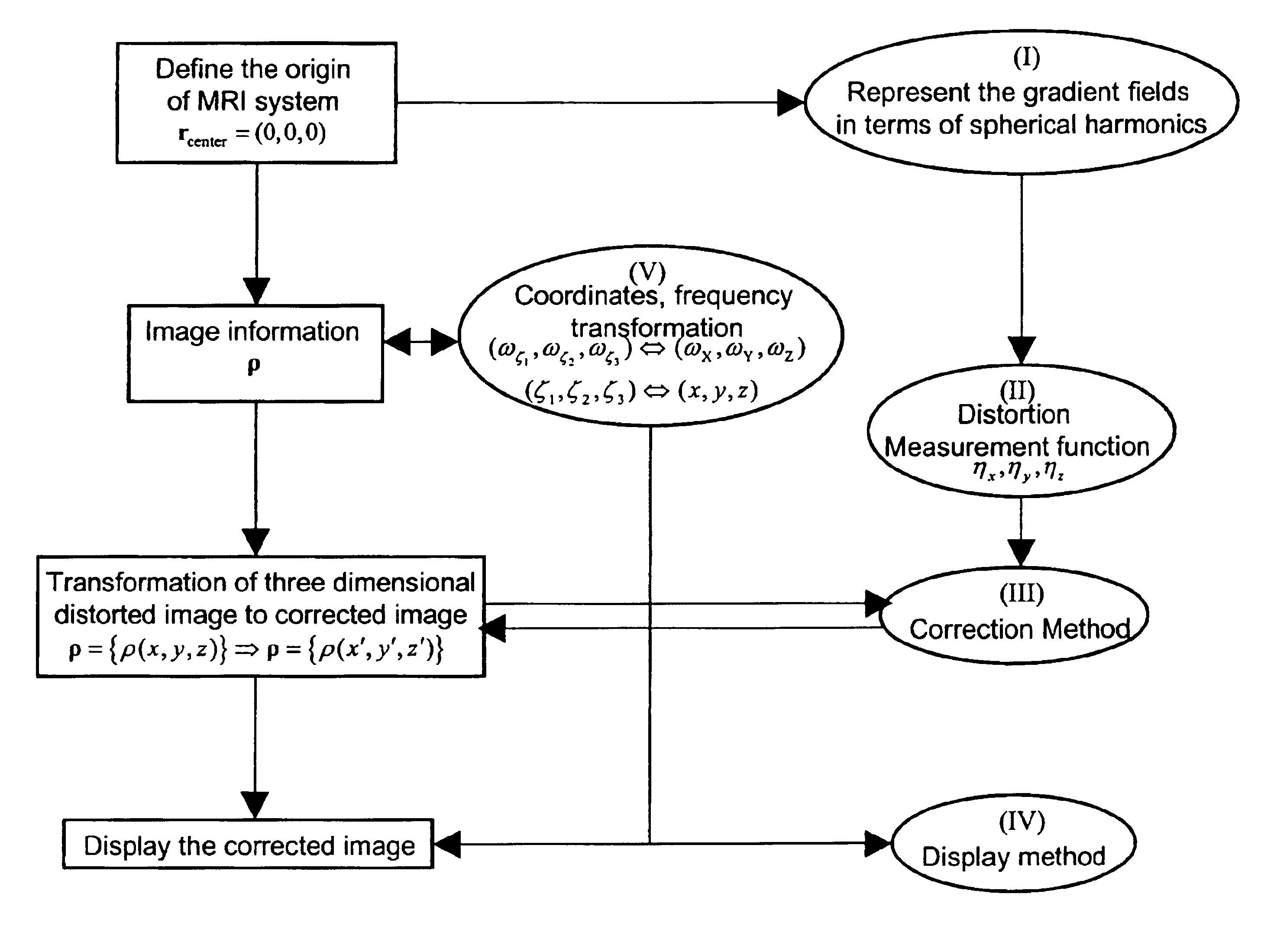

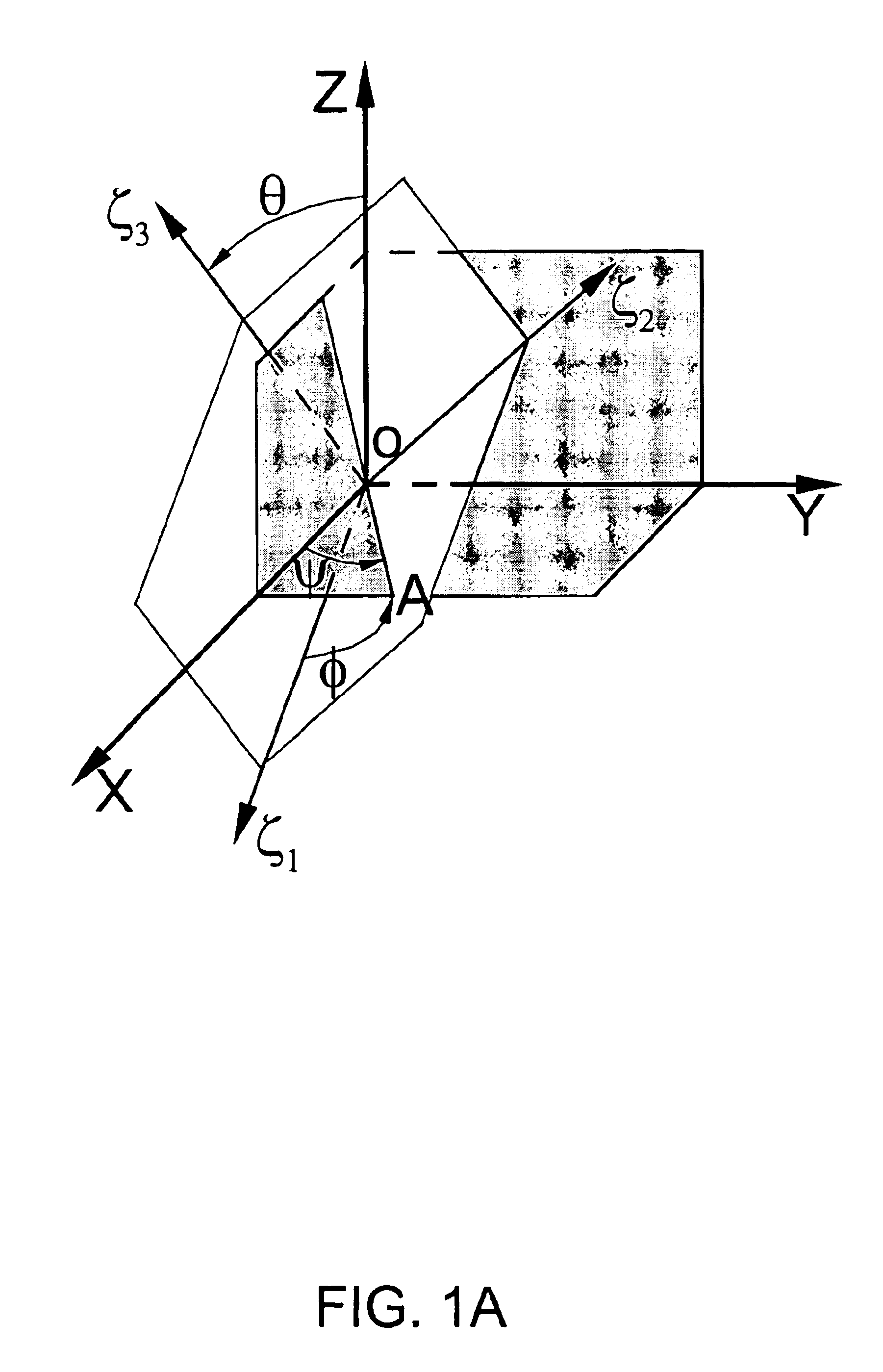

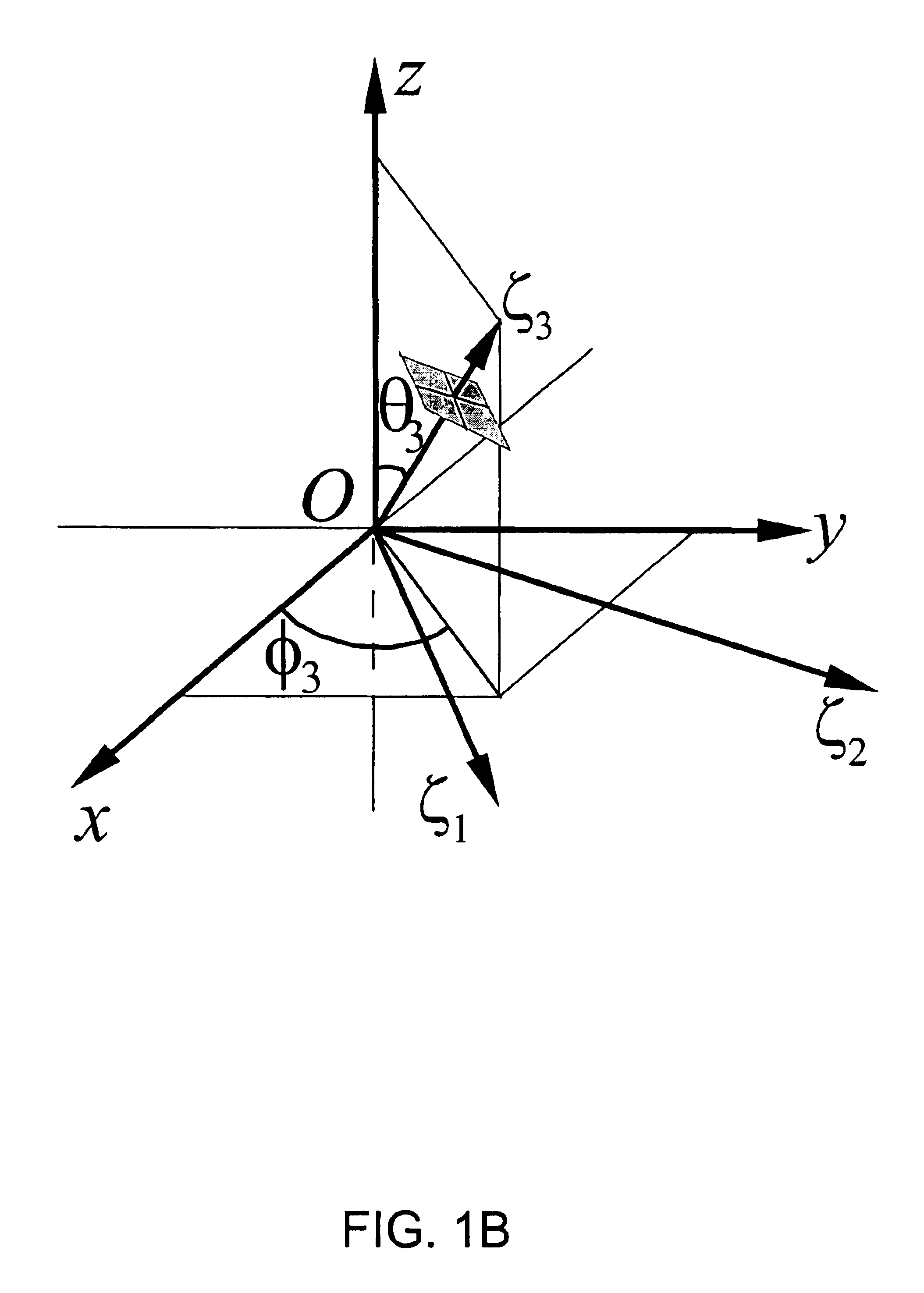

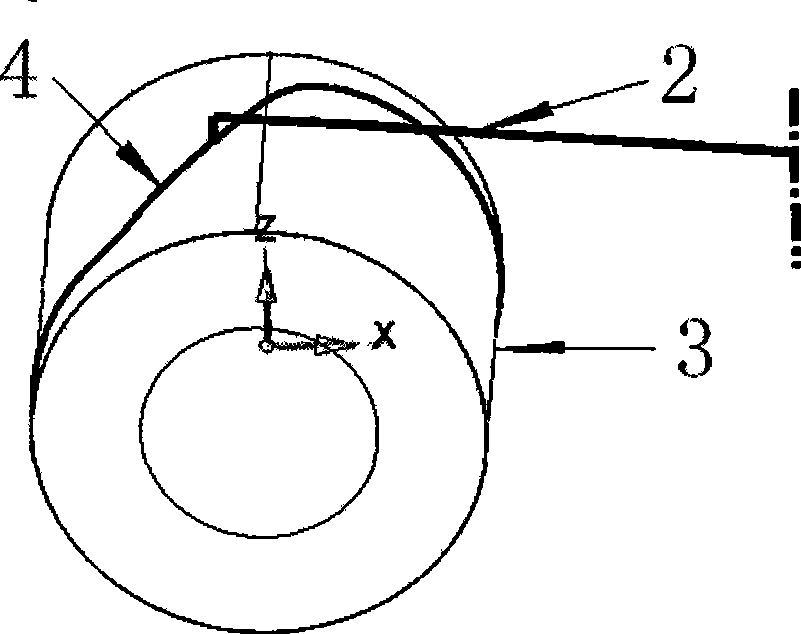

Correction of magnetic resonance images

InactiveUS20050024051A1Avoid artifactsAccurate imagingMagnetic measurementsDiagnostic recording/measuringMagnetic field gradientFourier transform on finite groups

Spatial encoding in magnetic resonance imaging (MRI) techniques is achieved by sampling the signal as a function of time in the presence of magnetic field gradients, e.g., X, Y, and Z gradients. The gradient magnets have in the past been assumed to generate a linear gradient, and typical image reconstruction techniques have relied upon this assumption. However, to achieve high speed performance, gradient magnets often sacrifice linearity for speed. This non-linearity, in turn, results in distorted images, the distortion often being sufficiently large to compromise the usefulness of MRI images for stereotaxy or longitudinal studies, where precise volumetric information is required. The disclosure provides practical methods for correcting distorted images resulting from such non-linearity in the gradient fields, as well as distortions resulting from translational, rotational, and / or winding / design errors in the field generating devices. The methods employ spherical harmonic expansions of the gradient fields and fast Fourier transform techniques to provide well-corrected images without undue computational burdens.

Owner:THE UNIV OF QUEENSLAND

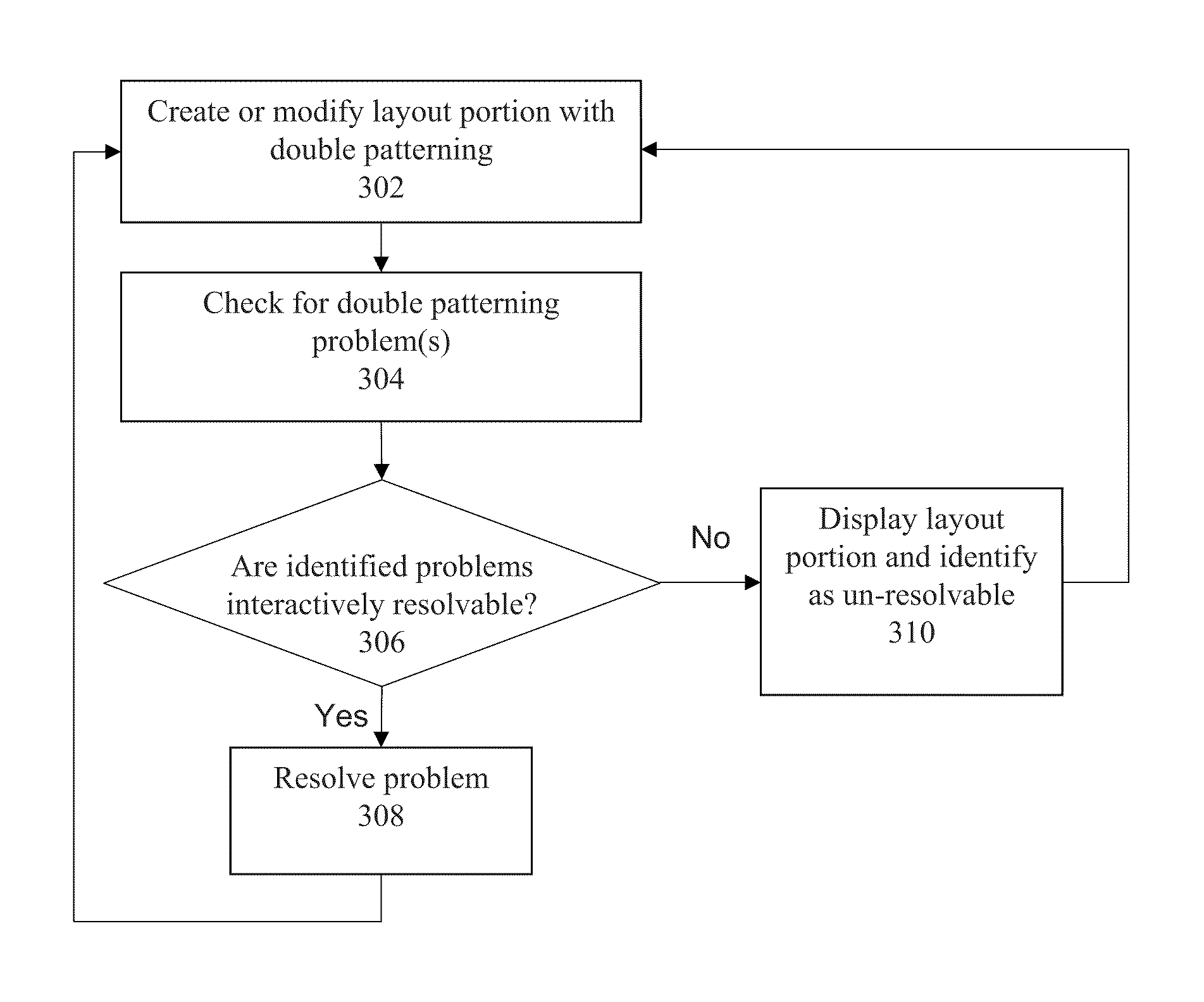

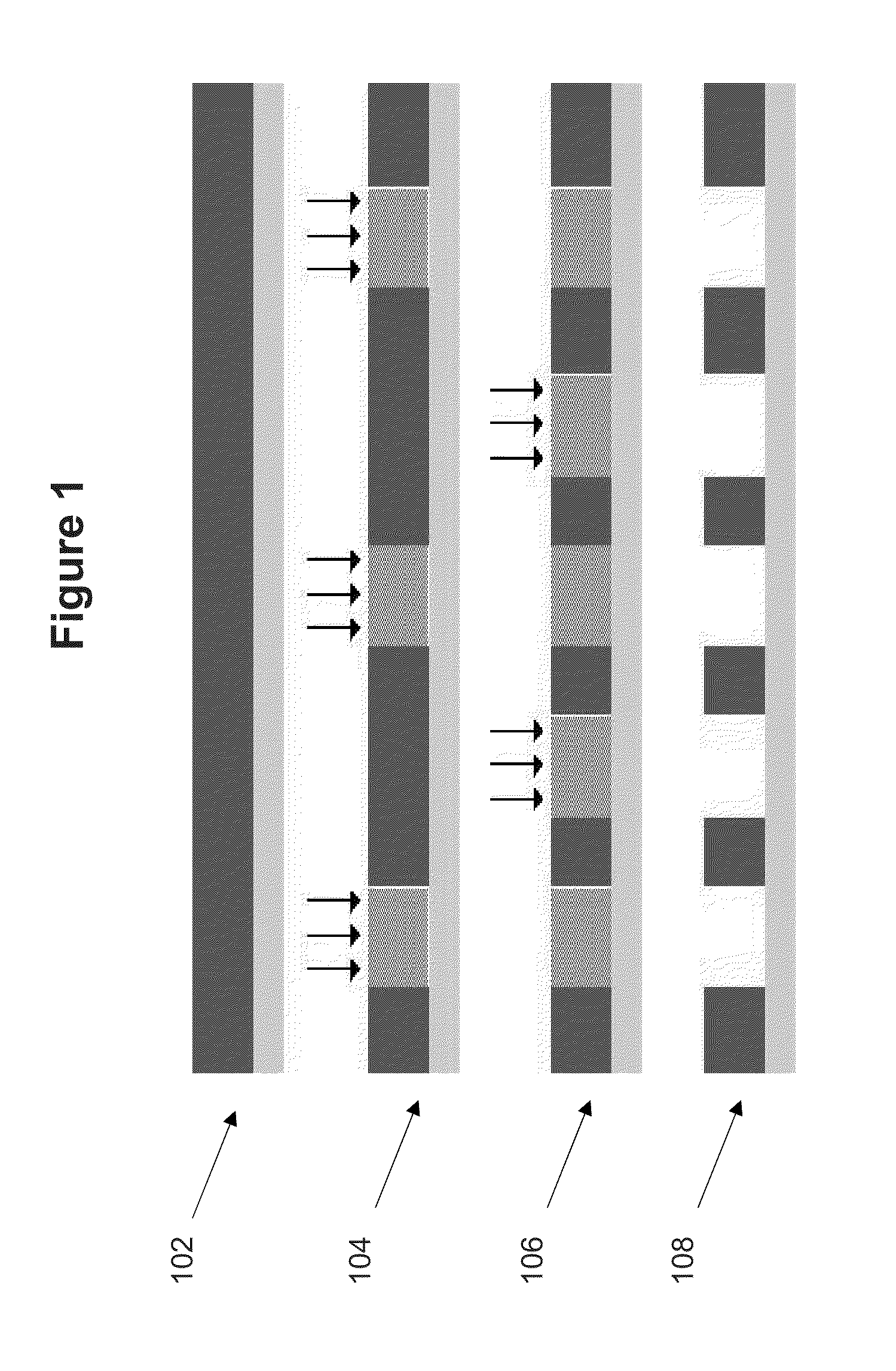

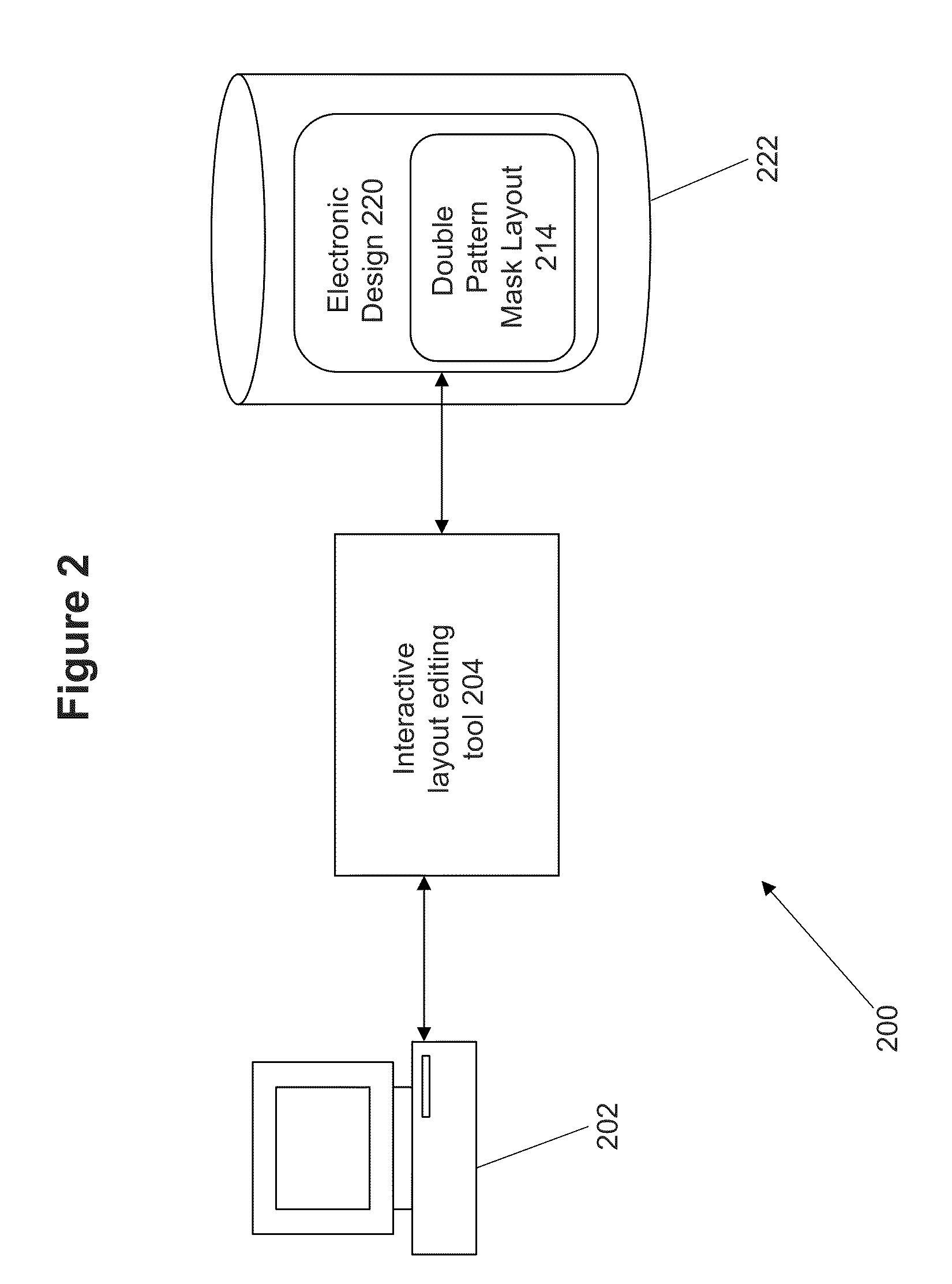

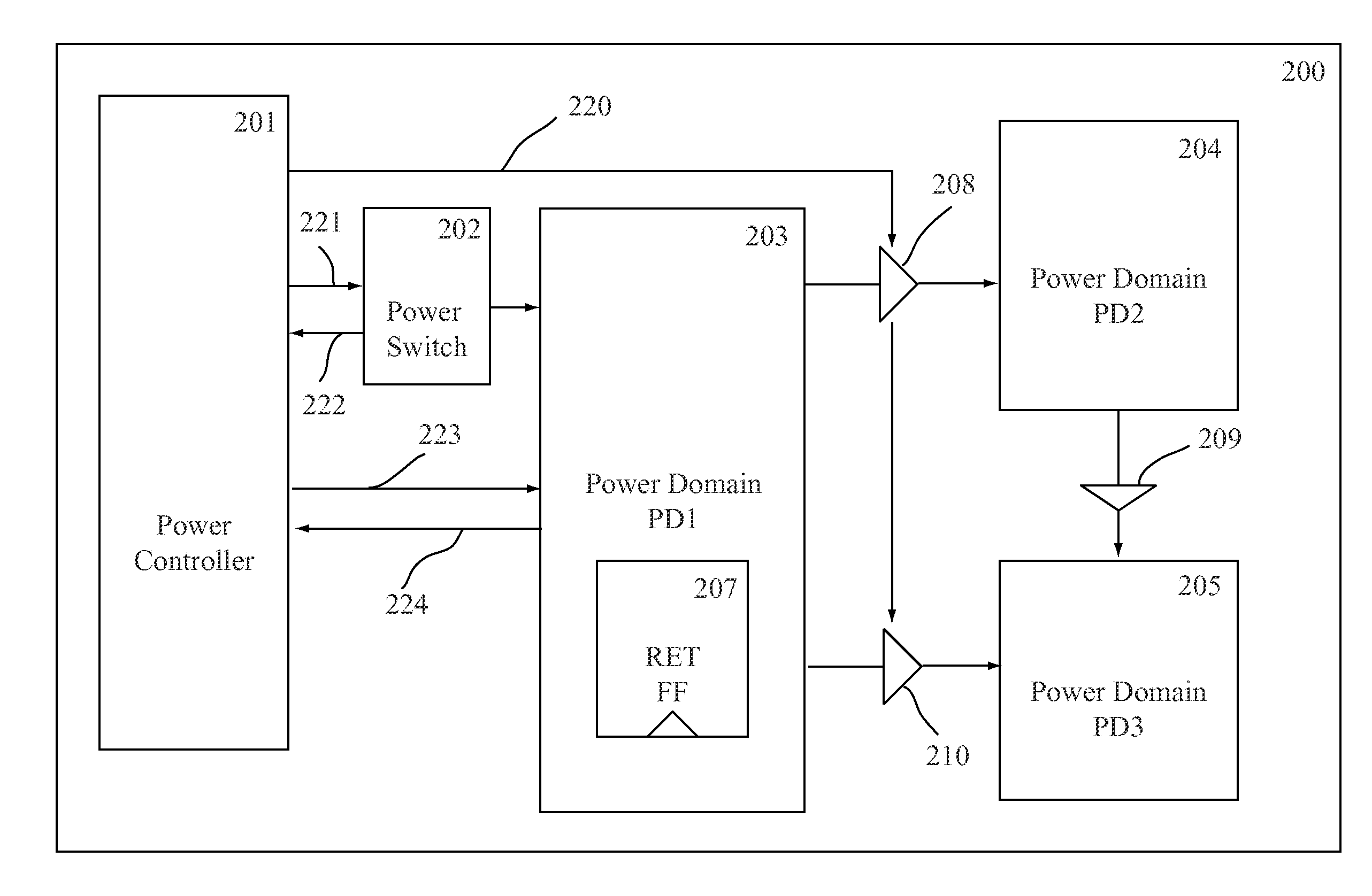

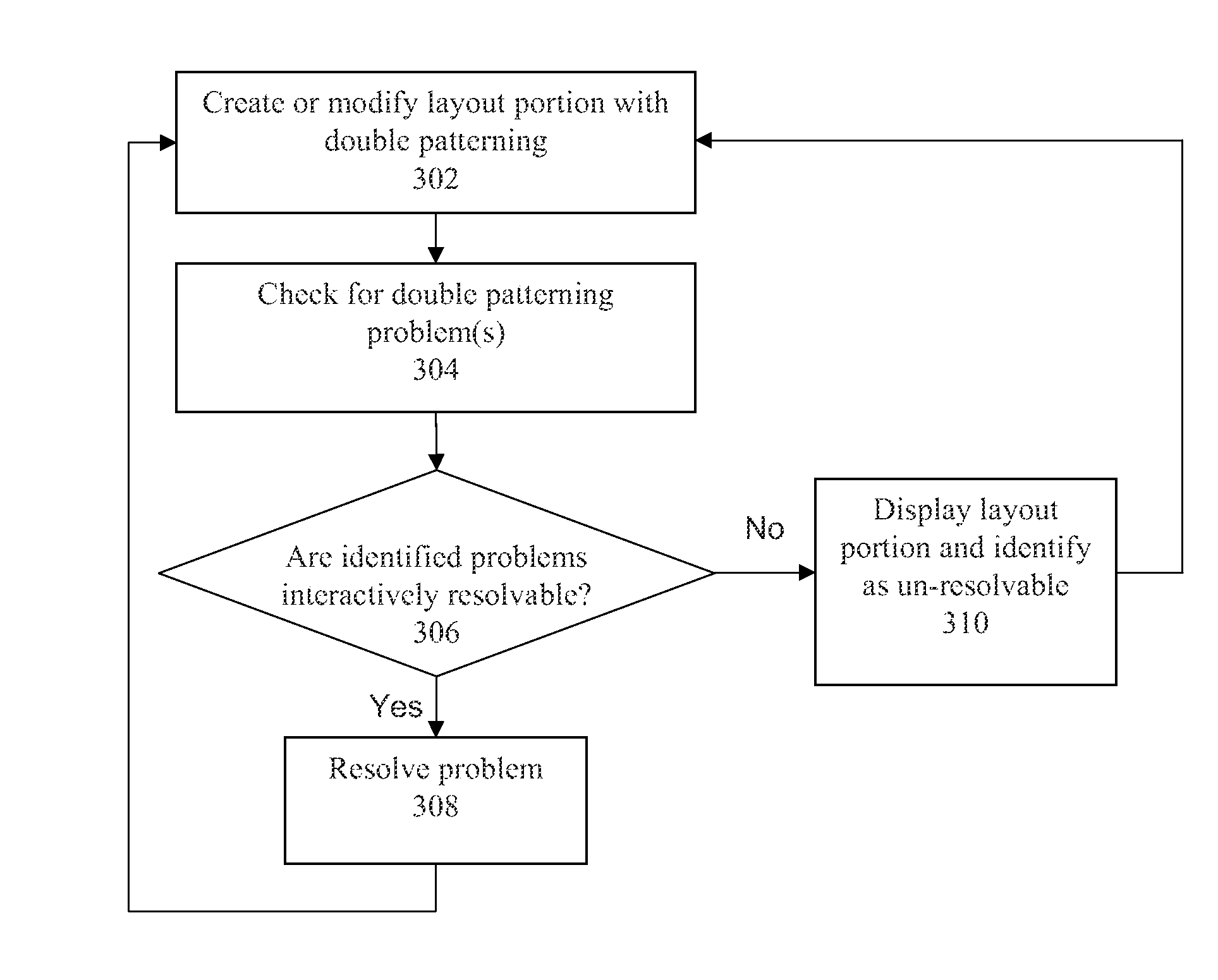

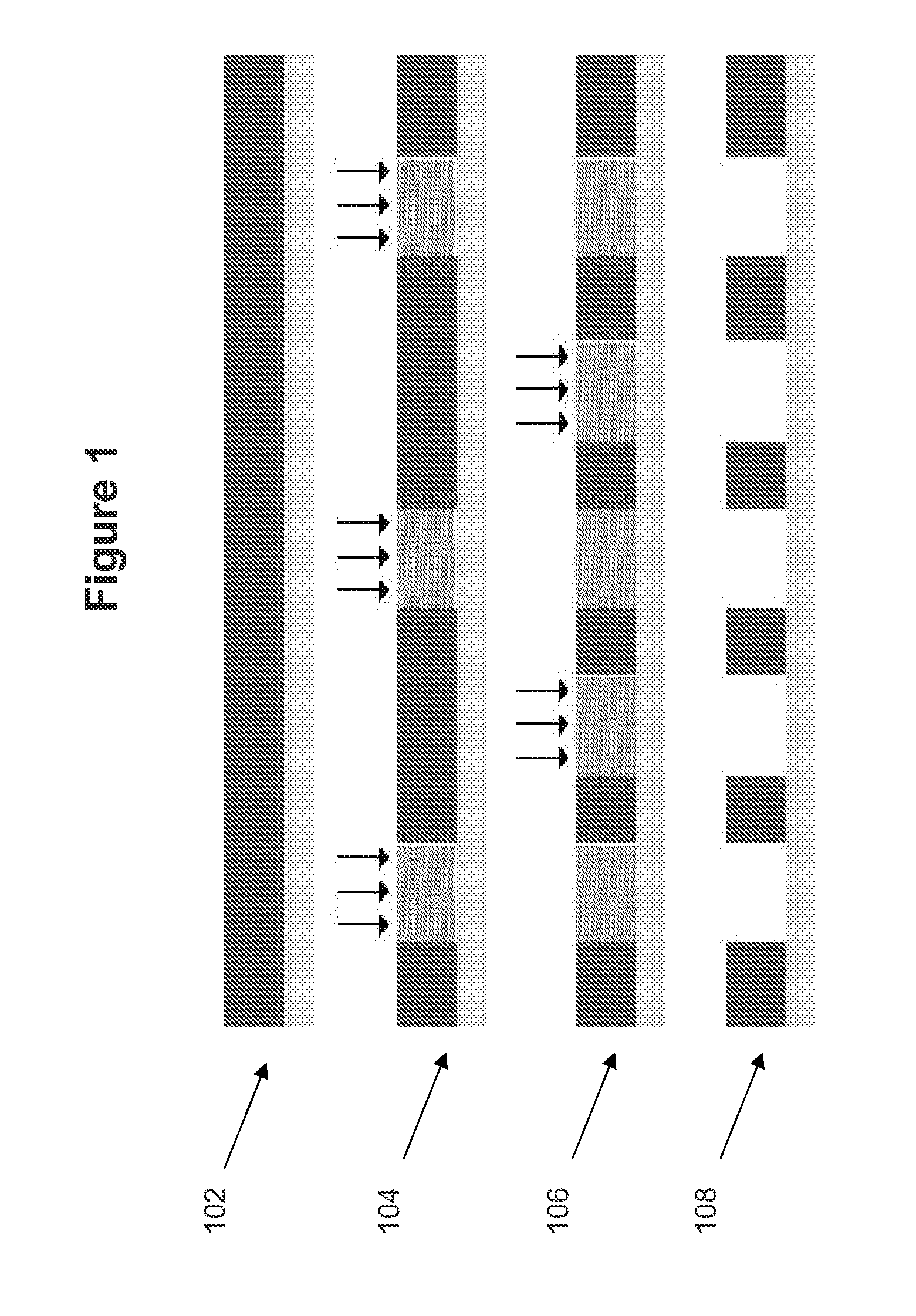

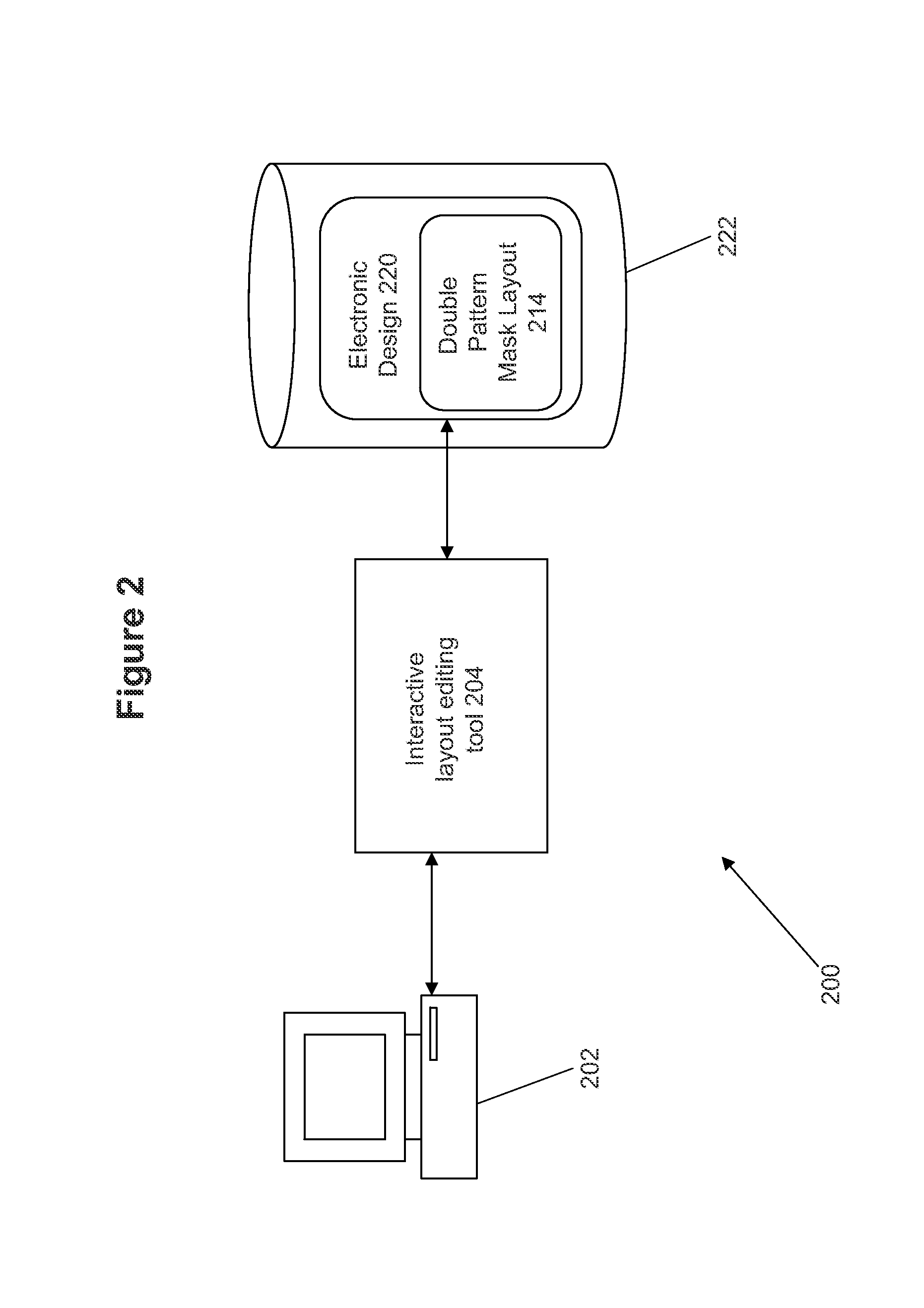

Method, system, and program product for interactive checking for double pattern lithography violations

ActiveUS20110219341A1CAD circuit designOriginals for photomechanical treatmentLithographic artistElectronic design

Disclosed are a method, apparatus, and computer program product for performing interactive layout editing to address double patterning approaches to implement lithography of electronic designs. A spatial query is performed around the shape(s) being created during editing with the distance of allowed spacing in a single mask. If a design error is encountered, corrective editing may occur to correct the error. Checking may occur to make sure that the error detection and corrective actions can be performed interactively.

Owner:CADENCE DESIGN SYST INC

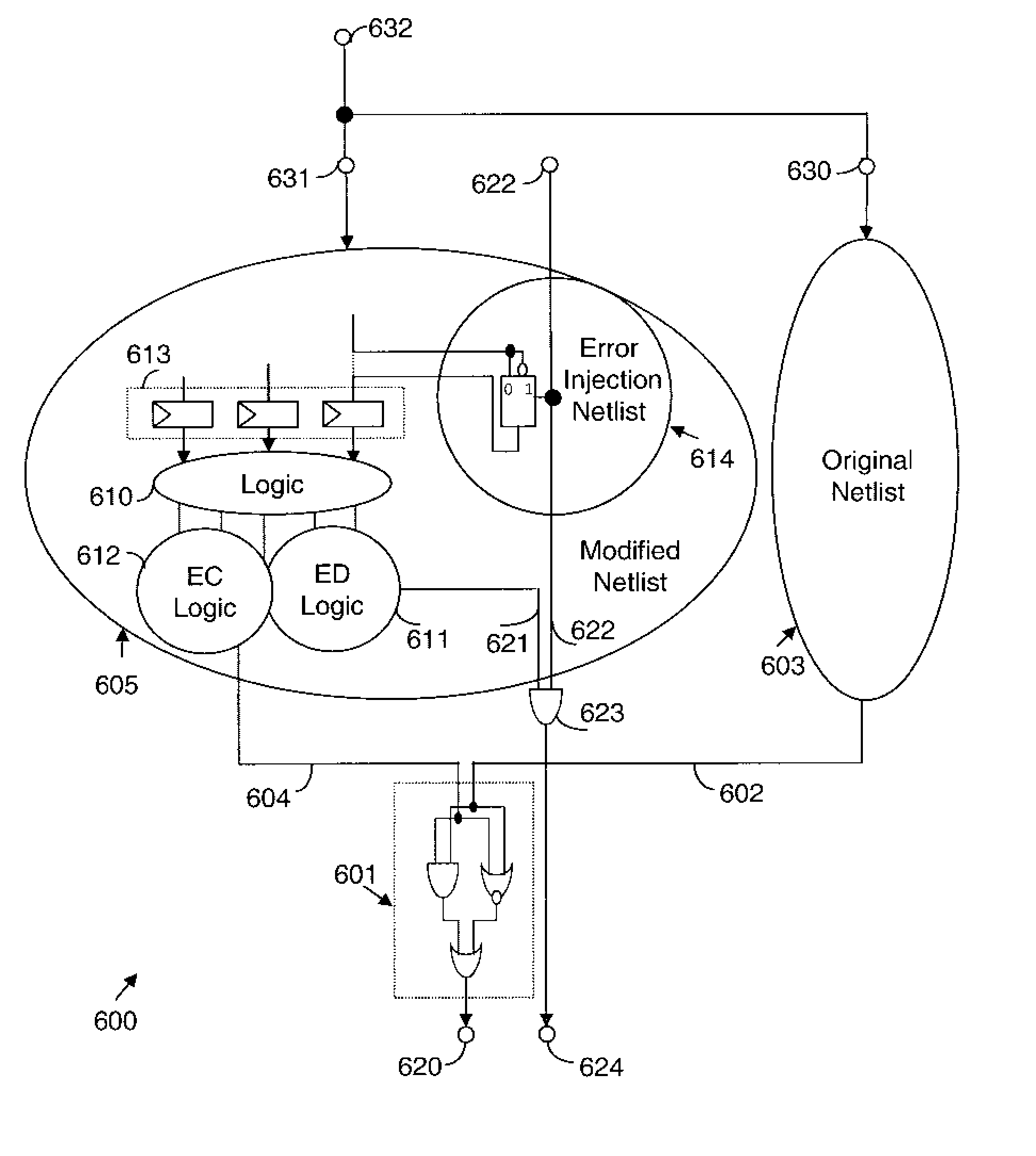

Method and System for Performing Functional Formal Verification of Logic Circuits

InactiveUS20070050740A1Detecting errorComputer aided designSoftware simulation/interpretation/emulationFault modelNetlist

The present invention relates to a method, a computer program product and a system for performing functional formal verification. Error detection logic is verified by injecting errors in a hardware design description without any changes to the original design description. With the present invention both permanent and transient faults can be modelled, and the complete error space can be covered for all types of fault models that can be used at the RTL. The number of detected design errors is used to determine the overall coverage in relation to the number of injected errors. The error injection is prepared by adding additional circuits to an RTL netlist representation of the hardware logic design. Signal values for selected signals related to the error detection logic are compared for a modified netlist representation and for the original netlist using a formal verification tool.

Owner:IBM CORP

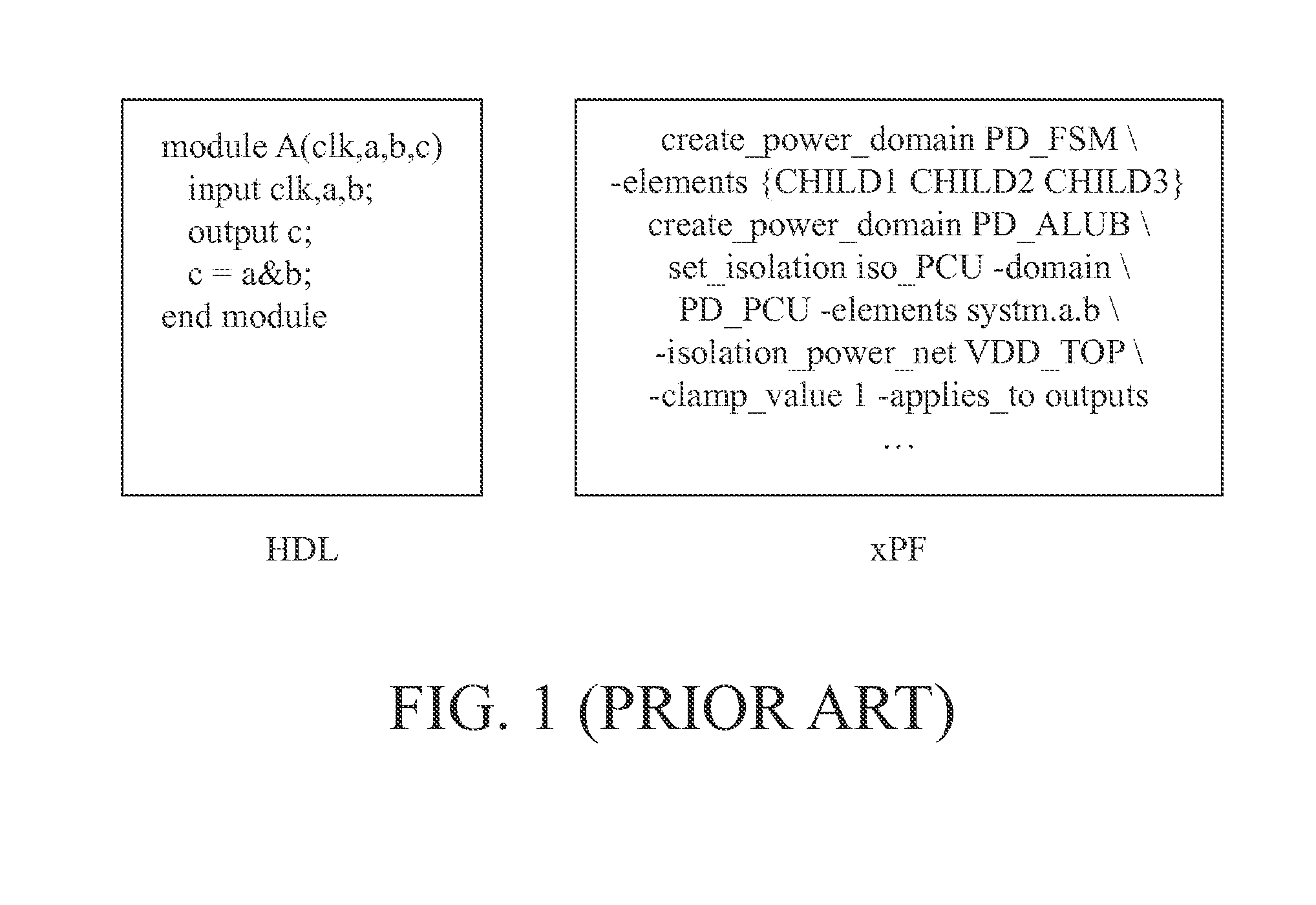

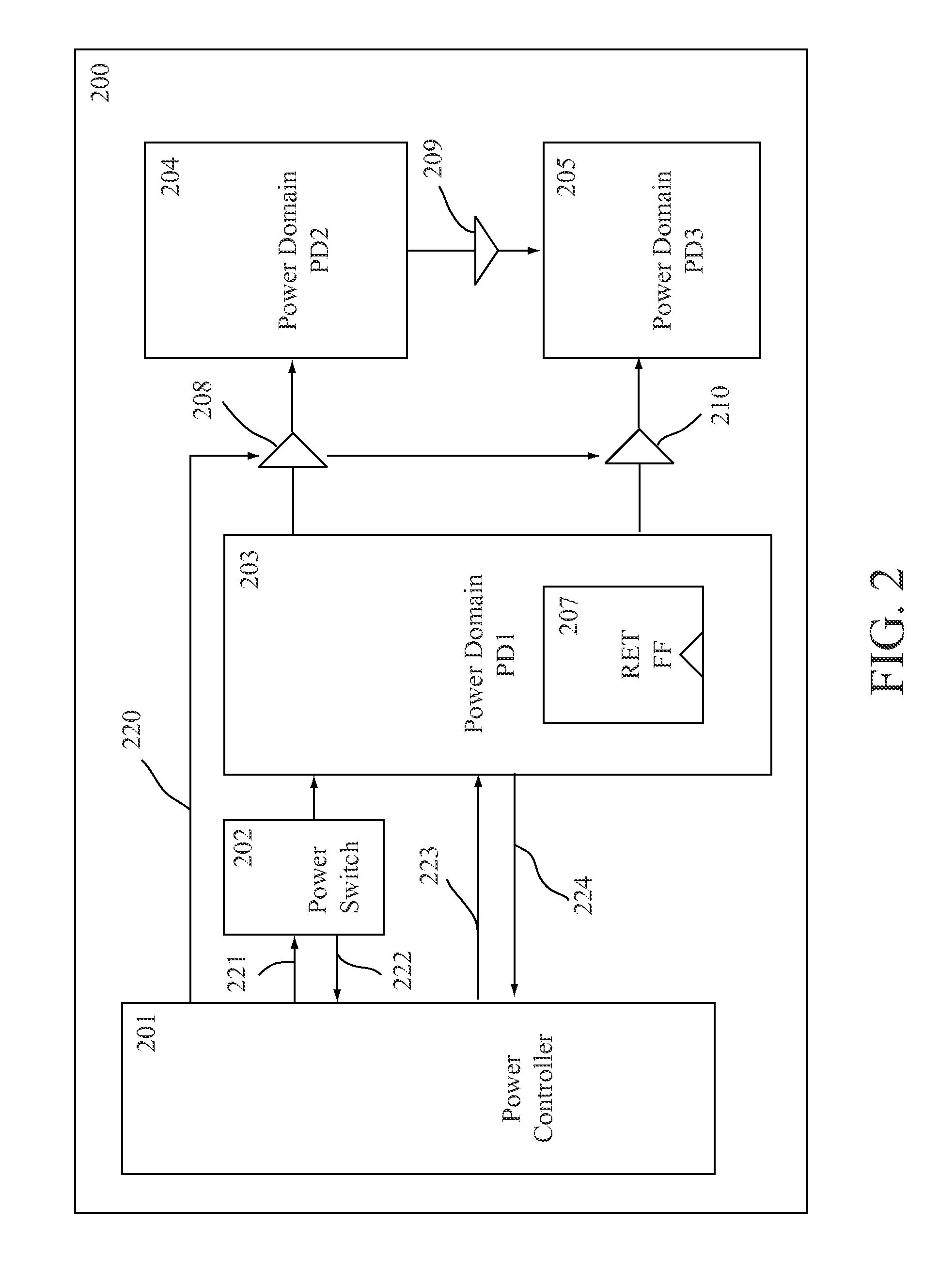

Method for detecting and debugging design errors in low power IC design

ActiveUS20130305207A1Detecting faulty computer hardwareDesign optimisation/simulationAnalog circuit designCircuit design

A method for detecting anomalies in signal behaviors in a simulation of a low power IC includes receiving a circuit design and a power specification of the IC, determining at least one power sequence checking rule from the power specification, simulating the circuit design and the power specification to obtain a dump file, identifying at least one anomaly of the at least one power sequence checking rule based on the dump file, and generating information relevant to the identified anomaly of the at least one power sequence checking rule. The method further includes setting up a context in a debugger for debugging the anomaly by displaying a waveform of misbehaved signals associated with the anomaly in a waveform window, and a portion of the circuit design and / or a portion of the power specification associated with the anomaly in a text window.

Owner:SYNOPSYS INC

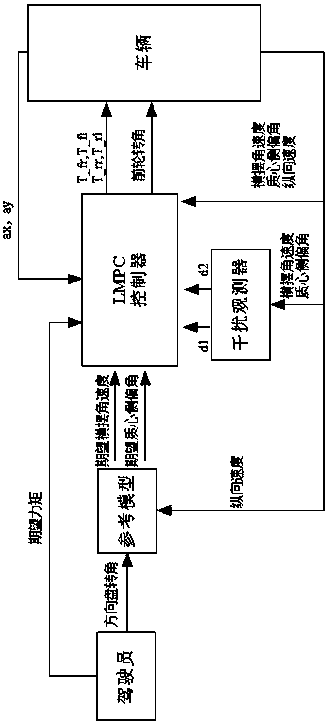

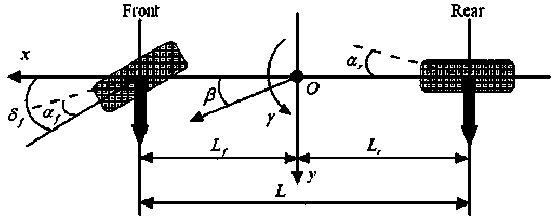

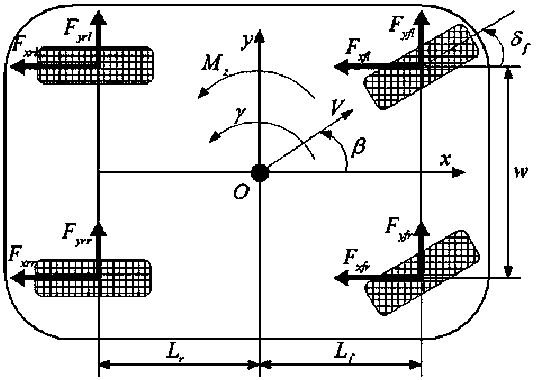

Vehicle yaw stability predicting model control method

ActiveCN108482363AMeet the needs of time controlLighten the computational burdenReference modelNonlinear model

The invention relates to a vehicle yaw stability predicting model control method and belongs to the technical field of a vehicle control. The disturbance-observer-based vehicle yaw stability predicting model control method uses a model predicting control method to design a linear model predicting controller, considers constraint conditions and can reduce computation time, track an expected value as much as possible and keep vehicle stability. The method includes: designing a reference model; performing linearization on a vehicle two-freedom-degree nonlinear model to obtain a linear model withmodel error disturbance terms; designing error terms in a disturbance observer pair model according to the linear model; using a model predicting control algorithm to build a target function, and solving an optimal problem corresponding to a cost function to obtain control input acting to a system to allow the vehicle system to track the expected value as much as possible so as to guaranteed vehicle stability. By the method, model complexity can be lowered effectively, control precision requirements are satisfied, and the constraint of driving torque is considered.

Owner:JILIN UNIV

Correction of magnetic resonance images

InactiveUS7088099B2Reduce computing timeExtension of timeMagnetic measurementsDiagnostic recording/measuringMagnetic field gradientSpatial encoding

Spatial encoding in magnetic resonance imaging (MRI) techniques is achieved by sampling the signal as a function of time in the presence of magnetic field gradients, e.g., X, Y, and Z gradients. The gradient magnets have in the past been assumed to generate a linear gradient, and typical image reconstruction techniques have relied upon this assumption. However, to achieve high speed performance, gradient magnets often sacrifice linearity for speed. This non-linearity, in turn, results in distorted images, the distortion often being sufficiently large to compromise the usefulness of MRI images for stereotaxy or longitudinal studies, where precise volumetric information is required. The disclosure provides practical methods for correcting distorted images resulting from such non-linearity in the gradient fields, as well as distortions resulting from translational, rotational, and / or winding / design errors in the field generating devices. The methods employ spherical harmonic expansions of the gradient fields and fast Fourier transform techniques to provide well-corrected images without undue computational burdens.

Owner:THE UNIV OF QUEENSLAND

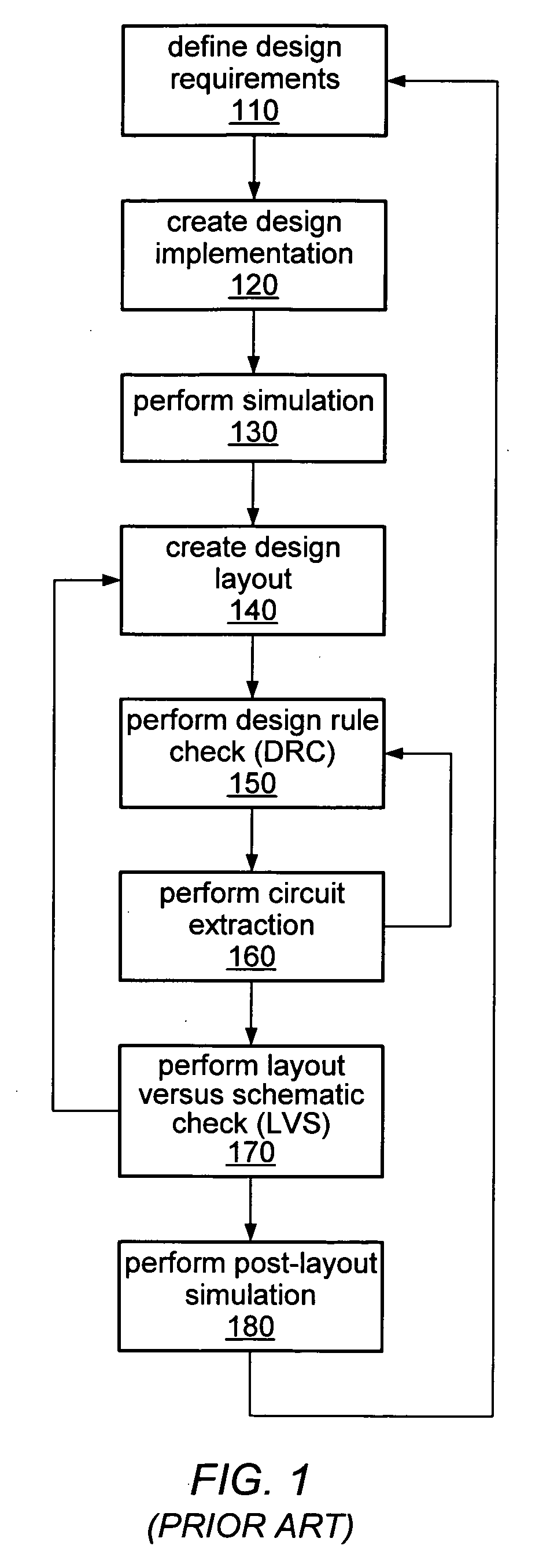

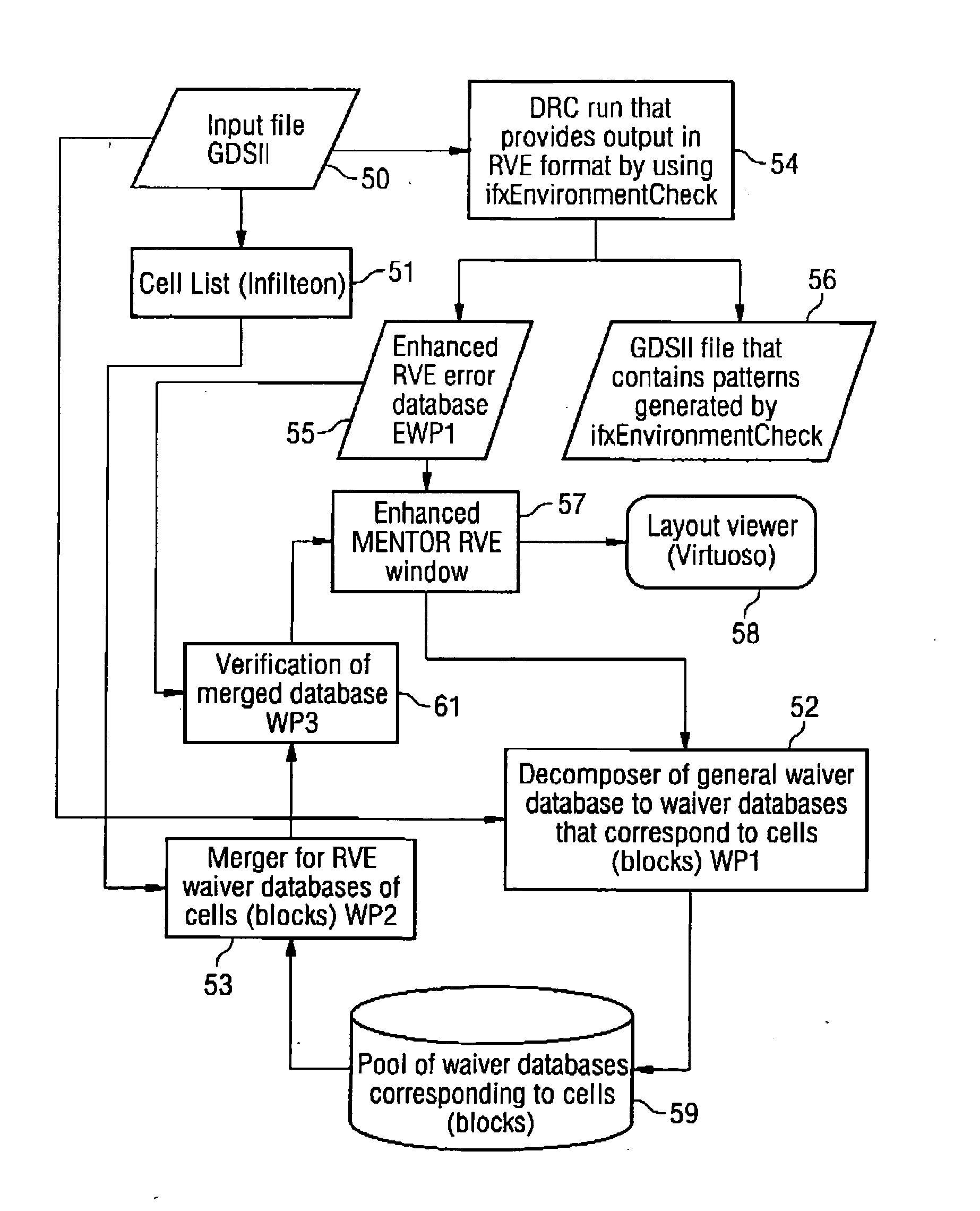

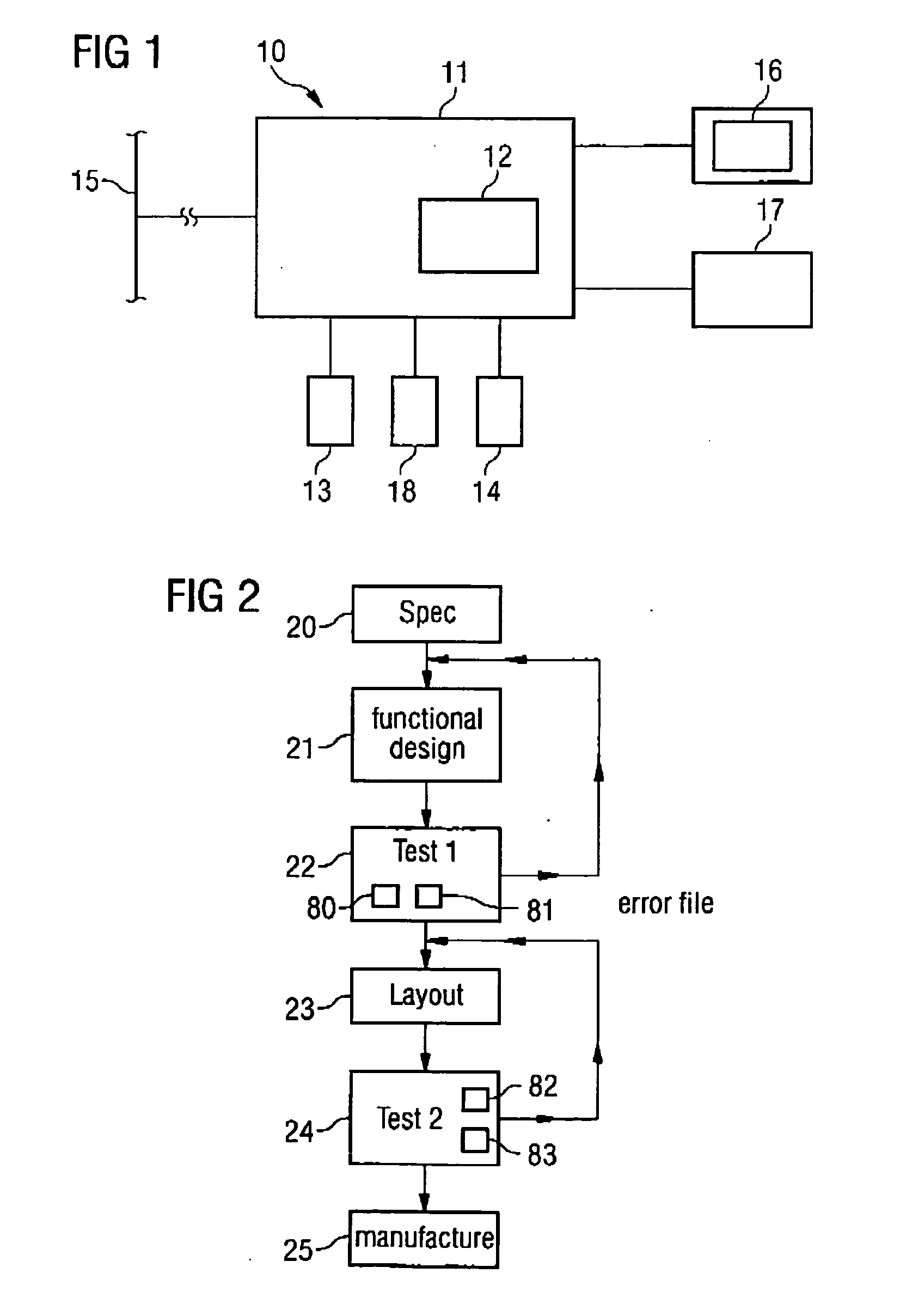

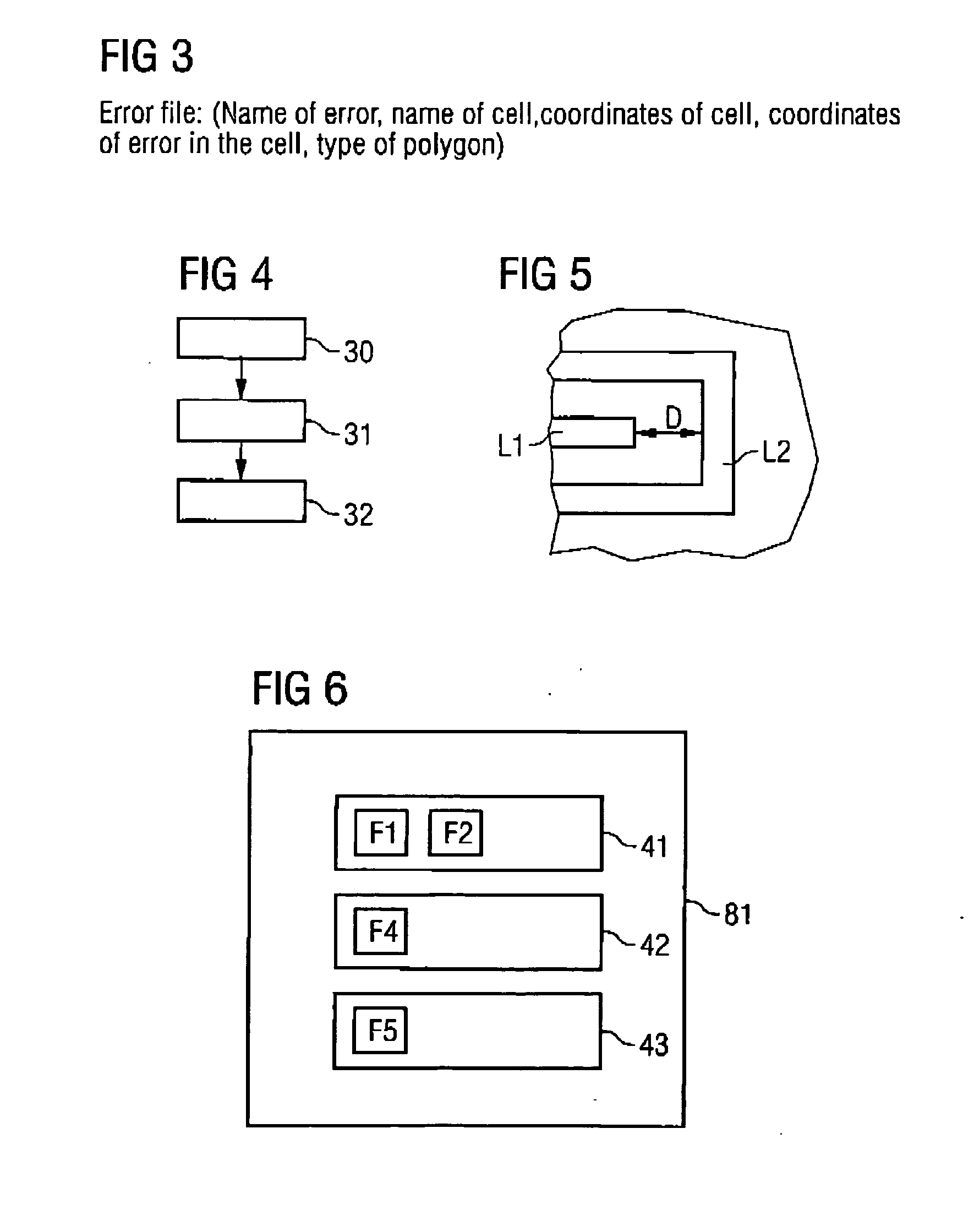

Method for treating design errors of a layout of an integrated circuit

InactiveUS20070192754A1Computer aided designSoftware simulation/interpretation/emulationProcess errorEngineering

Embodiments of the invention provide a method for treating errors during the checking of a design of an integrated circuit. In one embodiment, the method includes checking the design of the integrated circuit for errors using predetermined design rules, wherein the design includes a plurality of cells, detecting a design error when the design deviates from the predetermined design rules, writing the design error into a design error file, wherein at least one detected design error is written into a design waiver file if the design error is allowed as an allowed design error in spite of the deviation from the predetermined rules, and storing the allowed design error in the design waiver file with specification of a cell in which the design error occurs.

Owner:INFINEON TECH AG

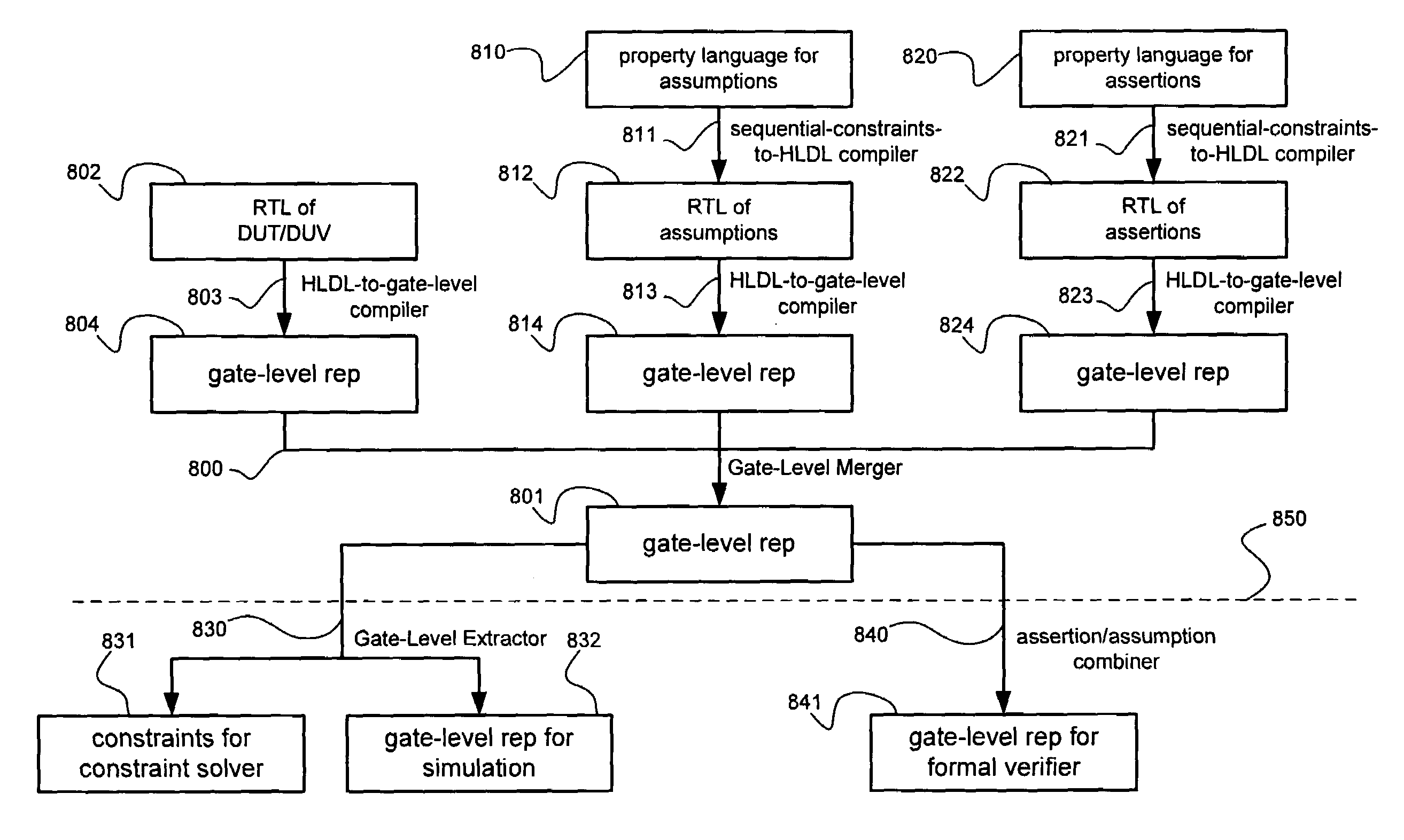

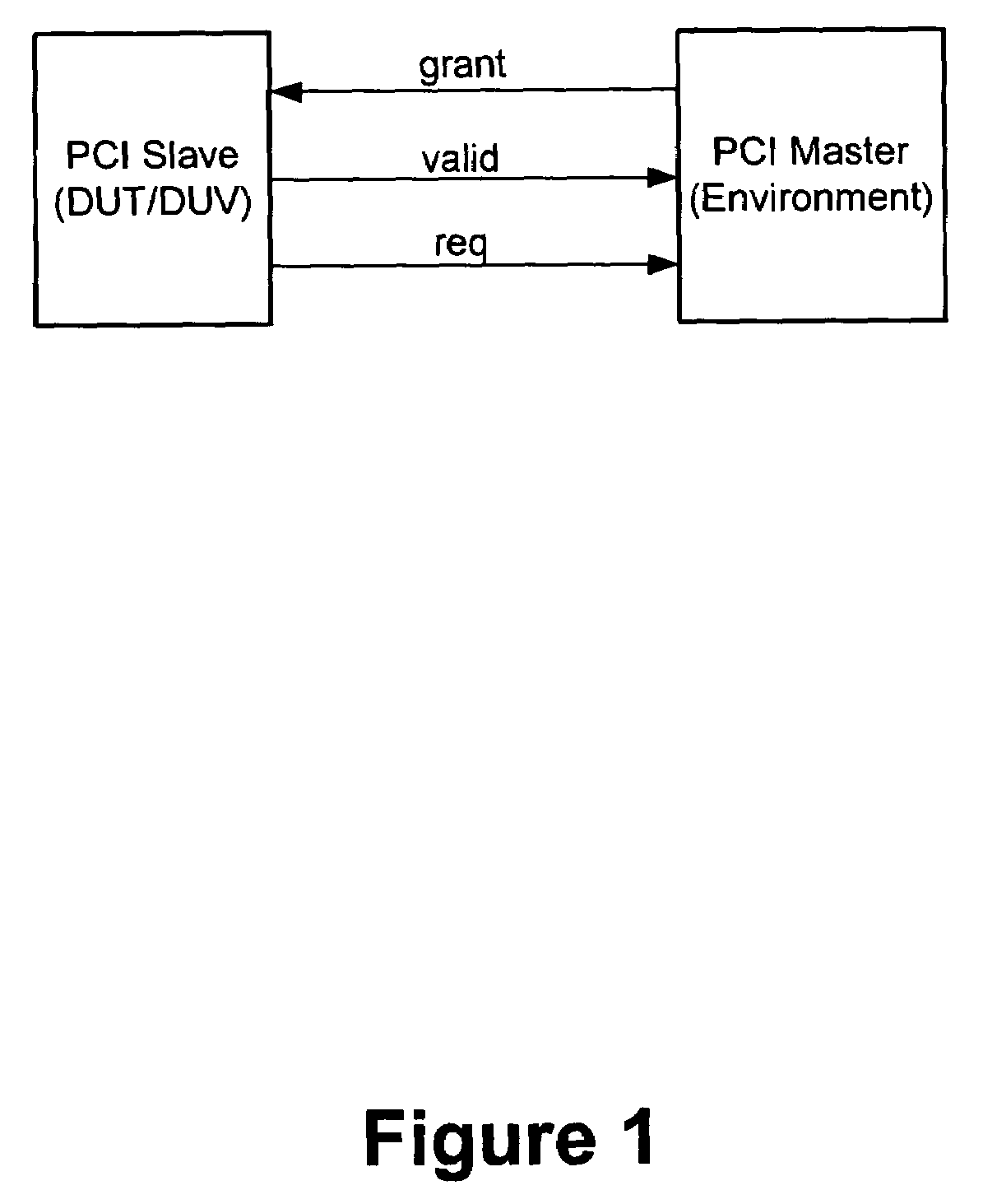

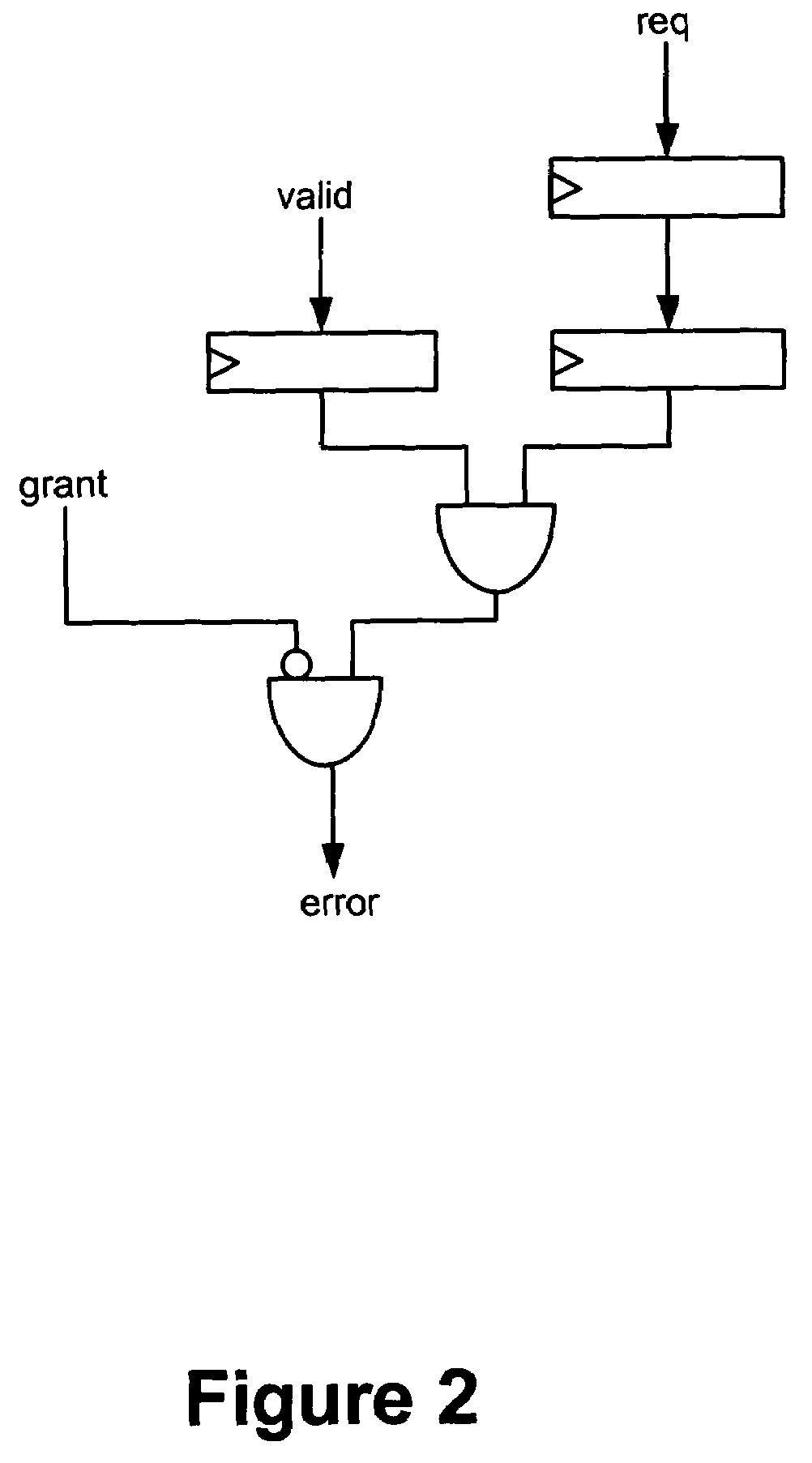

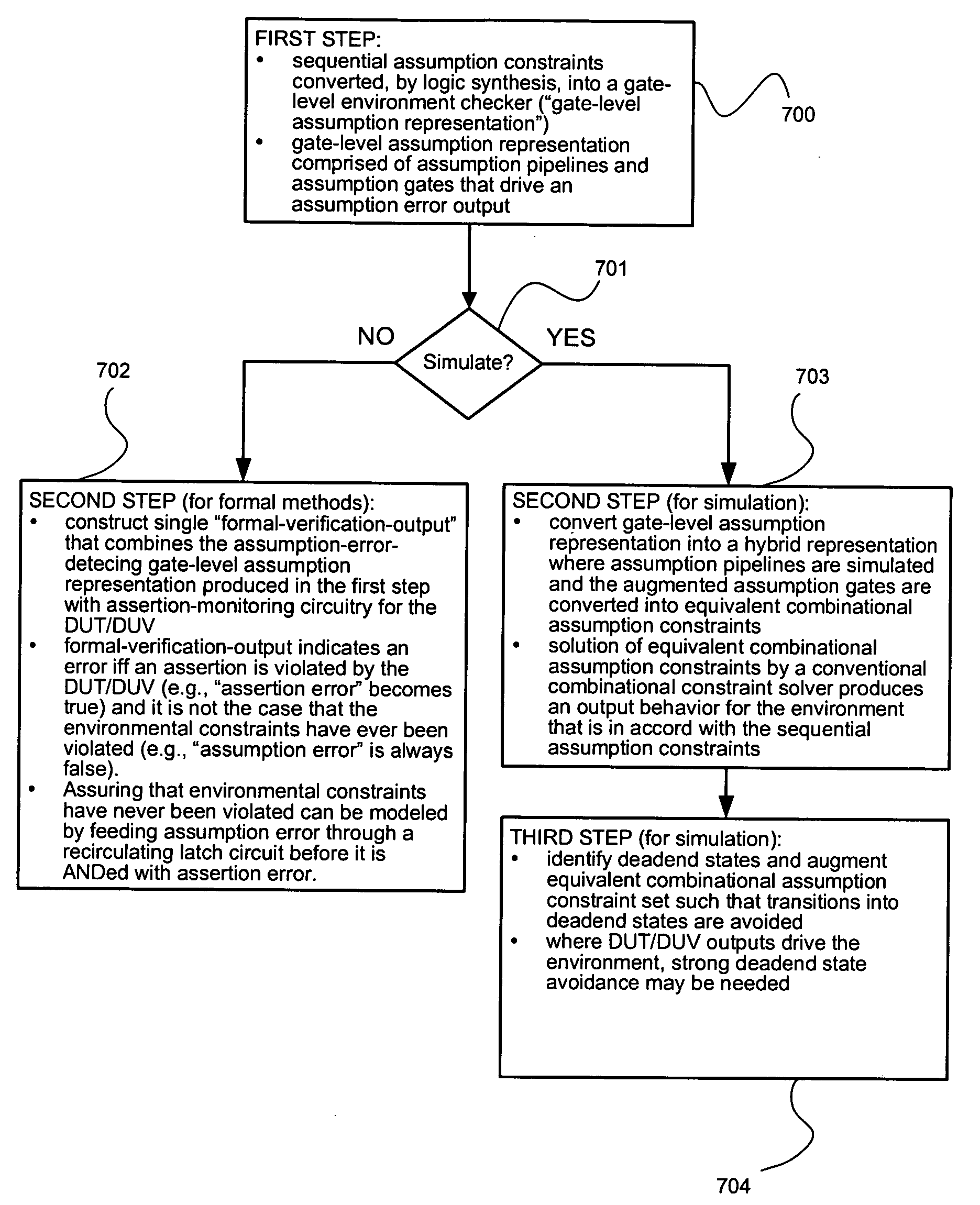

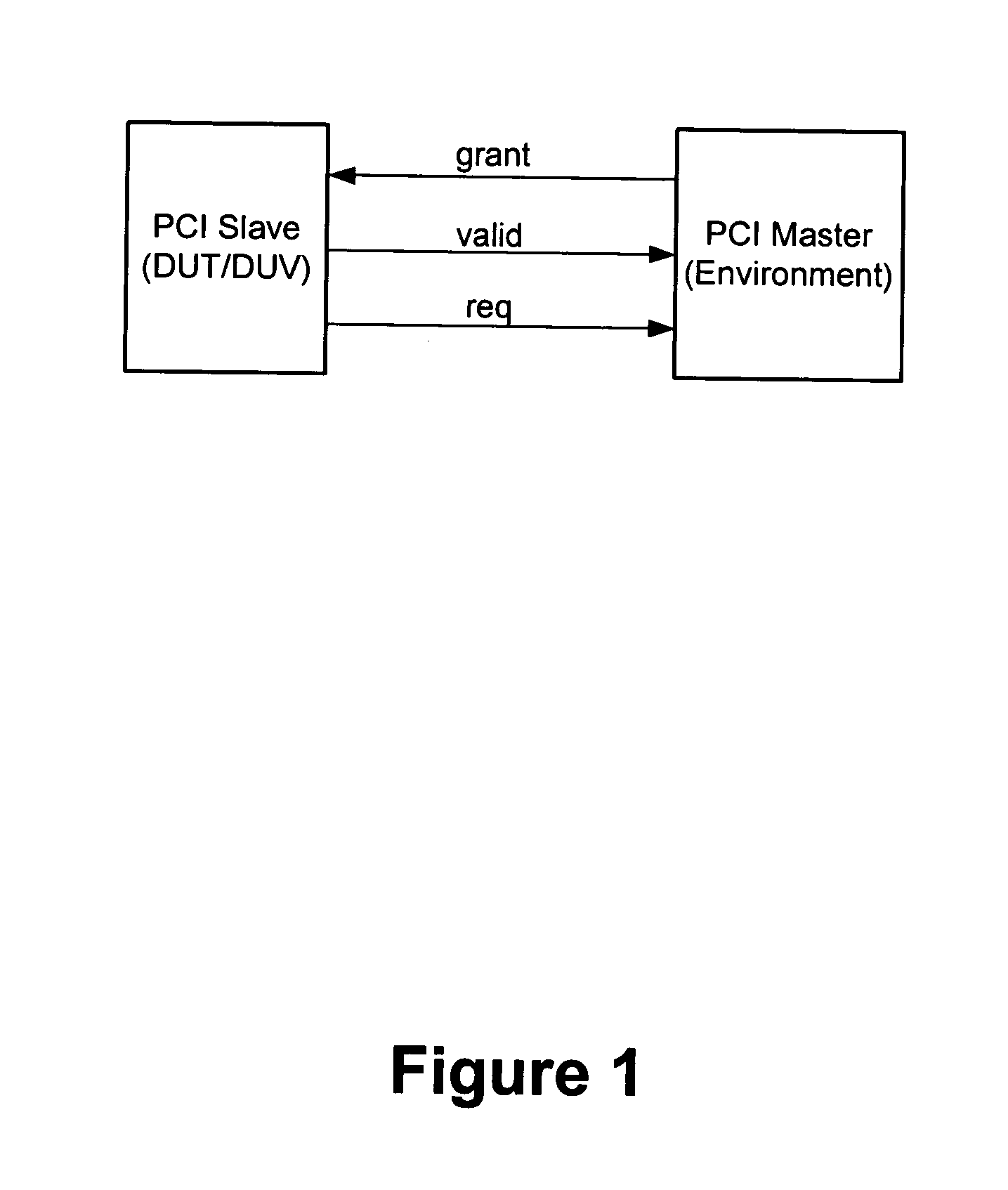

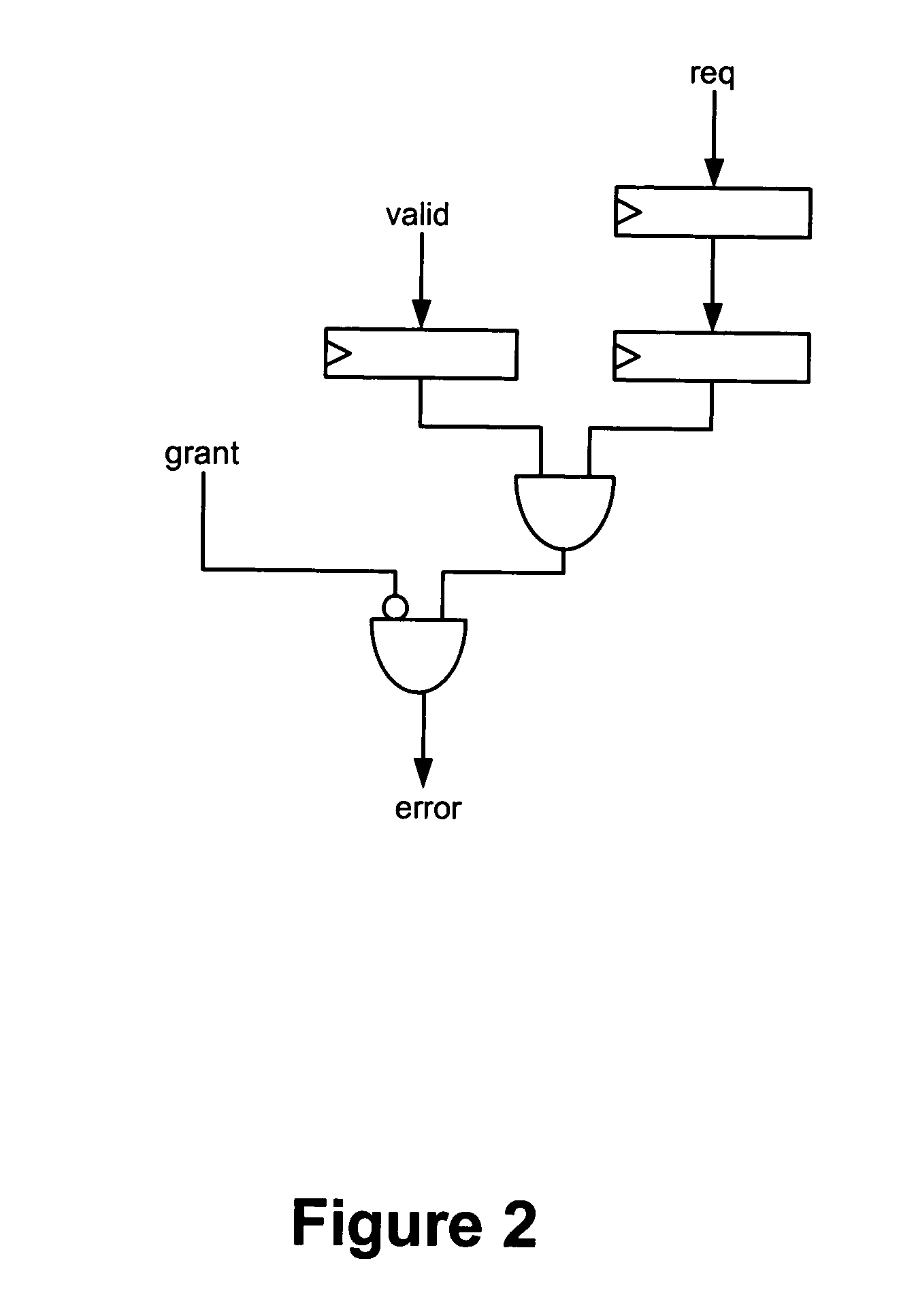

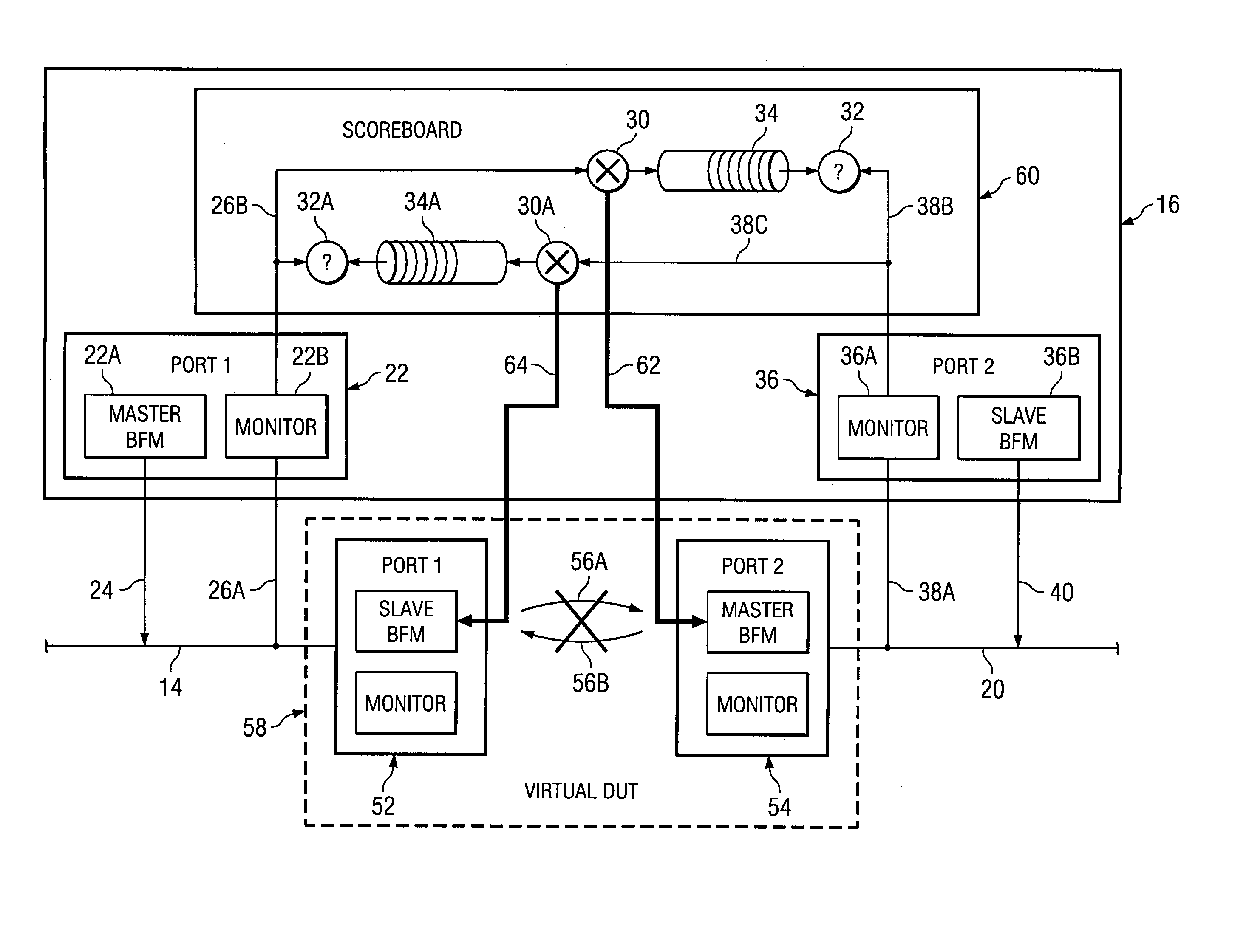

Method and apparatus for solving sequential constraints

ActiveUS7076753B2Computer aided designSoftware simulation/interpretation/emulationLogic synthesisCircuit design

Relates to automatic conversion of assumption constraints, used in circuit design verification, that model an environment for testing a DUT / DUV, where the assumptions specify sequential behavior. Such assumptions are converted, with the use of logic synthesis tools, into a gate-level representation. For formal verification, a verification output is constructed from the gate-level representation and DUT / DUV assertion-monitoring circuitry. A formal verifier seeks to prove the verification output cannot indicate a design error. For simulation verification, the gate-level representation is converted into a hybrid representation comprising pipelines and combinational constraints. During simulation, the pipelines hold state information necessary for a solution, of the combinational constraints, to be in accord with the sequential assumption constraints. For certain sequential assumption constraints, the combinational constraints are insufficient to insure avoidance of deadend states. In a deadend state, an assumption is violated. A method is presented for augmenting the combinational constraints to avoid deadend states.

Owner:SYNOPSYS INC

Method, system, and program product for interactive checking for double pattern lithography violations

Disclosed are a method, apparatus, and computer program product for performing interactive layout editing to address double patterning approaches to implement lithography of electronic designs. A spatial query is performed around the shape(s) being created during editing with the distance of allowed spacing in a single mask. If a design error is encountered, corrective editing may occur to correct the error. Checking may occur to make sure that the error detection and corrective actions can be performed interactively.

Owner:CADENCE DESIGN SYST INC

Method and apparatus for solving sequential constraints

ActiveUS20050138585A1Strong constraintComputer aided designSoftware simulation/interpretation/emulationLogic synthesisCircuit design

Relates to automatic conversion of assumption constraints, used in circuit design verification, that model an environment for testing a DUT / DUV, where the assumptions specify sequential behavior. Such assumptions are converted, with the use of logic synthesis tools, into a gate-level representation. For formal verification, a verification output is constructed from the gate-level representation and DUT / DUV assertion-monitoring circuitry. A formal verifier seeks to prove the verification output cannot indicate a design error. For simulation verification, the gate-level representation is converted into a hybrid representation comprising pipelines and combinational constraints. During simulation, the pipelines hold state information necessary for a solution, of the combinational constraints, to be in accord with the sequential assumption constraints. For certain sequential assumption constraints, the combinational constraints are insufficient to insure avoidance of deadend states. In a deadend state, an assumption is violated. A method is presented for augmenting the combinational constraints to avoid deadend states.

Owner:SYNOPSYS INC

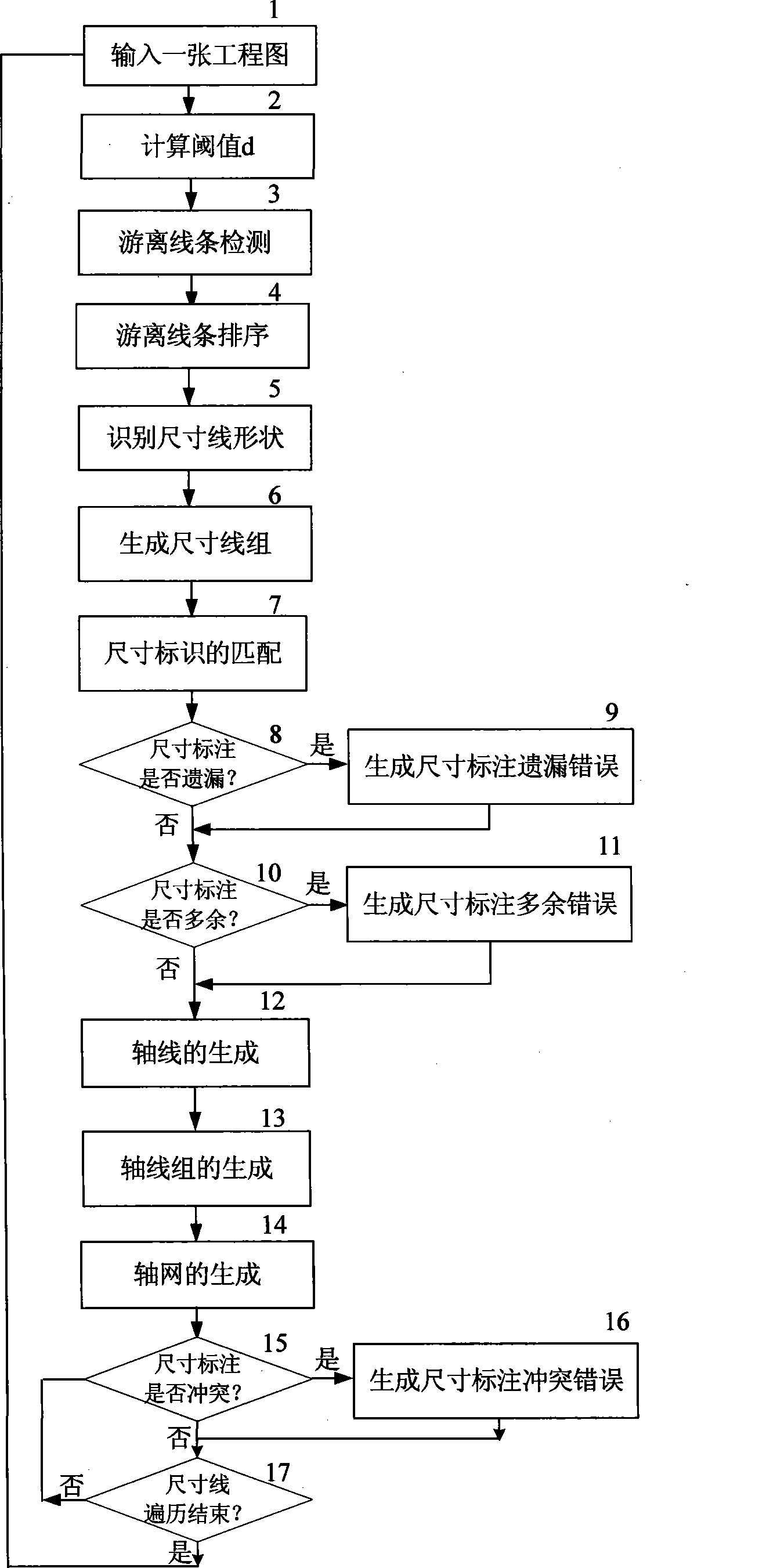

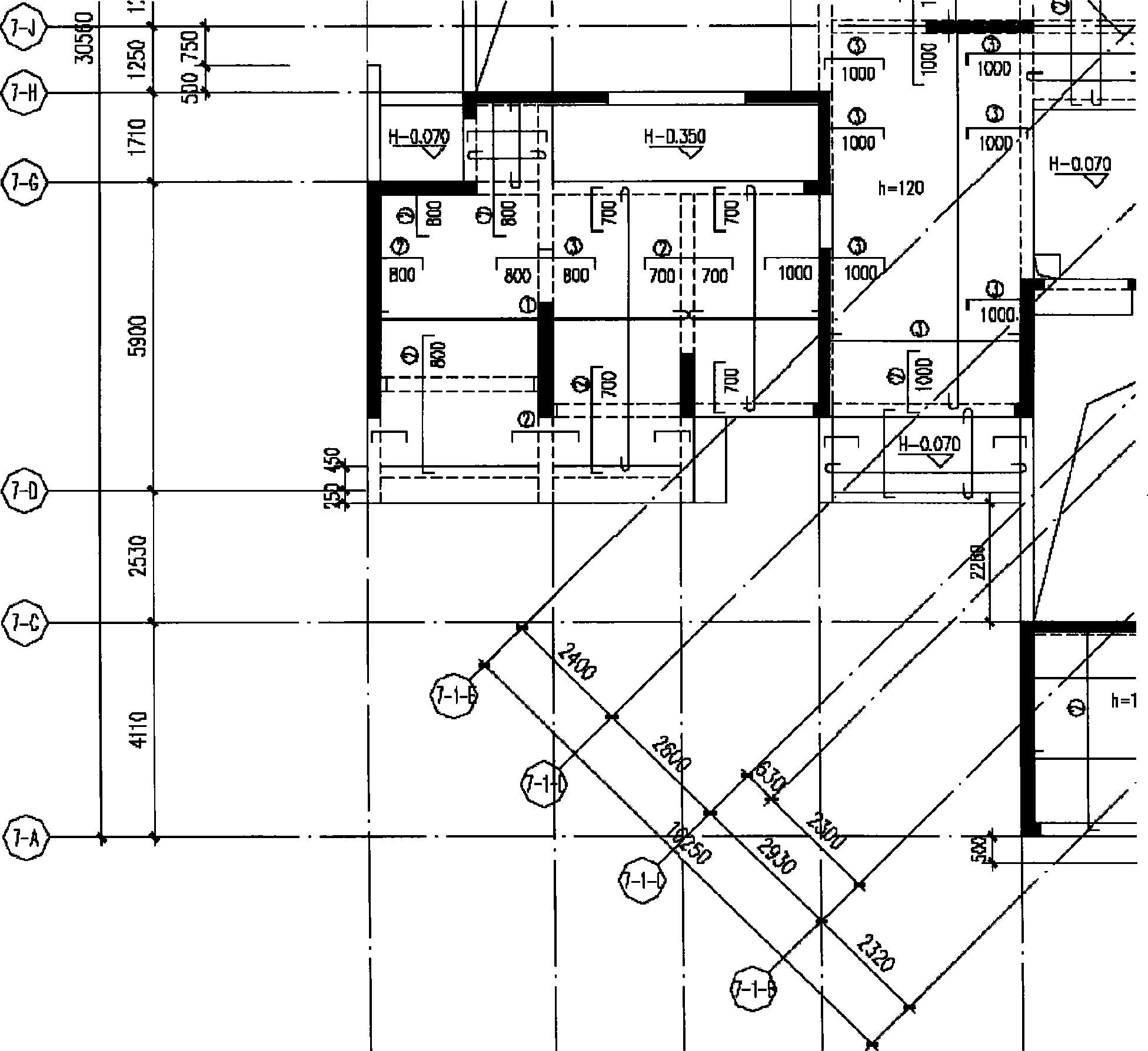

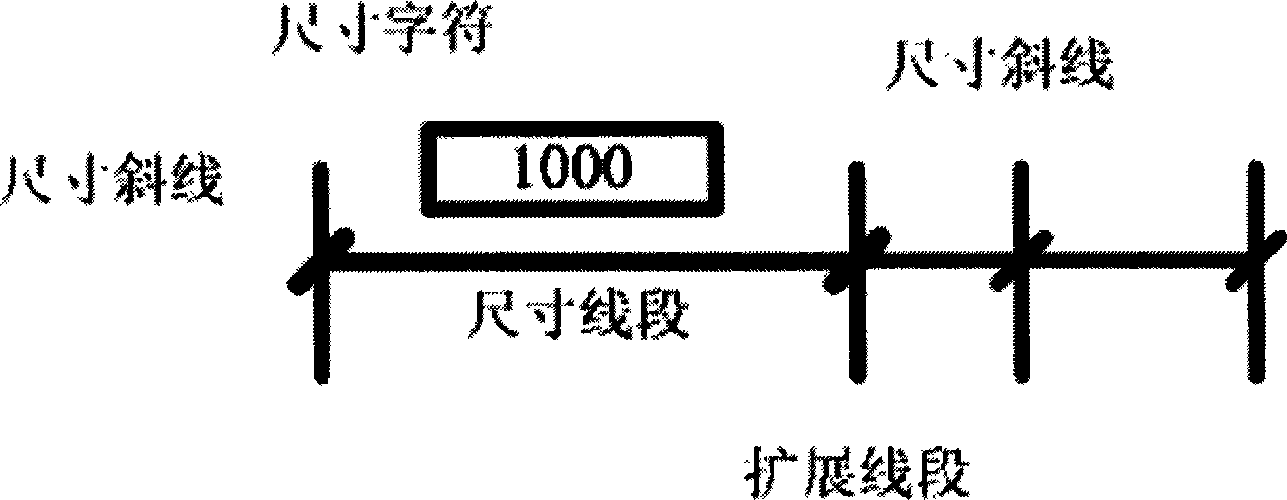

Automatic checking method for dimension line marking error in engineering drawing

InactiveCN101446999AImprove Aided Design EfficiencySave manual inspection overheadSpecial data processing applicationsComputer Aided DesignComputer science

The invention provides an automatic checking method for dimension line marking errors in an engineering drawing. The method comprises the following steps: on the basis of dissociated lines in the engineering drawing, by automatically identifying the shapes of a large quantity of dissociated dimension lines in the engineering drawing, the dissociated dimension lines are combined into a dimension line group, then, the dimension identification character strings of the dimension lines are searched by bilateral matching method, and whether the errors of mark missing or excess marks exist in the dimension marks are checked during the matching process; By inputting an engineering drawing into a CAD environment, the shapes and the marks of a large quantity of dissociated dimension lines can be quickly identified, and whether the dimension marking errors such as dimension mark missing, excess marks or dimension mark conflict exist is detected through the matching of the dimension line shapes and the identification character strings and the generation of an axis net, thereby saving a large amount of expense on manual check, reducing or avoiding design error, and effectively improving the efficiency of CAD.

Owner:NANJING UNIV

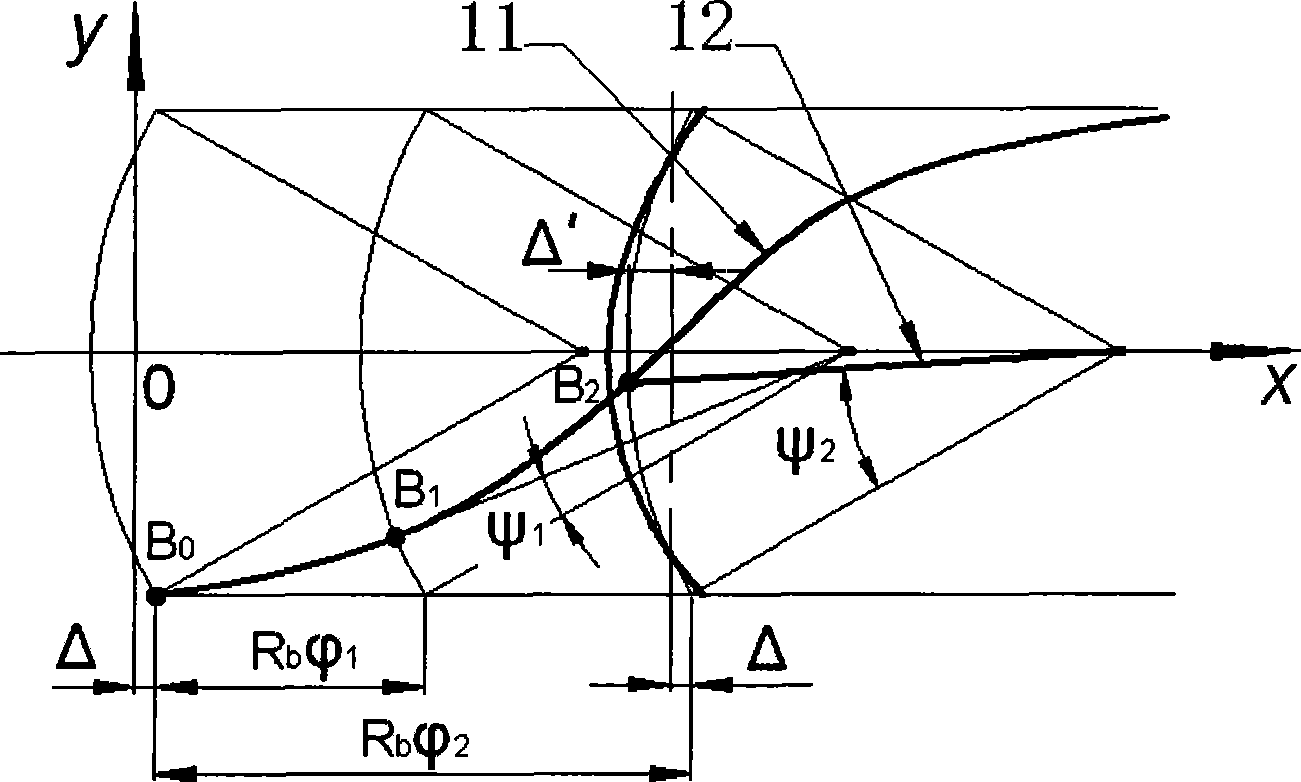

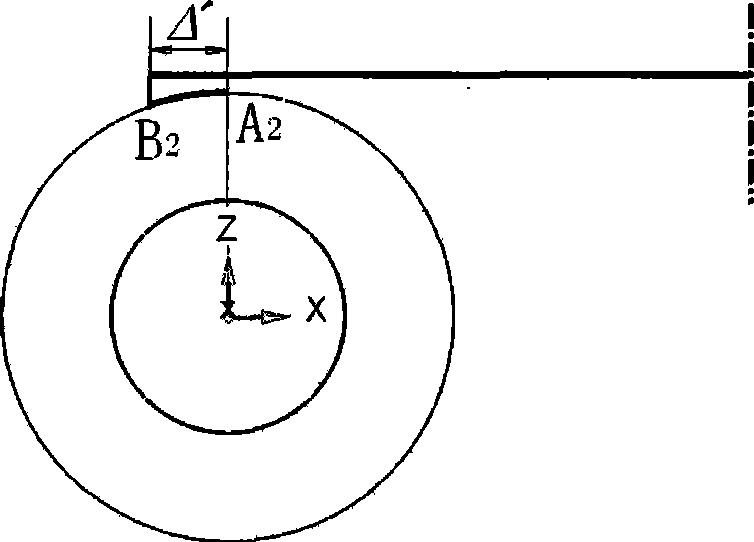

Method for designing swinging follower cylindrical cam contour line

The invention relates to a design method of a cylindrical cam profile of an oscillating follower. The method is characterized by comprising the following steps: introducing a coordinate expression of a 3D evolute of a displacement curve of the oscillating follower, putting forward a concept of a deviation angle, deducting the expression of the deviation angle according to a geometrical relation, and establishing a profile equation which is convenient for analyzing, designing and constructing the cylindrical cam of the oscillating follower; deducting an expression of a pressure angle according to the geometrical relation of the profile evolute, drawing a relation curve of a base radius R in relation to a maximum pressure angle alpha, and obtaining the minimum base radii which are corresponding to different allowable pressure angles; and programming an MATLAB program according to a known expression, namely, S=f(phi), 1, a and R, extracting coordinate values of the curve by MATLAB software after the operation of the program, pasting the coordinate values to AutoCAD software under a 'PLINE' command after processing, and then processing the coordinate values to 3D CAD software to obtain the profile. The solution process and the design process of the method are concise, visual, and easy to be controlled and practical, and have no design error.

Owner:NINGBO INST OF TECH ZHEJIANG UNIV ZHEJIANG

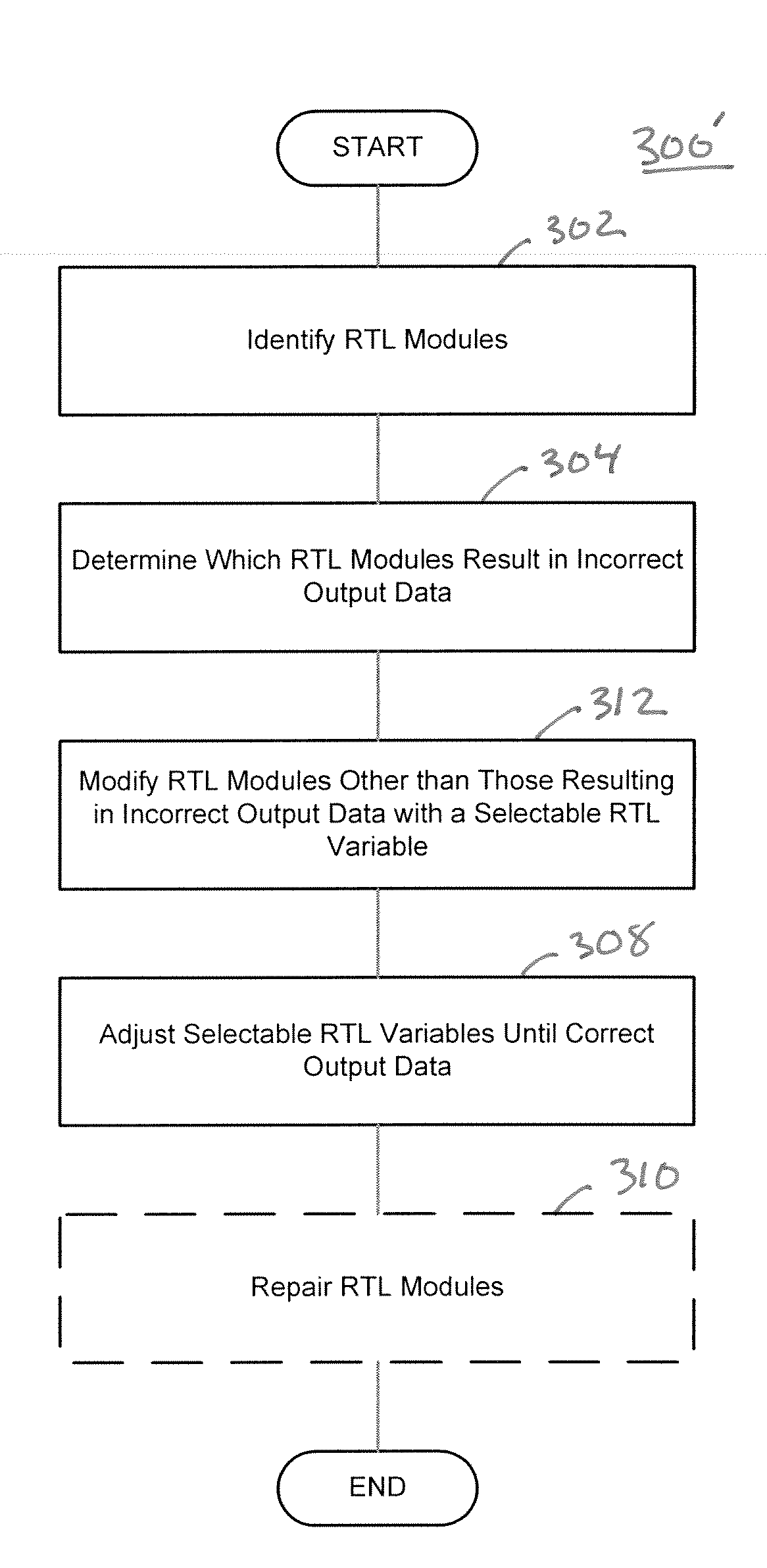

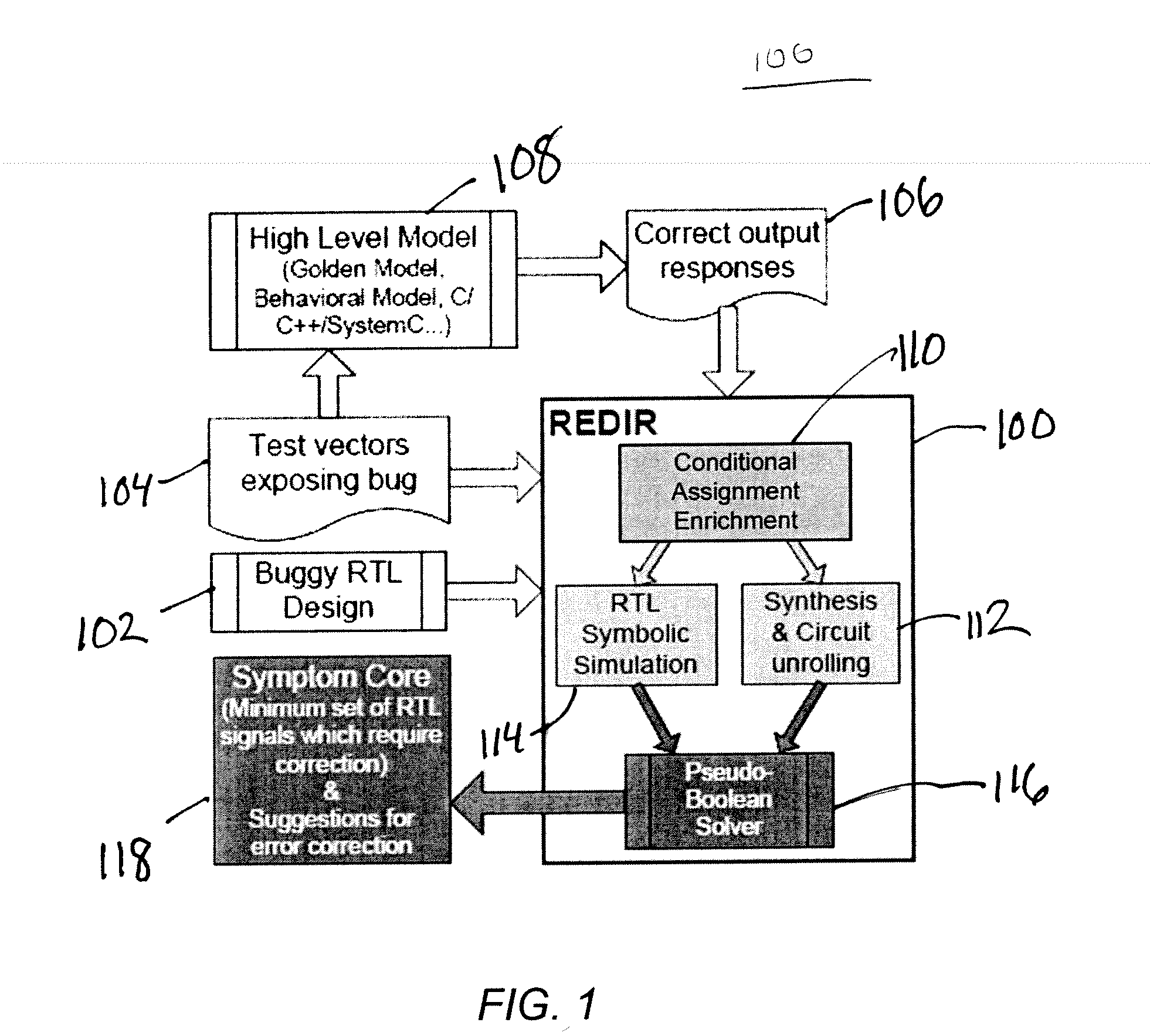

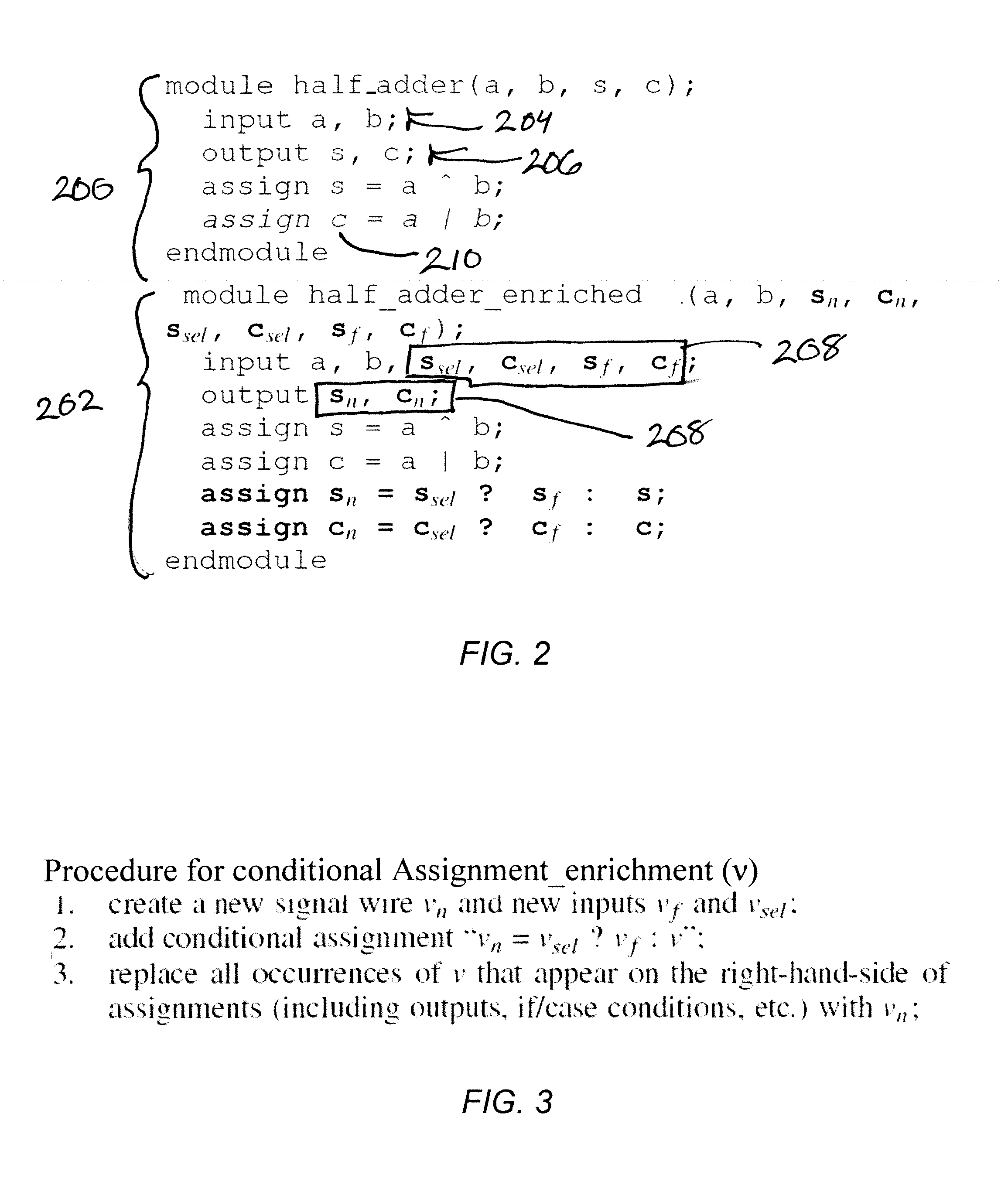

Automatic Error Diagnosis and Correction for RTL Designs

InactiveUS20080295043A1Facilitate RTL debugging processImprove verification qualityComputer programmed simultaneously with data introductionCAD circuit designExtensibilityProcessor register

A computer executable tool facilitates integrated circuit design and debugging by working directly at the Register Transfer Level, where most design activities take place. The tool determines when an integrated circuit design produces incorrect output responses for a given set of input vectors. The tool accesses the expected responses and returns the signal paths in the integrated circuit that are responsible for the errors along with suggested changes for fixing the errors. The tool may operate at the RTL, which is above the gate-level abstraction which means that the design errors will be much more readily understood to the designer, and may improve scalability and efficiency.

Owner:RGT UNIV OF MICHIGAN

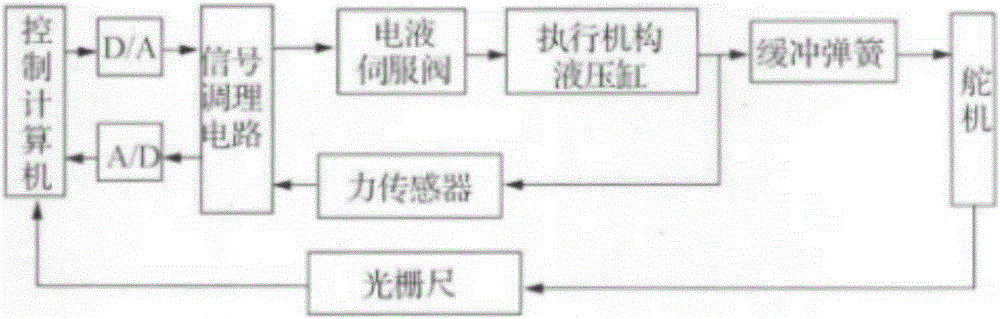

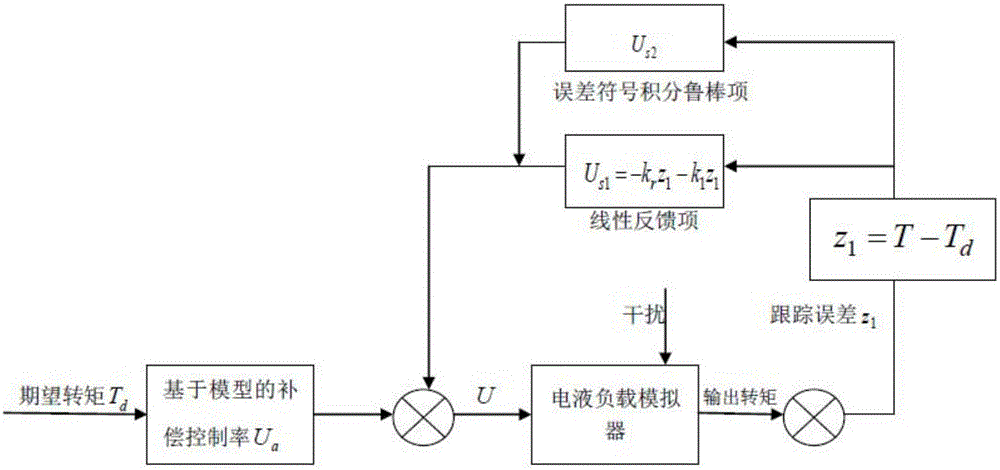

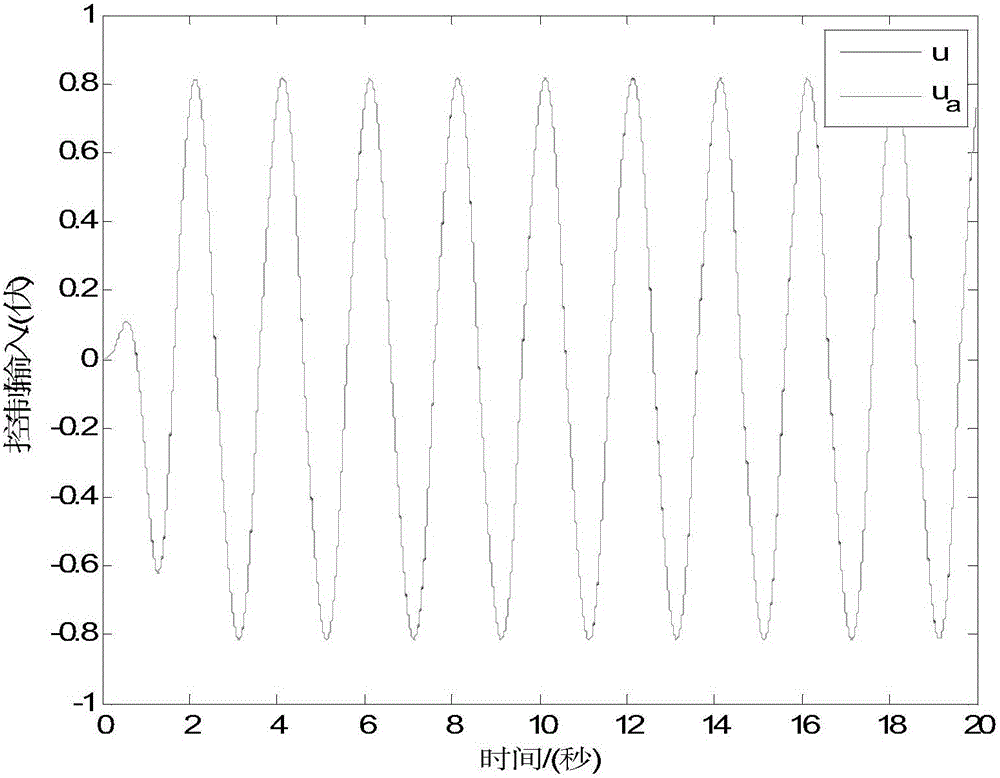

An electro-hydraulic load simulator error symbol integral robustness control method

ActiveCN105700352AImprove stabilityAccurate trackingAdaptive controlElectro hydraulicComputer science

The invention discloses an electro-hydraulic load simulator error symbol integral robustness control method. On account of system characteristics of an electro-hydraulic load simulator, friction characteristics of the system are analyzed through friction identification, and a continuously differentiable friction model is established; parameter errors, modeling errors, unmodeled dynamics and outer interferences are classified into system non-determinacy non-linearity. A designed error symbol integral robustness control device realizes asymptotic stability performance in a condition that no high gain feedback is used, so that a good robustness effect is realized, and an output torque of the electro-hydraulic load simulator can be ensured to accurately track any assigned torque instruction. According to the invention, the design of the controller is simplified; control voltages of the controller are continuous; and application in engineering reality is facilitated.

Owner:NANJING UNIV OF SCI & TECH

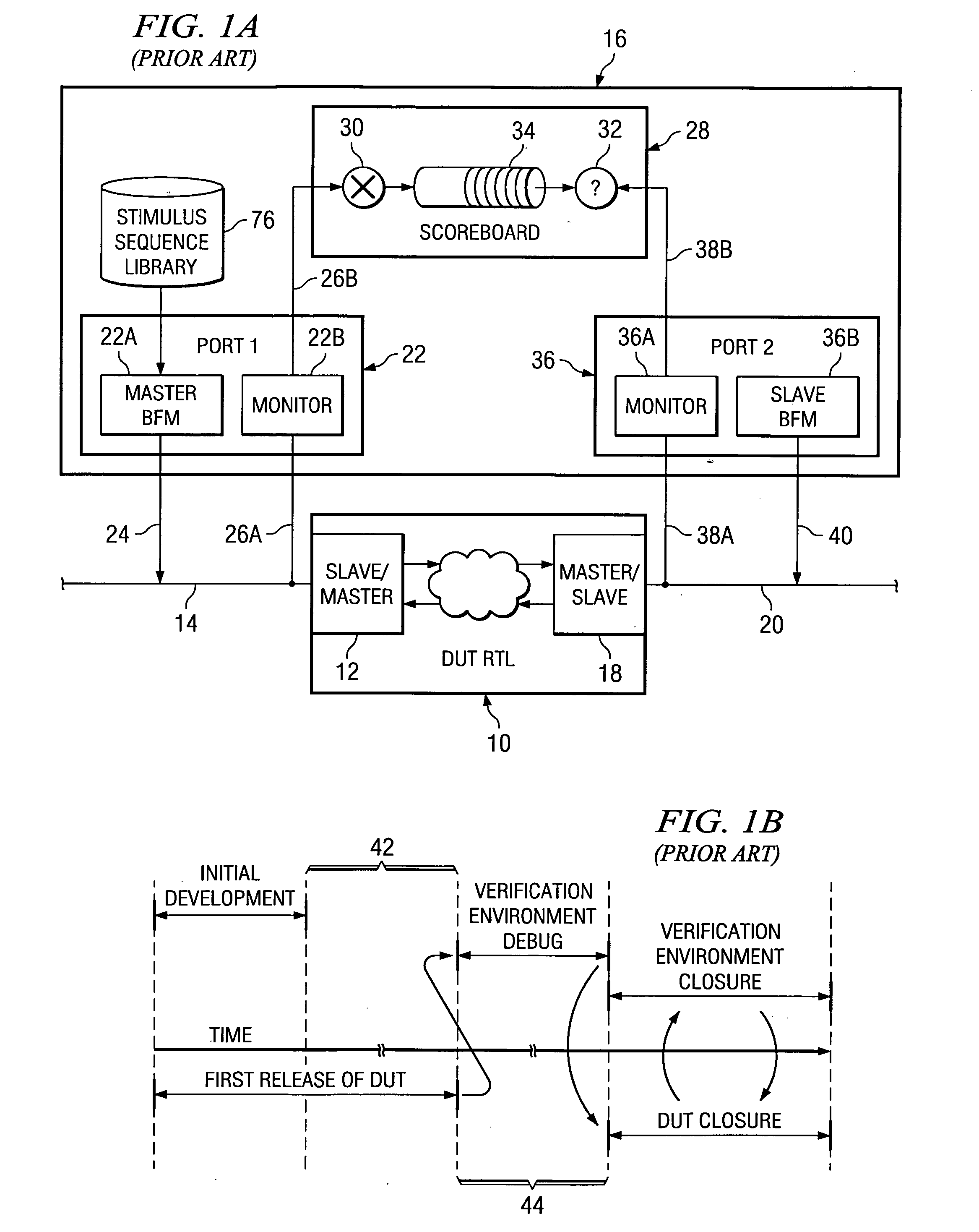

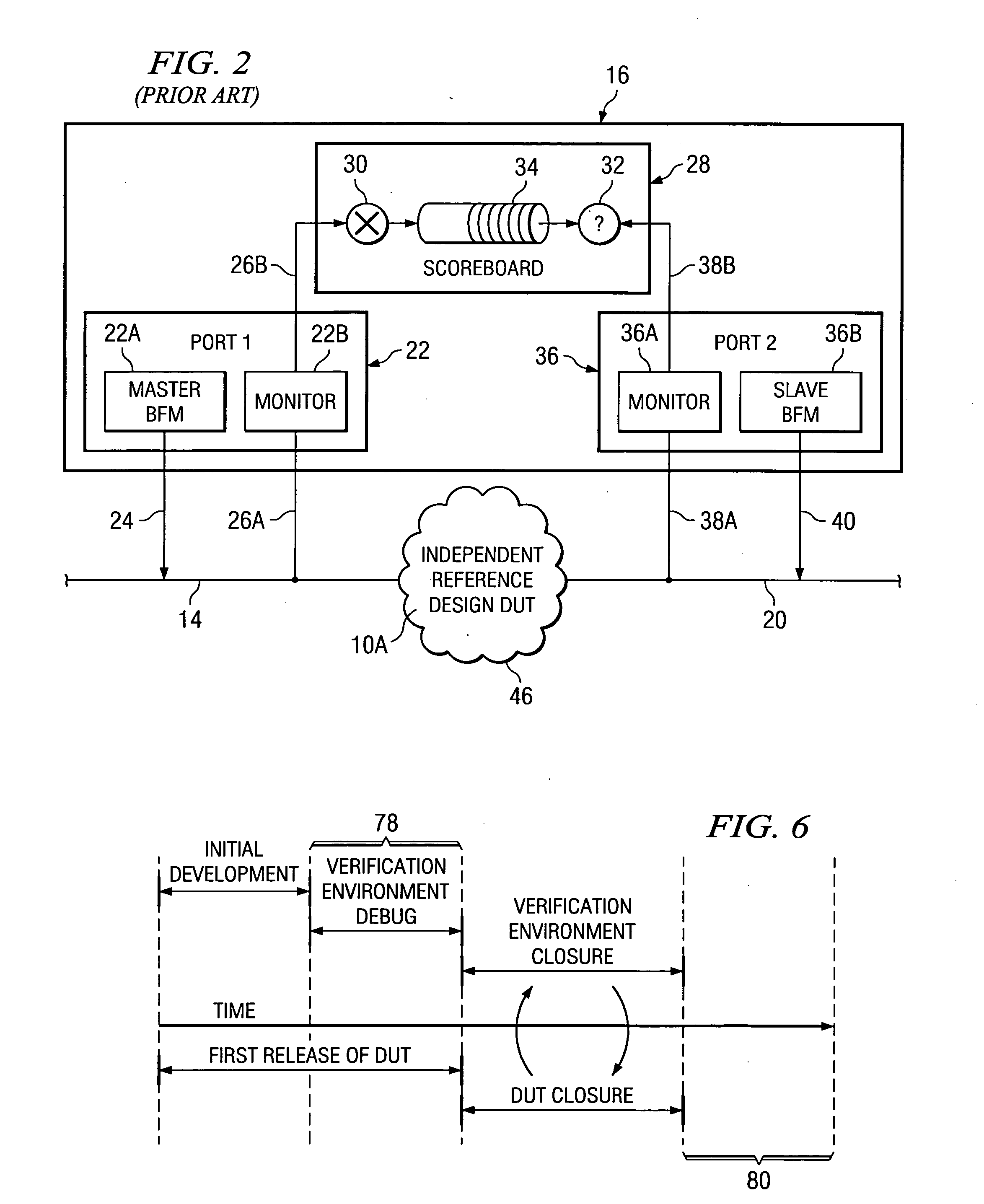

Method of verifying circuitry used for testing a new logic component prior to the first release of the component

A method and operation for developing and testing the logic environment used for providing logic inputs to and receiving logic inputs from a logic device or device under test such as an ASIC device prior to the completion of the device production design. The invention eliminates much of the waiting time typically required for determining whether problems are due to design errors in the DUT or incorrect operation of the environment used to test and develop the DUT.

Owner:TEXAS INSTR INC

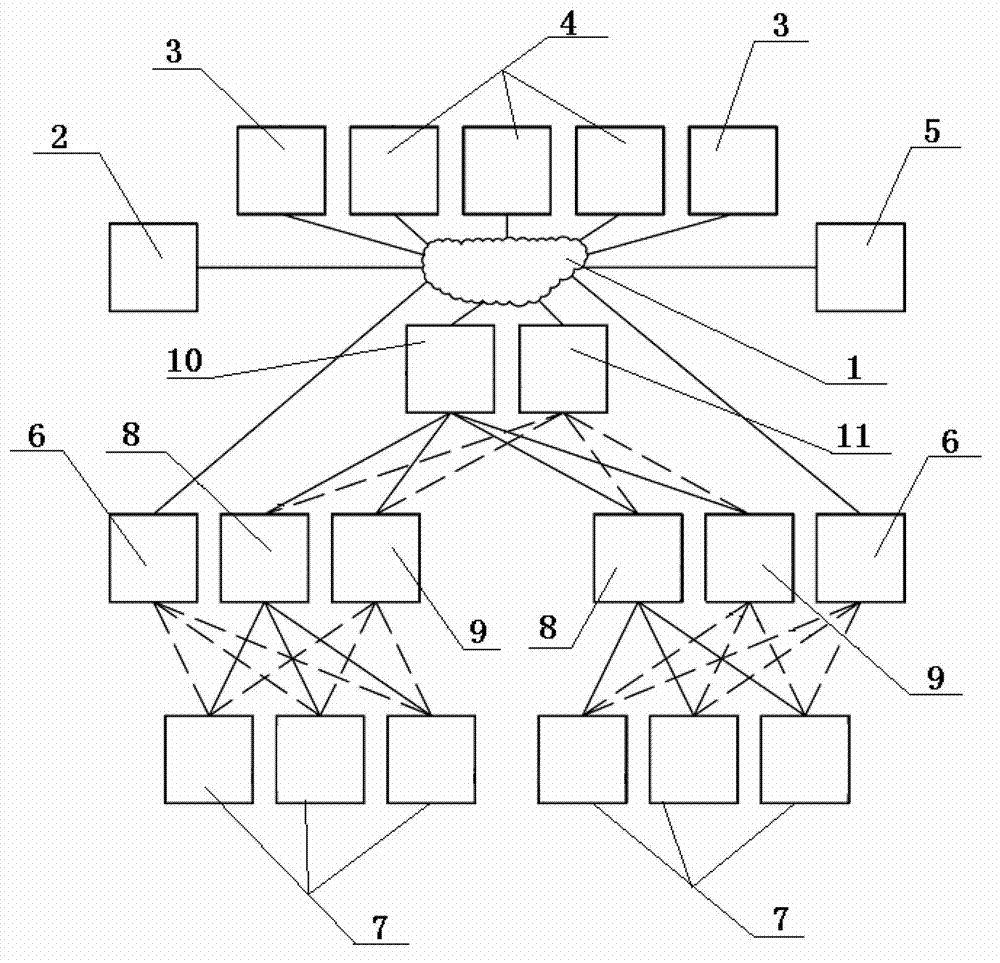

BIM (building information modeling) collaborative designing system based on cloud servers

InactiveCN103118114AImprove creation efficiencyImprove utilization efficiencyTransmissionGraphicsWorking environment

The invention relates to a BIM (building information modeling) collaborative designing system based on cloud servers. The BIM collaborative designing system comprises a computer network. The computer network is respectively connected to BIM mobile workstations, a plurality of family cloud servers, a plurality of BIM cloud servers, BIM application terminals, a plurality of family servers and primary BIM servers. The primary BIM servers are connected with a plurality of second BIM servers. Each of the family servers and the second BIM servers is connected with a plurality of BIM image workstations. The BIM collaborative designing system has the advantages that working efficiency of collaborative design is remarkably improved, primary investment of hardware is reduced, reliability of design working environment is improved, working interruption and design data loss are prevented, collaborative design errors are reduced, and remote collaborations in different places can be realized.

Owner:CHINA RAILWAY CONSTR GROUP

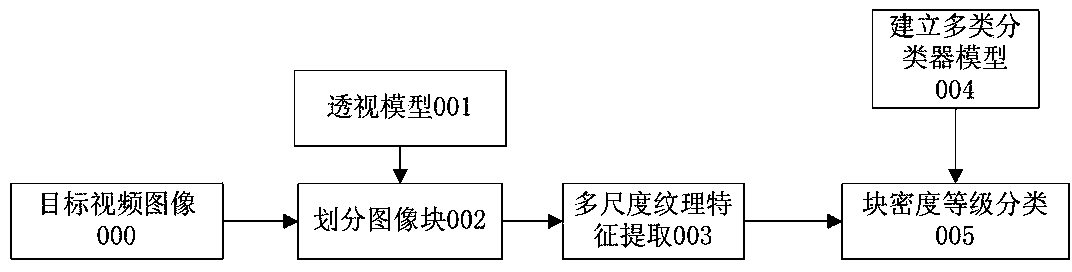

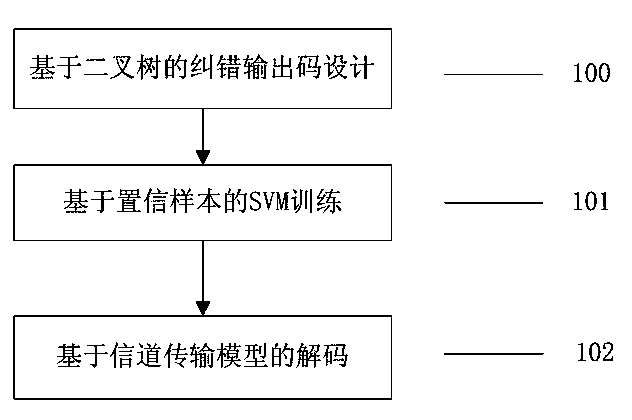

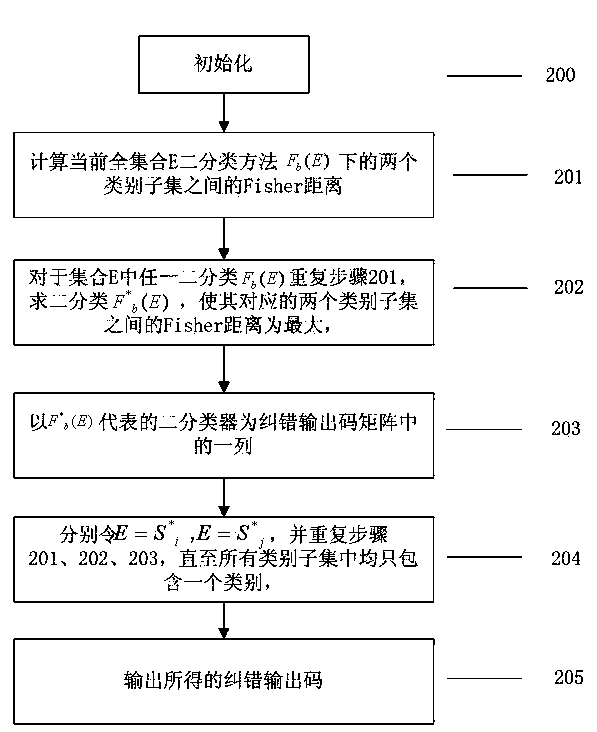

Method for classifying crowd density degrees in video image

The invention provides a method for classifying crowd density degrees in a video image. The method comprises the steps that firstly, an interest region is selected from the video image and is subjected to image block division and analysis according to a perspective model; secondly, multi-scale textural features are obtained for each image block; the video image is subjected to clustering analysis, a classifier model based on confidence degree analysis is established, multiple binary classifiers are optimized and combined by designing error correction output codes based on a binary-tree classification idea, confidence samples are extracted, and SVM binary classifiers are trained; finally, a channel transmission model is utilized to conduct decoding, and the crowd density degrees which the samples belong to are obtained according to the posterior probability maximum rule. According to the method, classification is conducted on the premise that sample sets and features are identical, the accuracy and generalization performance are both superior to those of a transmission classification model, and an idea is provided for solutions to various classification problems represented by crowd density estimation.

Owner:SICHUAN MIANYANG SOUTHWEST AUTOMATION INST

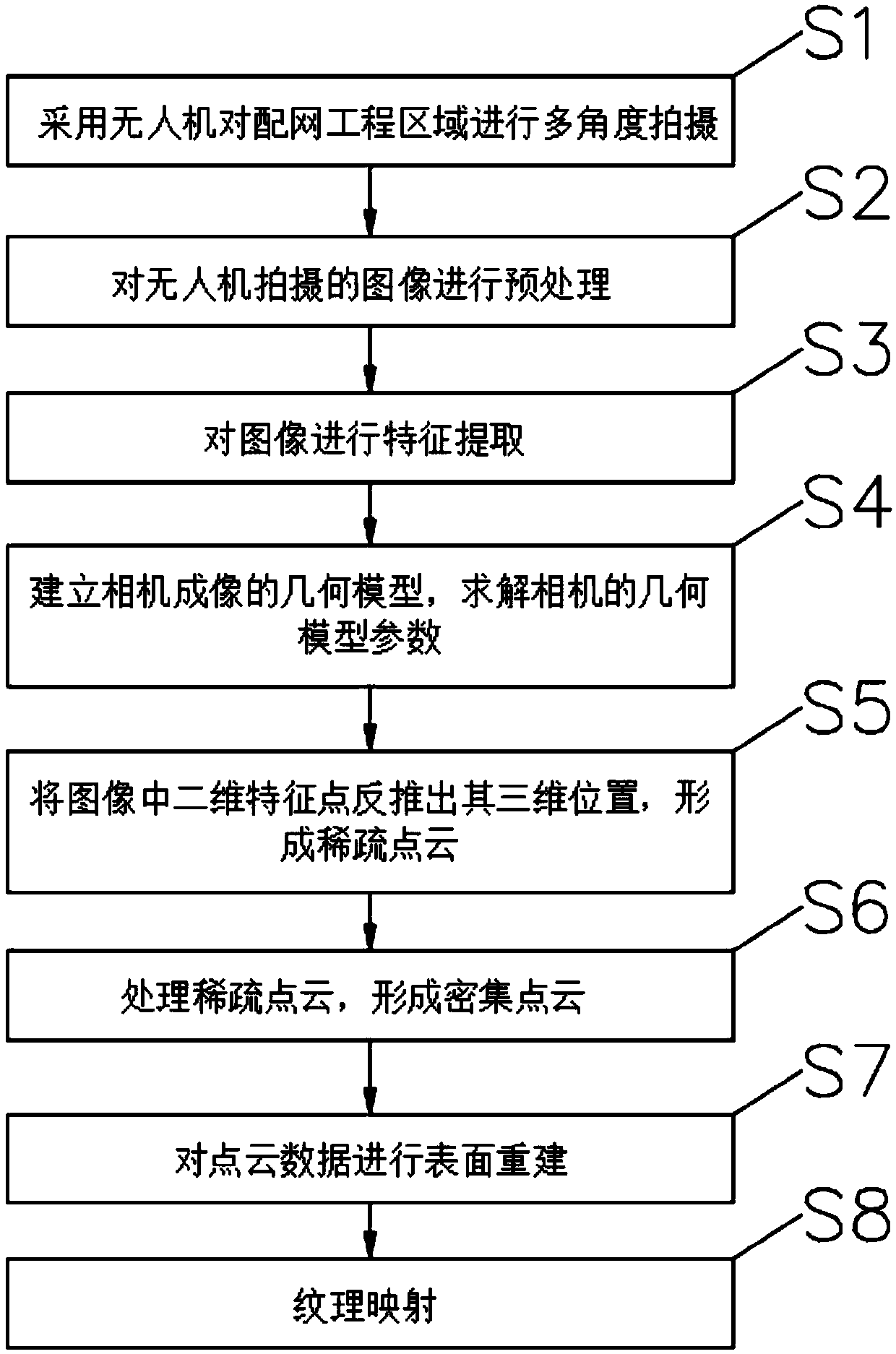

A distribution network three-dimensional scene modeling method based on a mixed reality technology

PendingCN109685886AReduce workloadReduce human resource consumptionDetails involving processing steps3D modellingMixed realityModel parameters

The invention provides a distribution network three-dimensional scene modeling method based on a mixed reality technology. The method comprises the following steps: S1, image acquisition: carrying outmulti-angle shooting on a distribution network engineering area by adopting an unmanned aerial vehicle; S2, image preprocessing: images shot by the unmanned aerial vehicle are screened, denoised andcalibrated; S3, obtaining feature points: carrying out feature extraction on the preprocessed image; S4, camera calibration: establishing a geometric model of camera imaging, and solving geometric model parameters of the camera; S5, acquiring sparse point cloud: through a calibration result, reversely deriving the three-dimensional positions of the two-dimensional feature points in the image, andreversely deducing all the two-dimensional feature points into a three-dimensional space to form the sparse point cloud; S6, obtaining dense point cloud: processing the sparse point cloud data to formdense point cloud; And S7, surface reconstruction: performing surface reconstruction on the dense point cloud data. The invention provides the distribution network three-dimensional scene modeling method which can improve the design efficiency and reduce the design errors.

Owner:STATE GRID ZHEJIANG HANGZHOU CITY FUYANG DISTRICT POWER SUPPLY CO LTD +1

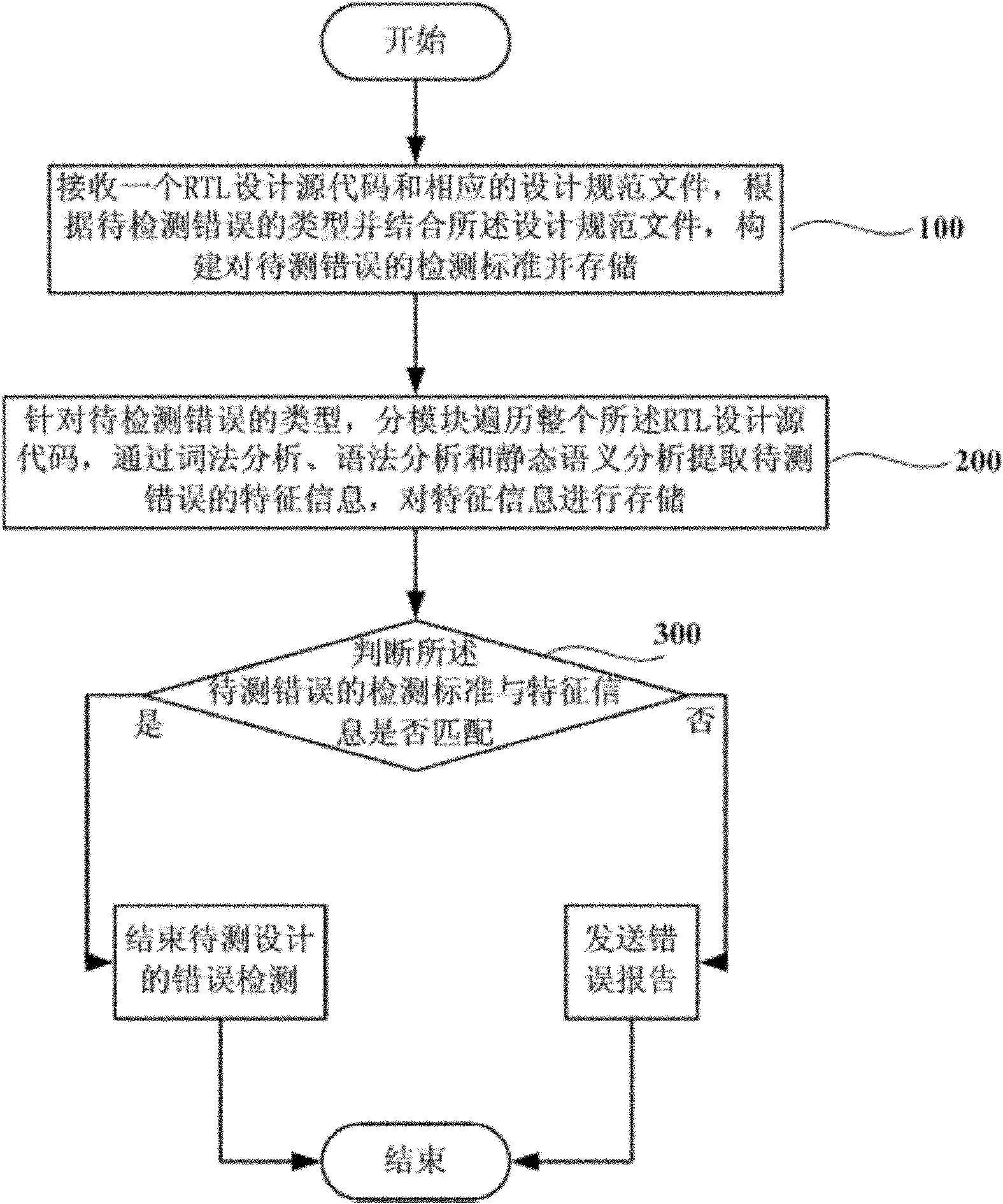

Static analysis-based method and system for detecting RTL (Resistor Transistor Logic) design errors

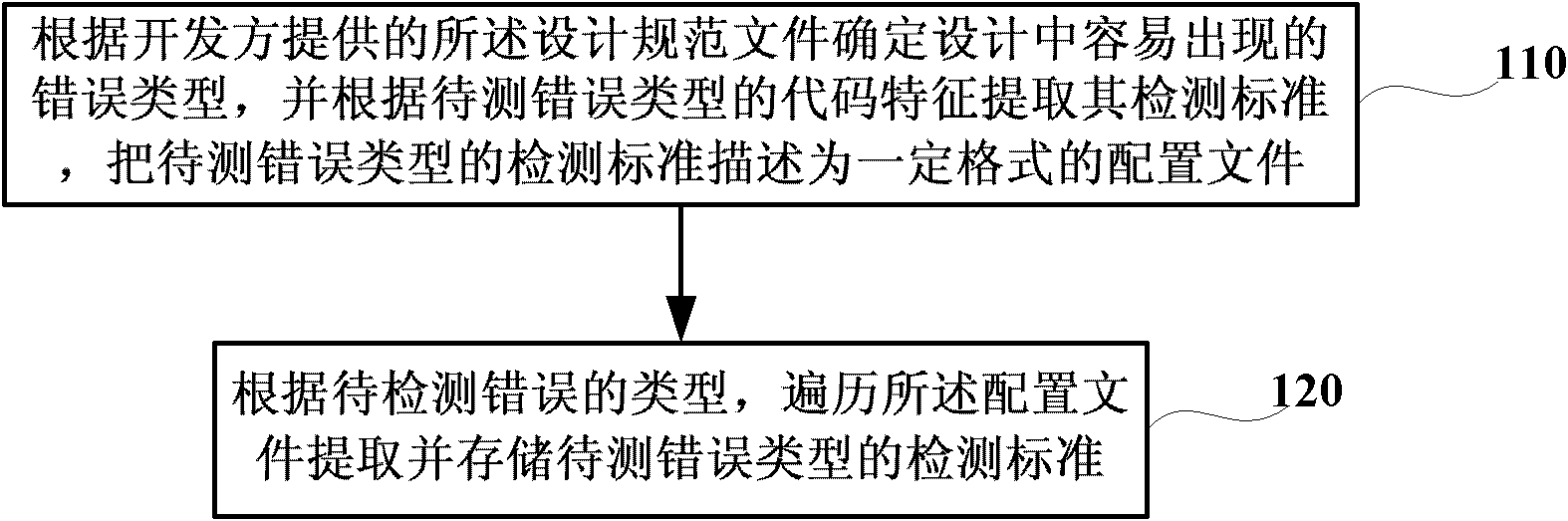

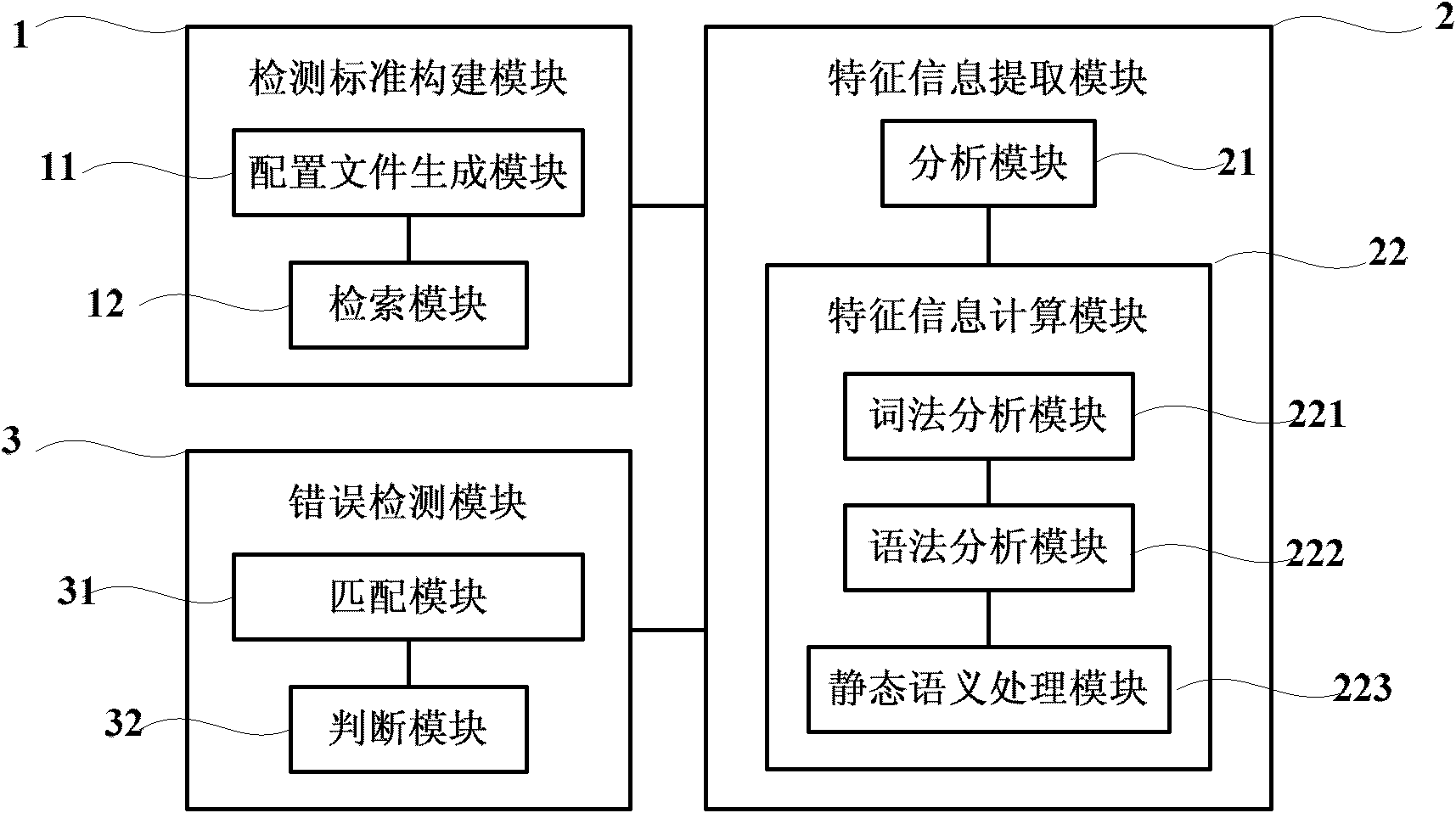

ActiveCN102054100ACan handle large design sizesHigh degree of automationSpecial data processing applicationsStatic timing analysisLexical analysis

The invention discloses a static analysis-based method and system for detecting RTL (Resistor Transistor Logic) design errors. The method comprises the following steps of: receiving an RTL design source code and a corresponding design specification file, constructing and storing a detection standard of errors to be detected according to the type of the errors to be detected and in combination with the design specification file; traversing the whole RTL design source code in modules aiming at the types of the errors to be detected, extracting characteristic information of the errors to be detected through lexical analysis, grammatical analysis and static semantic analysis, and storing the characteristic information; and judging whether the detection standard of the errors to be detected is matched with the characteristic information, if so, ending the error detection of the design to be detected, and otherwise, sending an error report.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

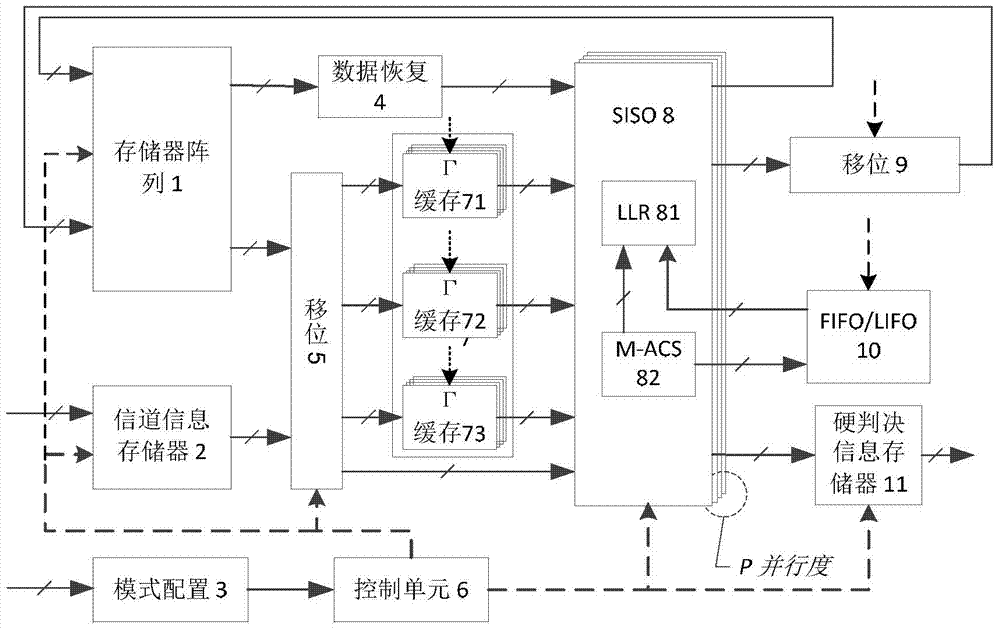

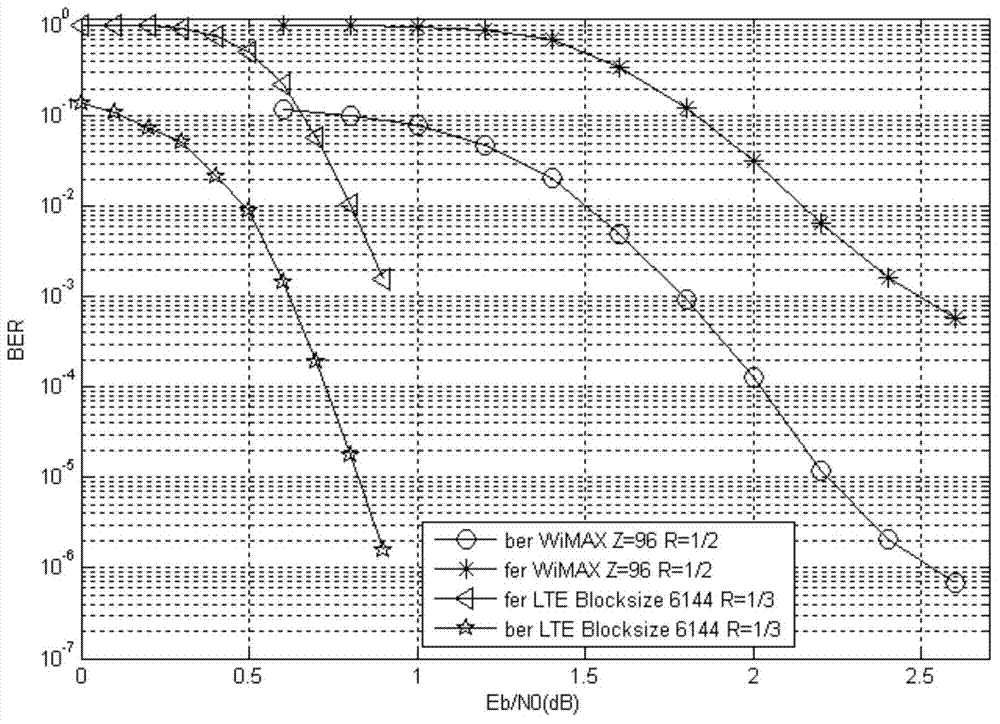

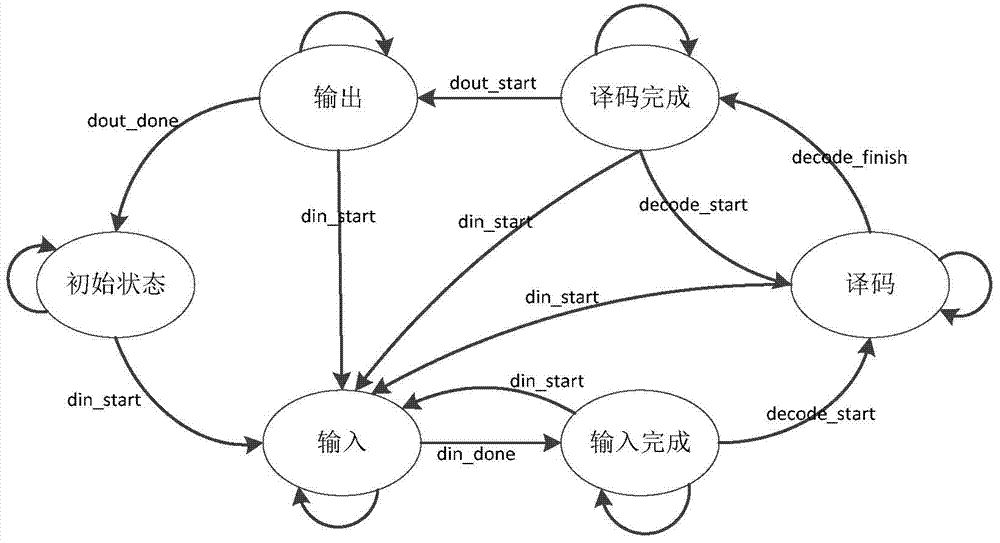

High-performance multistandard FEC (Forward Error Correction) decoder

The invention belongs to the technical field of wireless digital communication and broadcast, and particularly relates to a high-performance multistandard FEC (Forward Error Correction) decoder. The decoder is flexible and configurable, and can be simultaneously compatible with multistandard and multimode of a LDPC code and a Turbo code. The decoder can meet the requirements of high throughput rate and low power consumption of a current communication system, can enable a designed structure to have higher structure configurability simultaneously, and can be very easily applied in different communication standards. The decoder can support WiMAX and WMAN WLAN (Wireless Local Area Network) broadband access technology and an LTE standard of 4G mobile communication. The decoder works at an LDPC decoding mode in a WiMAX and a WLAN, and works at a Turbo decoding mode in LTE communication. Designed error correcting codes can be used for decoding all 114 modes in the WiMAX, all 12 modes in the WLAN and all 188 modes in LTE.

Owner:FUDAN UNIV

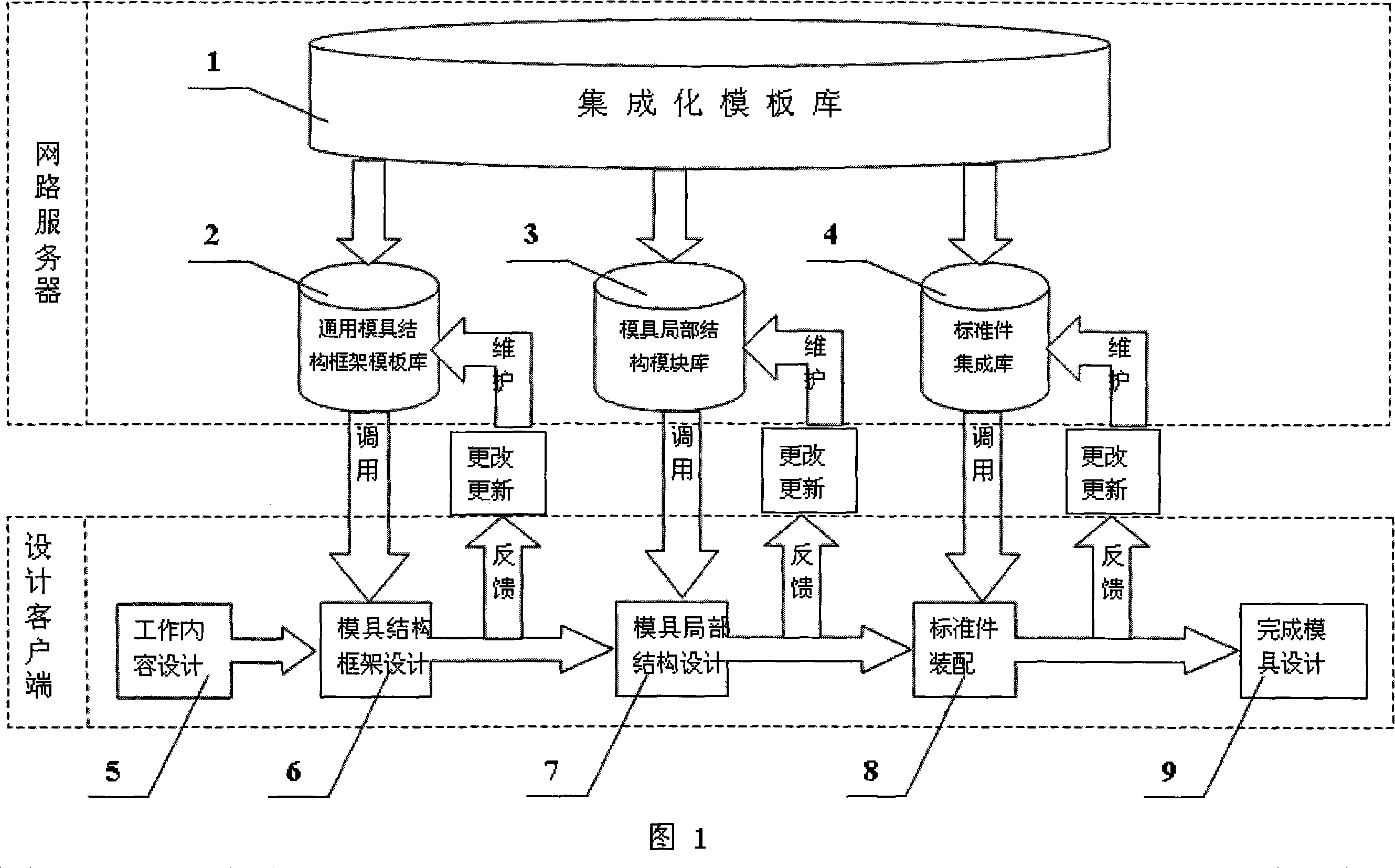

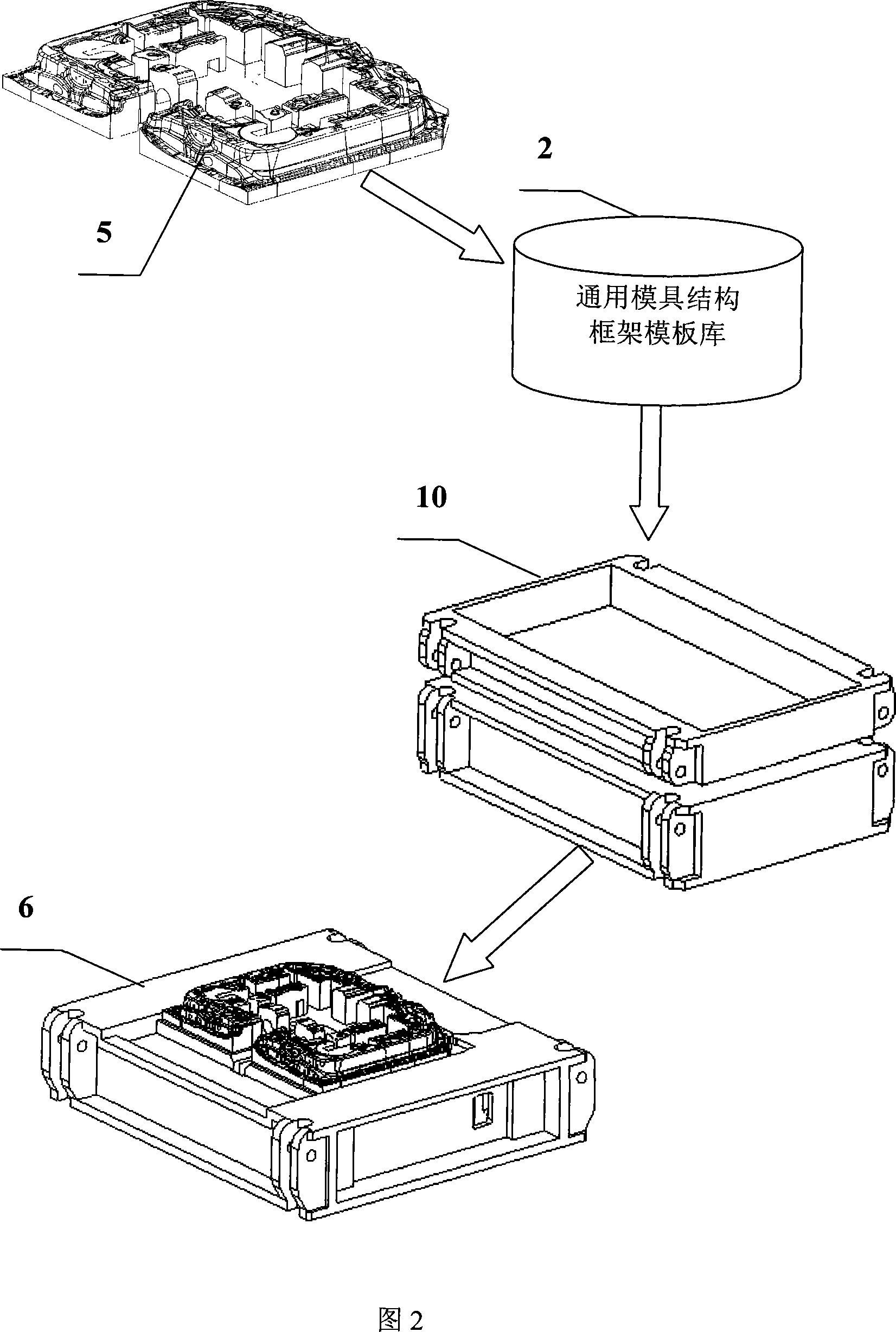

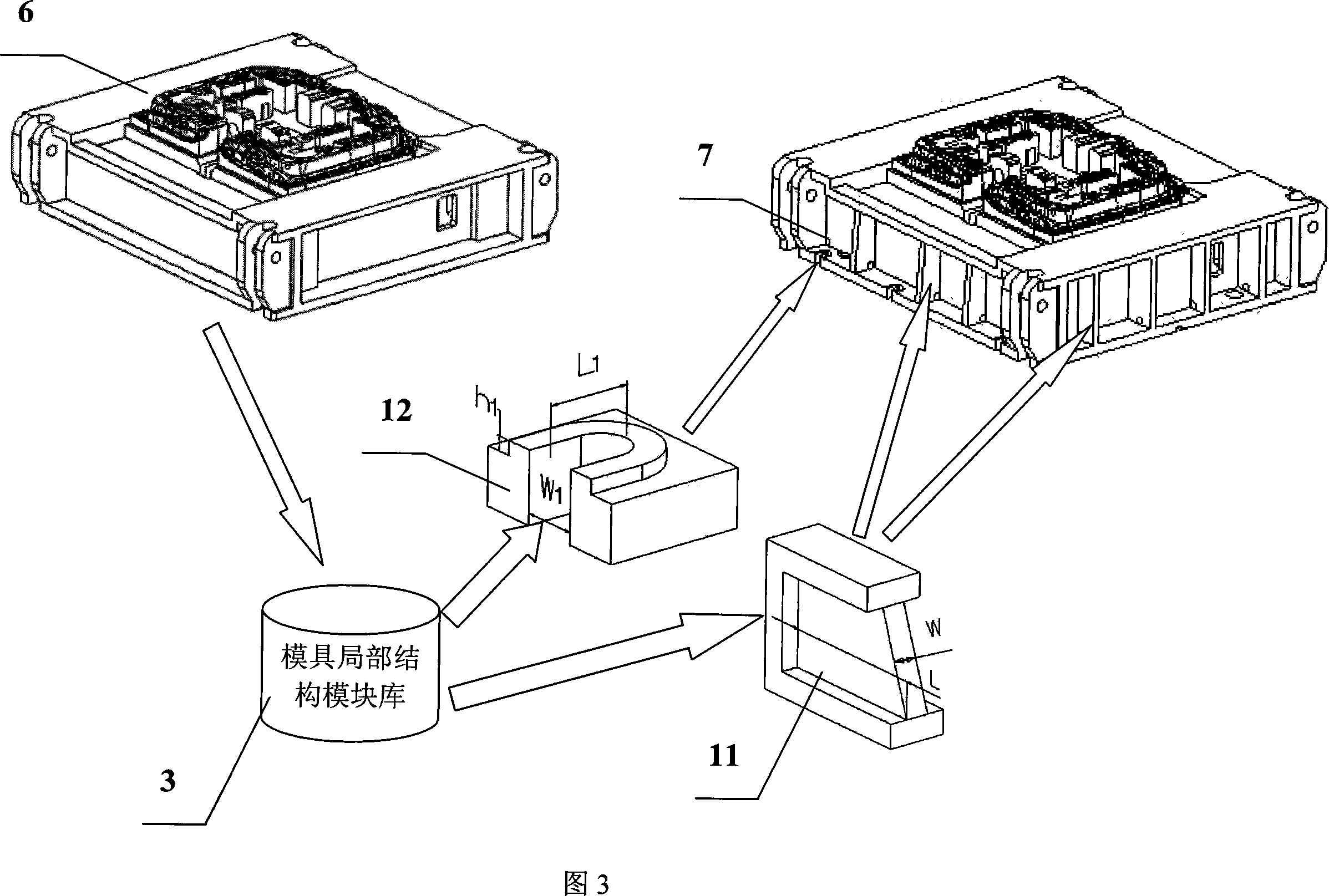

Method for quickly designing mould using computer

InactiveCN101192250AEasy to useEfficient use ofSpecial data processing applicationsSoftware engineeringWork content

The invention discloses a computer-based fast design mould method which comprises the following steps of: acquisition of customer requiring data, date processing, establishing integrated template database, and encapsulating the establishing integrated template database on network server; finishing the structure design of working contents according to technology contents; determining the framework design of mould structure according to working contents; calling the mould structure from the partial mould structure module database and thus accomplishing the partial structure design of mould; calling parts from standard part integrating warehouse, adjusting specification size, extracting the feature of installing structure and thus accomplishing mould design that meets the design requirements. The invention has the advantages that the integrated template database is simple and rapid to learn and use and is suitable for mould designers of different levels, the complicated mould structures become simpler, more standard, more intelligent, and the design regulations are integrated into template database, thereby the much more difficult mould structure design is capable of being accomplished much faster and better, the design period is shortened by 30 percent and design errors are avoided.

Owner:TIANJIN MOTOR DIES

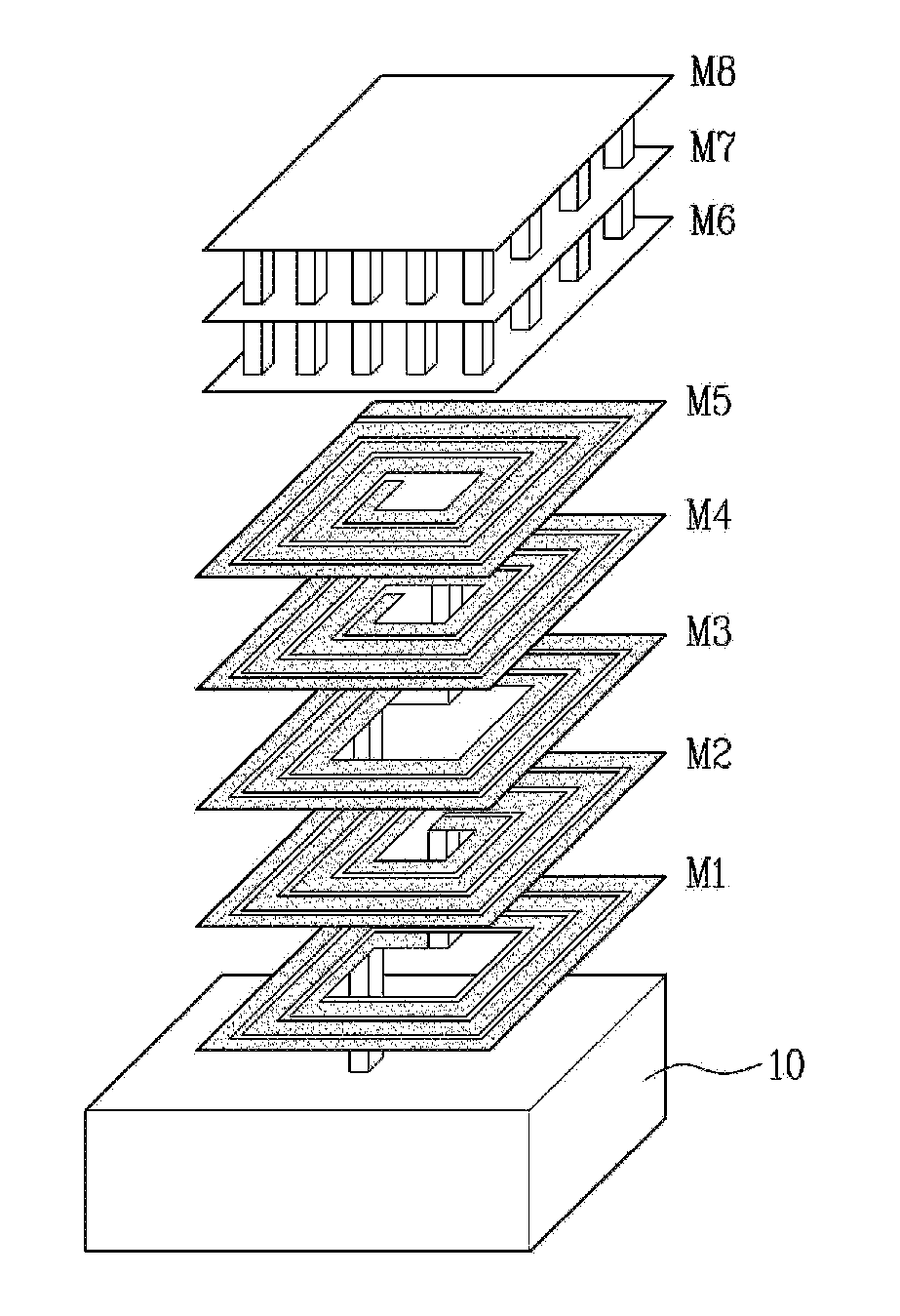

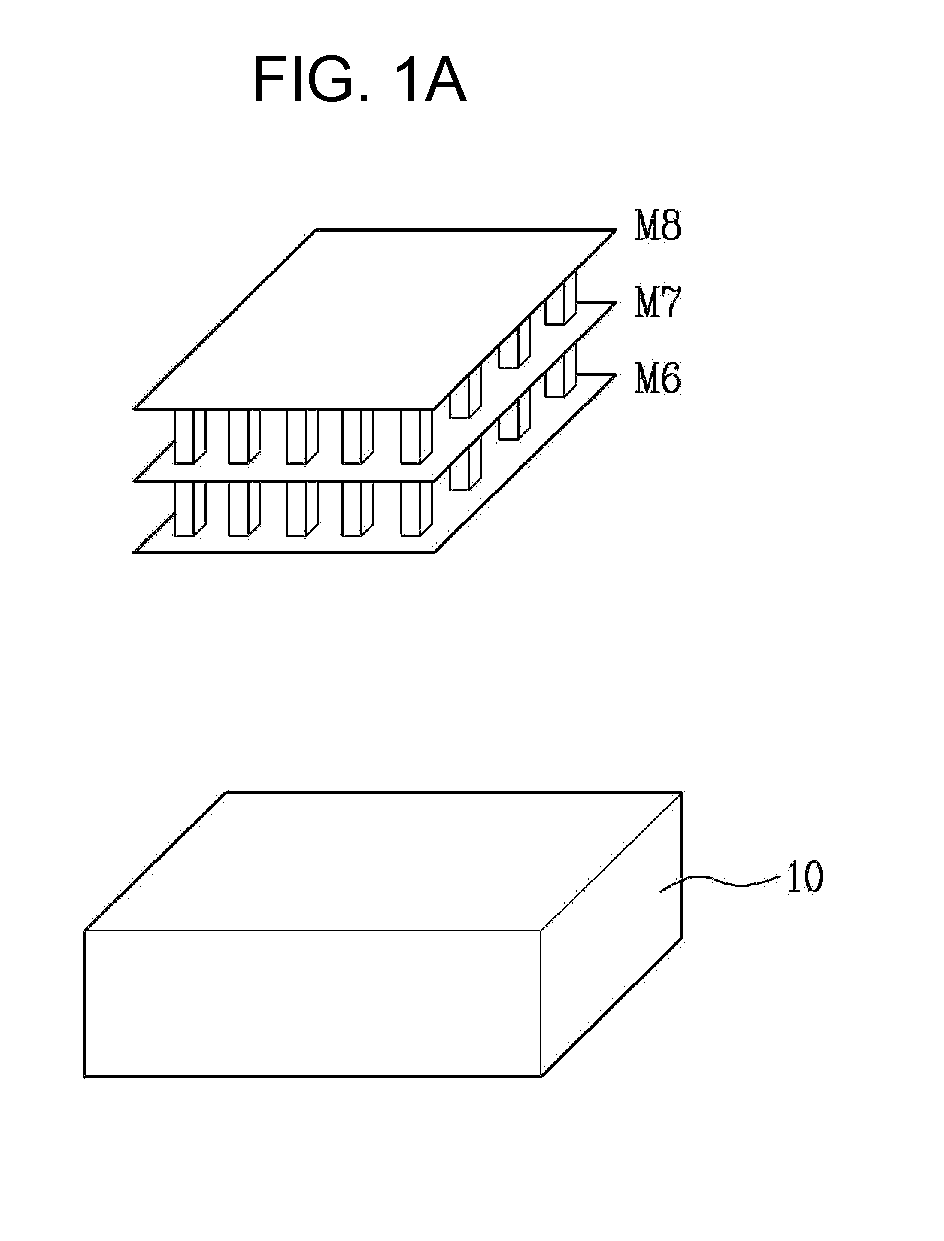

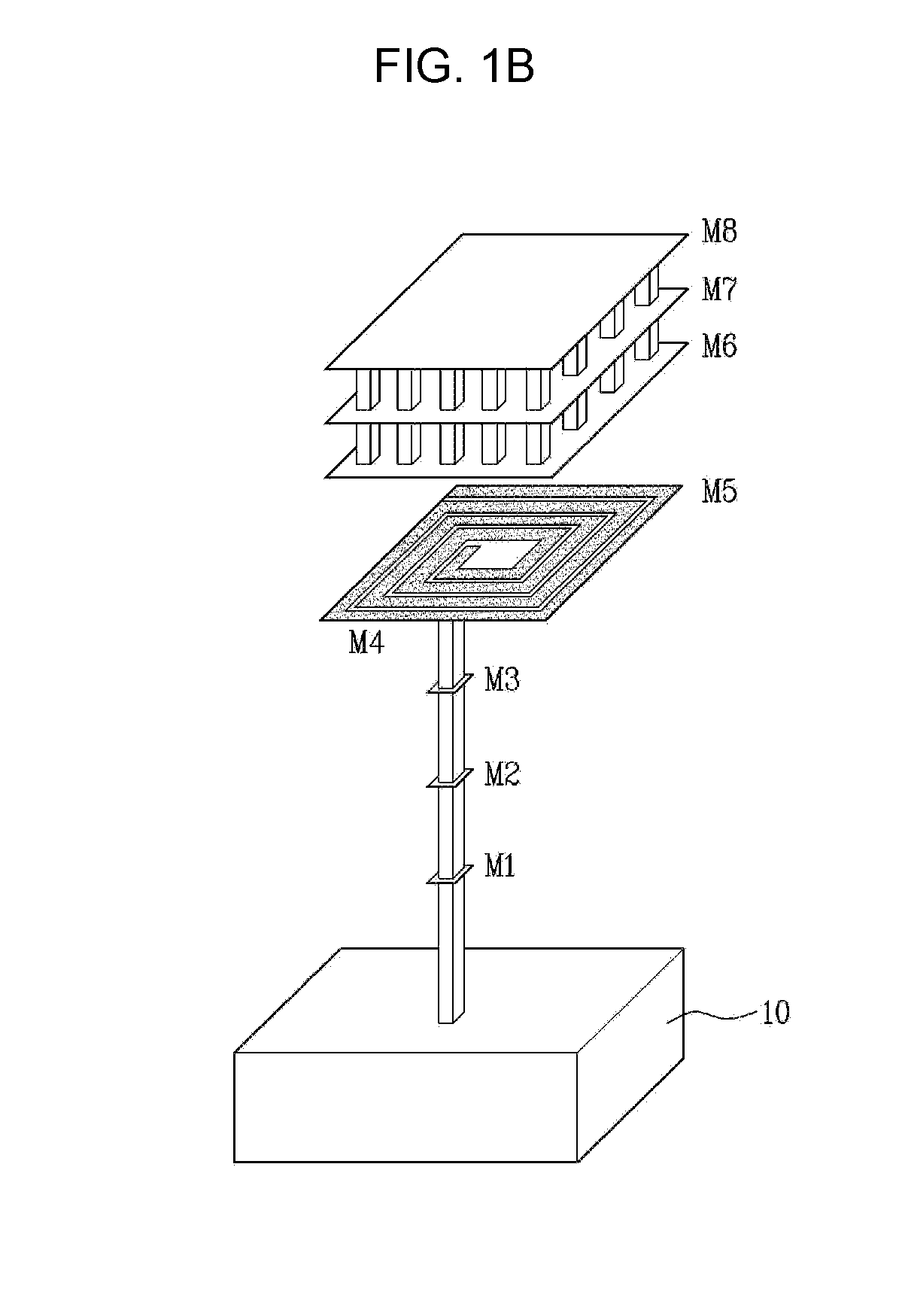

Pad in Semicondcutor Device and Fabricating Method Thereof

InactiveUS20090168293A1Reduces total parasitic capacitance componentMinimizing design error(s)Multiple fixed capacitorsSemiconductor/solid-state device detailsResonanceParasitic capacitance

A pad in a semiconductor device and fabricating method thereof are disclosed. The pad includes an uppermost metal layer first to Nth intermediate metal layers, wherein capacitors configured or formed by the uppermost metal layer and the first to Nth intermediate metal layers are serially connected. Accordingly, the pad reduces total parasitic capacitance components by connecting MIM type capacitors in series, and not necessarily overlapping with each other, thereby minimizing design errors attributed to the pad by reducing parasitic factors generated from the integrated circuit design. The pad may also minimize capacitance attributed to resonance at a specific frequency. Moreover, the pad avoids affecting an adjacent pad or circuit without additional processing, despite maintaining the above-mentioned effects, thereby reducing cost.

Owner:DSS TECH MANAGEMENT

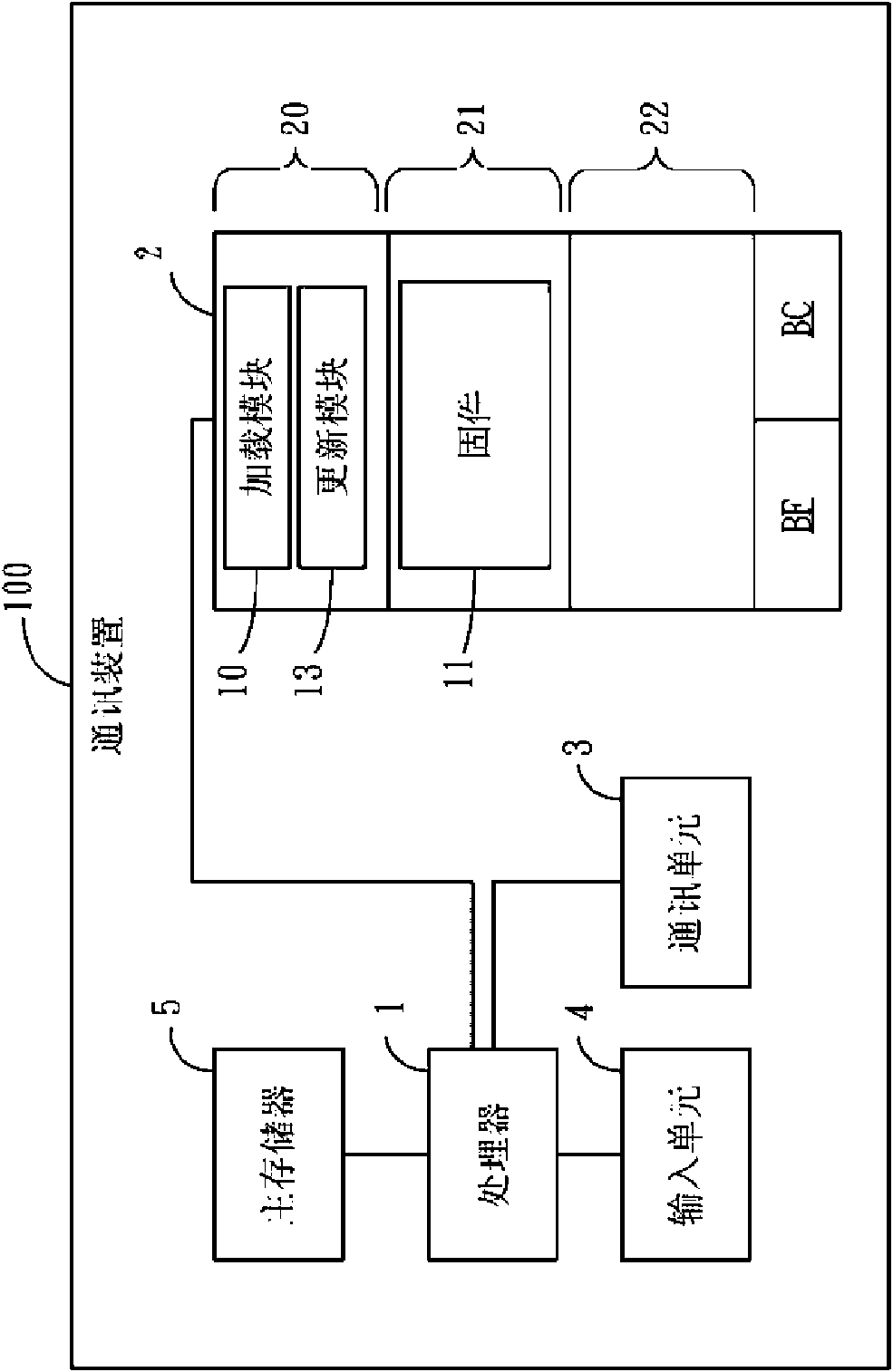

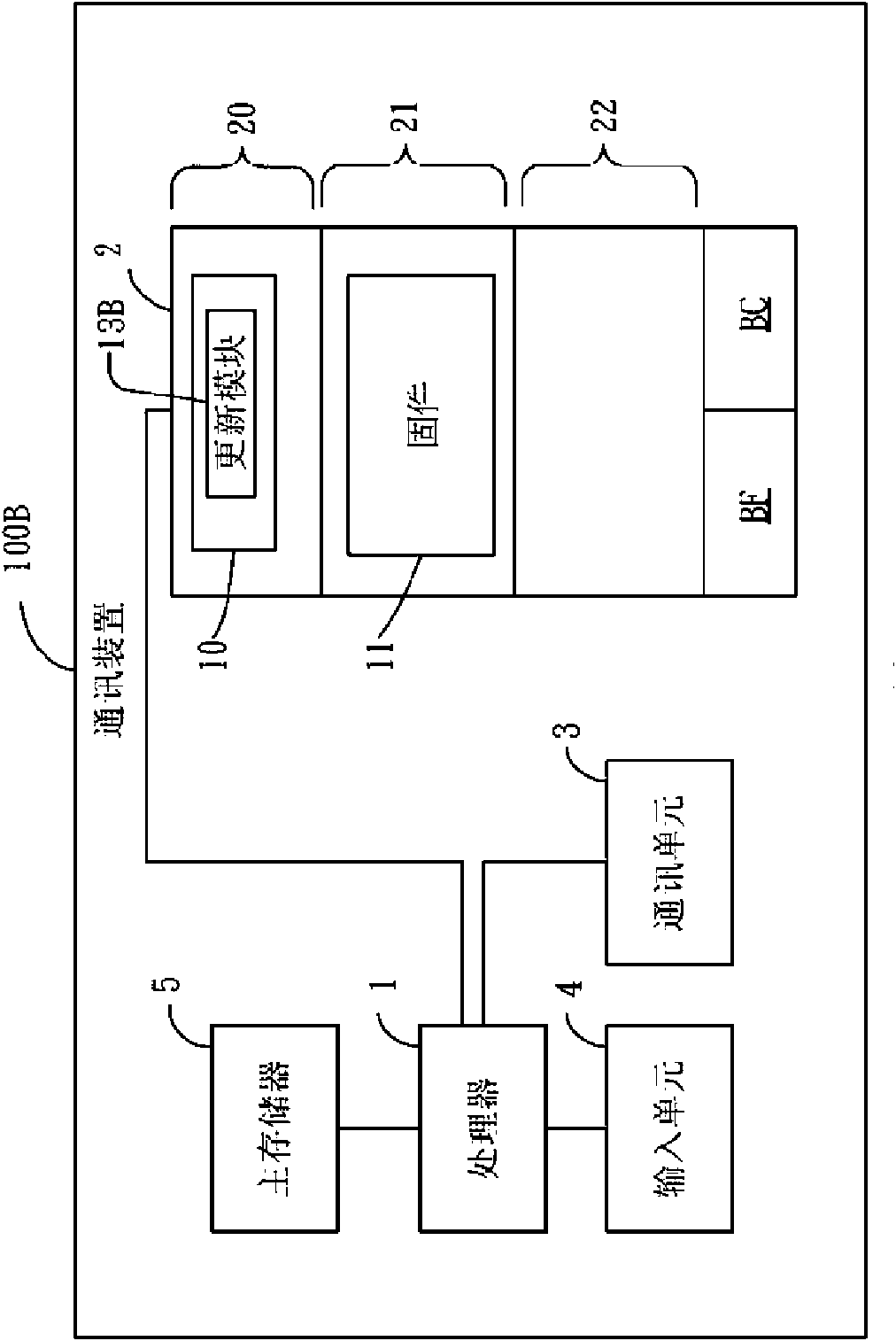

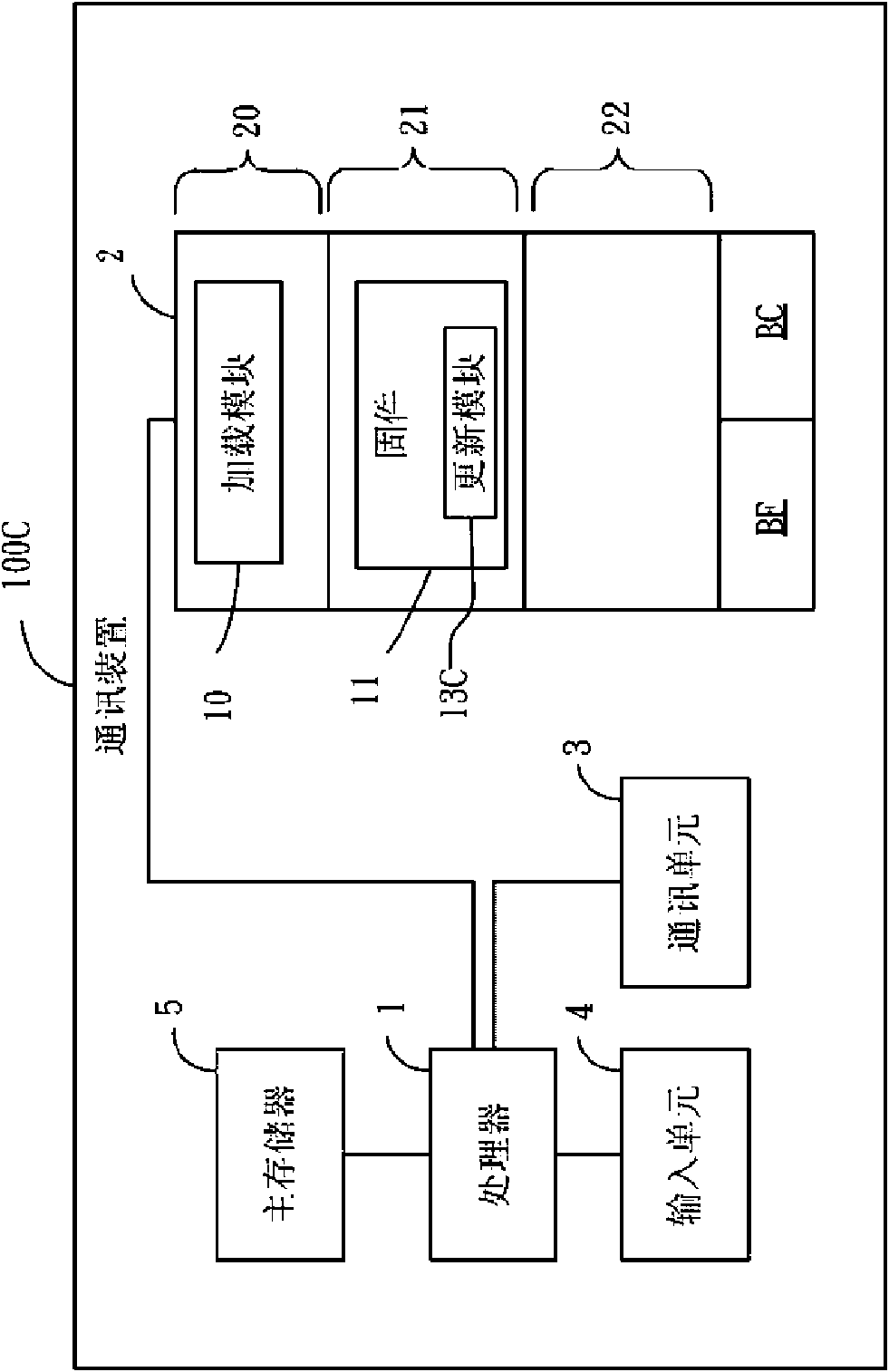

Communication device and method for updating firmware thereof

InactiveCN101526903AAvoid boot problemsTelevision system detailsColor television detailsFirmware versionProficiency testing

The invention relates to a method for updating firmware, which is executed in a device with a non-volatile memory, wherein the original firmware of the device is stored in a first region in the memory. Firstly, new firmware is obtained and stored in a second region in the memory. When the firmware storage is finished, the capability of start-up is tested. The test for the capability of start-up also comprises the steps: before judging whether the new firmware can pass the test or not, using a flag to designate another firmware for the start-up of the device besides the new firmware, responding to the start-up action of the device, loading and operating the new firmware, judging whether the new firmware passes the test for the capability of start-up or not, if the new firmware can operate and the device conforms to preset conditions, changing the value of the flag, designating the new firmware for next start-up, and maintaining the value of the flag if the new firmware does not pass the test for the capability of start-up. The method for updating firmware can avoid the problem of start-up caused by firmware version or design errors.

Owner:NANNING FUGUI PRECISION IND CO LTD

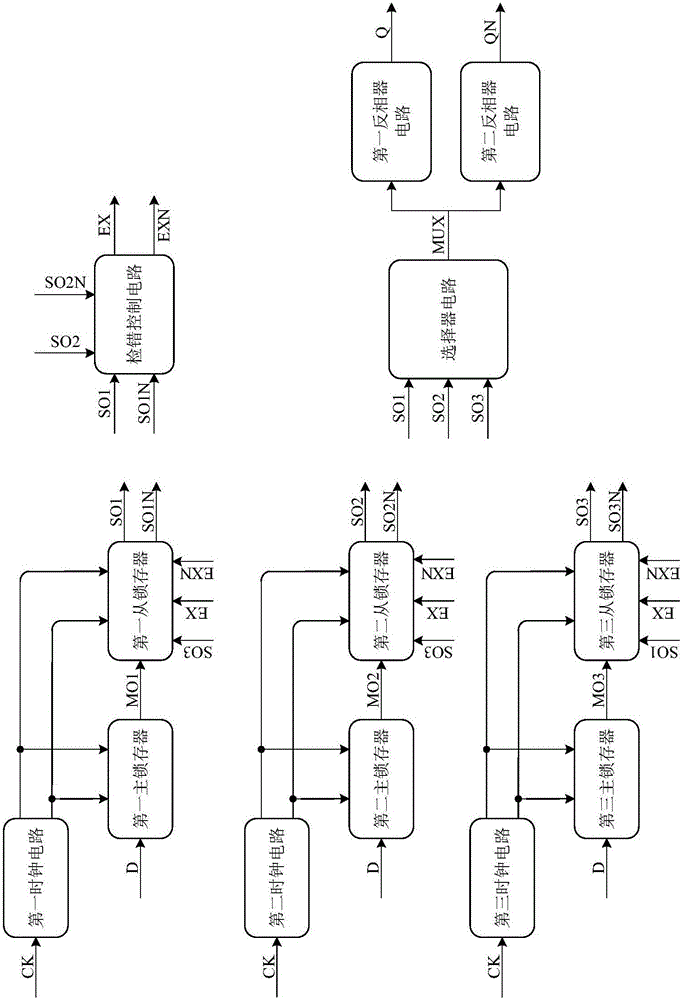

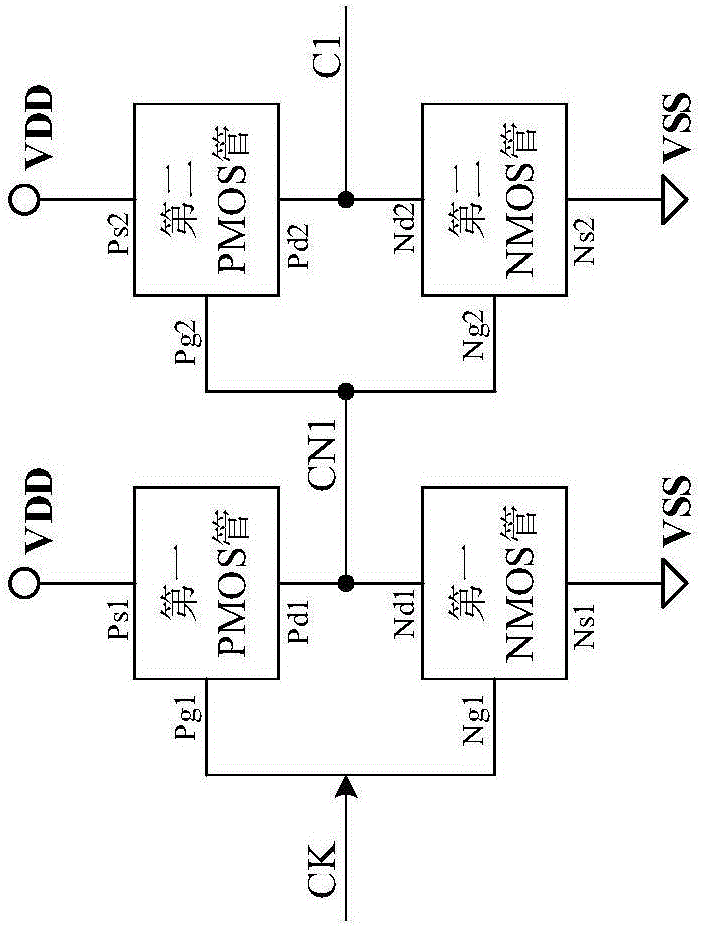

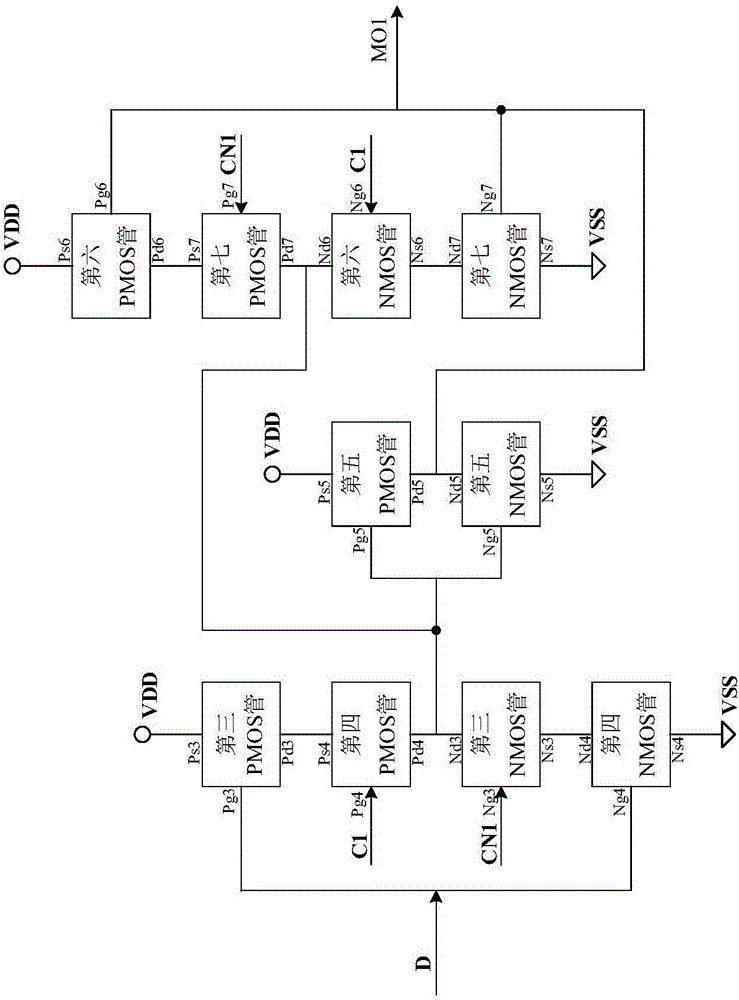

Triplication redundancy D trigger capable of realizing self error detection and single event upset prevention

ActiveCN105790734AAvoid flippingExcellent turning abilityElectric pulse generatorSingle event upsetControl circuit

The invention discloses a triplication redundancy D trigger capable of realizing self error detection and single event upset prevention. The trigger comprises a first clock circuit, a first main latch register, a first secondary latch register, a second clock circuit, a second main latch register, a second secondary latch register, a third clock circuit, a third main latch register, a third secondary latch register, a selector circuit, a first inverter circuit, a second inverter circuit and an error detection control circuit. The trigger is on the basis of a traditional reinforced triplication redundancy D trigger, output of three basic triggers in the triplication redundancy structure is controlled through the designed error detection control circuit, that correct output can be determined by a selector at any time is guaranteed; when output upset occurs in one of the three basic triggers, the one with output upset is instantly recovered through the error detection control circuit, upset accumulation can be avoided, and single event upset caused upset accumulation can be avoided, and single event upset prevention capability is further improved.

Owner:NAT UNIV OF DEFENSE TECH

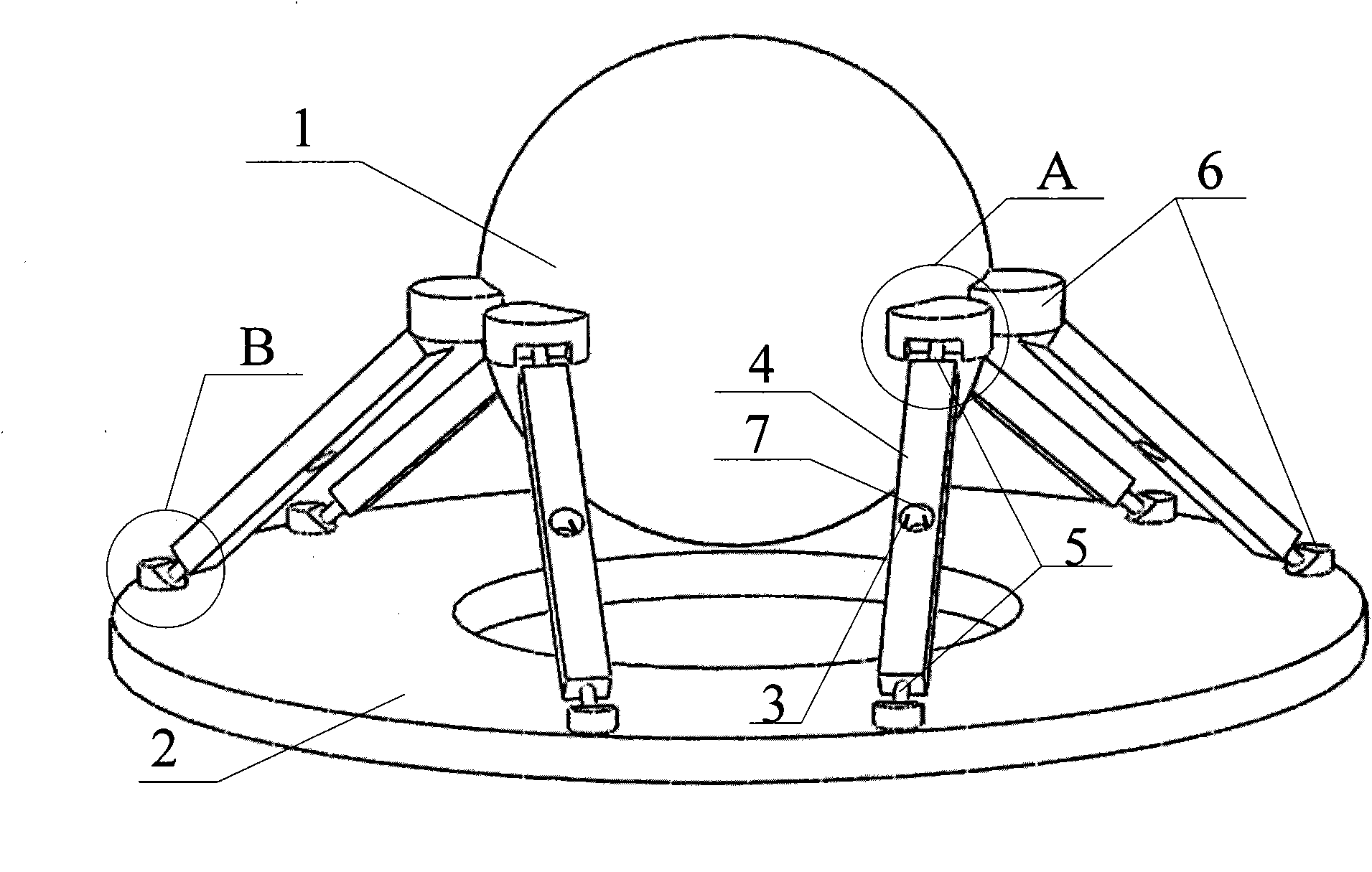

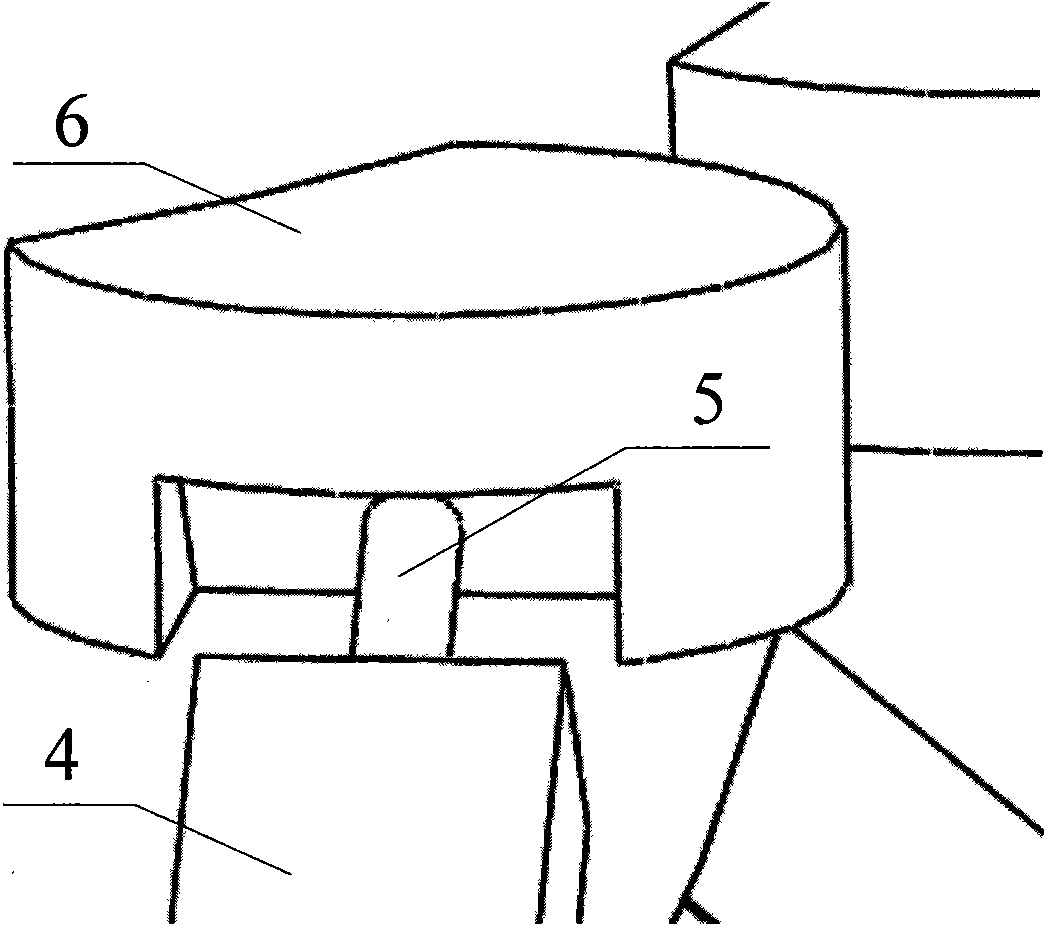

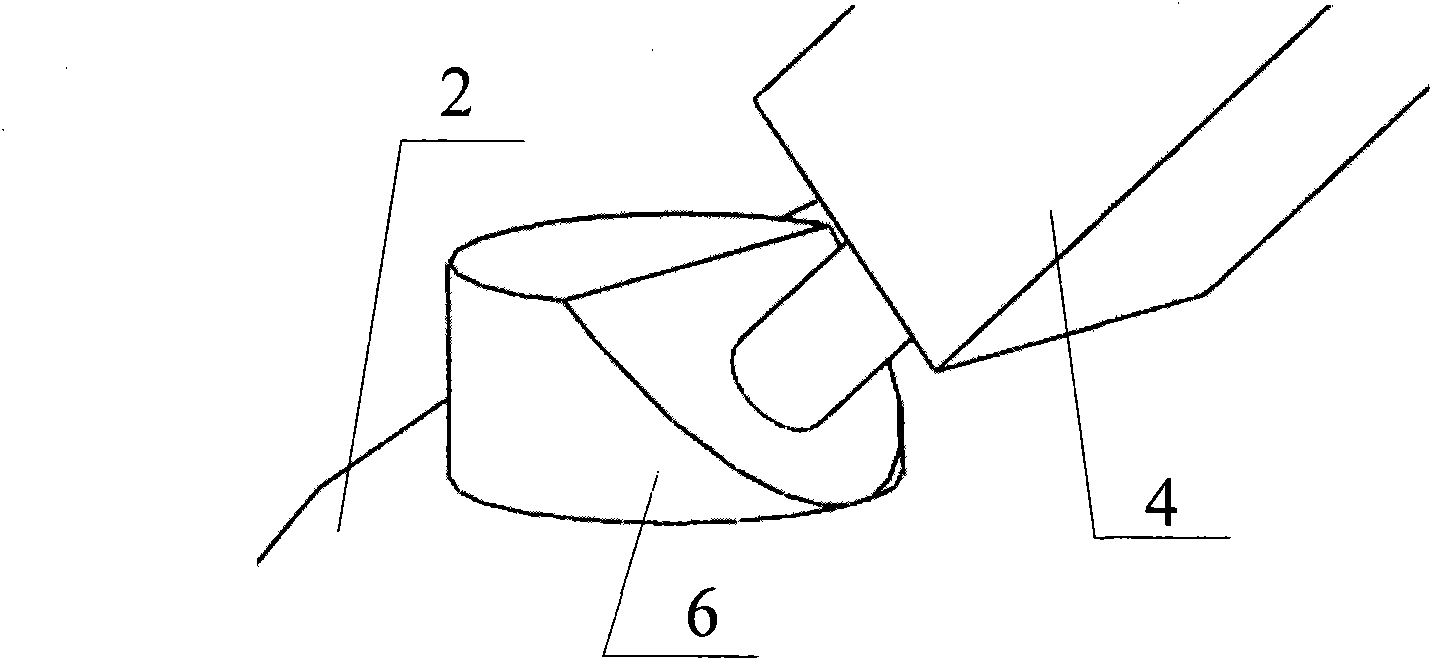

Six-dimensional acceleration transducer

InactiveCN101858932AConsistent Entity ModelConsistent theoretical modelAcceleration measurement using interia forcesAcceleration measurement in multiple dimensionsInertial massMaximum diameter

The invention relates to a six-dimensional acceleration transducer, comprising an inertial mass ball platform, a lower platform, a paster and six branched chains which are divided into three groups. The connecting points of the three groups of branched chains and the inertial mass ball platform are all located on the horizontal circumference with the largest diameter of the inertial mass ball platform and are distributed evenly; the connecting points of the three groups of branched chains and the lower platform are located on the same circumference and are distributed evenly; each branched chain consists of an elastic connecting rod and cylindric hinges arranged at the two ends of the elastic connecting rod; the cylindric hinges and the elastic connecting rod are at the same axial lead; and the inertial mass ball platform, the lower platform, the six branched chains and a boss are processed in an integral manner, which is characterized in that a through hole is arranged at each elastic connecting rod, the axial lead of the hole is vertical to the lateral surface of a circular truncated cone on which the six elastic connecting rods are located, two symmetric pasters are arranged corresponding to each hole, and each paster is adhered on the inner wall of the hole along the axial lead direction of the elastic connecting rod. The invention has the advantages of small design error, good dynamic properties, rapid response and high precision.

Owner:SHANDONG UNIV OF TECH

Aspheric myopia eyeglass

The invention discloses an aspheric myopia eyeglass, comprising a back surface and a front surface. Curved surfaces of the back surface and the front surface are all aspheric even number aspheric refracting surfaces. The even number aspheric refracting surface is determined by a function as below; optimized variables are increased by times, so as to reach higher imaging quality and larger thinning amount. In addition, the even number aspheric refracting surface guarantees holosymmetry of the eyeglass and is beneficial for processing and manufacture; detection is same as a general spherical eyeglass, and measurement of degrees of eyeglass will not be influnced. The front surface and the back surface employ completely opposite aspheric design, so that various design errors and processing errors can compensate mutually. The eyeglass has excellent stability, and will not cause uncomfortableness to first time wearer due to various errors. Therefore, the aspheric myopia eyeglass has advantages of thin thickness, light weight, good imaging quality and facility for processing, etc.

Owner:SUZHOU MASON OPTICAL CO LTD +1

Application of a relational database in integrated circuit design

Owner:ORACLE INT CORP

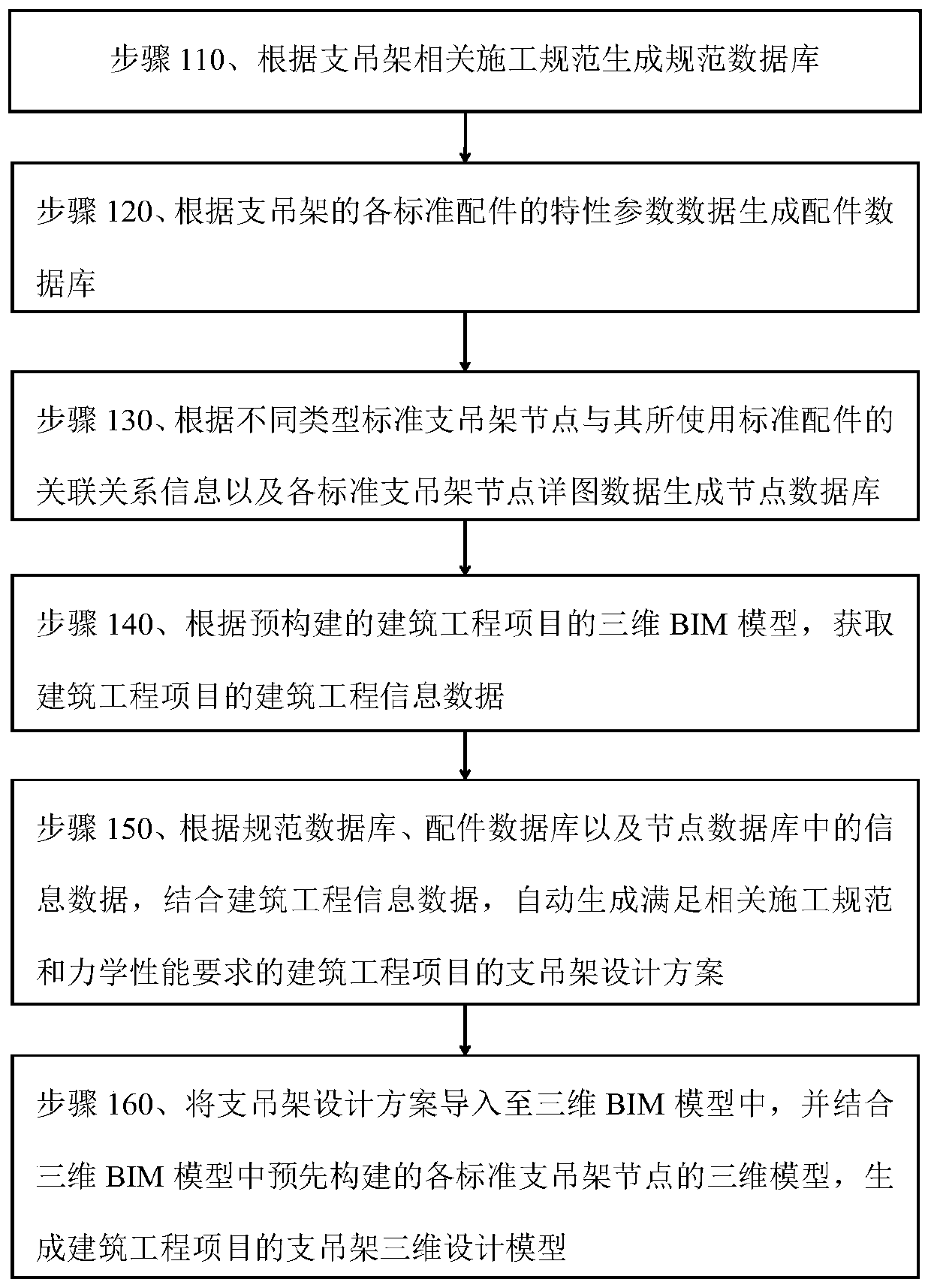

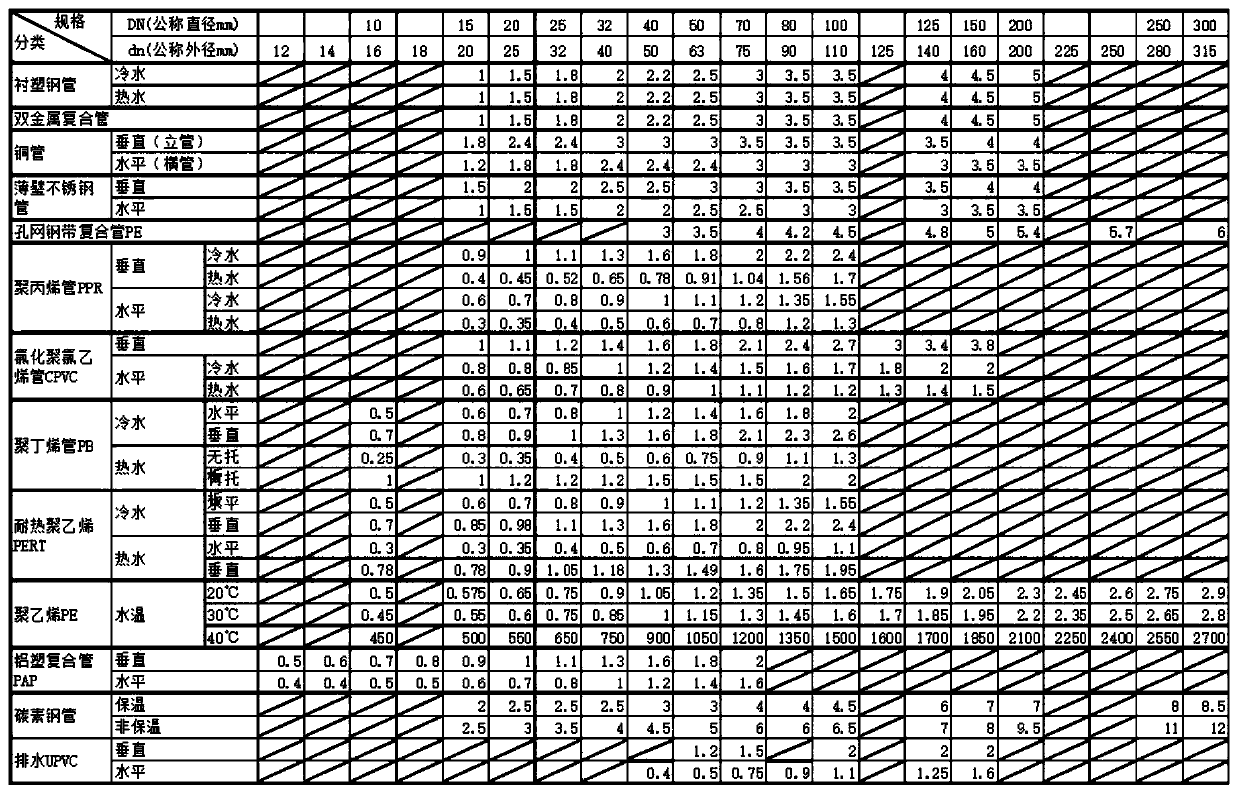

Method, device and system for automatically designing support and hangers based on three-dimensional BIM model

The embodiment of the invention discloses a method, device and system for automatically designing support and hangers based on a three-dimensional BIM model, and the method comprises the steps: obtaining the building engineering information data of a building engineering project according to the pre-built three-dimensional BIM model of the building engineering project; automatically generating a support hanger design scheme of the constructional engineering project according to the generated information data in the standard database, the accessory database and the node database in combinationwith the constructional engineering information data; and importing the support and hanger design scheme into the three-dimensional BIM model to generate a support and hanger three-dimensional designmodel of the constructional engineering project. The method is suitable for three-dimensional BIM model-based constructional engineering projects (each component has an information attribute and supports export). Compared with the traditional manual support hanger design, the method has the advantages that the efficiency is greatly improved, design errors caused by manual errors, faults and the like are greatly avoided, and repeated work of engineers is not needed.

Owner:莫亦科技(上海)有限公司