Patents

Literature

349 results about "Process error" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

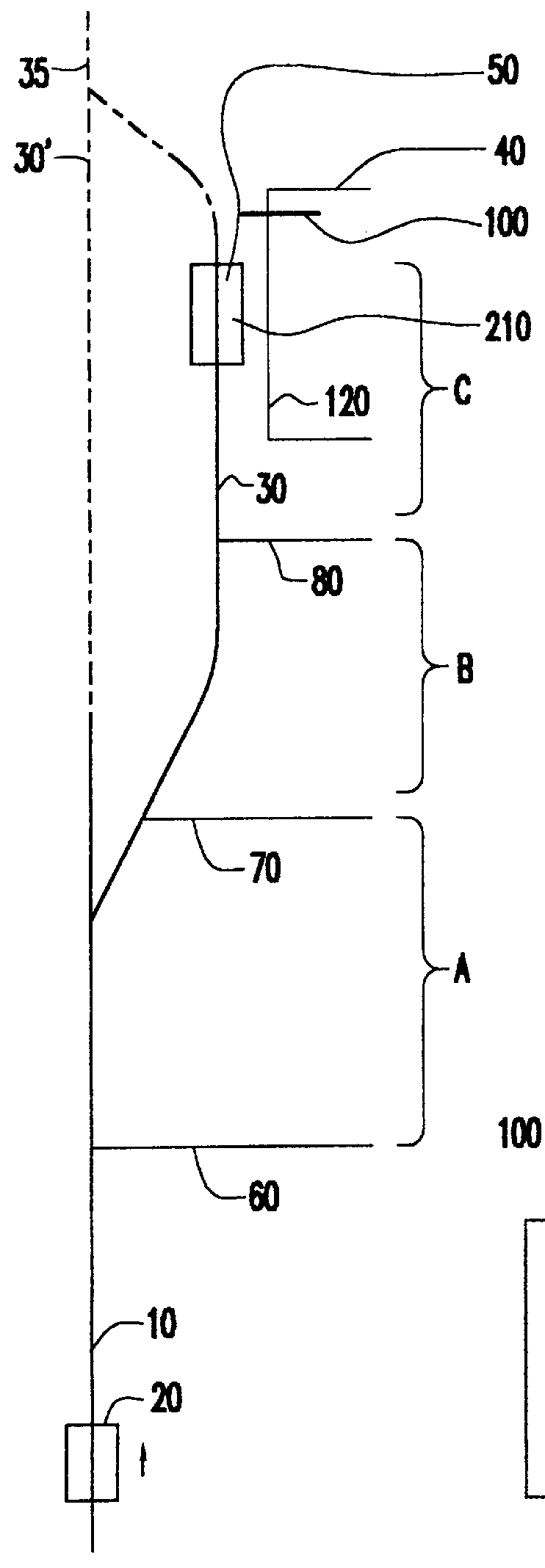

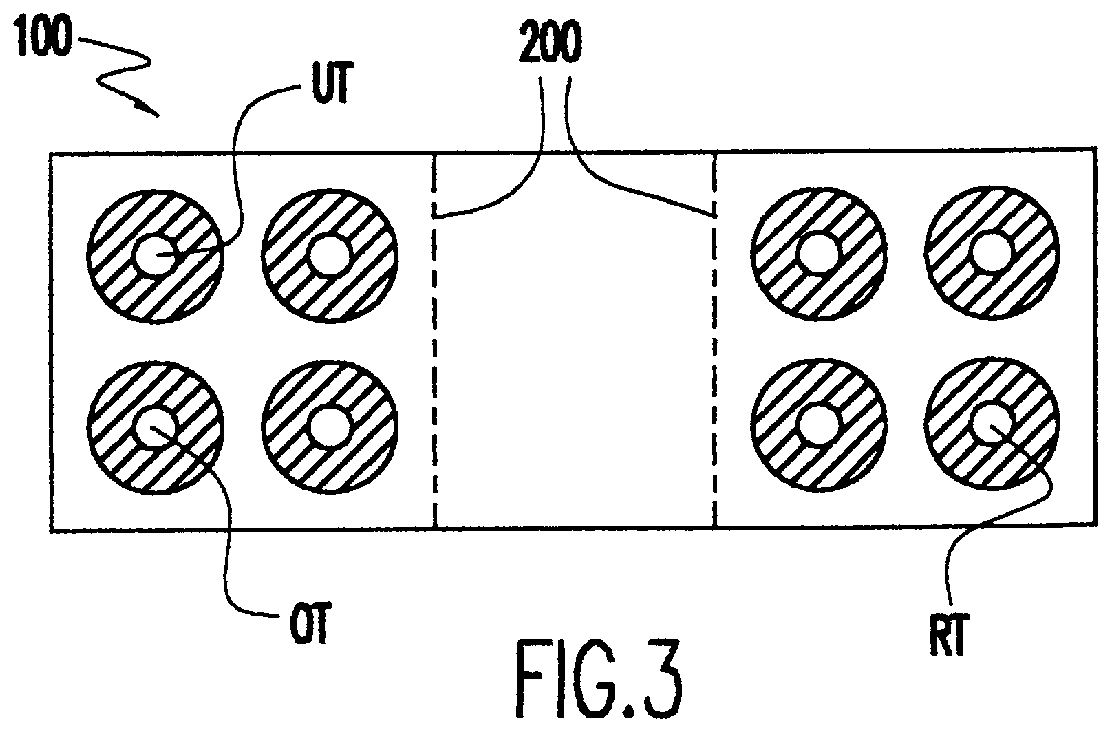

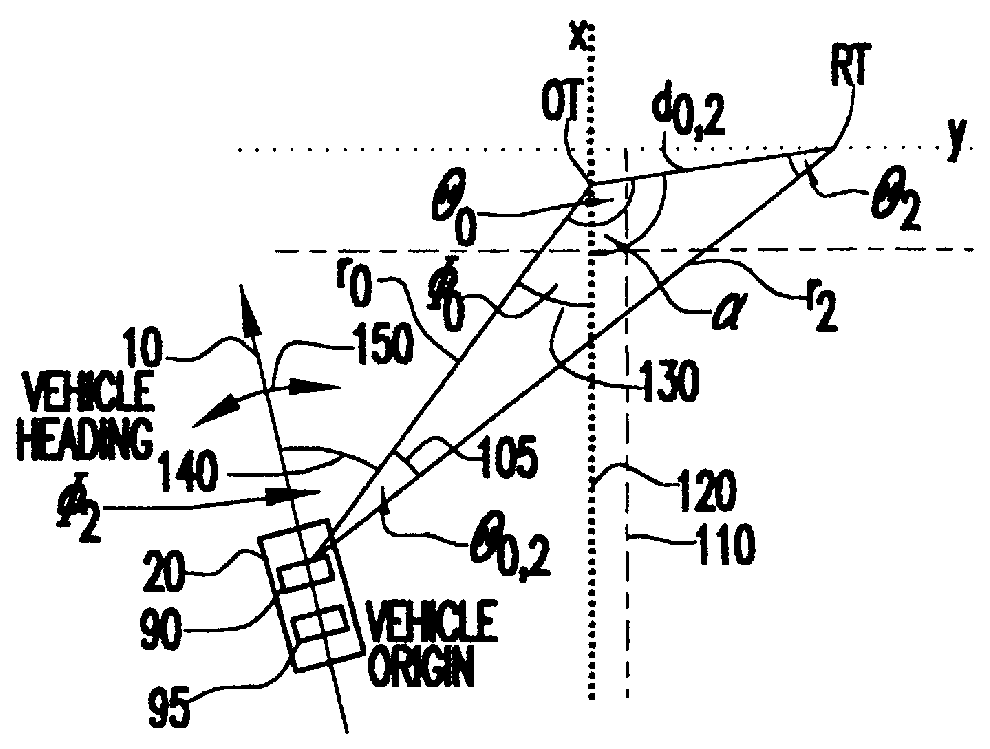

Vision based precision docking of vehicles

InactiveUS6078849ALong operationInstallation economyDirection finders using radio wavesDigital data processing detailsProcess errorVision based

A three phase control arrangement is employed after visual detection of a target at greater range than otherwise available. The first and last phases employ an optimization criterion for which errors do not vary with distance from a target; limiting the initial error and process error in an intermediate phase which controls approach trajectory to the intended docking location and yielding repeatable high accuracy docking. The three phase approach with different control criteria and control gain parameters makes feasible a docking maneuver that begins at a much greater range and potentially greater lateral separation from the destination than would otherwise be possible, while providing control of both the final location and final orientation of the vehicle. A preferred visual thresholding technique provides consistency of results over a wide range of illumination and contrast conditions while limiting the computation burden for target image acquisition and tracking.

Owner:LOCKHEED MARTIN CORP

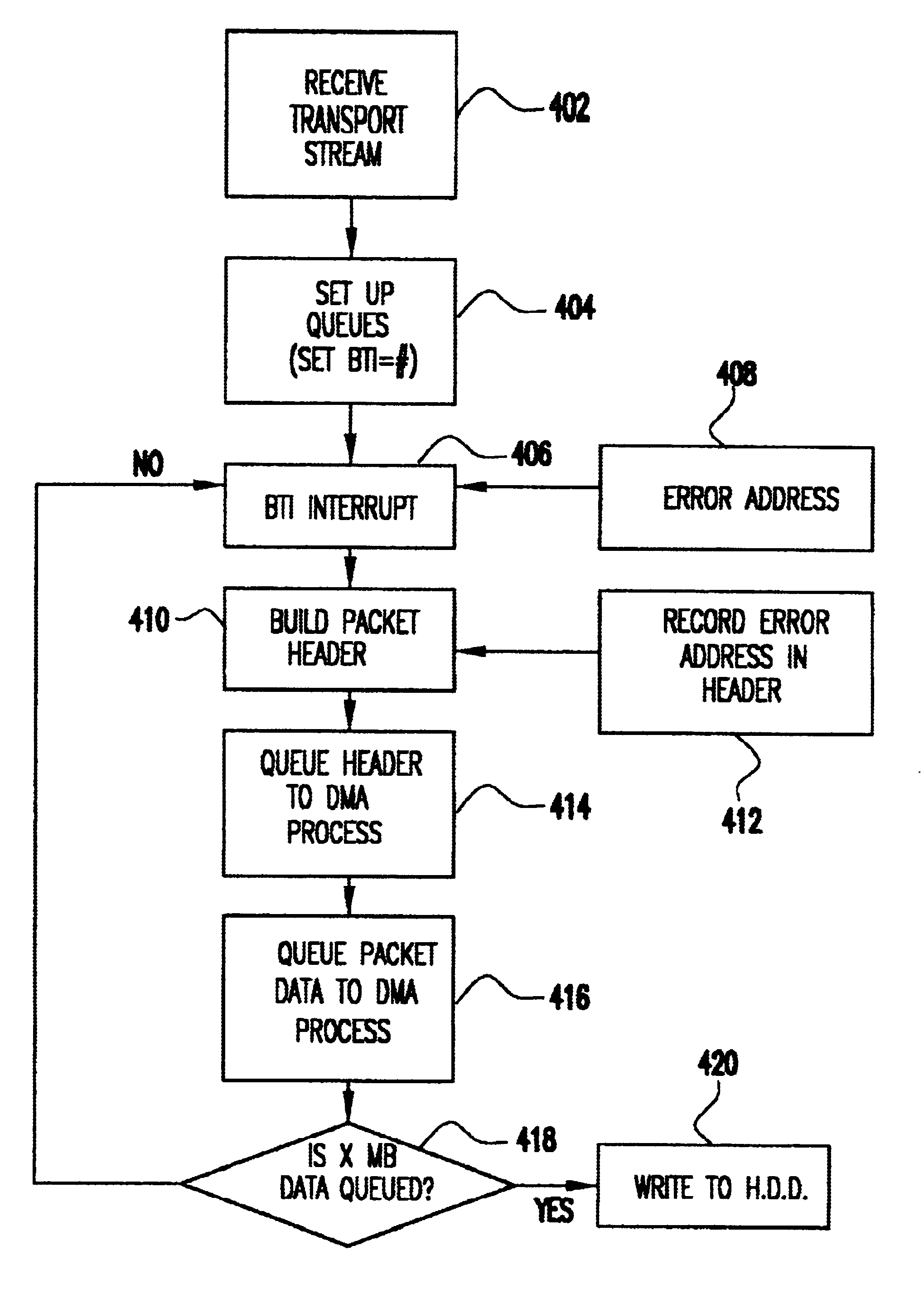

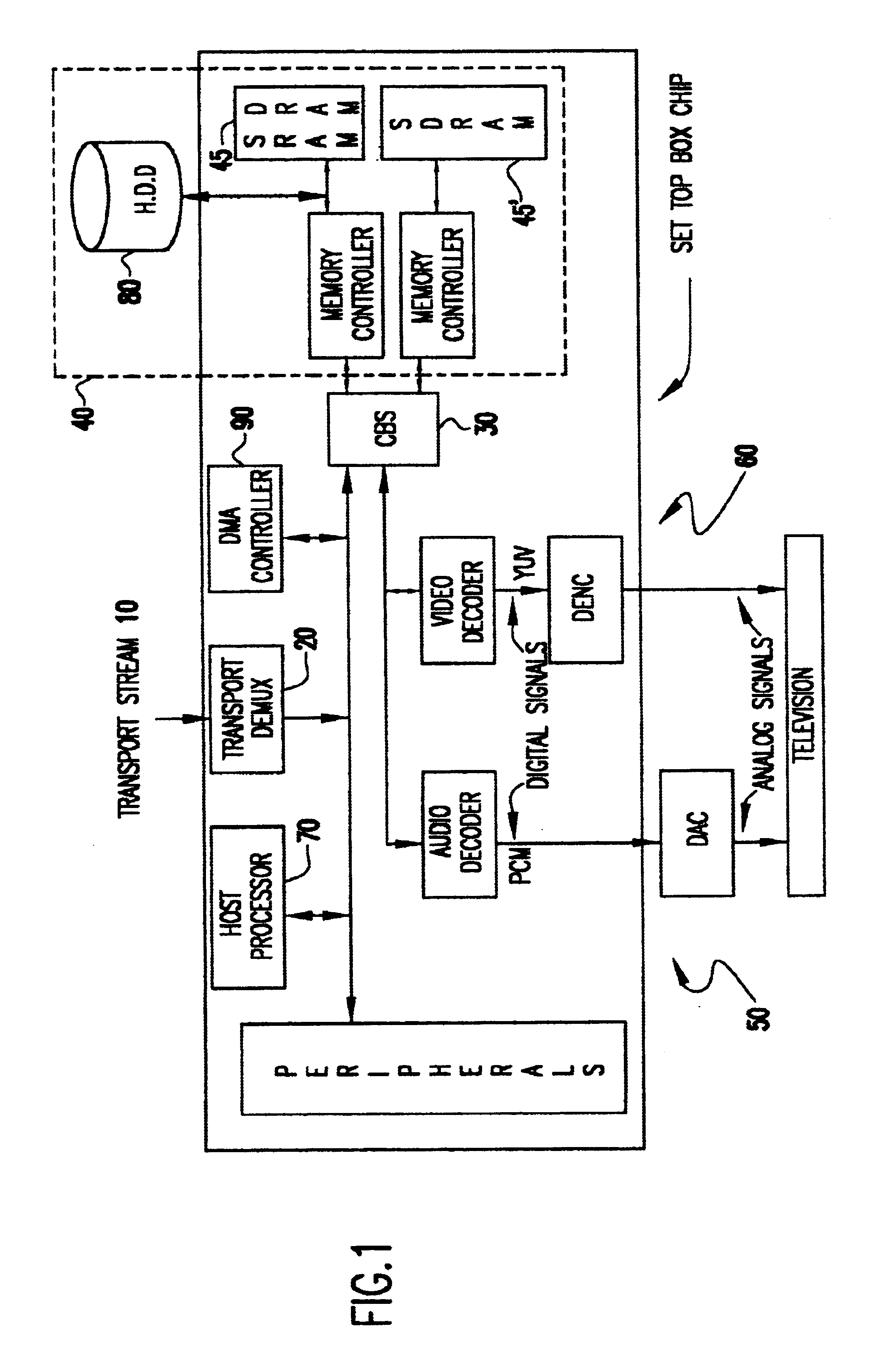

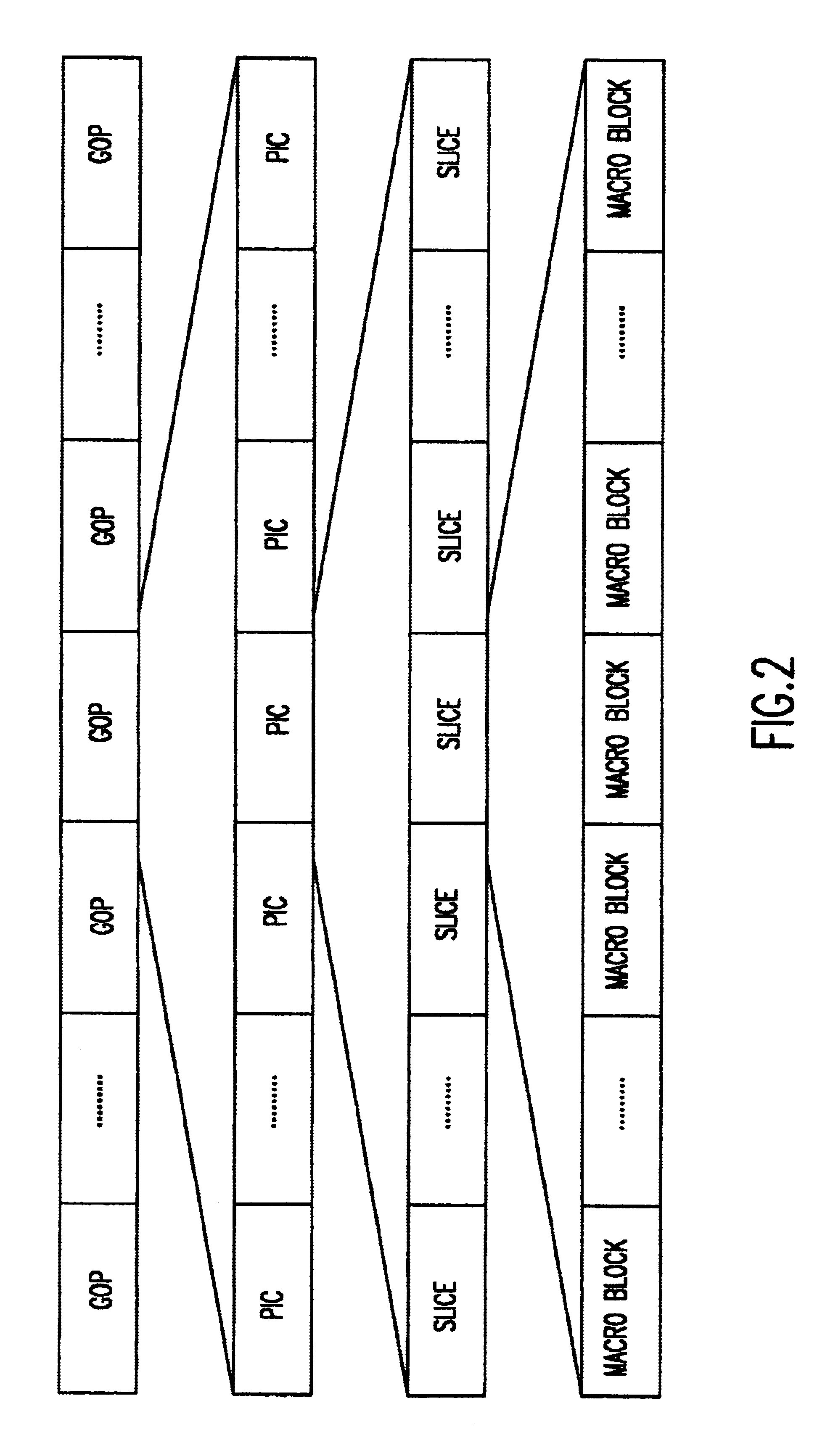

Processing errors in MPEG data as it is sent to a fixed storage device

InactiveUS6662329B1Easy to hideReduce number and severityError prevention/detection by using return channelTelevision system detailsMass storageData stream

Data corrupted or lost in transmission over a lossy digital transmission link is replaced and / or omitted from data presented in connection with storage to and read out from a mass storage device. Different procedures are used to conceal artifacts corresponding to errored data based upon valid data preceding and following the error in a data stream and a size of the error.

Owner:WISTRON CORP

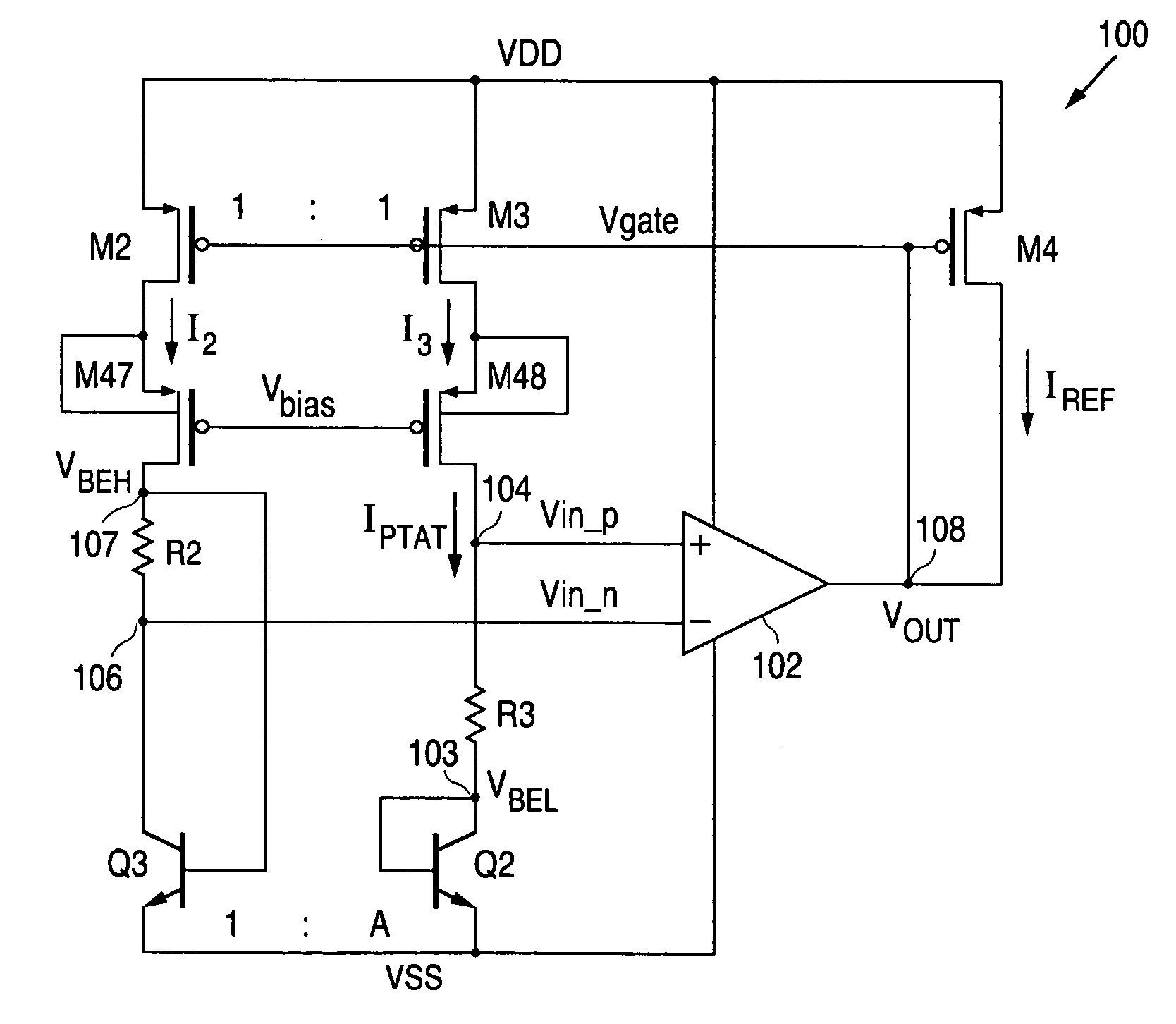

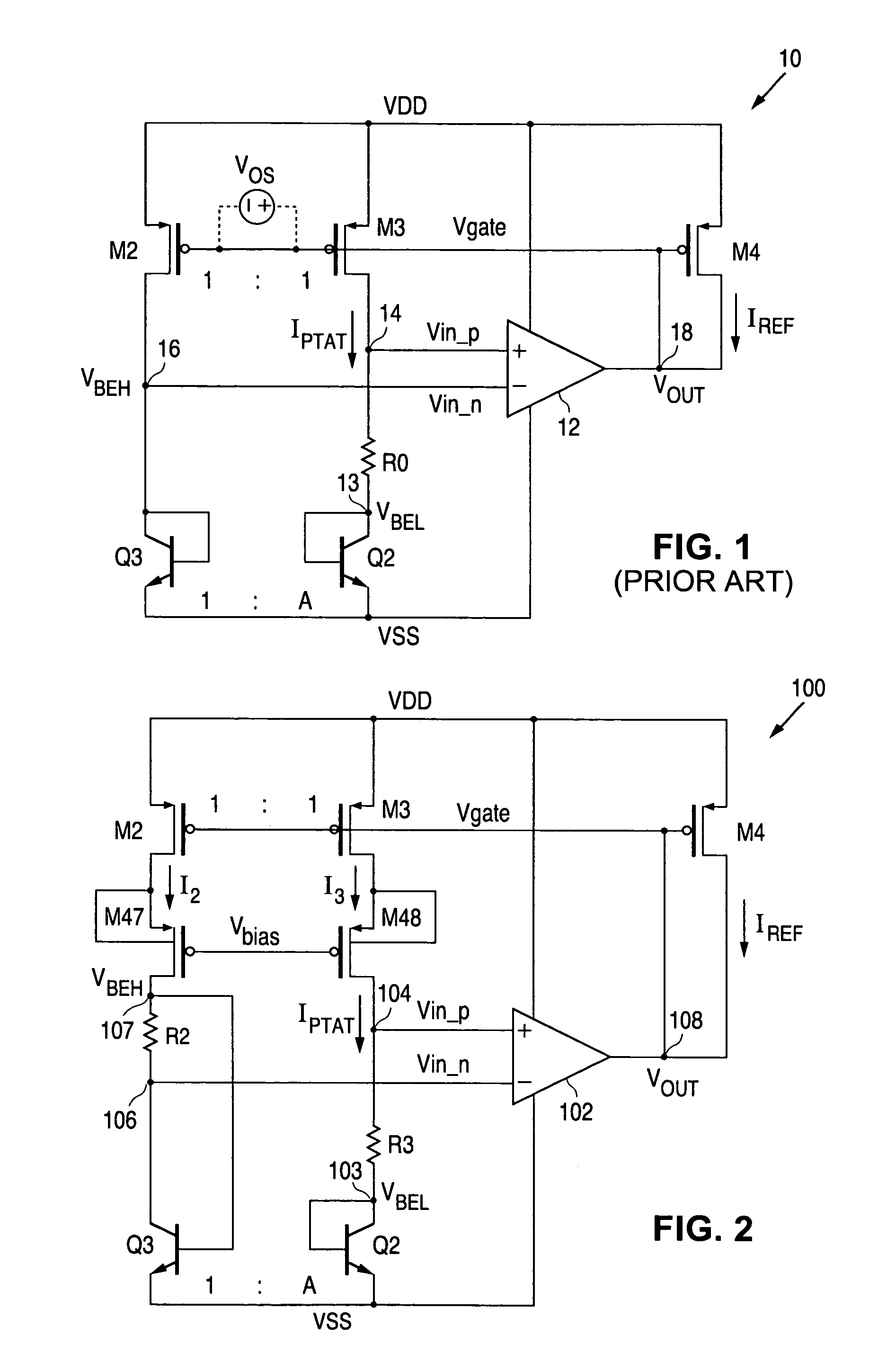

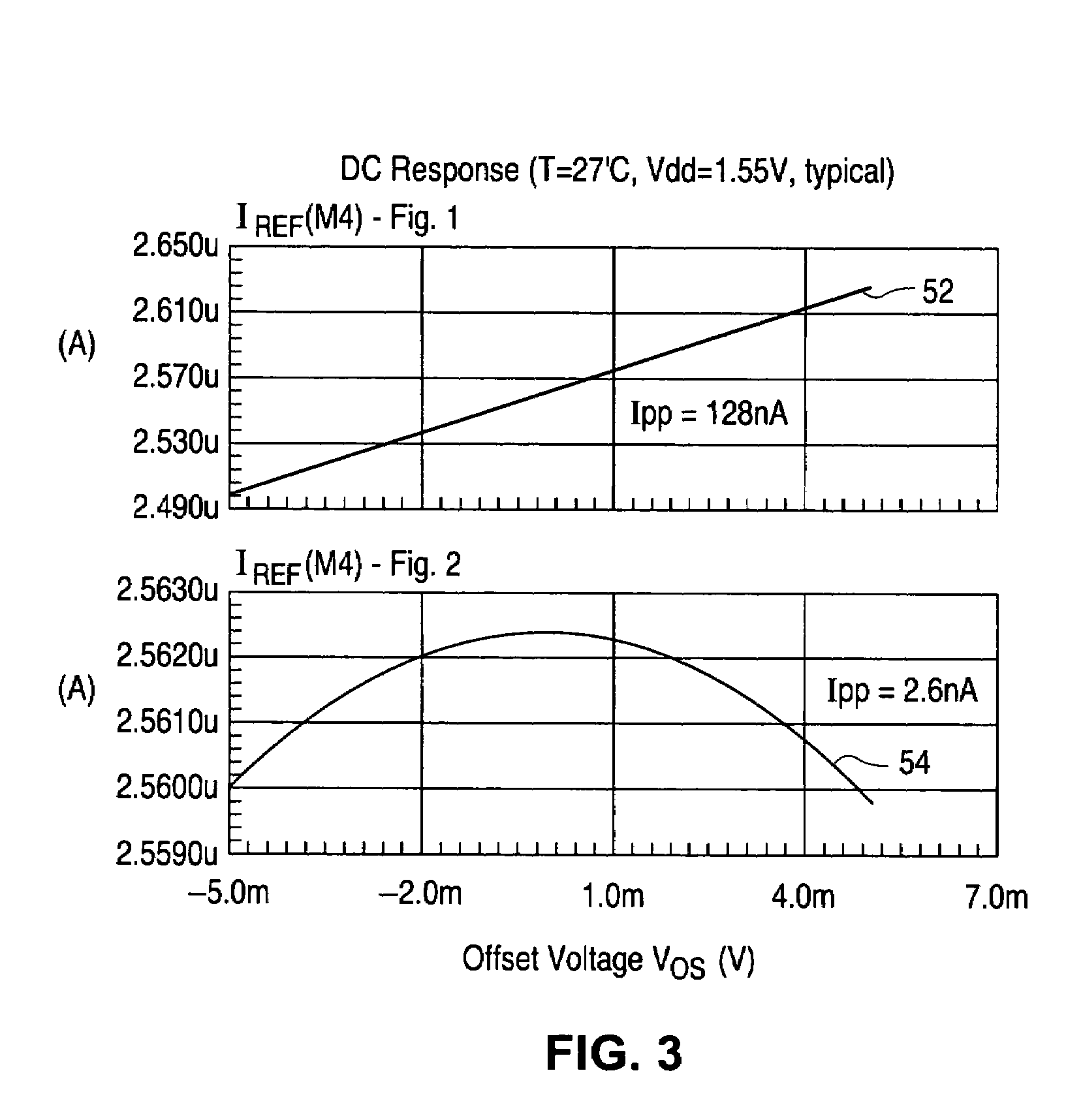

Self-regulating process-error trimmable PTAT current source

ActiveUS7236048B1Electronic switchingPulse generation by opto-electronic devicesElectrical resistance and conductanceProcess error

A current source for generating a PTAT current using two bipolar transistors with an 1:A emitter area ratio implements a split resistor architecture to cancel mismatch errors in the current mirror of the current source. In one embodiment, a first resistor is coupled to the unit area bipolar transistor and a second resistor is coupled to the A-ratio-area bipolar transistor. The first resistor has a resistance value indicative of the emitter resistance re of the bipolar transistors while the second resistor has a resistance value satisfying the equation re*(lnA−1). In another embodiment, an emitter area trim scheme is applied in a PTAT current source to cancel, in one trim operation, both bipolar transistor area mismatch error and sheet resistance variations. The emitter area trim scheme operates to modify the emitter area of the A-ratio-area bipolar transistor to select the best effective emitter area that provides the most accurate PTAT current.

Owner:NAT SEMICON CORP

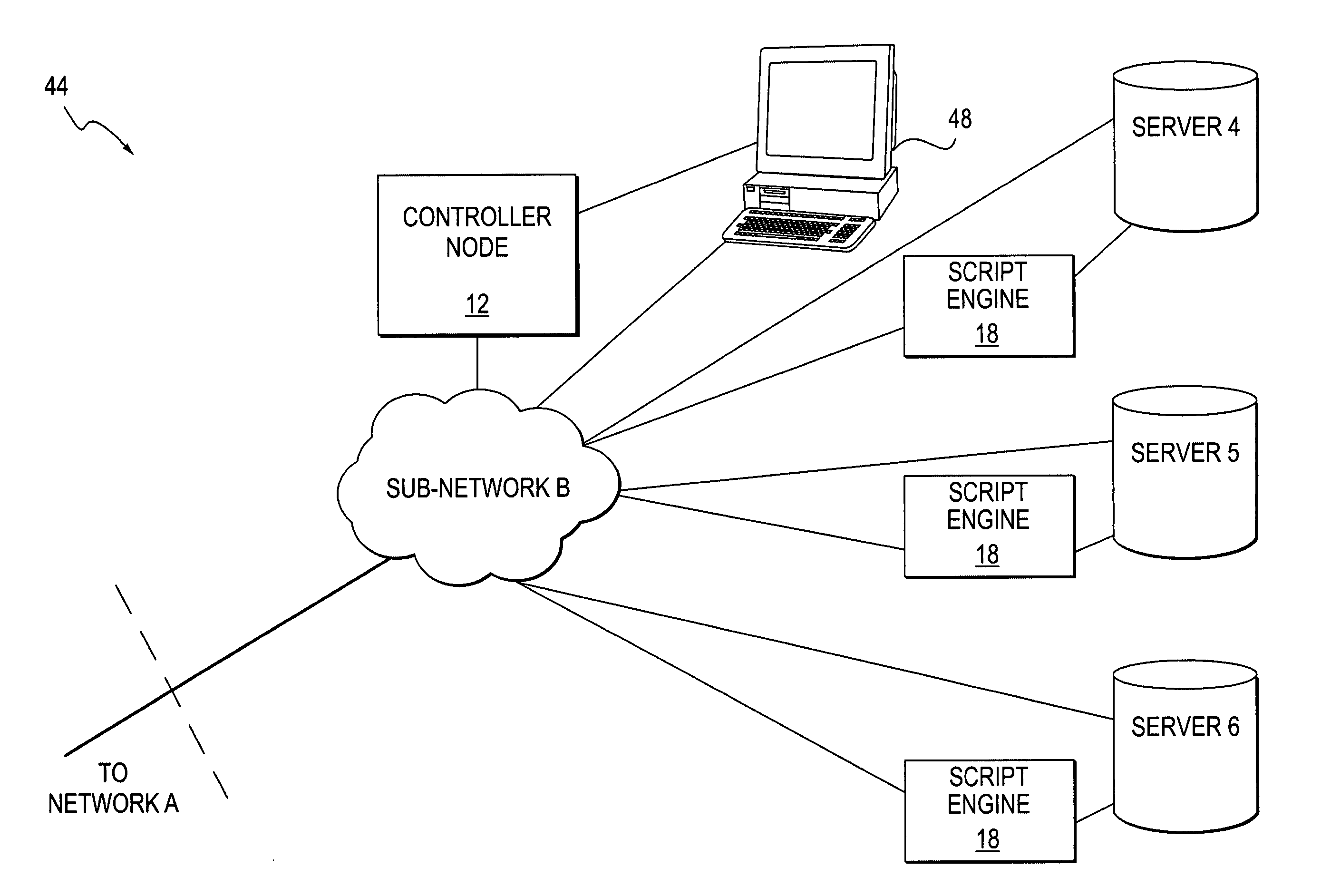

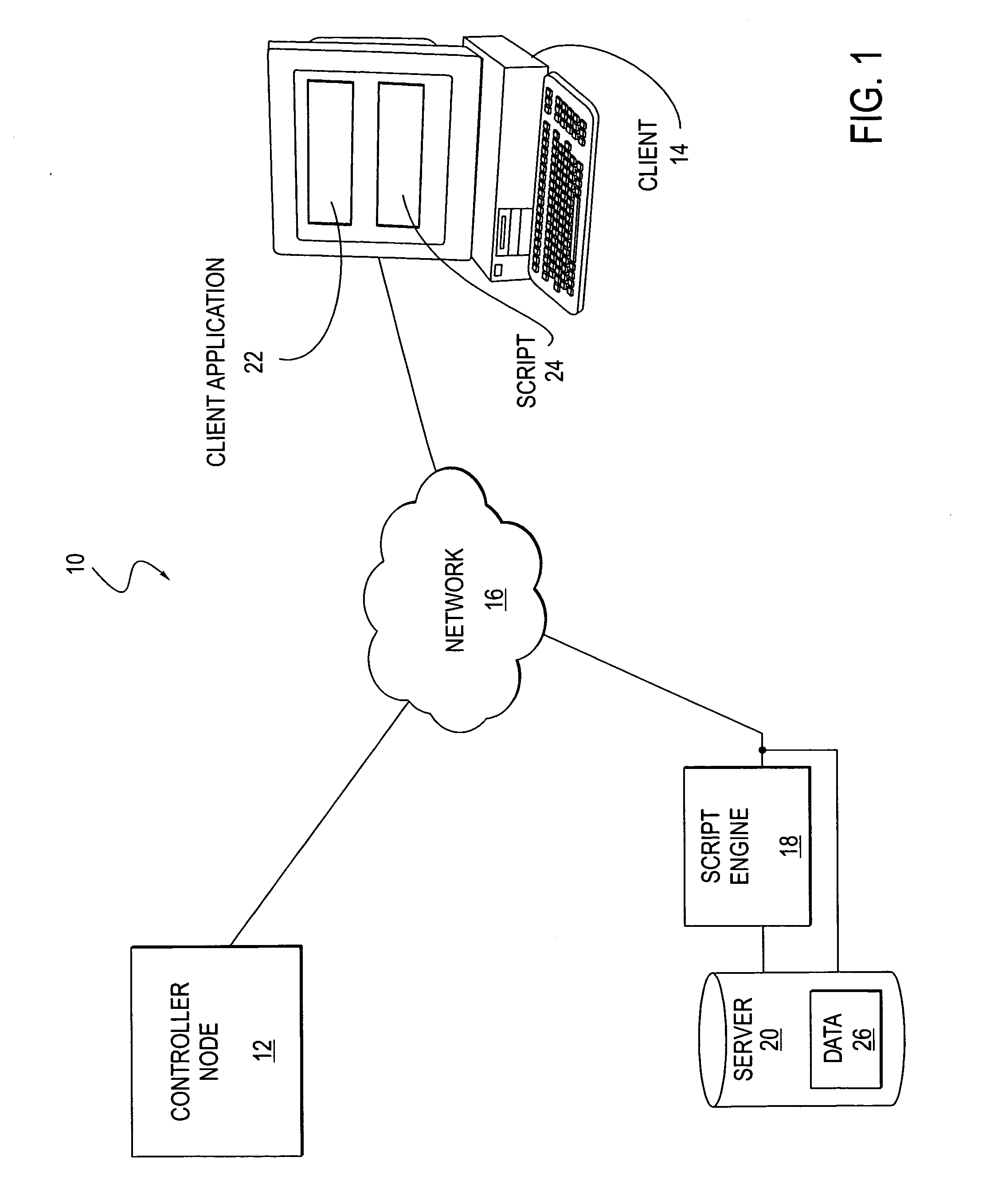

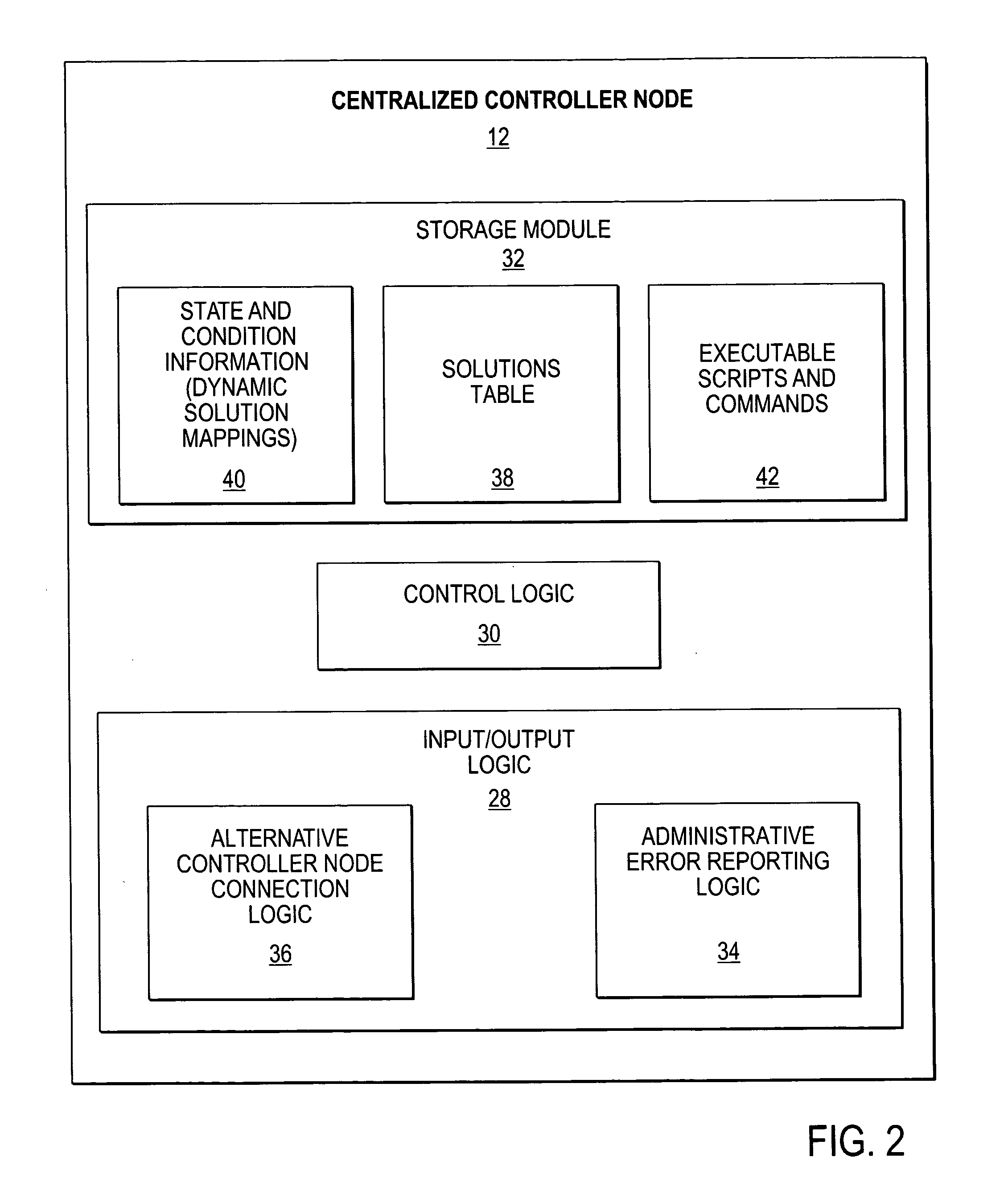

Method and system for intelligent and adaptive exception handling

A method and system for handling errors and exceptions in an ERP environment are disclosed. According to one aspect of the present invention, a condition or event causes a script-engine associated with a particular ERP server to generate an error message. The error message is communicated to a centralized controller-node. The centralized controller-node analyzes the message and determines the best course of action for handling an error or exception related to the error message. Based on the controller node's analysis, the controller node communicates a response message, thereby enabling the process that caused the error to continue without terminating abnormally.

Owner:SAP AG

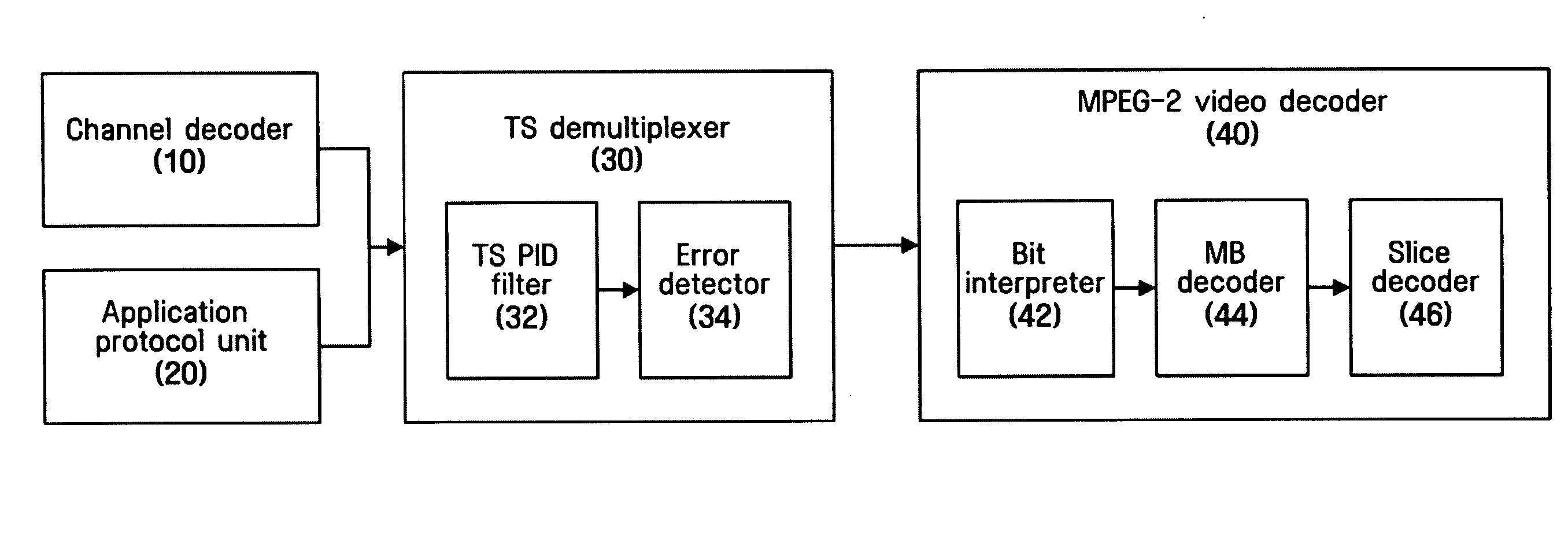

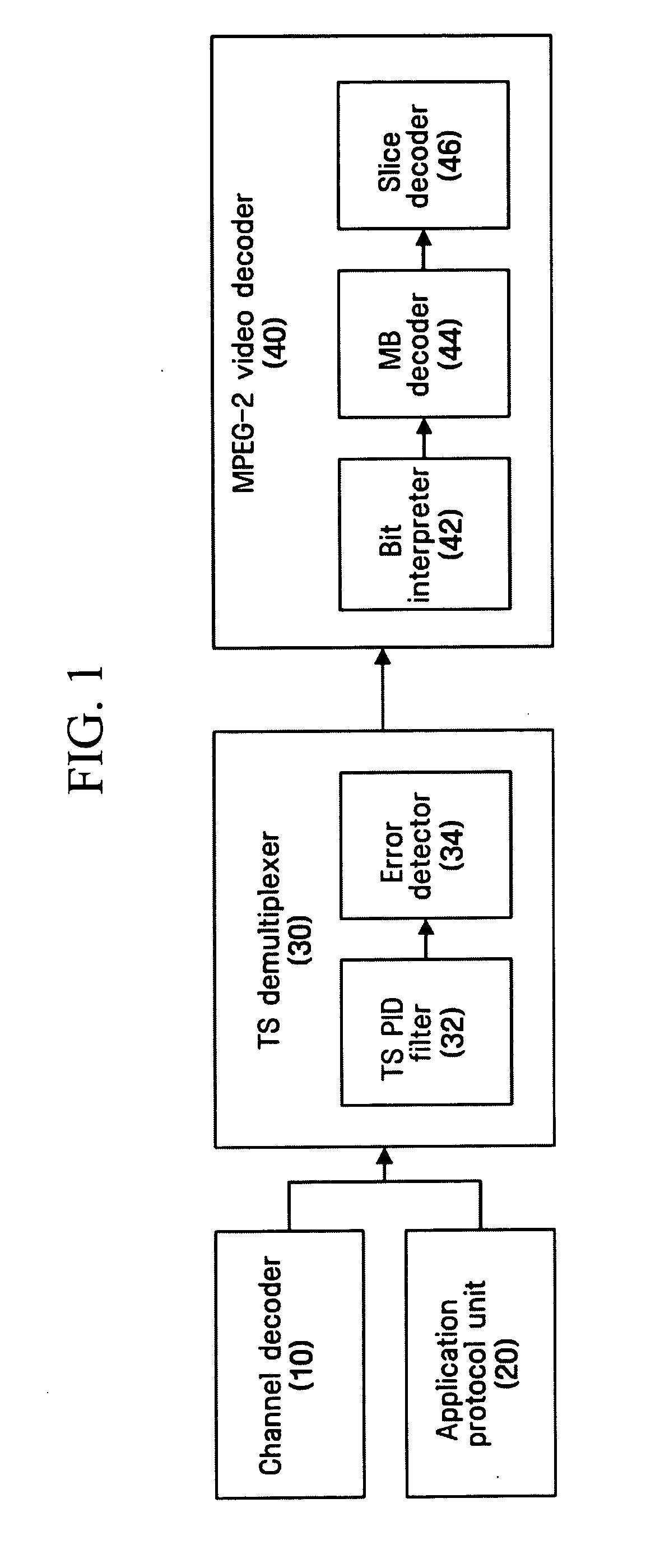

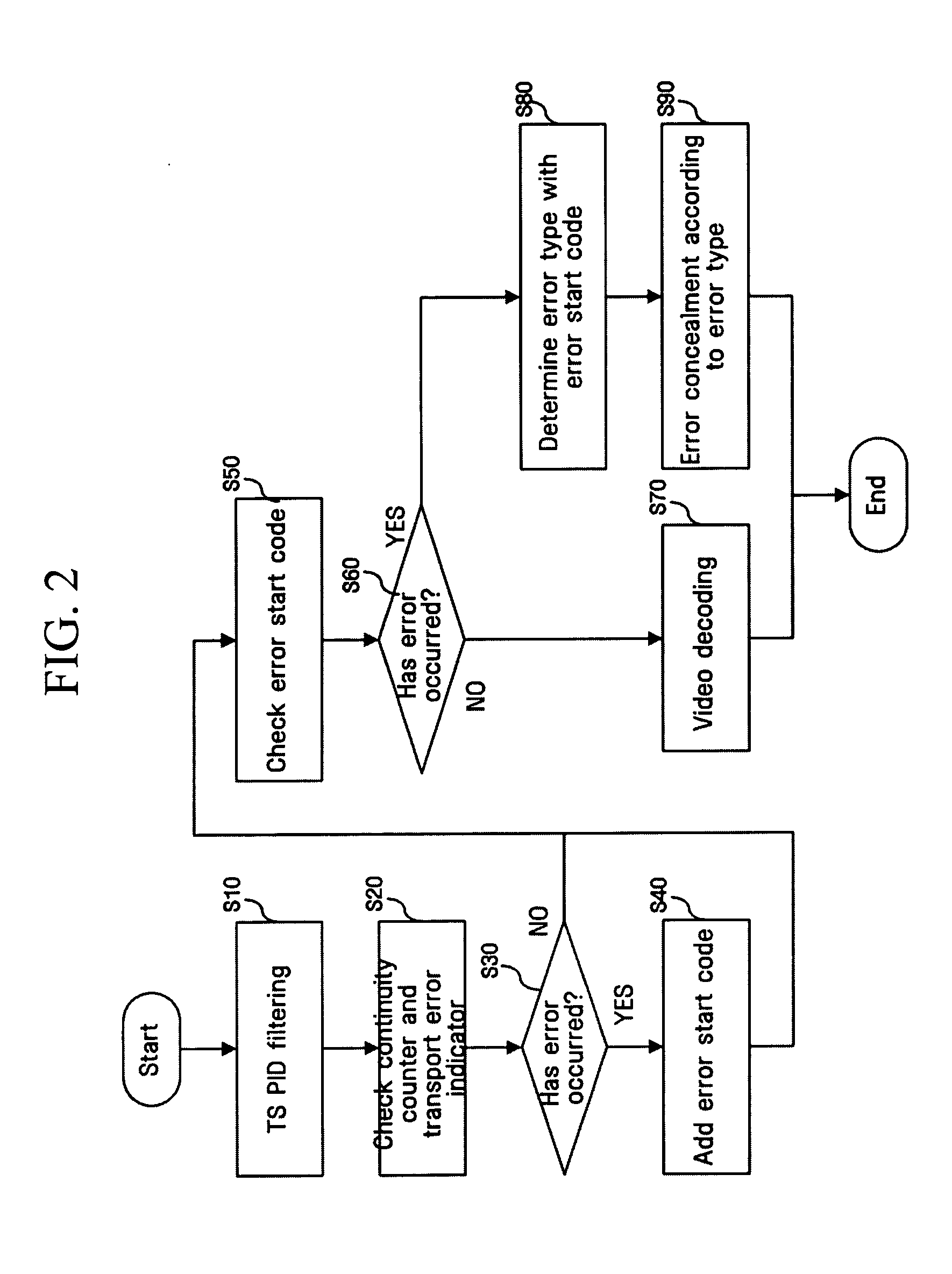

Video decoding method and apparatus for providing error detection

InactiveUS20050089104A1Color television with pulse code modulationColor television with bandwidth reductionProcess errorError concealment

Provided are a method and apparatus for detecting an error during video decoding and handling of the error. An error is detected in a received video stream having a predetermined format, error information is recorded at a predetermined location of the video stream, and the type of the error is determined using the recorded error information. The video decoder includes a broadcast signal receiver that extracts a broadcast stream from a broadcast signal being transmitted via a transmission medium, a demultiplexing and error detection unit that demultiplexes the broadcast stream of a predetermined format extracted by the broadcast signal receiver for extraction of a video stream, detects errors in packets making up the extracted video stream, and records error information at a predetermined location of the video stream, and a video decoding unit that interprets the error information, determines the type of the errors using a predetermined method, and decodes the video stream according to the result of determination. The type and position of an error may be determined during video decoding. The video decoder is able to improve video quality by performing proper error concealment according to the type of error determined.

Owner:SAMSUNG ELECTRONICS CO LTD

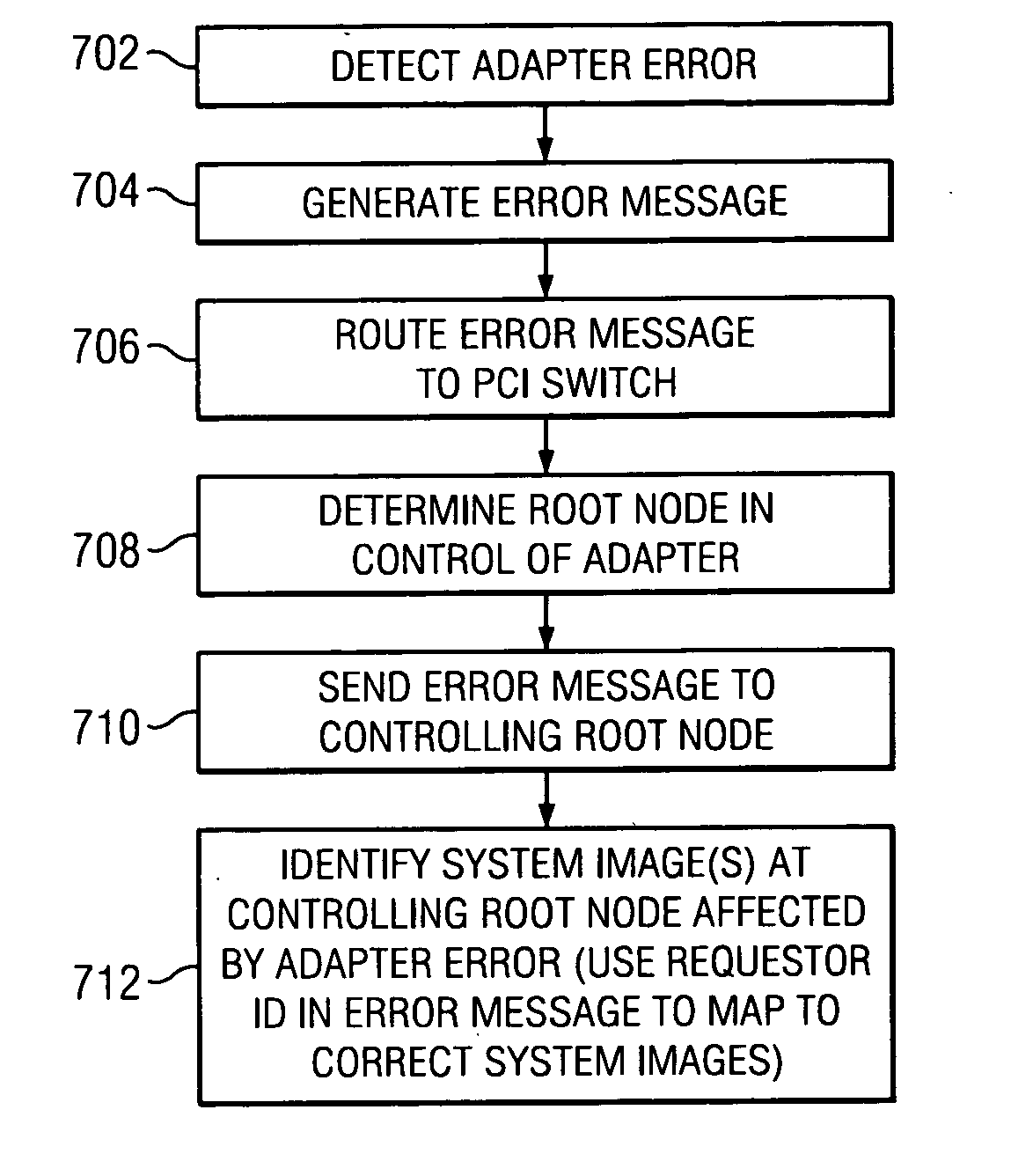

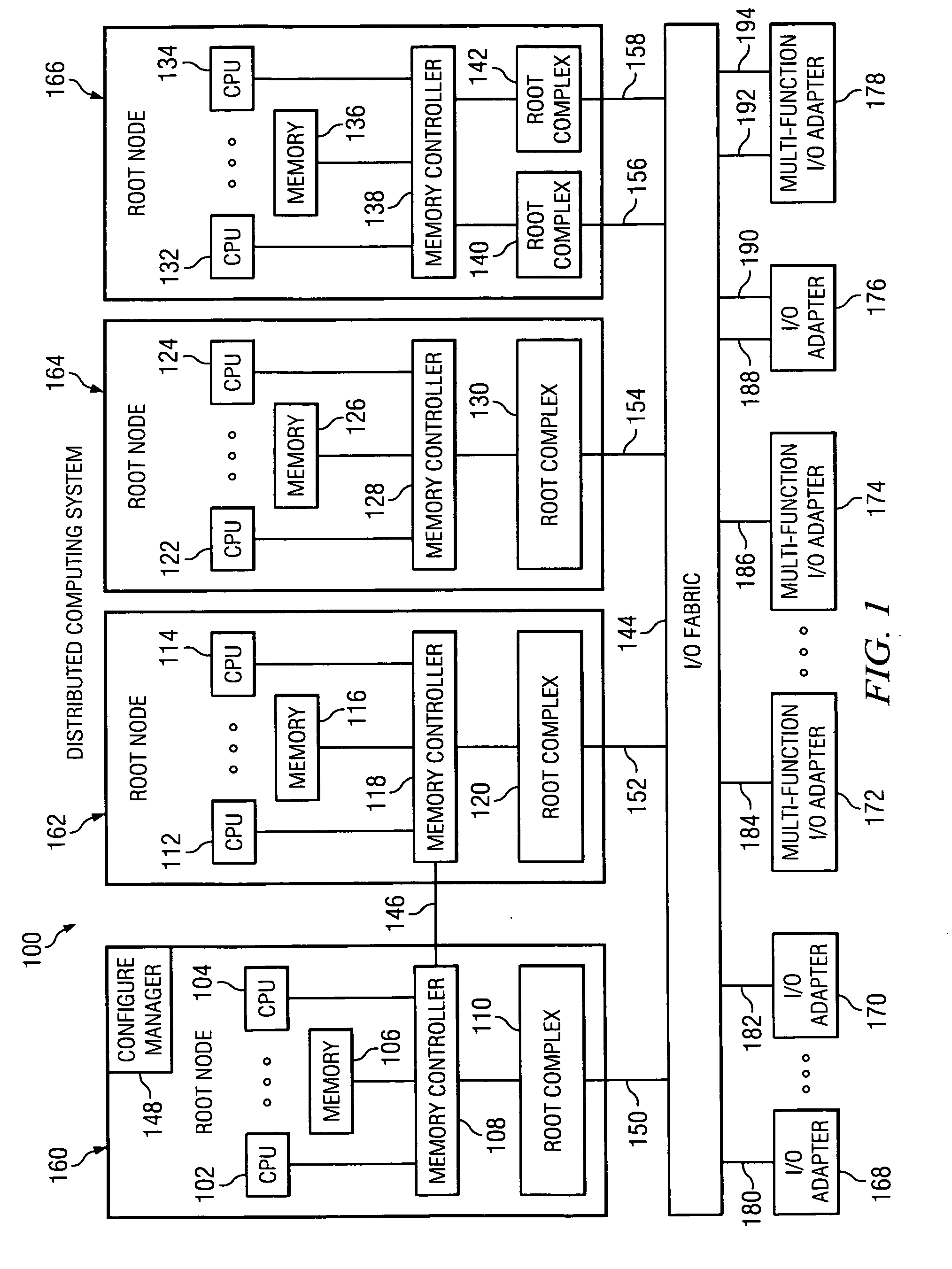

Method of routing I/O adapter error messages in a multi-host environment

A method and apparatus is provided for routing error messages in a distributed computer system comprising multiple root nodes, and further comprising one or more PCI switches and one or more I / O adapters, wherein each root node includes one or more system images. In one useful embodiment, a method is provided for routing I / O error messages to root nodes respectively associated with the errors contained in the messages. The method includes detecting occurrence of an error at a specified one of the adapters, wherein the error affects one of the system images, and generating an error message at the specified adapter. The method further comprises routing the error message from the specified adapter to the particular root node that includes the affected system image. The error message is then selectively processed at the particular root node, in order to identify the affected system image. Usefully, the step of routing the error message includes using a bus / device / function number associated with the error, together with a routing table located in one of the PCI switches, to route the error message to the correct root node and system image.

Owner:LENOVO GLOBAL TECH INT LTD

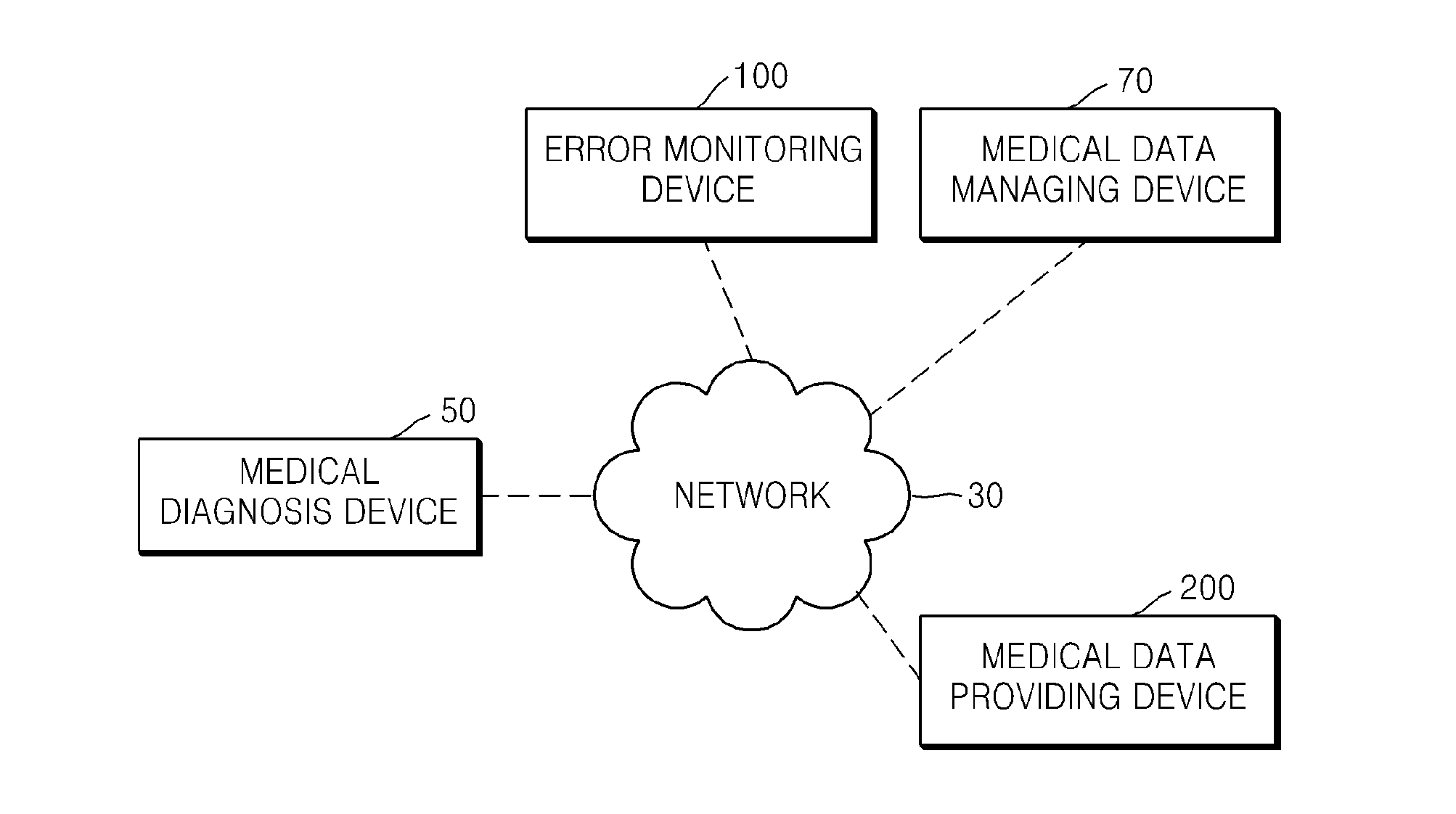

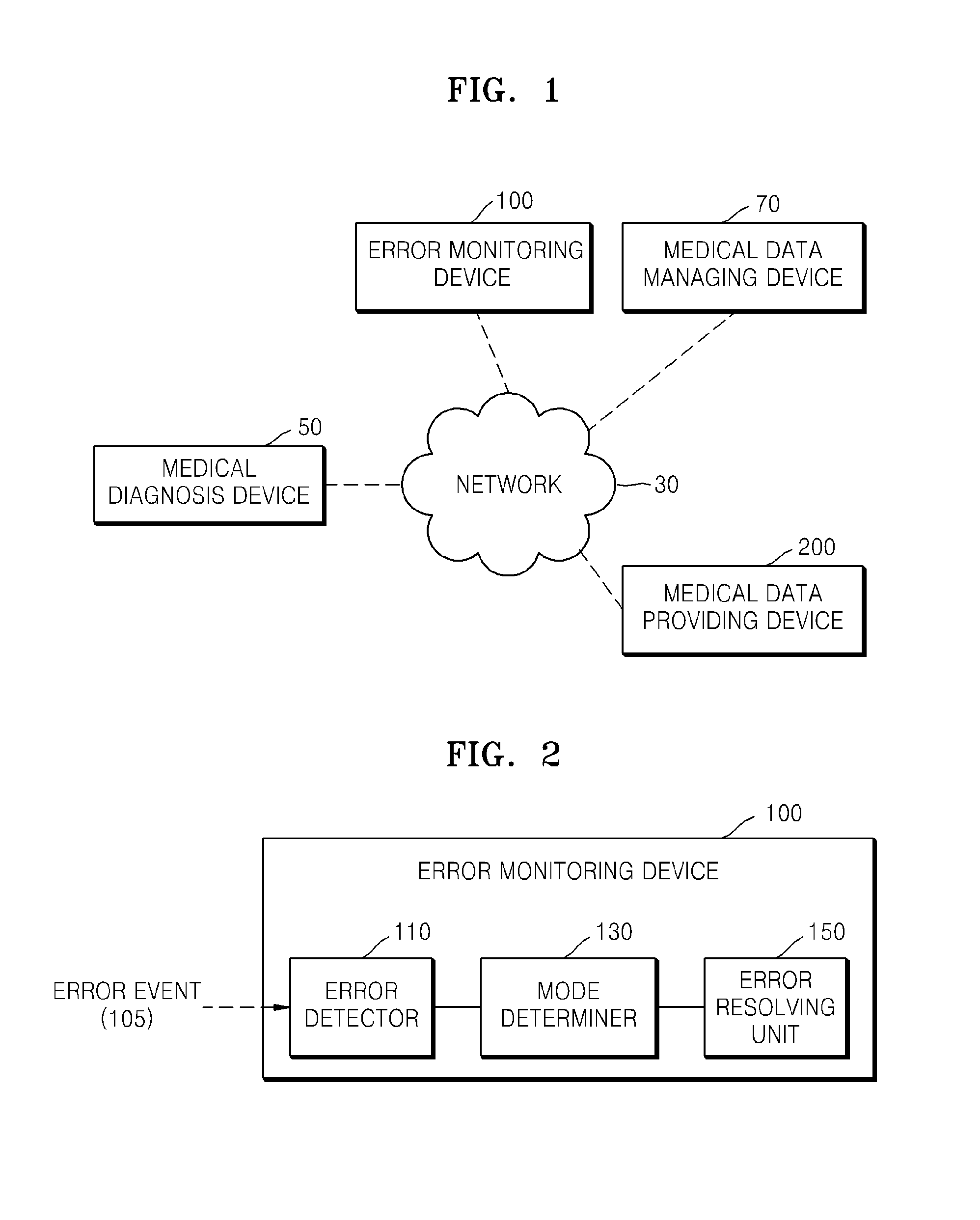

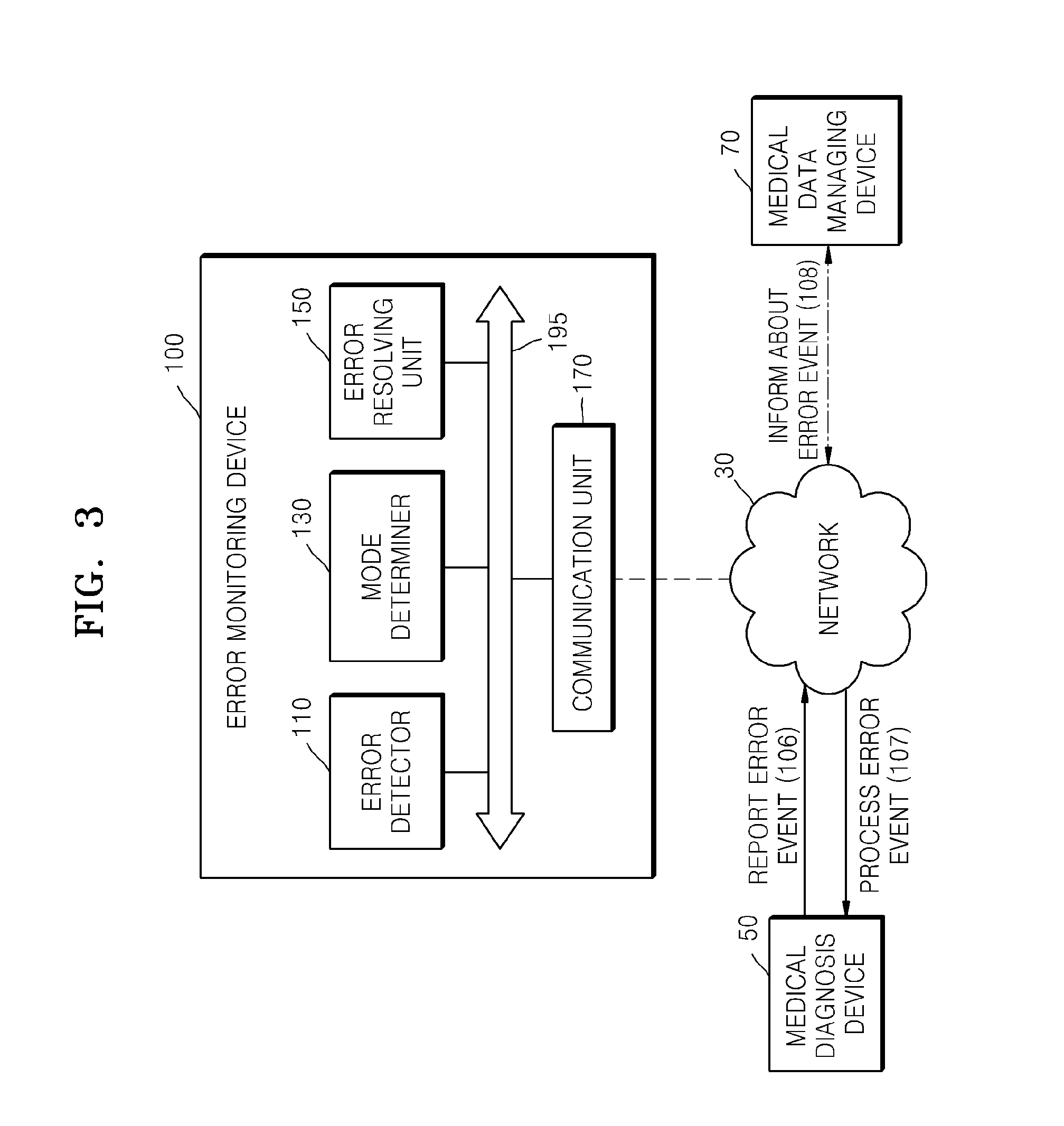

Method and apparatus for processing error event of medical diagnosis device, and for providing medical information

A method and an apparatus for processing an error event of a medical diagnosis device is provided that includes detecting an error event at a medical diagnosis system, determining an error correcting mode from among a first mode for restarting a diagnosis process at which the error event occurred, a second mode for informing the error event to components of the medical diagnosis system at which the error event did not occur, and a third mode for stopping operation of the medical diagnosis system, based on information regarding the error event, and processing the error event based on the determined error correcting mode. There is also provided a method for providing medical information that includes receiving medical data, providing a diagnosis process a first region, providing log data at a second region, and providing video data at a third region of the screen image.

Owner:SAMSUNG ELECTRONICS CO LTD

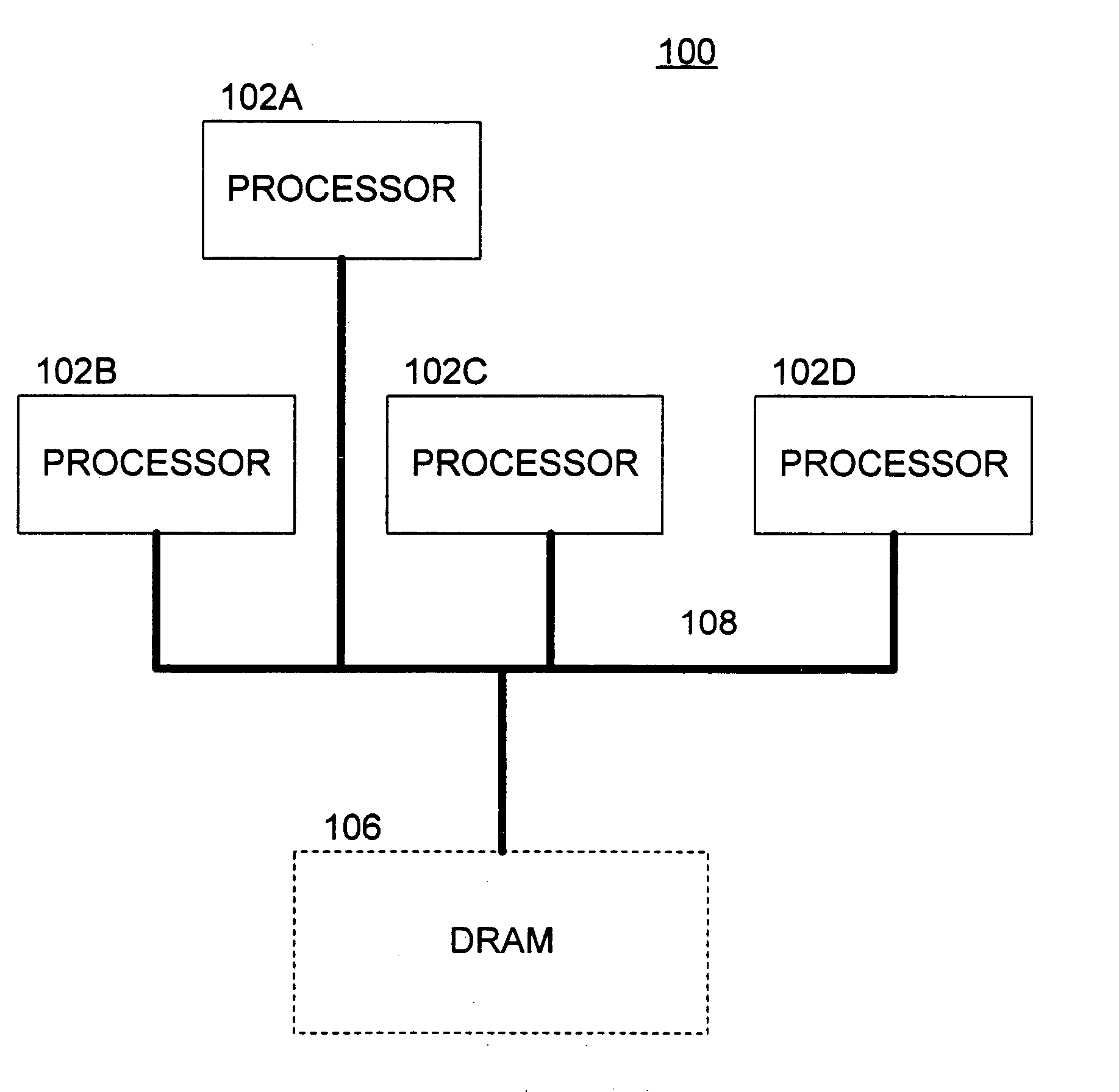

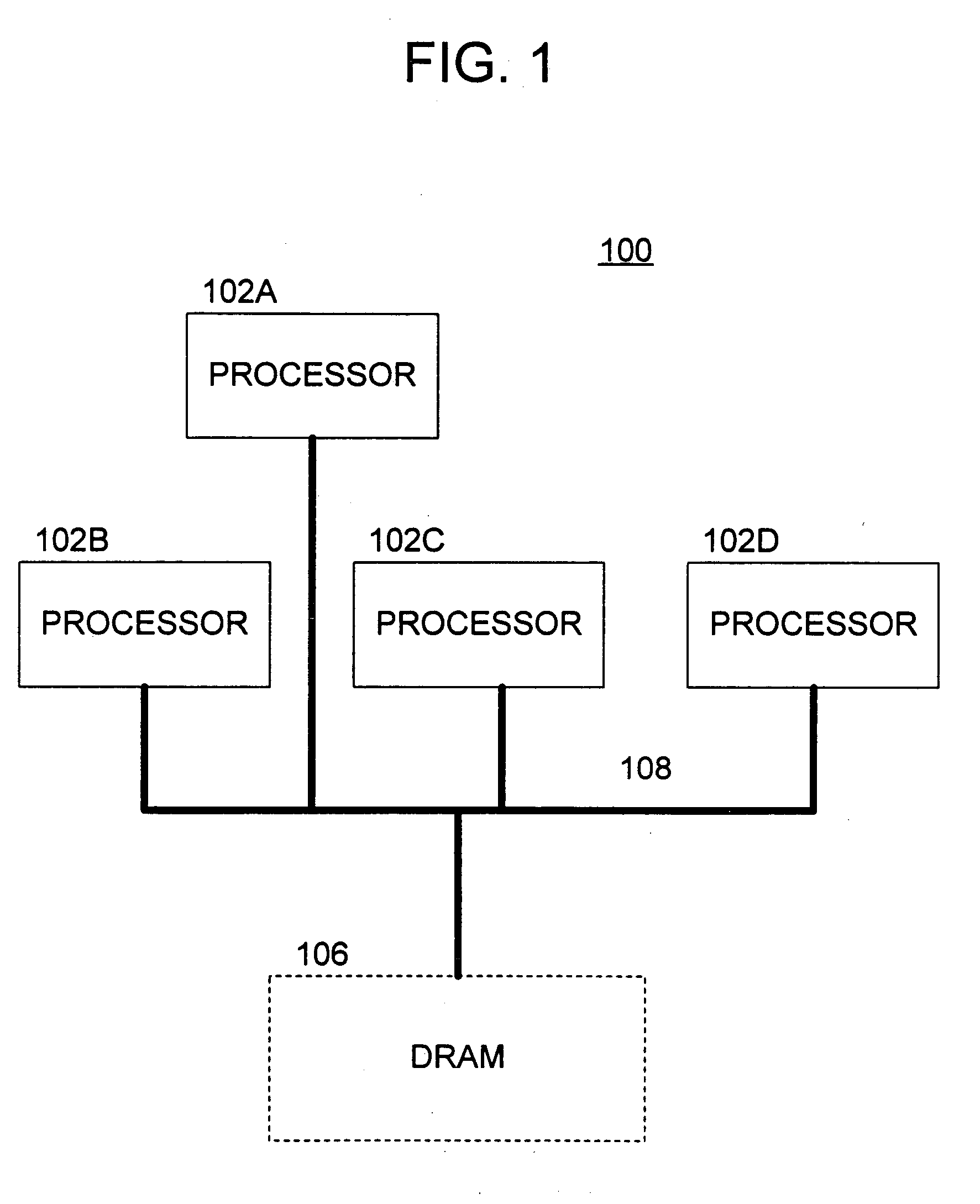

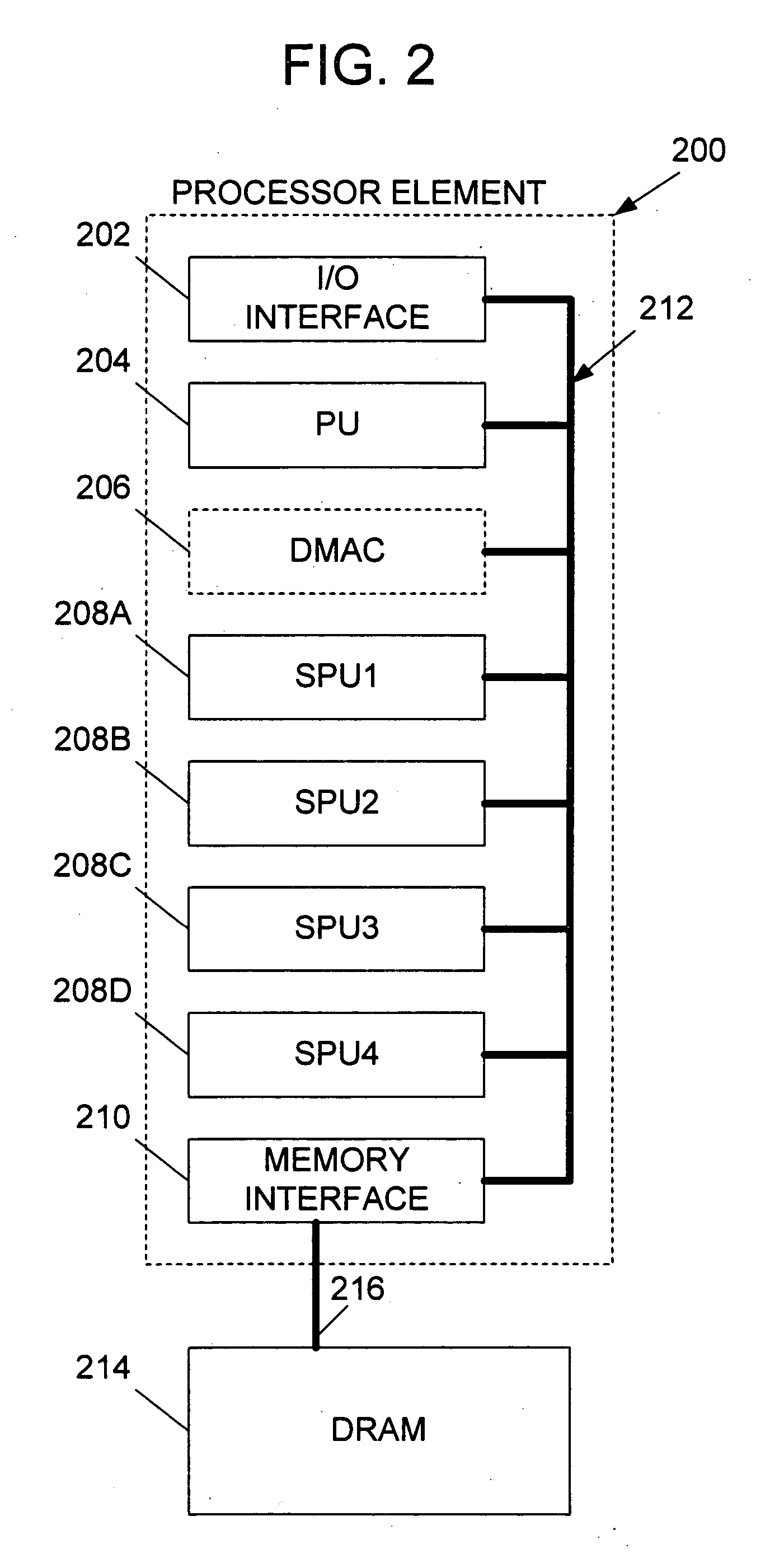

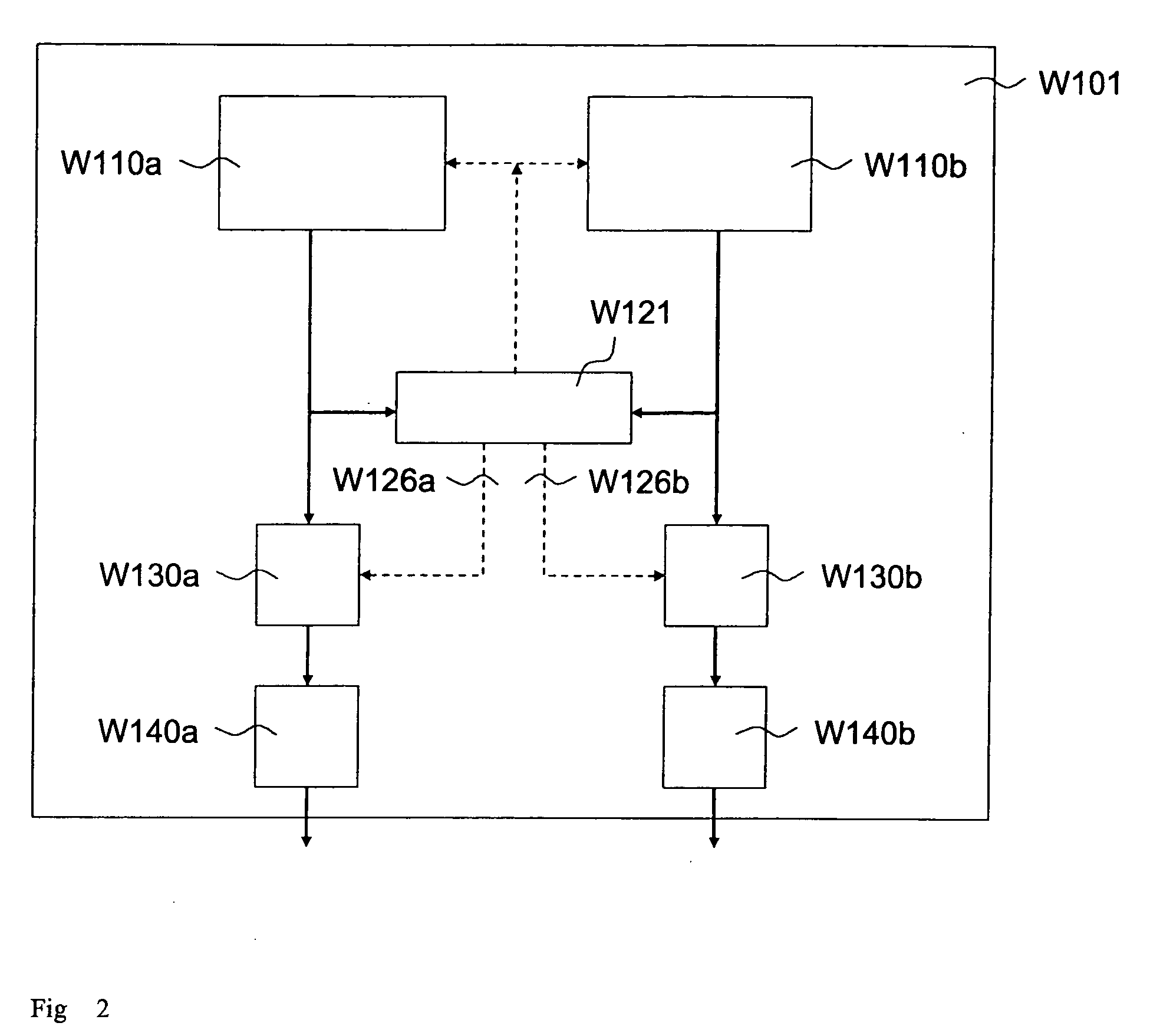

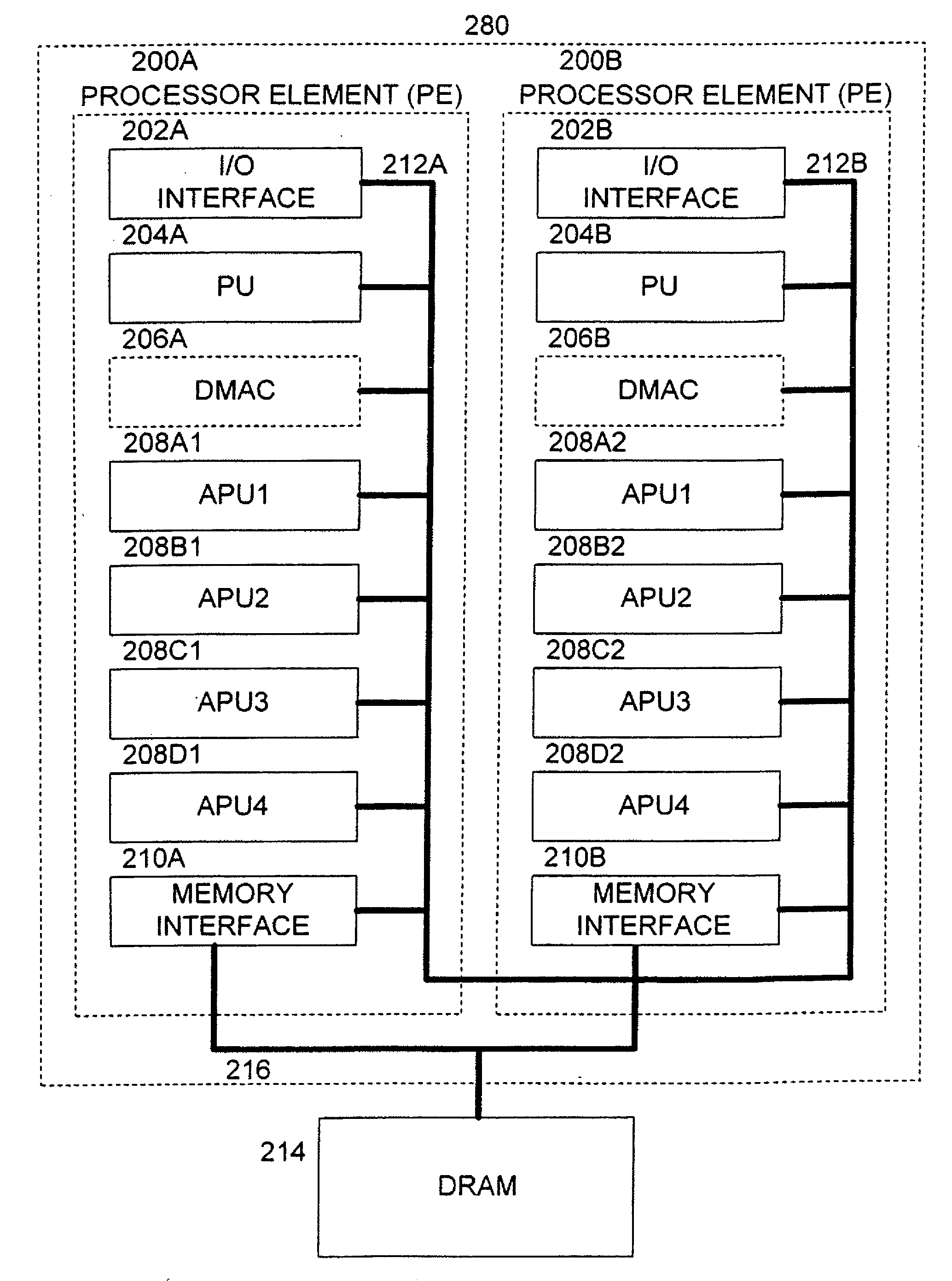

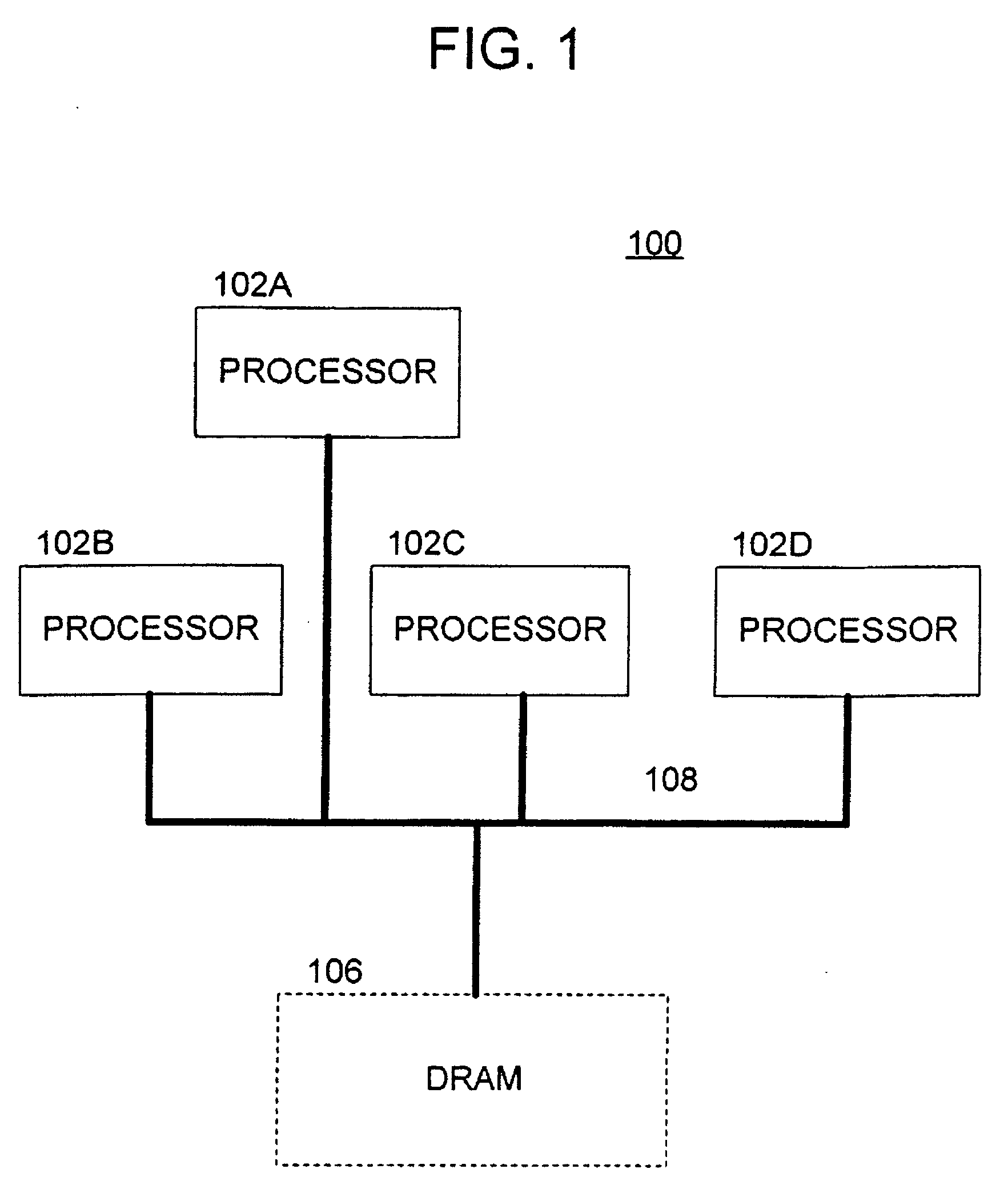

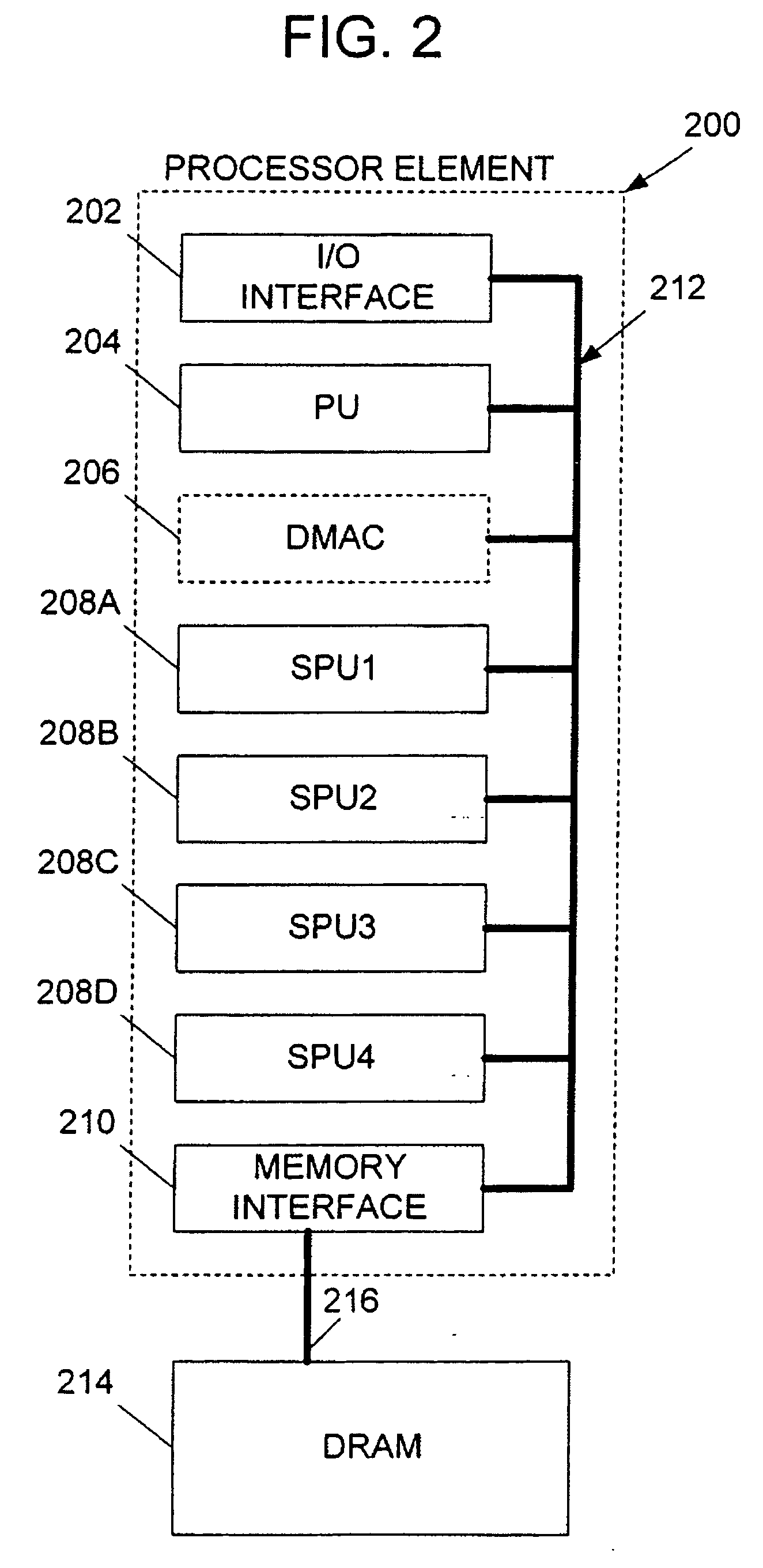

Methods and apparatus for handling processing errors in a multi-processing system

InactiveUS20050273652A1Resource allocationSpecific program execution arrangementsMain processing unitProcess error

Methods and apparatus are provided for: monitoring processor tasks and associated processor loads therefor that are allocated to be performed by respective sub-processing units associated with a main processing unit; detecting whether a processing error has occurred in a given one of the sub-processing units; re-allocating all of the processor tasks of the given sub-processing unit to one or more participating sub-processing units, including other sub-processing units associated with the main processing unit, based on the processor loads of the processor tasks of the given sub-processing unit and the processor loads of the participating sub-processing units; and at least one of: (i) shutting down, and (ii) re-booting the given sub-processing unit.

Owner:SONY COMPUTER ENTERTAINMENT INC

Method and Device for Controlling a Computer System Having At Least Two Execution Units and One Comparator Unit

A method for controlling a computer system having at least two execution units and one comparator unit, which system is operated in the lock-step mode and in which the results of the at least two execution units are compared, wherein when or after an error is detected by the comparator unit, an error-detection mechanism is processed on at least one execution unit for this execution unit.

Owner:ROBERT BOSCH GMBH

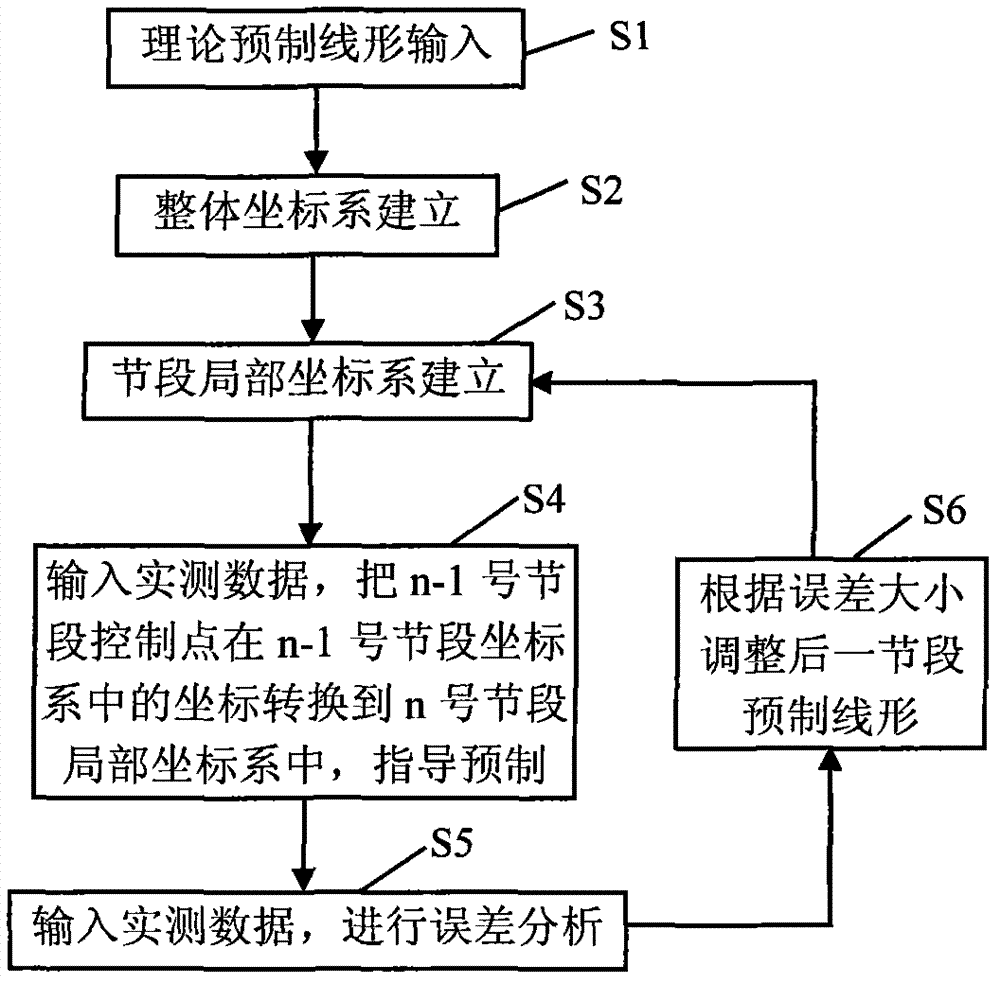

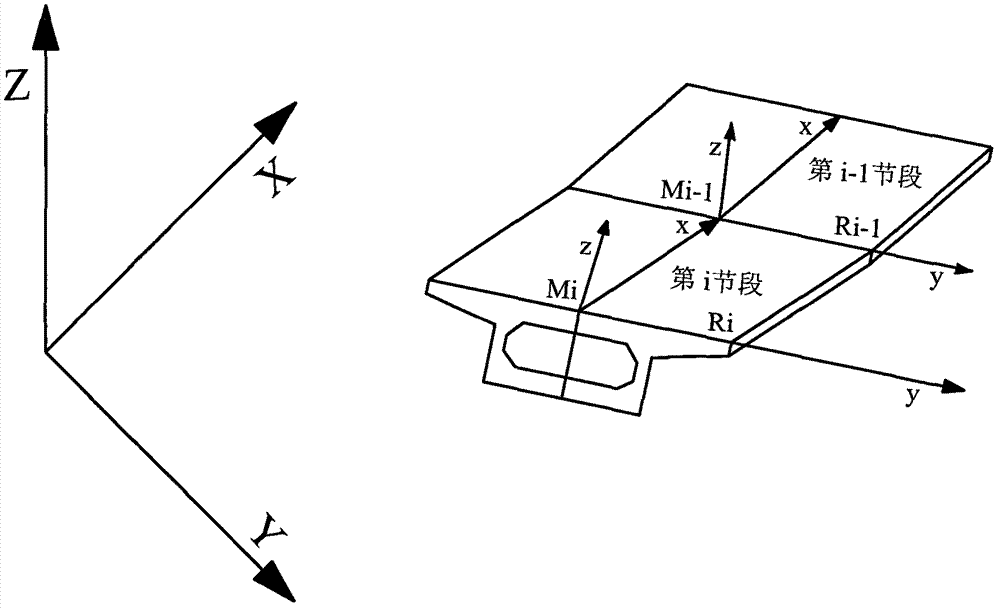

Line shape control method for short line method segment prefabrication construction

ActiveCN102733311AHigh control precisionCalculation speedBridge erection/assemblyObservational errorProcess error

The invention discloses a line shape control method for short line method segment prefabrication construction and relates to the field of control of bridge construction. The method comprises the following steps of: calculating a theoretical prefabrication line shape according to the line shape of bridge design and the construction sequence by a tangent displacement method; building the global coordinate system of the prefabrication line shape and the local coordinate systems of all prefabrication segments; converting segment control points between the local coordinate systems and the global coordinate system by a matrix calculation method; processing errors by a non-linear least square method, and correcting coordinates of segment nodes in the global coordinate system; and adjusting the line shapes of subsequent segments by a direct adjustment method or a segmentation adjustment method according to the errors. According to the method, the errors are processed by the non-linear least square method, so the method is high in calculation speed; the influence of position errors of matched segments, measurement errors of a control point coordinate, and template errors on the prefabrication line shape is comprehensively considered, the control accuracy of the line shape is improve obviously, and the popularization of a short line method segment construction method in China is accelerated.

Owner:CHINA RAILWAY BRIDGE SCI RES INST LTD +1

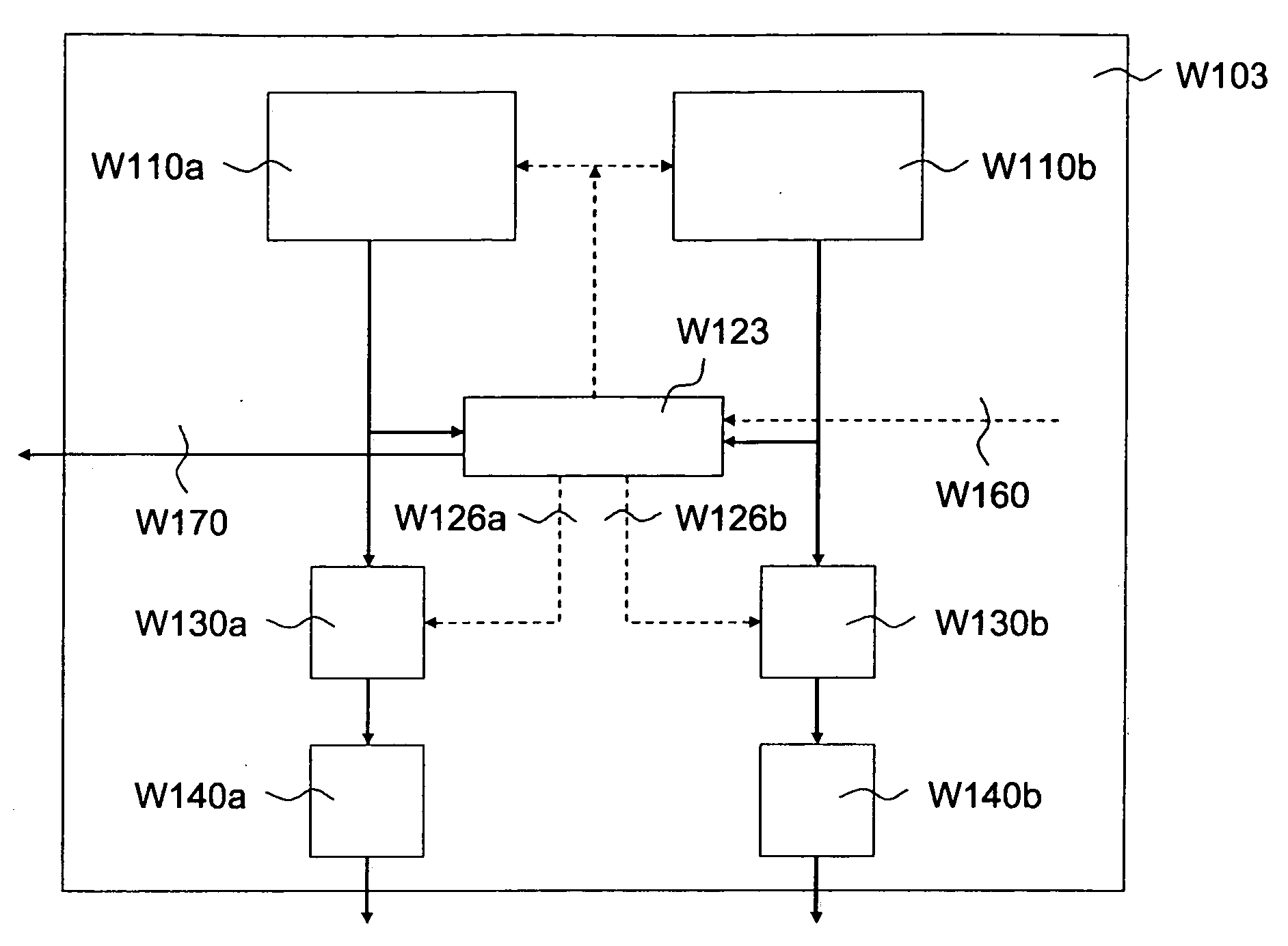

Methods and apparatus for handling processing errors in a multi-processing system

ActiveUS20080098260A1Resource allocationSpecific program execution arrangementsMain processing unitProcess error

Methods and apparatus are provided for: monitoring processor tasks and associated processor loads therefor that are allocated to be performed by respective sub-processing units associated with a main processing unit; detecting whether a processing error has occurred in a given one of the sub-processing units; re-allocating all of the processor tasks of the given sub-processing unit to one or more participating sub-processing units, including other sub-processing units associated with the main processing unit, based on the processor loads of the processor tasks of the given sub-processing unit and the processor loads of the participating sub-processing units; and at least one of: (i) shutting down, and (ii) re-booting the given sub-processing unit.

Owner:SONY COMPUTER ENTERTAINMENT INC

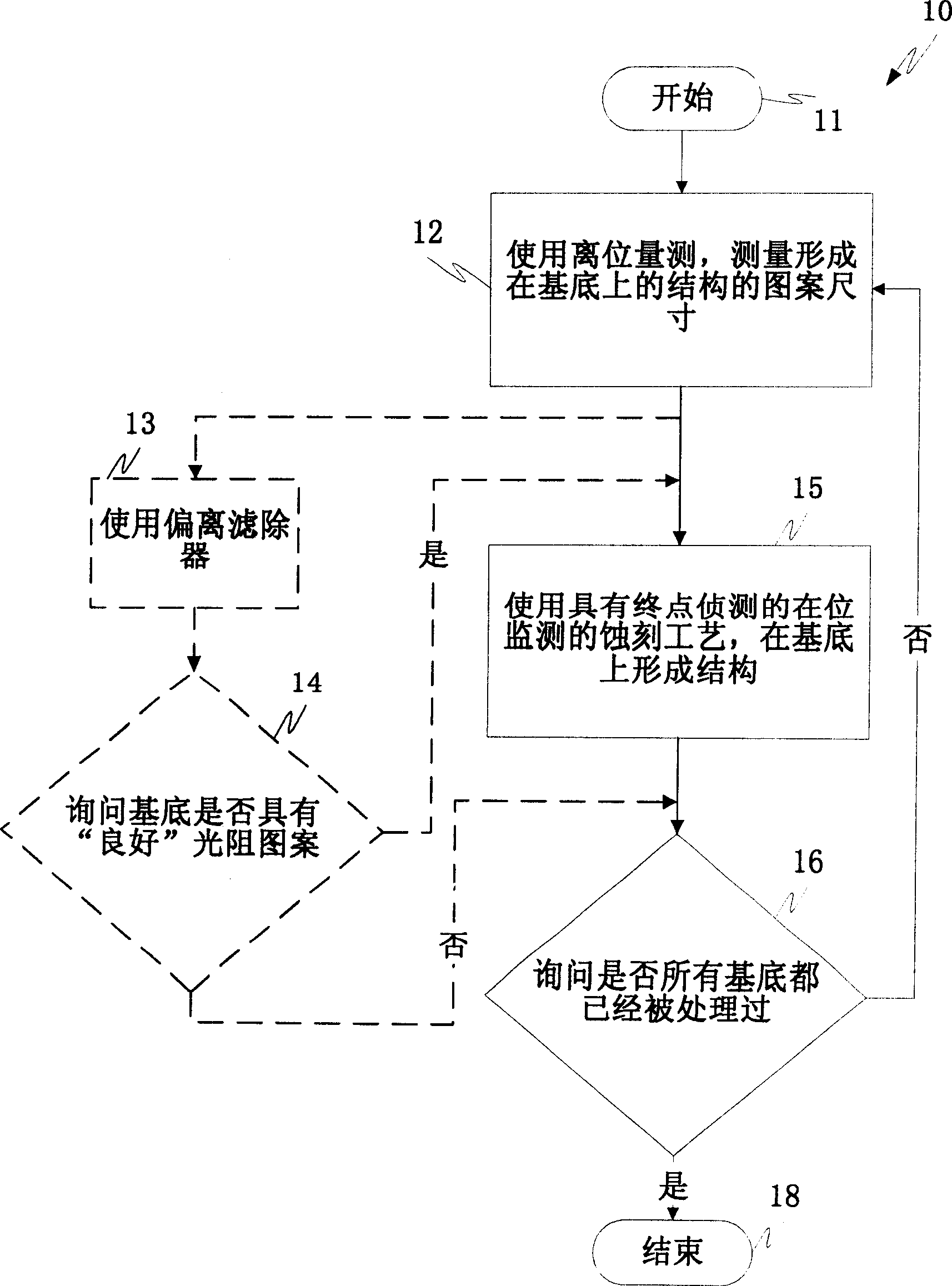

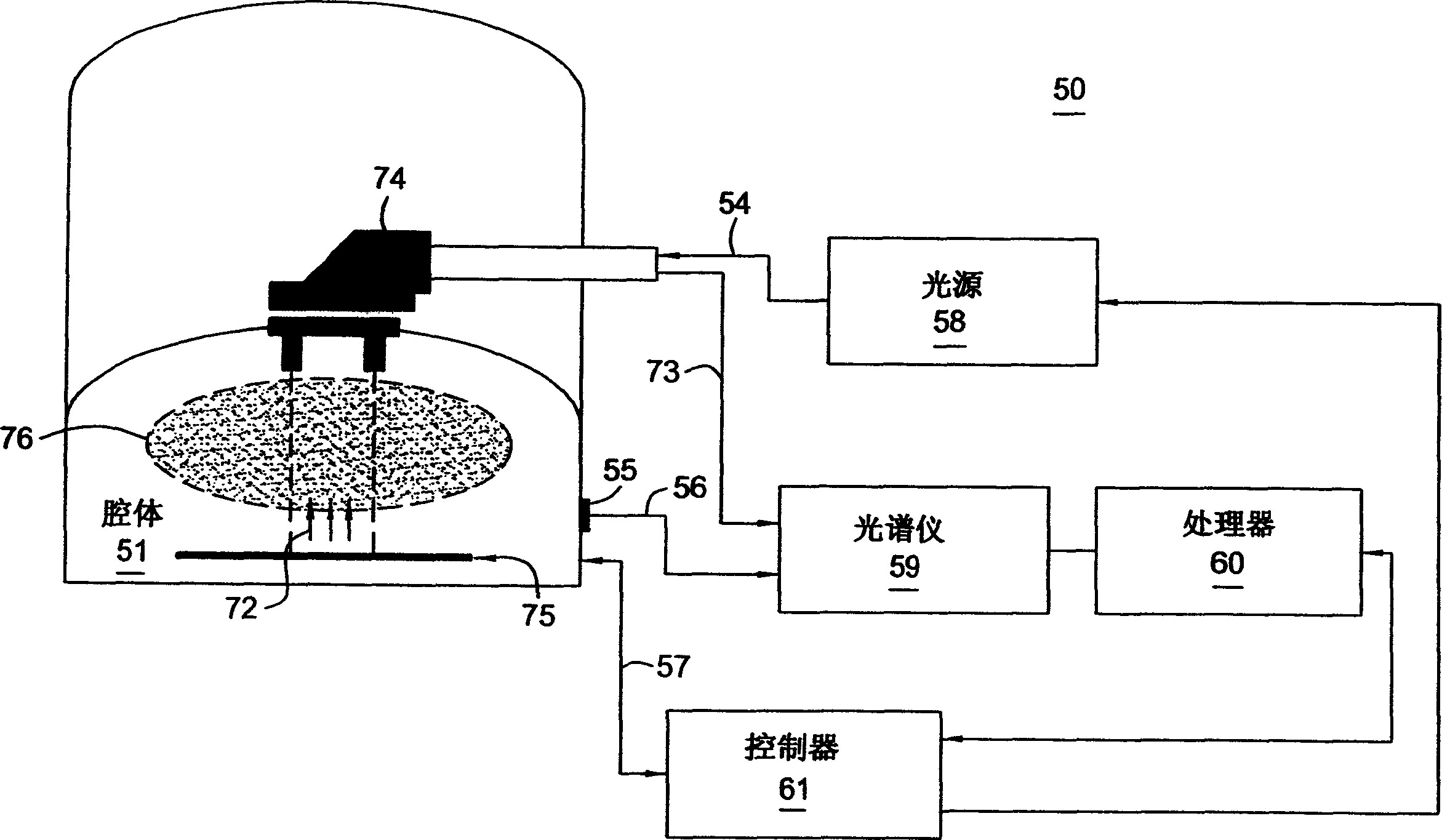

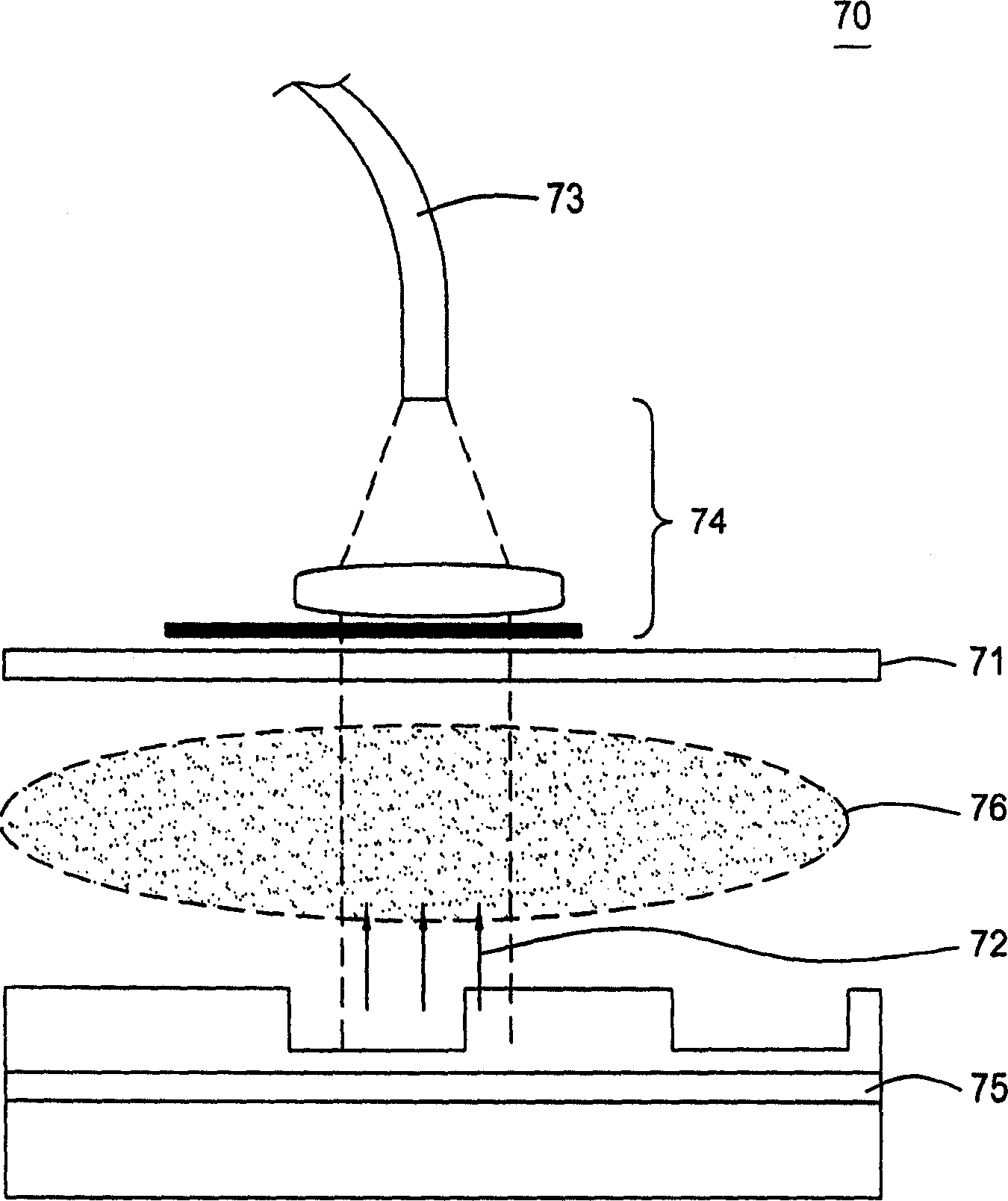

Method and system for monitoring etch process

InactiveCN1619788ASemiconductor/solid-state device testing/measurementElectric discharge tubesKey sizeProcess error

A method and system for monitoring an etching process. The etch process can be monitored using metrology information, such as critical dimensions or layer thicknesses, etc. The metrology information is provided by ex-situ and in-situ monitoring of the etch process performed during the etch process, such as spectroscopic analysis, interferometry, scatterometry, and reflectometry. Off-site measurement information and on-site monitoring can be used to monitor, for example, an end point of an etch process, a feature of the etch depth profile formed on a substrate, and error detection of an integrated circuit process.

Owner:APPLIED MATERIALS INC

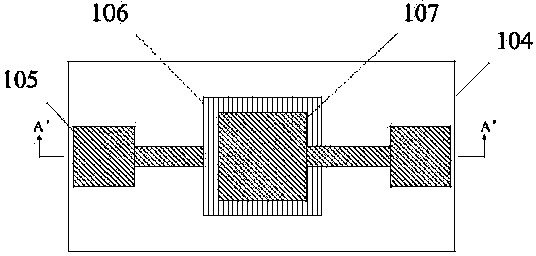

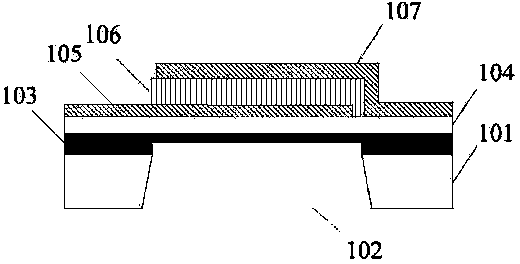

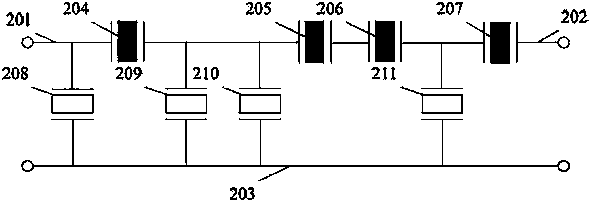

FBAR with temperature compensation function and resonance frequency tuning function and filter

InactiveCN104242864AImprove temperature stabilitySimple structureImpedence networksNegative temperatureProcess error

The invention discloses an FBAR with a temperature compensation function and a resonance frequency tuning function and a filter. The FBAR comprises a substrate, a temperature compensation and resonance frequency tuning layer, a supporting layer, a bottom electrode, a top electrode and a piezoelectric film. The middle of the bottom of the temperature compensation and resonance frequency tuning layer is provided with a groove, the substrate is arranged under the two sides of the groove, and a cavity is formed through the substrate and the bottom face of the temperature compensation and resonance frequency tuning layer; the supporting layer is arranged on the upper side of the temperature compensation and resonance frequency tuning layer; the piezoelectric film is arranged between the bottom electrode and the top electrode; the FBAR and the filter can effectively reduce temperature and frequency drift caused by a piezoelectric film with a negative temperature coefficient, and accordingly the temperature stability of the FBAR is improved. In the post-processing technology, the thickness of an FBAR lamination is adjusted by controlling etching time of the temperature compensation and resonance frequency tuning layer in the FBAR lamination, frequency drift caused by process errors can be effectively reduced, and the frequency accuracy of the FBAR is improved.

Owner:INST OF ELECTRONICS ENG CHINA ACAD OF ENG PHYSICS

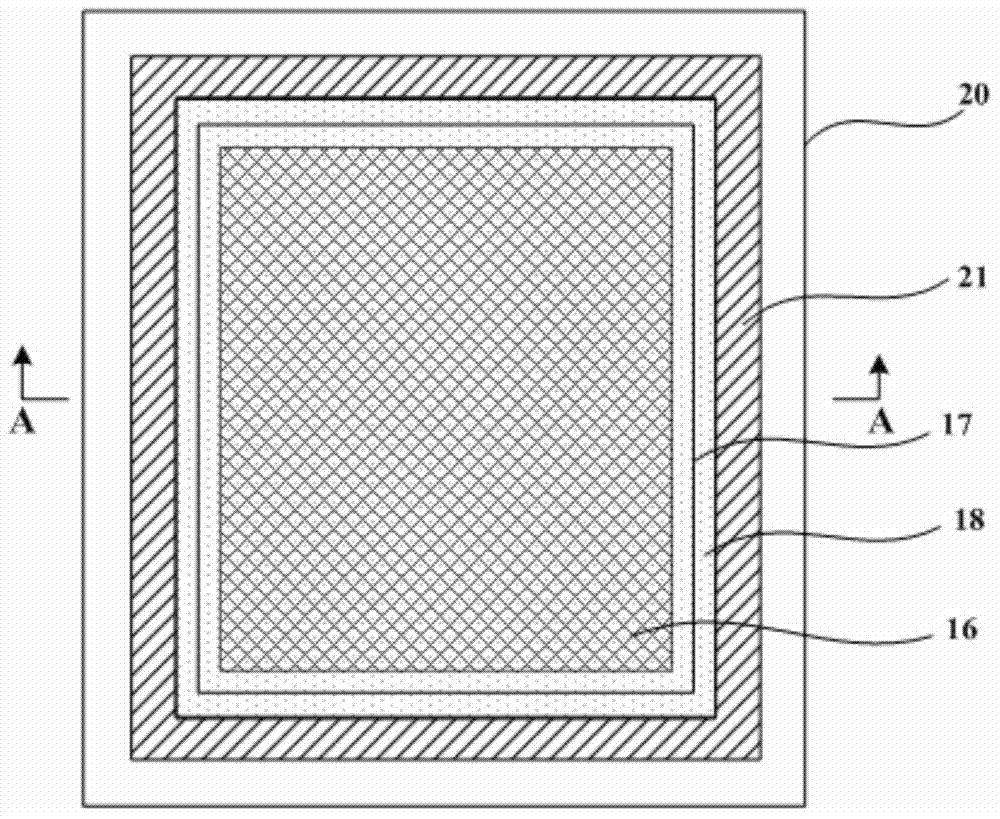

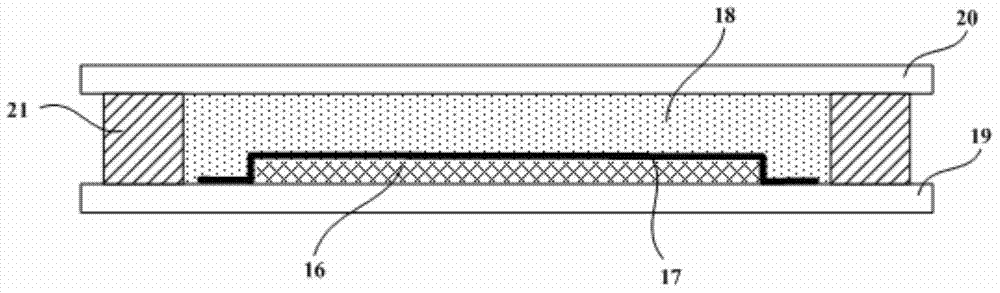

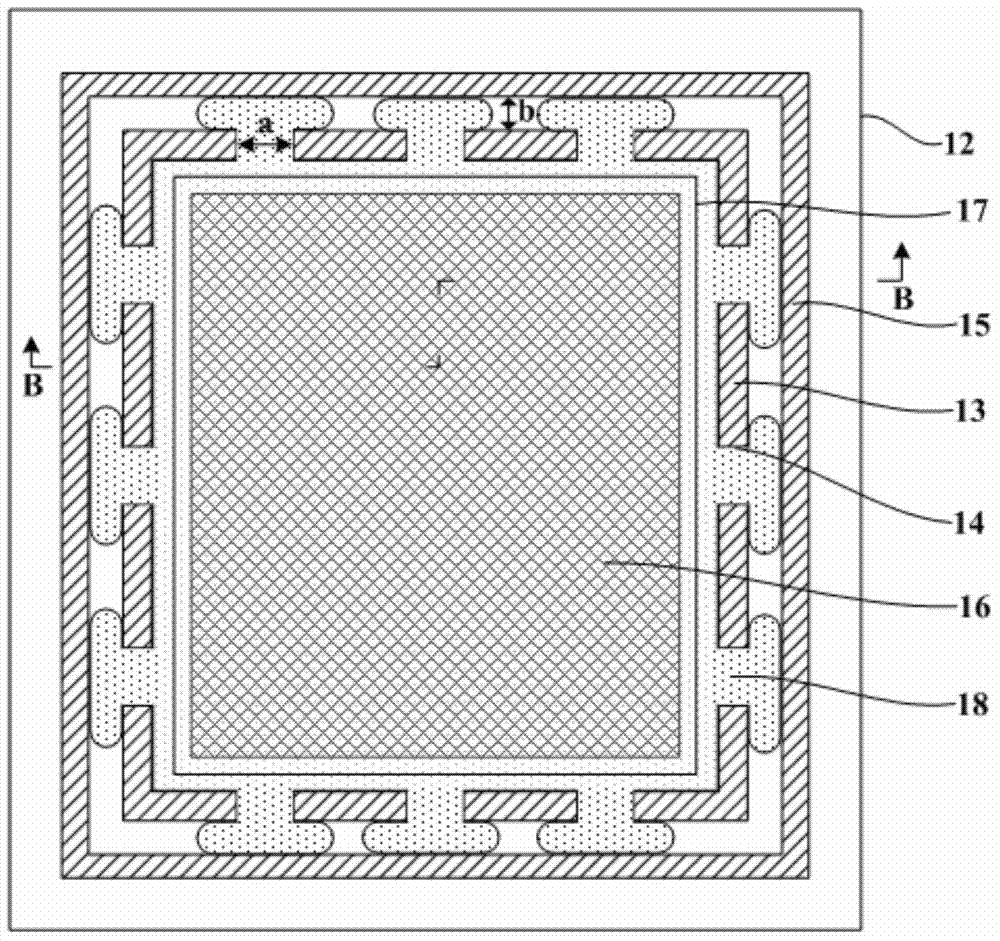

OLED (organic light-emitting diode) display screen, manufacturing method for same and display device

InactiveCN103500755ALarge process error rangeReduce the difficulty of debuggingSolid-state devicesSemiconductor/solid-state device manufacturingProcess errorDisplay device

The invention discloses an OLED (organic light-emitting diode) display screen, a manufacturing method for the same and a display device, and aims to lower the debugging difficulty of an OLED display screen production process and improve the production efficiency and the quality of a product. The OLED display screen comprises a first substrate, a second substrate, first surrounding dam rubber, second surrounding dam rubber, an OLED device, a protective layer and filling rubber, wherein the first and second substrates are opposite to each other; the first surrounding dam rubber is connected between the first and second substrates, and is provided with at least one opening; the second surrounding dam rubber is connected between the first and second substrates, and is positioned outside the first surrounding dam rubber; the second surrounding dam rubber, the first substrate and the second substrate form a sealed box; the OLED device is positioned on the inner side of the first surrounding dam rubber, is positioned on the first substrate, and is covered by the protective layer; the protective layer is in sealed connection with the first substrate; the filling rubber is filled on the inner side of the first surrounding dam rubber. According to the OLED display screen, the manufacturing method for the same and the display device, the process error range of the filling volume of the filling rubber is widened, the debugging difficulty of the production process is lowered, and the production efficiency and the quality of the product are favorably improved.

Owner:BOE TECH GRP CO LTD

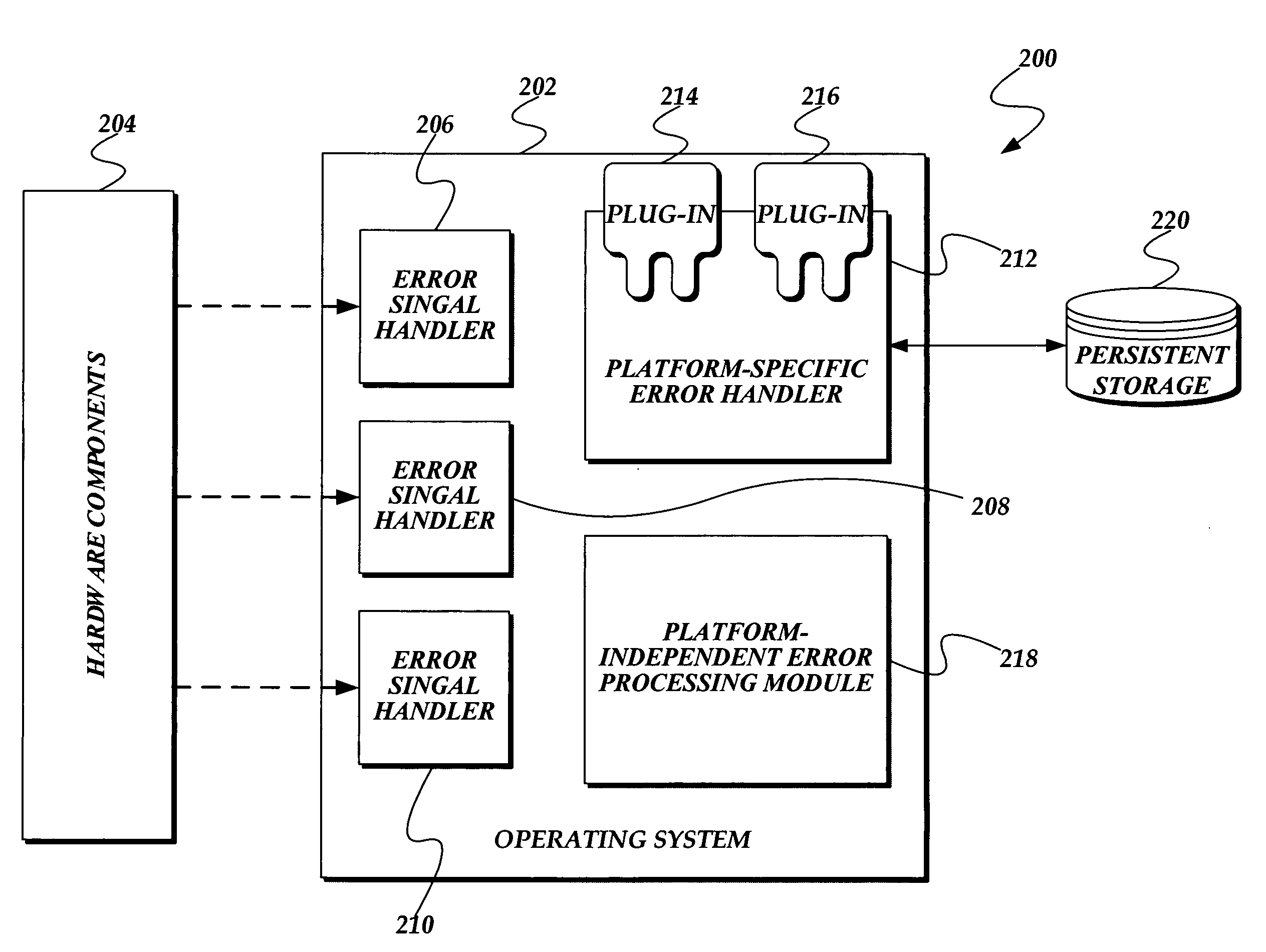

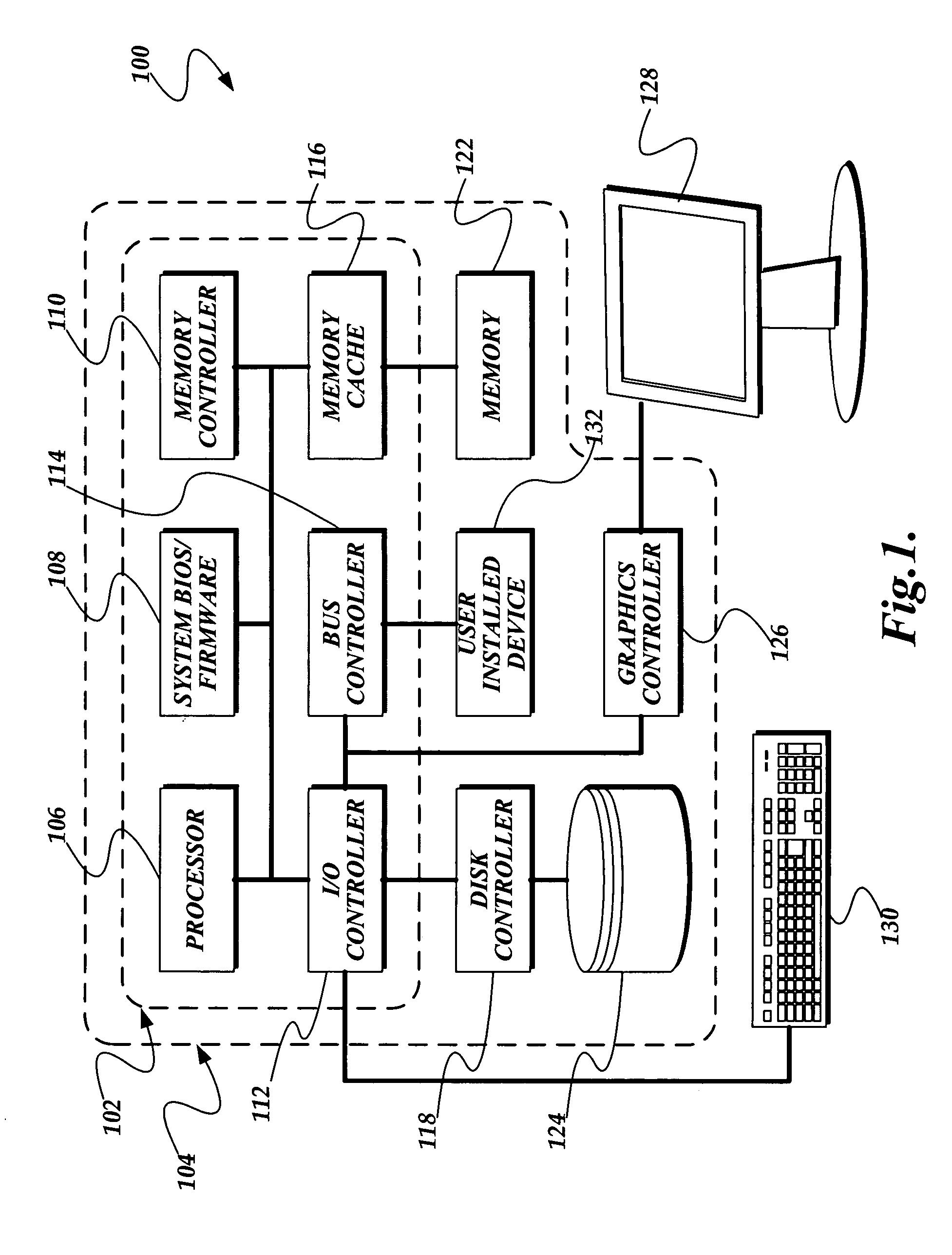

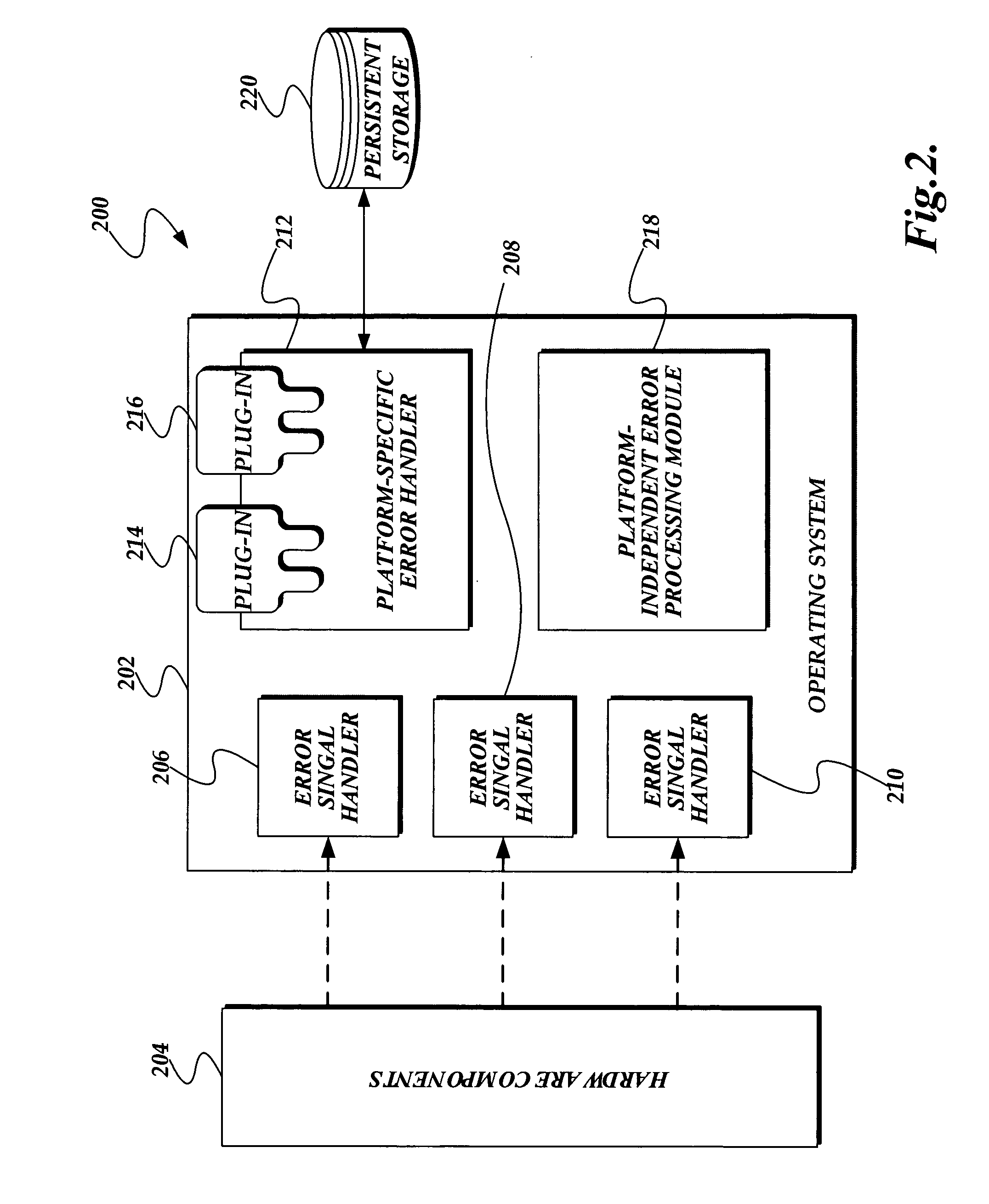

System and method for hardware error reporting and recovery

A system and method for hardware error reporting and recovery is presented. An operating system provides an error signal handler, a platform-independent error processing module, and a platform-specific error handler. The error signal handler is configured to detect the occurrence of a hardware error and to notify the platform-independent error processing module of the detected hardware error. The platform-independent error processing module is configured to process the hardware error detected by the error signal handler. The platform-specific error handler is configured to perform platform-specific error processing of the hardware error in cooperation with the platform-independent error processing module.

Owner:MICROSOFT TECH LICENSING LLC

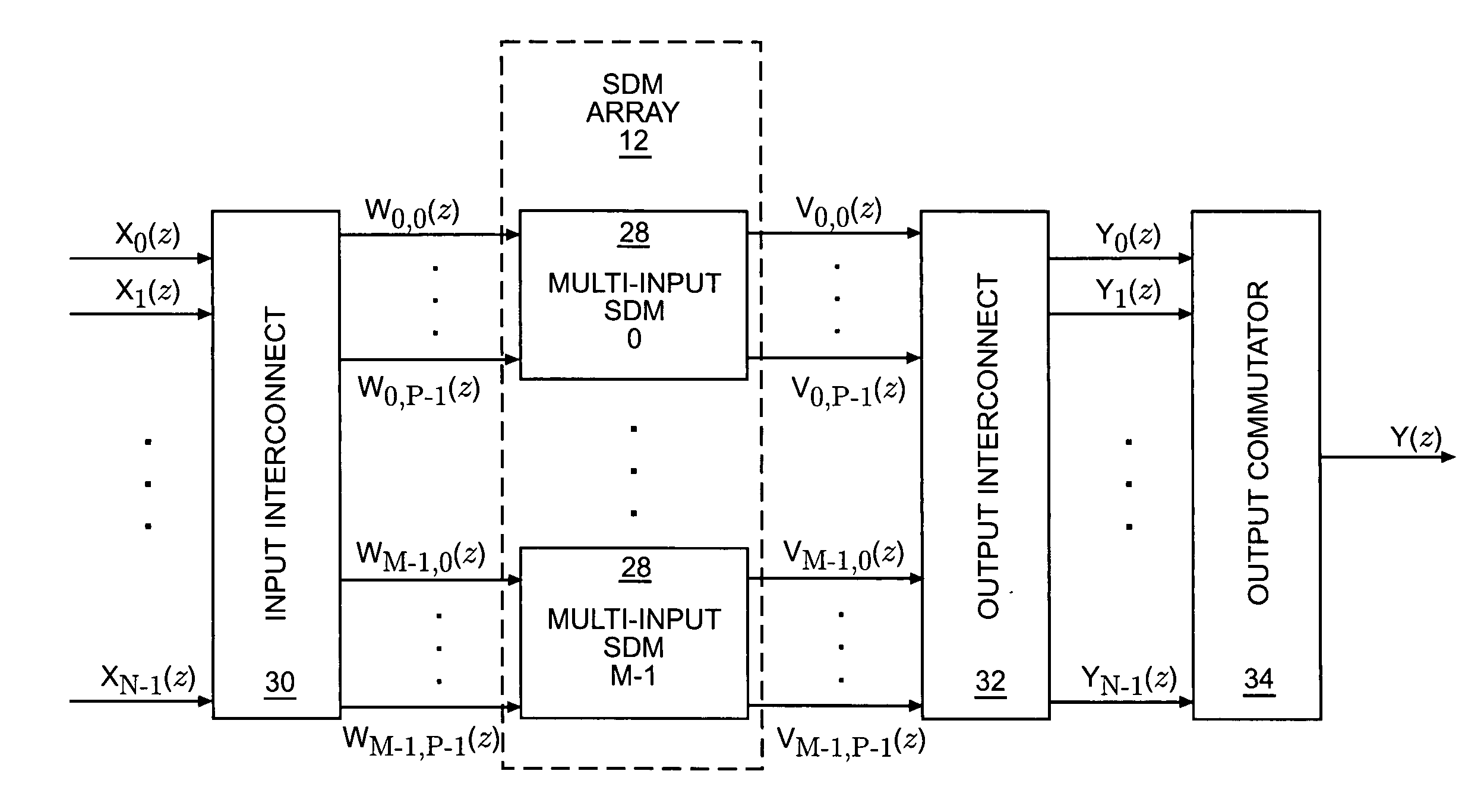

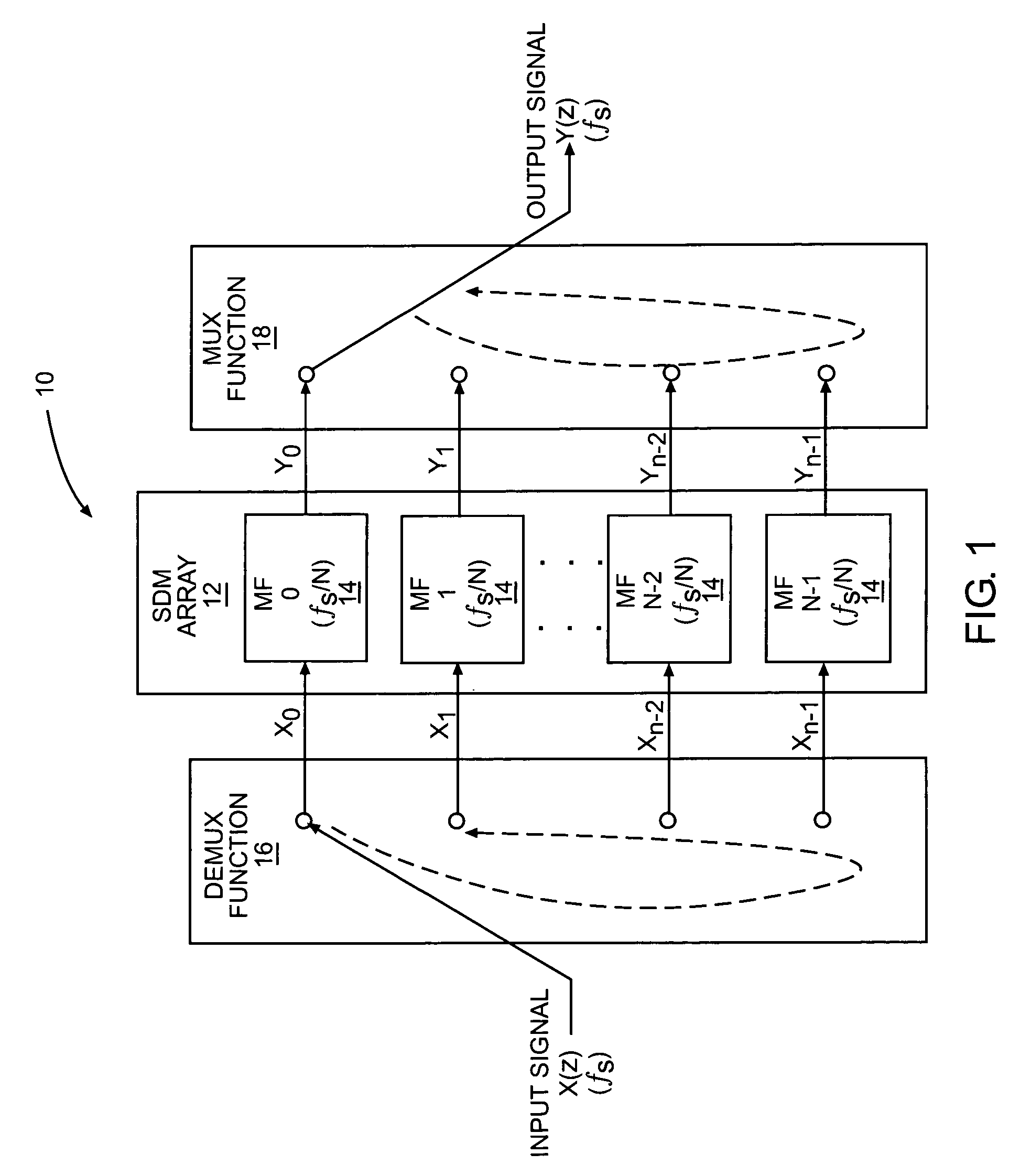

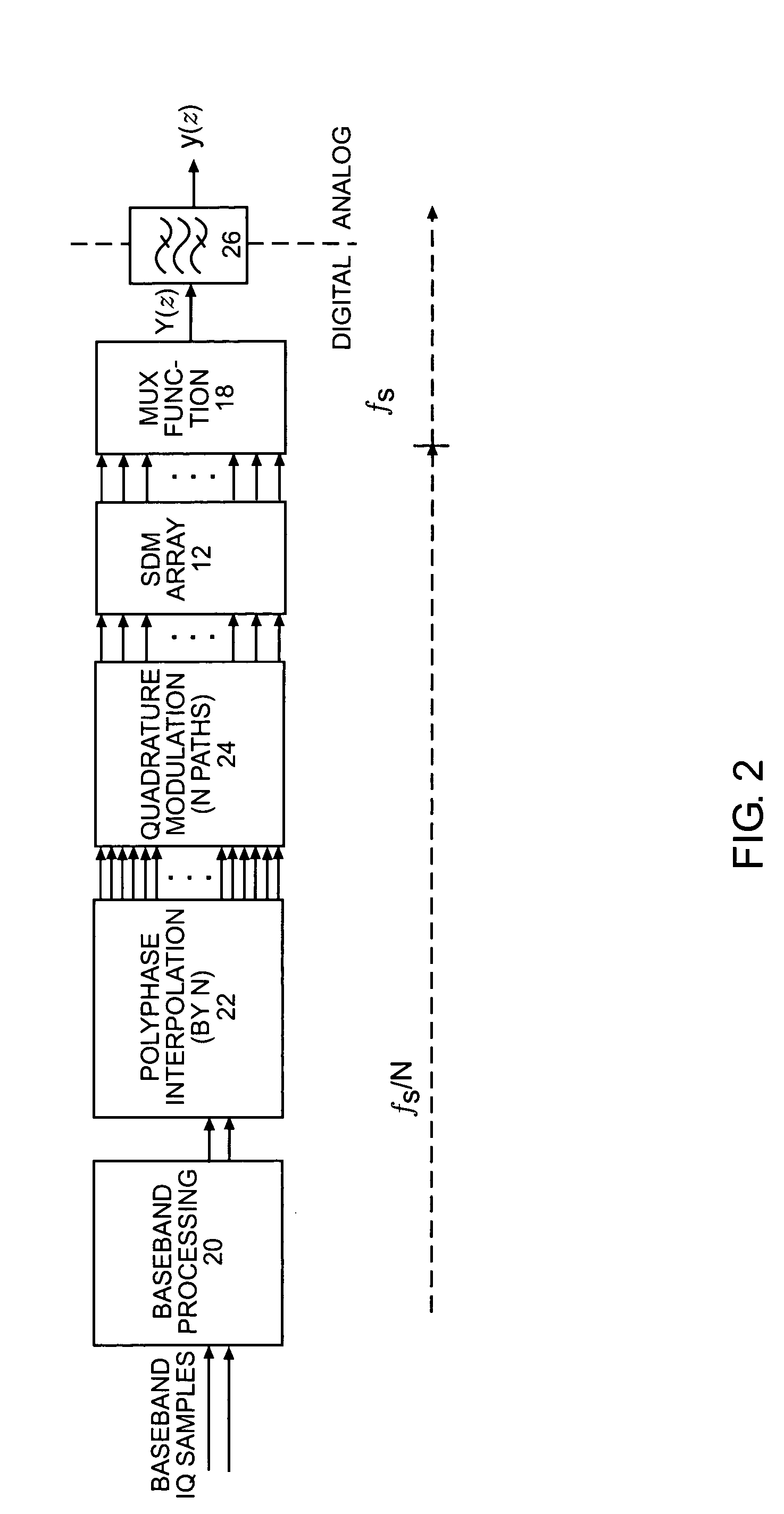

Multiple input sigma-delta architecture

InactiveUS7176820B1Effectively operating at high than traditional operating rateEnhanced output signalElectric signal transmission systemsAnalogue conversionProcess errorDelta modulation

A number of parallel modulation functions are configured to provide sigma-delta modulation on a plurality of low sampling rate signals, which are representative of a high sampling rate input signal. Resultant sigma-delta modulated signals from each of the modulation functions are combined in a multiplexing fashion to create a high sampling rate output signal. The modulation functions may be interdependent, wherein error signals from the modulation functions are provided to a parallel block digital filter, which will provide a processed error signal to feed back into the input of each modulation function. The processed error signal for a given modulation function may be a function of the error signals derived from multiple ones of the modulation functions. In one embodiment, there are N modulation functions, and the operating rate of the modulation functions is fs / N wherein the sampling rate of the high frequency output signal is fs.

Owner:APPLE INC

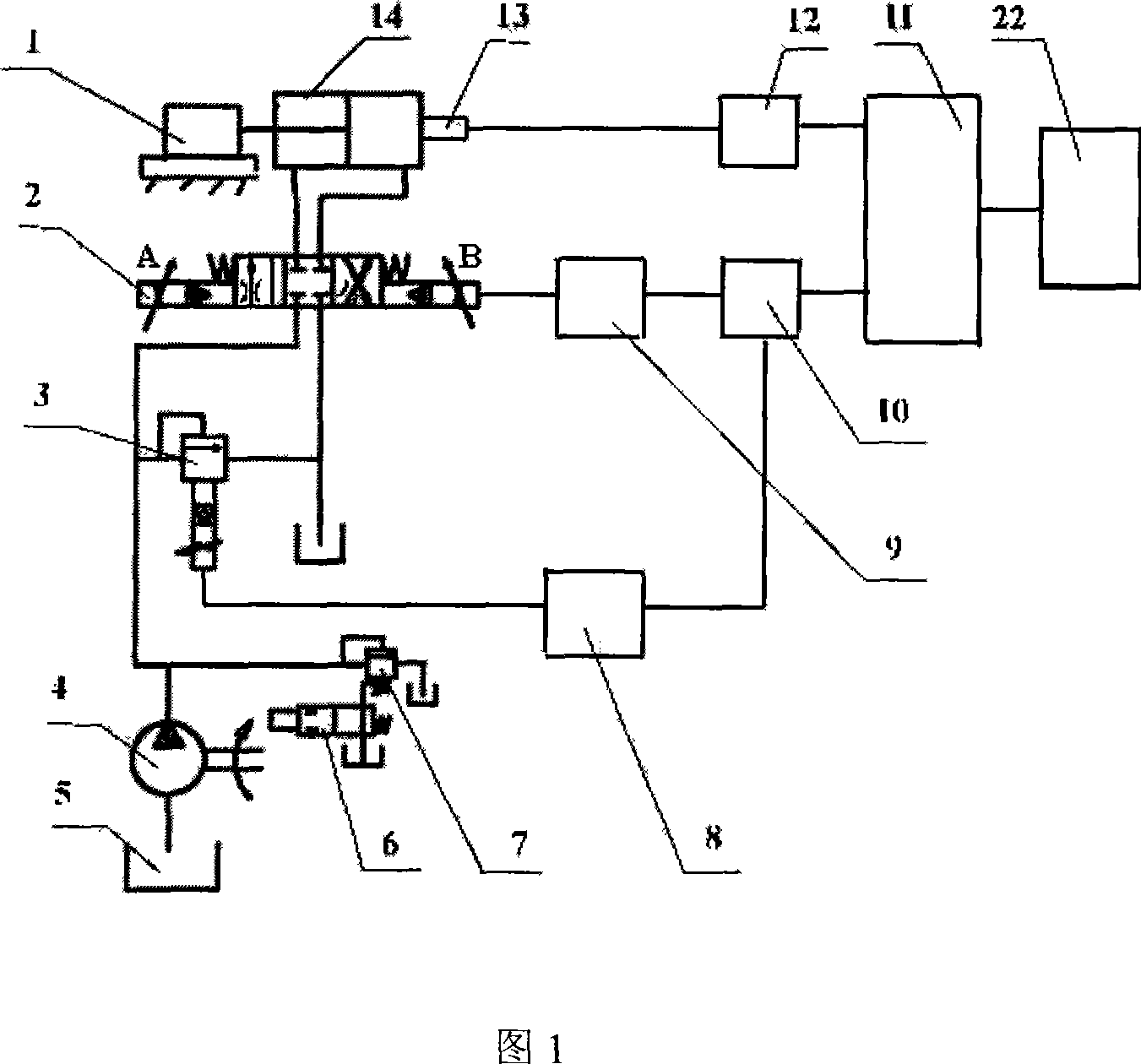

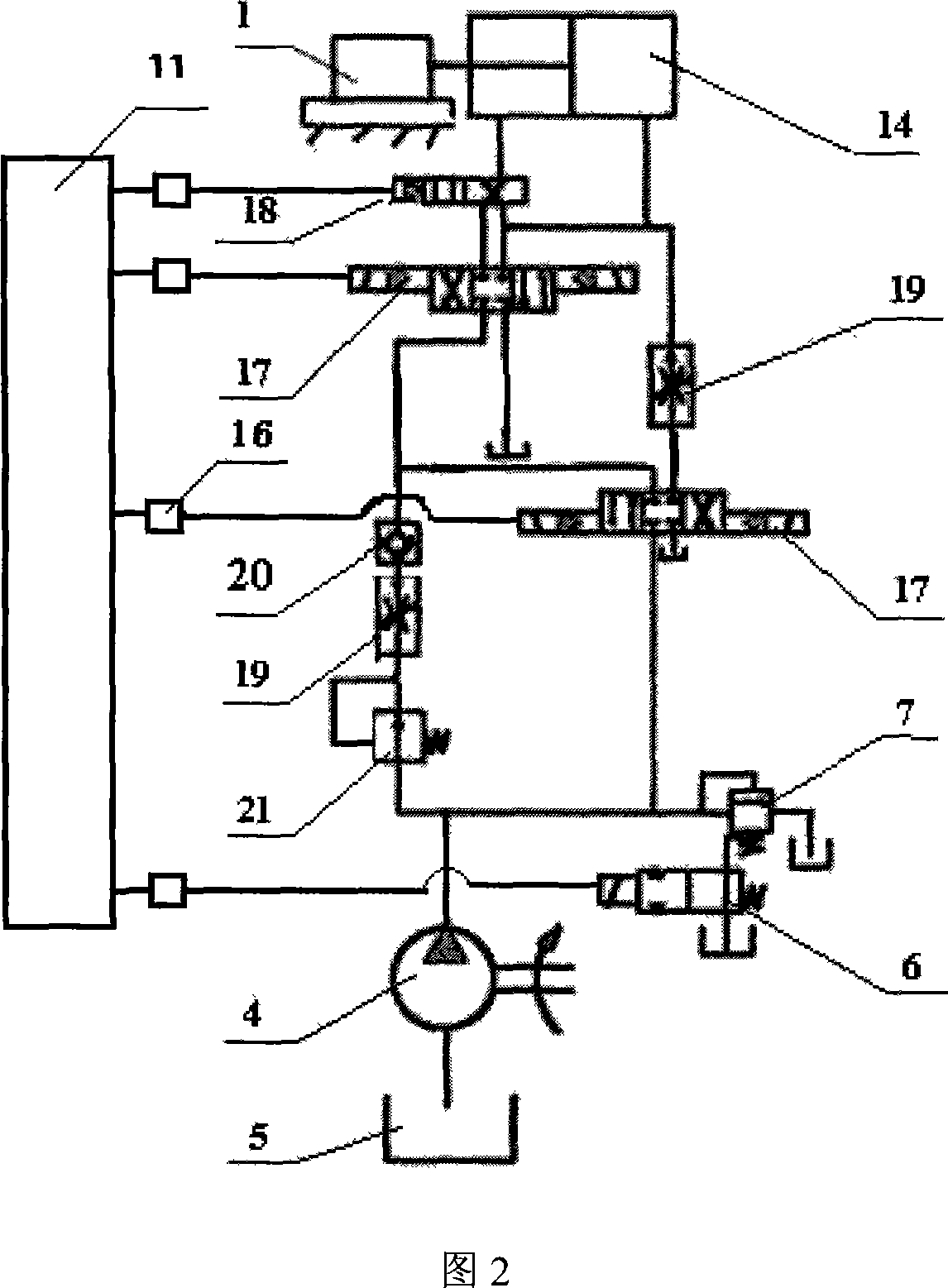

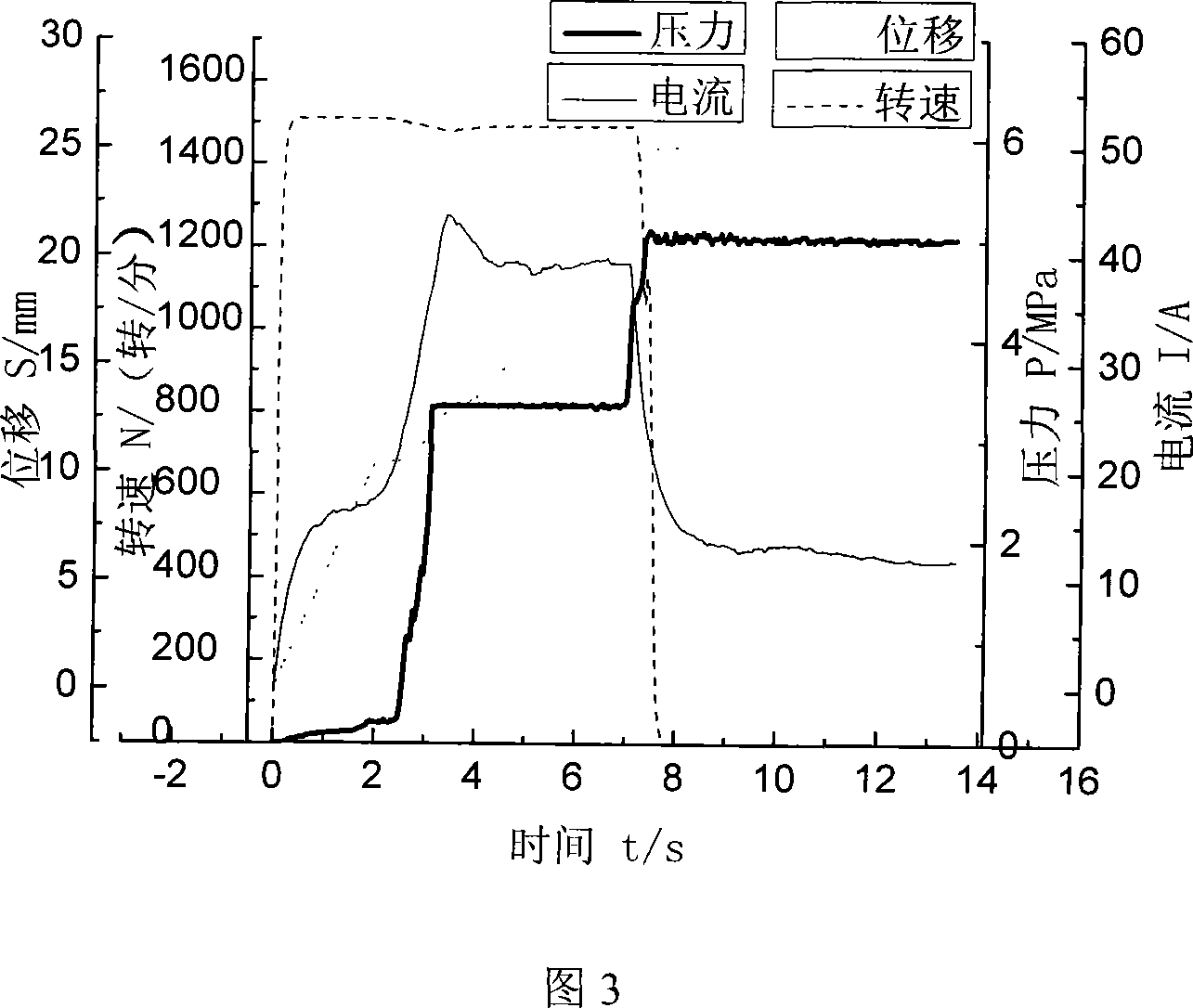

Friction welding machine closed loop control device

InactiveCN101059694AReduce usageLow costProgramme control in sequence/logic controllersNon-electric welding apparatusHuman–machine interfaceAxial pressure

The invention discloses a friction welding machine closed controller, comprising an electrohydraulic ratio steering speed-adjusting valve, an electrohydraulic ratio overflow valve, A and B power amplifying plates, a D / A module, an A / D module, a pressure sensor and a man-machine interface module, wherein the pressure sensor uses the AD module to convert the analogue signal of cylinder pressure value into digit signal, to be compared with a preset pressure value in a PLC controller and process error calculation, to adjust the overflow pressure of the electrohydraulic ratio overflow valve, to realize the axial pressure control of function cylinder, and the PLC controller receives the direction and speed command transmitted from the man-machine interface module, while the output digit signal via the DA module is converted into analogue signal, to adjust the pressure of the electrohydraulic ratio steering speed-adjusting valve to control the open direction and size of the valve, to realize the motion speed and direction controls of the cylinder piston. The invention uses the PLC controller with analogue amount and man-machine interface function to reduce the valves, accident and realize real-time closed control in welding process.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

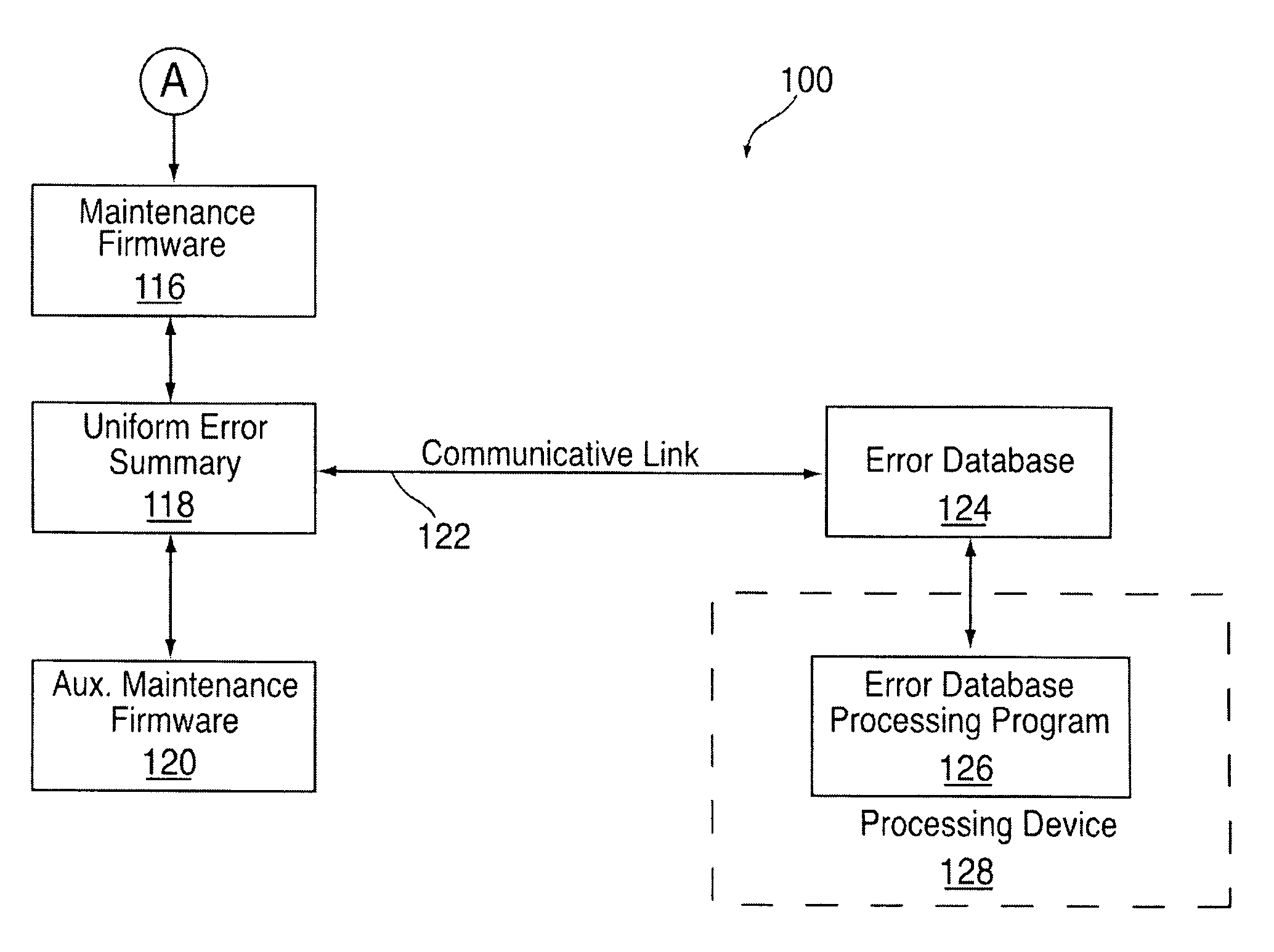

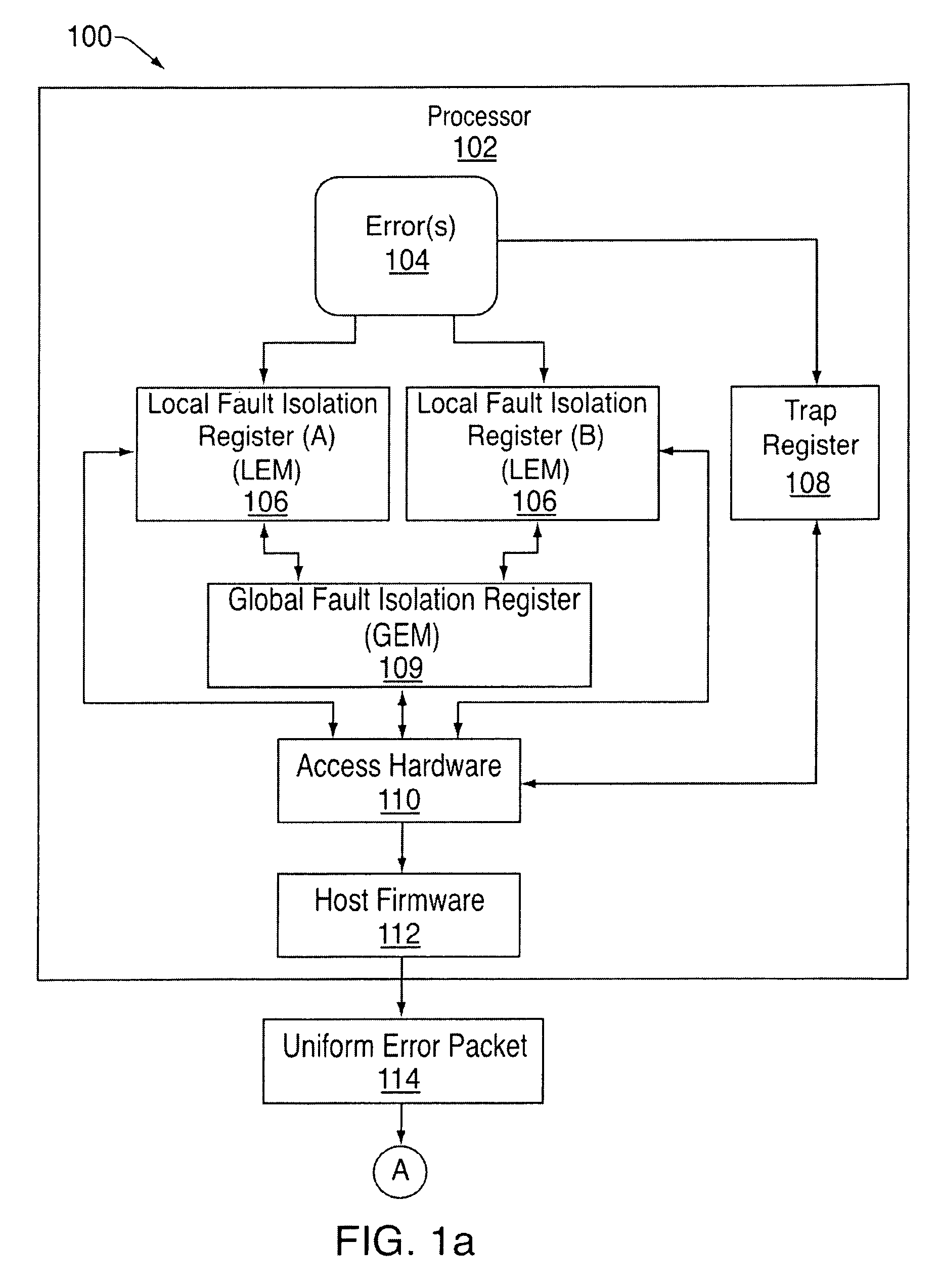

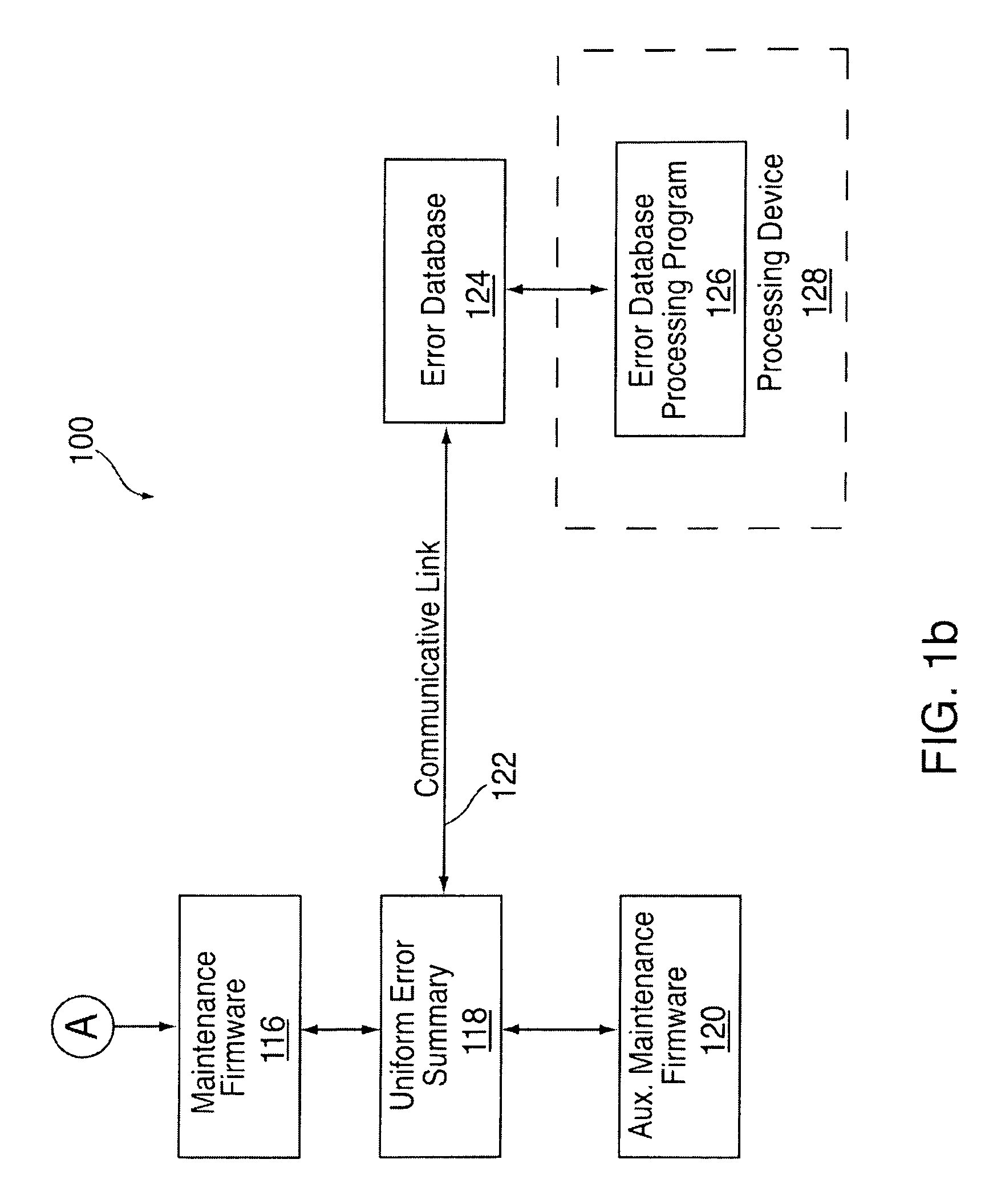

Method, system and computer program product for processing error information in a system

A system for processing errors in a processor comprising, a first register having a unique identifier operative to store a first error data, a processor operative to retrieve the first error data from the first register, associate the first error data with the unique identifier, and generate a first uniform error packet including the first error data and the unique identifier and a storage medium operative to store the first uniform error packet.

Owner:GLOBALFOUNDRIES INC

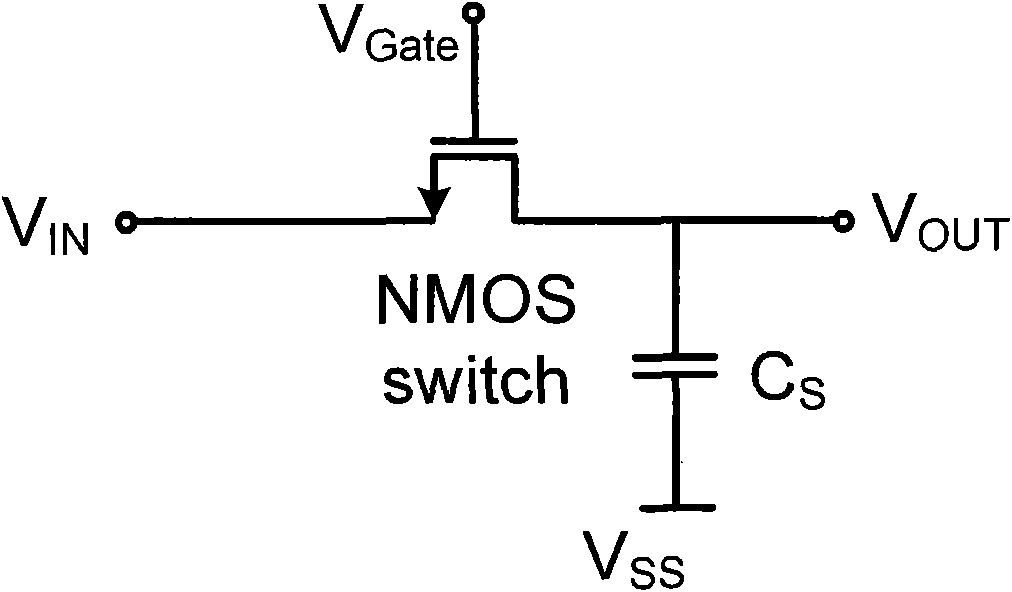

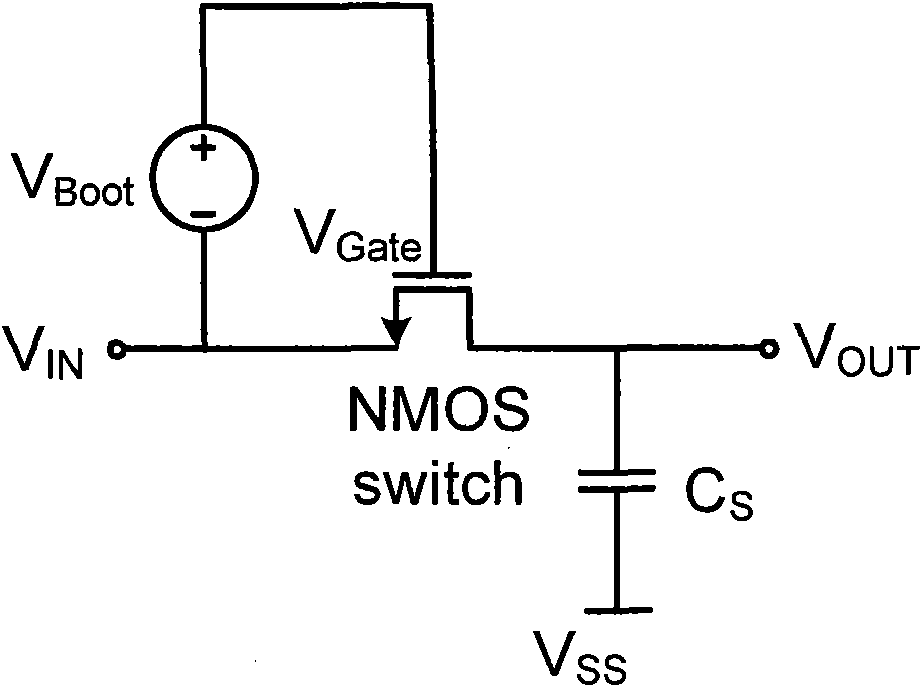

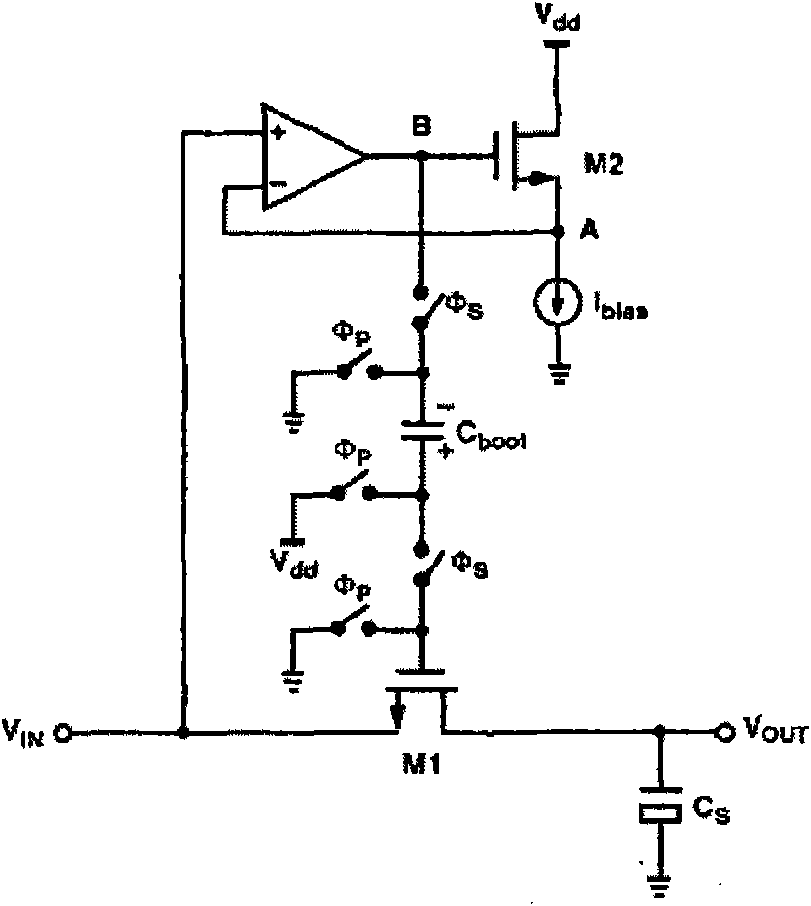

Dual bootstrap and voltage compensation technology-based A/D converter sampling switch

ActiveCN101577545AReduce power consumptionSolve nonlinear problemsElectric analogue storesElectronic switchingLow voltageProcess error

The invention discloses a dual bootstrap and voltage compensation technology-based A / D converter sampling switch, which comprises a primary switch unit used for a to-be-sampled signal channel to sample to-be-sampled signals, a underlayer voltage bootstrap unit for realizing the underlayer voltage bootstrap of a switching tube PMOS Switch in the primary switch unit, a grid voltage bootstrap unit for realizing the grid voltage bootstrap of the switching tube PMOS Switch in the primary switch unit, a storage unit for parallelly sampling input signals VIN and realizing the temporary storage of a VIN voltage, and a voltage compensation unit for compensating the sampling output voltage of an output end VOUT. The invention provides a sampling switch which is capable of working at low voltage and low power consumption and is insensitive to process errors. Meanwhile, the adopted voltage self-compensation method effectively solves a nonlinear problem caused by clock feedthrough occurring after the grid voltage bootstrap of the switching tube.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

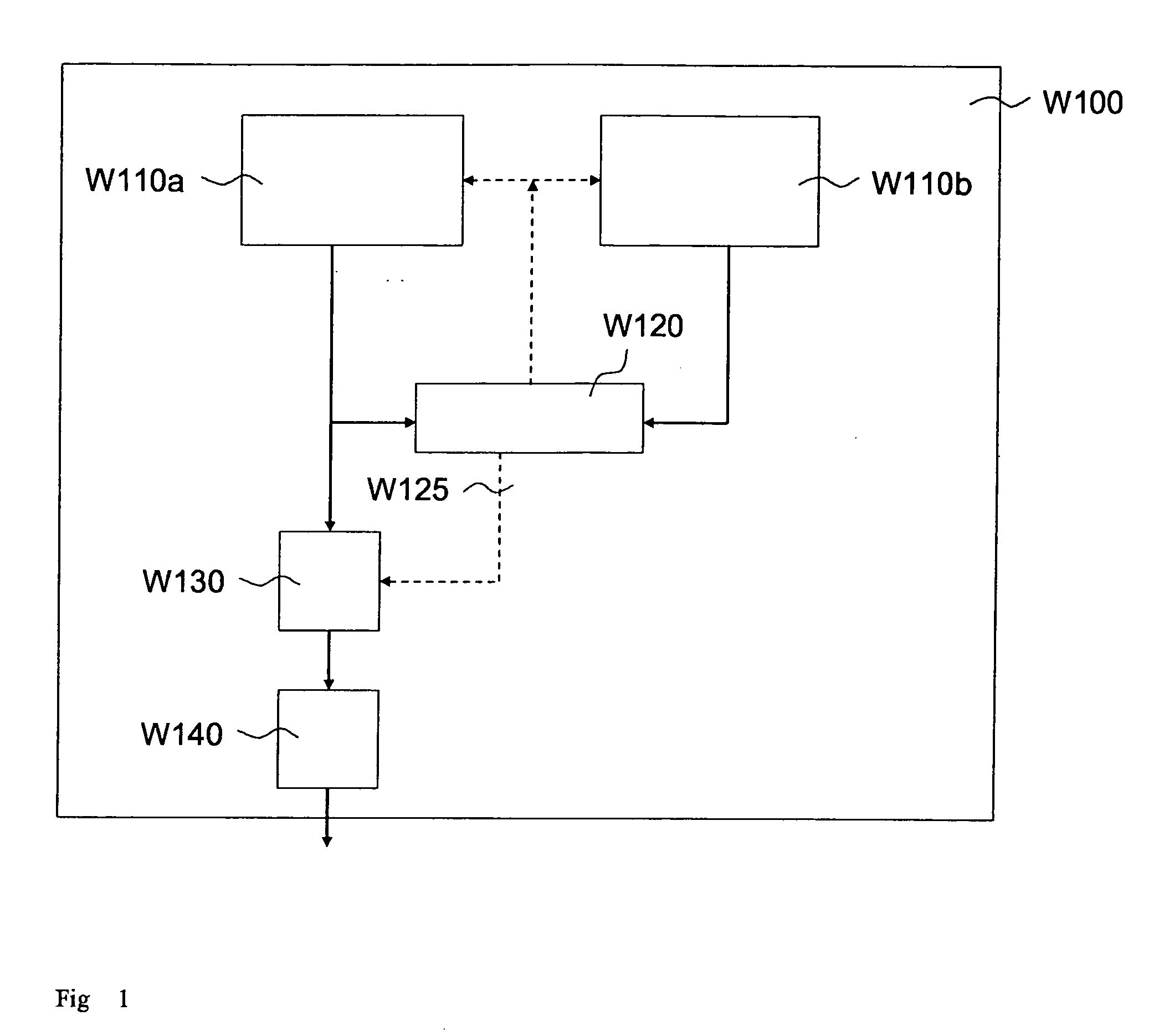

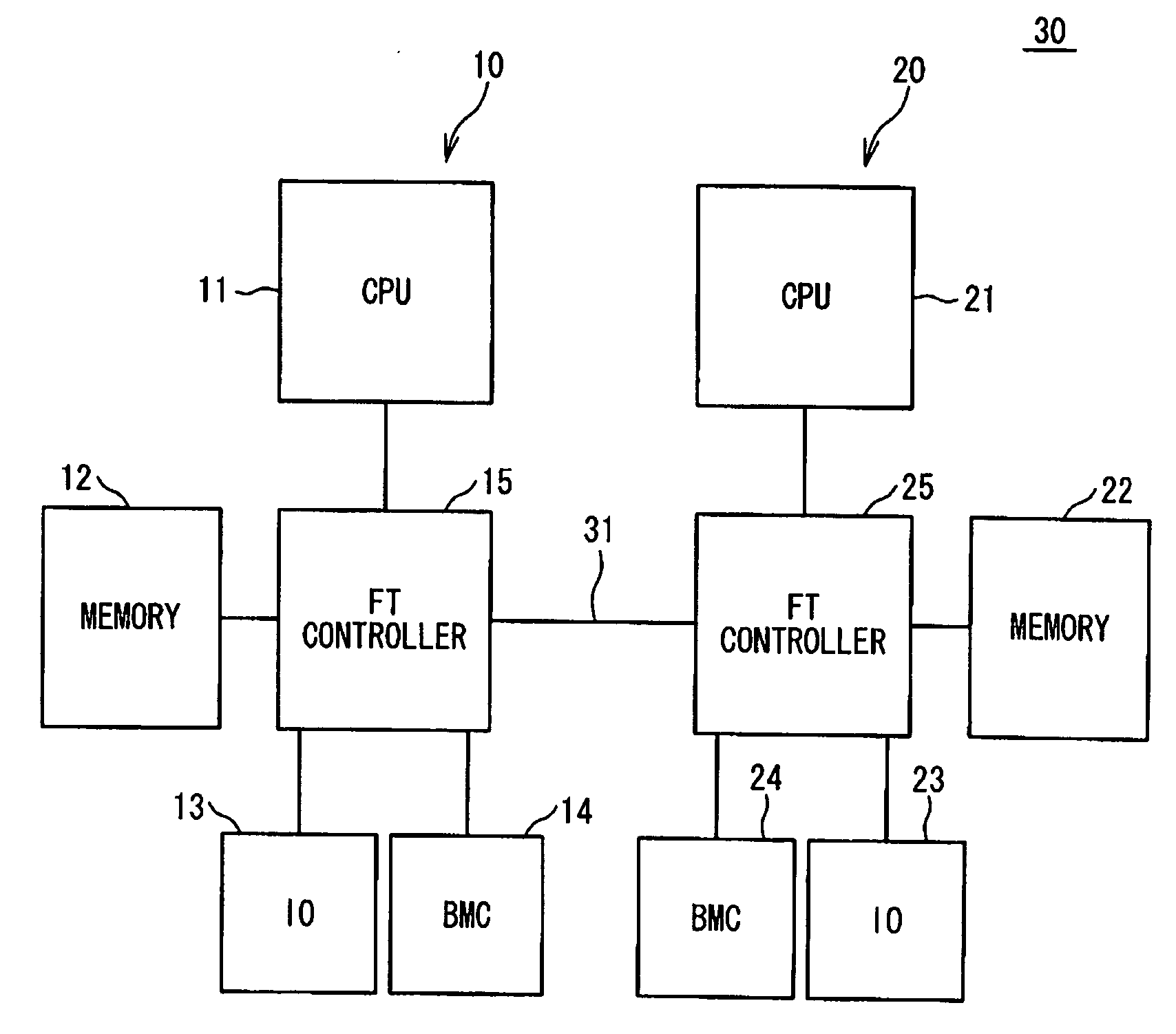

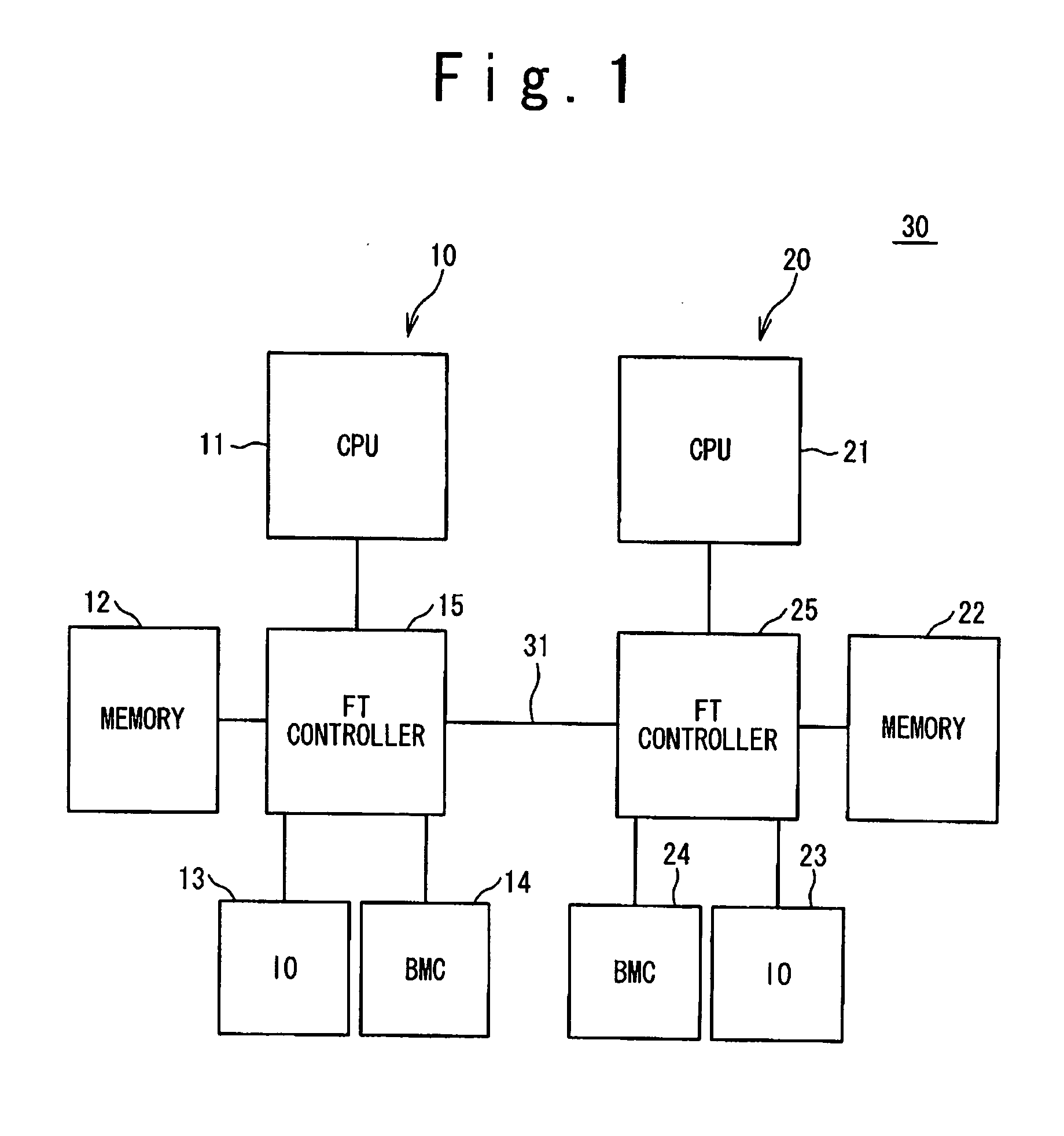

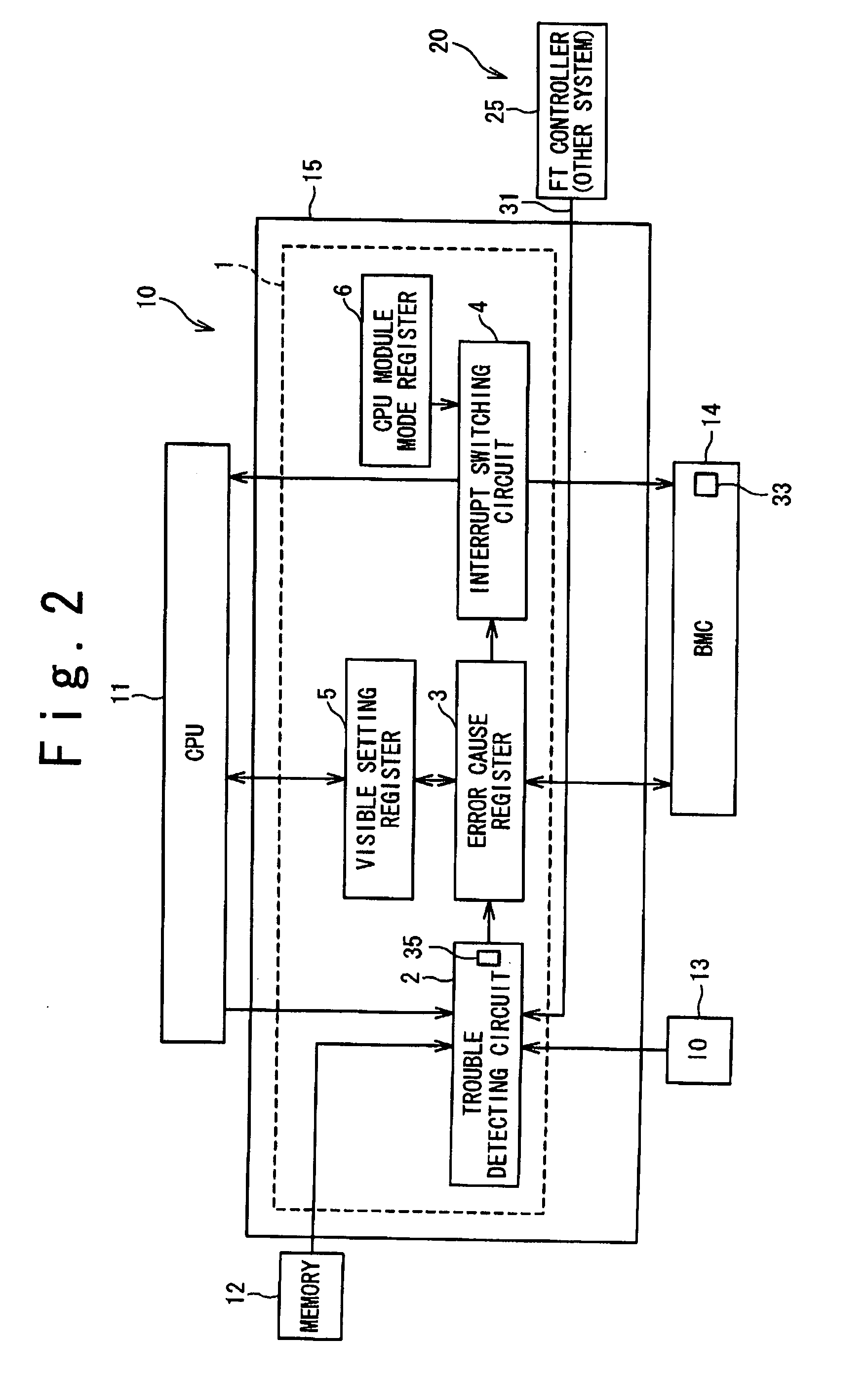

Computer system and method for dealing with errors

A computer system includes a plurality of systems configured to be connected to each other by links and to operate synchronously each other. Each of said plurality of systems includes a fault tolerant controller, a CPU, a baseboard management controller and a plurality of hardware modules. The CPU is connected with the fault tolerant controller. The baseboard management controller is connected with the fault tolerant controller. The plurality of hardware modules is connected with the fault tolerant controller. When receiving a trouble which occurs in any of the plurality of systems, the fault tolerant controller outputs an interrupt regarding the trouble to at least one of the CPU and the baseboard management controller predetermined correspondingly to the trouble.

Owner:NEC CORP

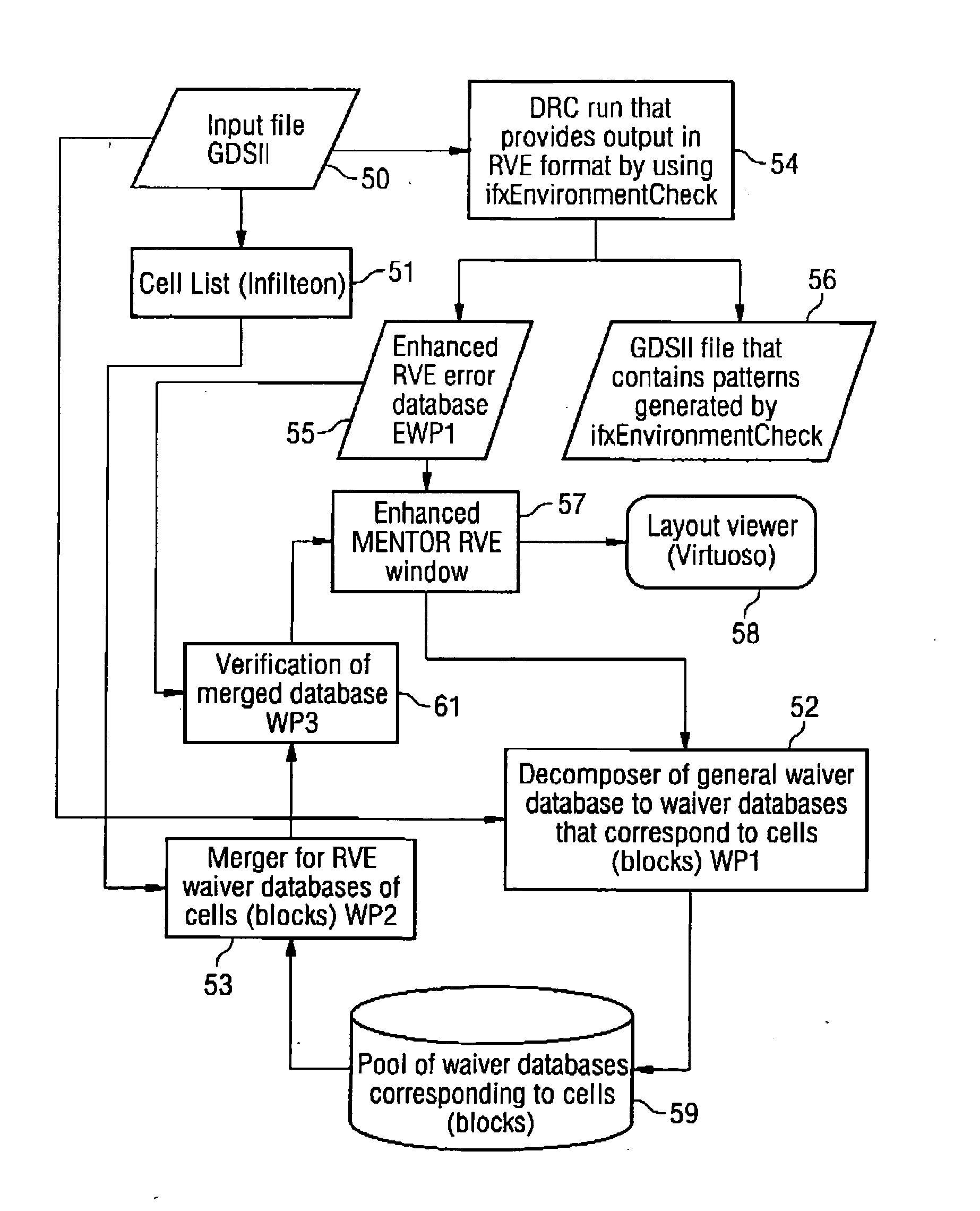

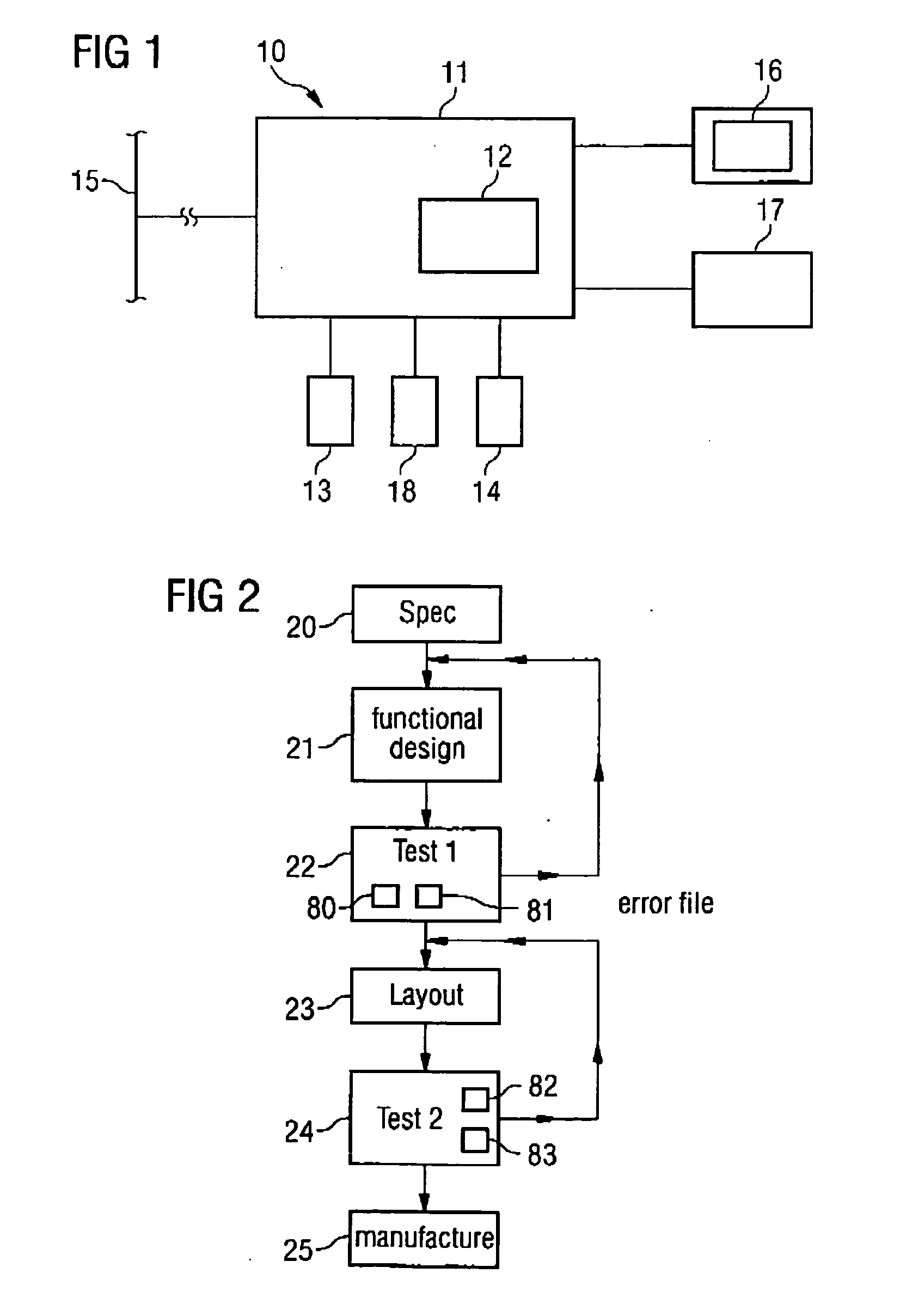

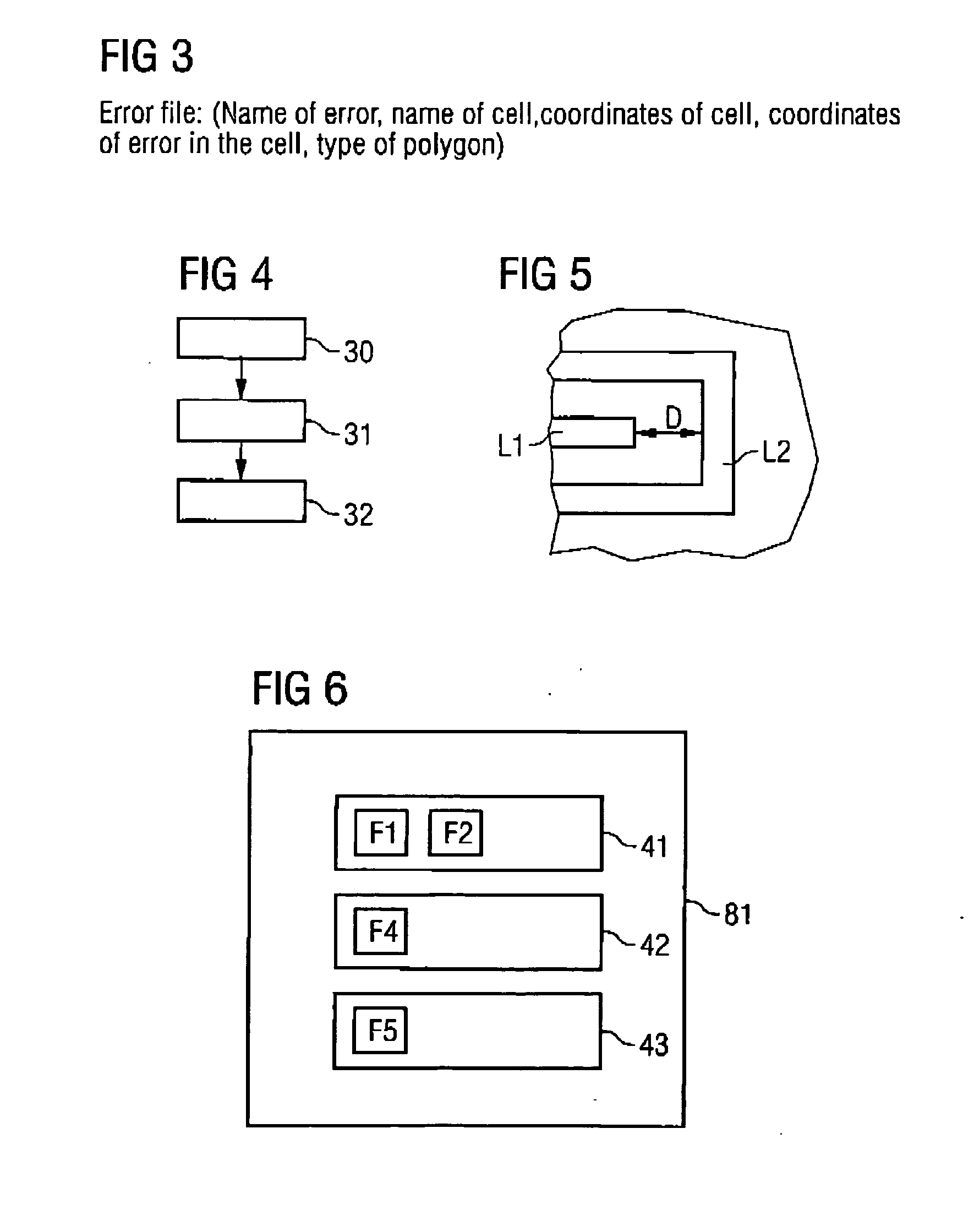

Method for treating design errors of a layout of an integrated circuit

InactiveUS20070192754A1Computer aided designSoftware simulation/interpretation/emulationProcess errorEngineering

Embodiments of the invention provide a method for treating errors during the checking of a design of an integrated circuit. In one embodiment, the method includes checking the design of the integrated circuit for errors using predetermined design rules, wherein the design includes a plurality of cells, detecting a design error when the design deviates from the predetermined design rules, writing the design error into a design error file, wherein at least one detected design error is written into a design waiver file if the design error is allowed as an allowed design error in spite of the deviation from the predetermined rules, and storing the allowed design error in the design waiver file with specification of a cell in which the design error occurs.

Owner:INFINEON TECH AG

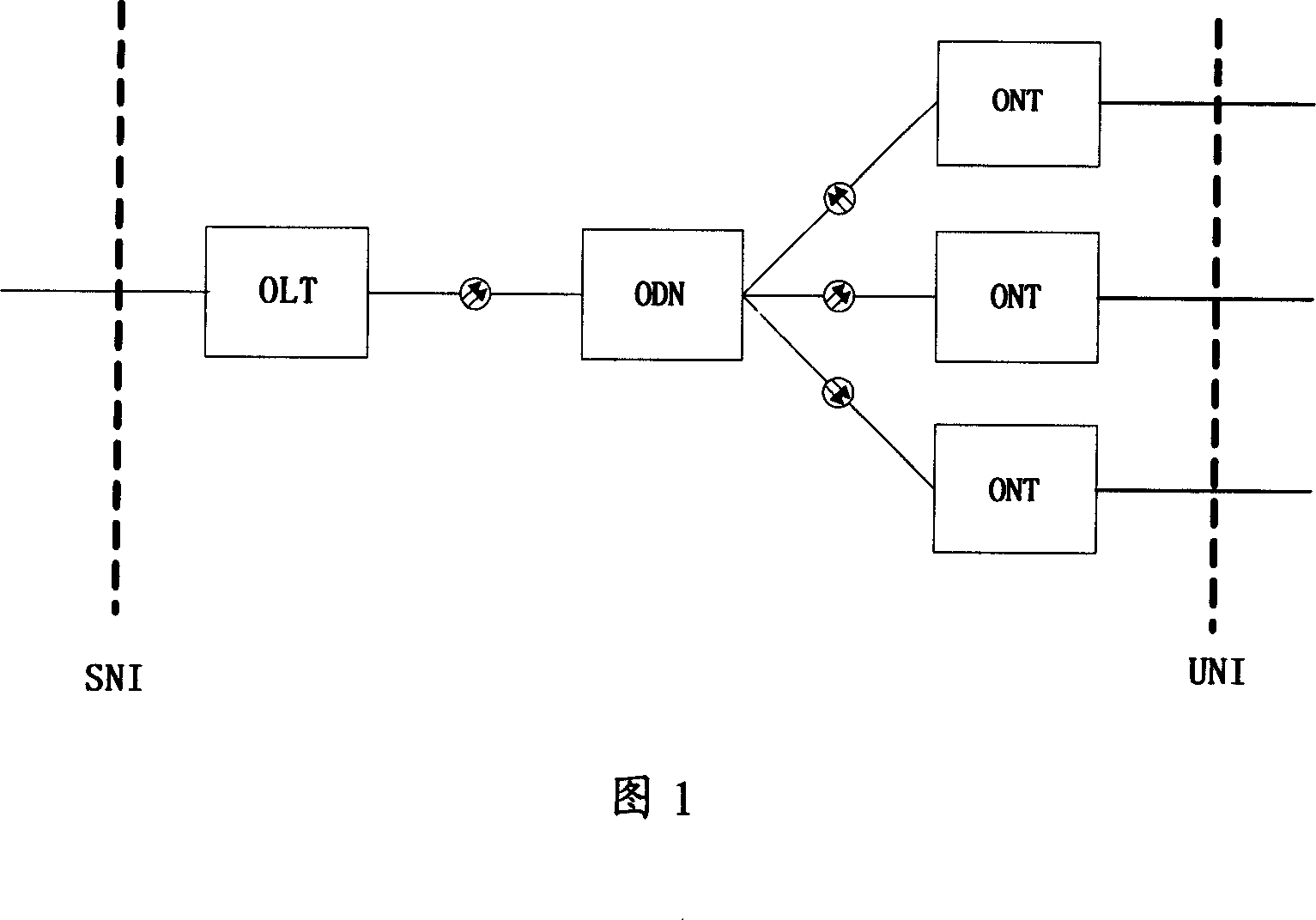

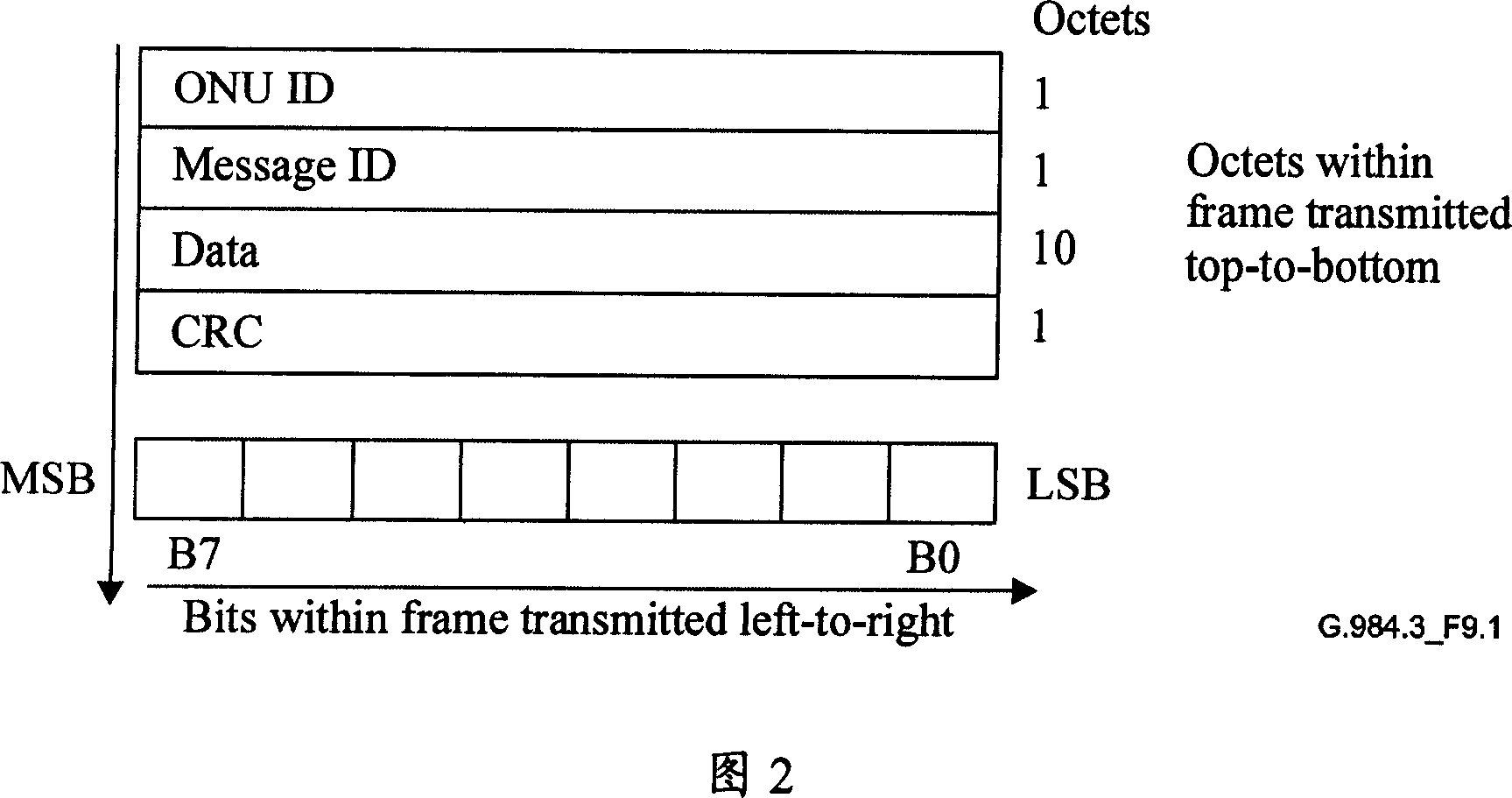

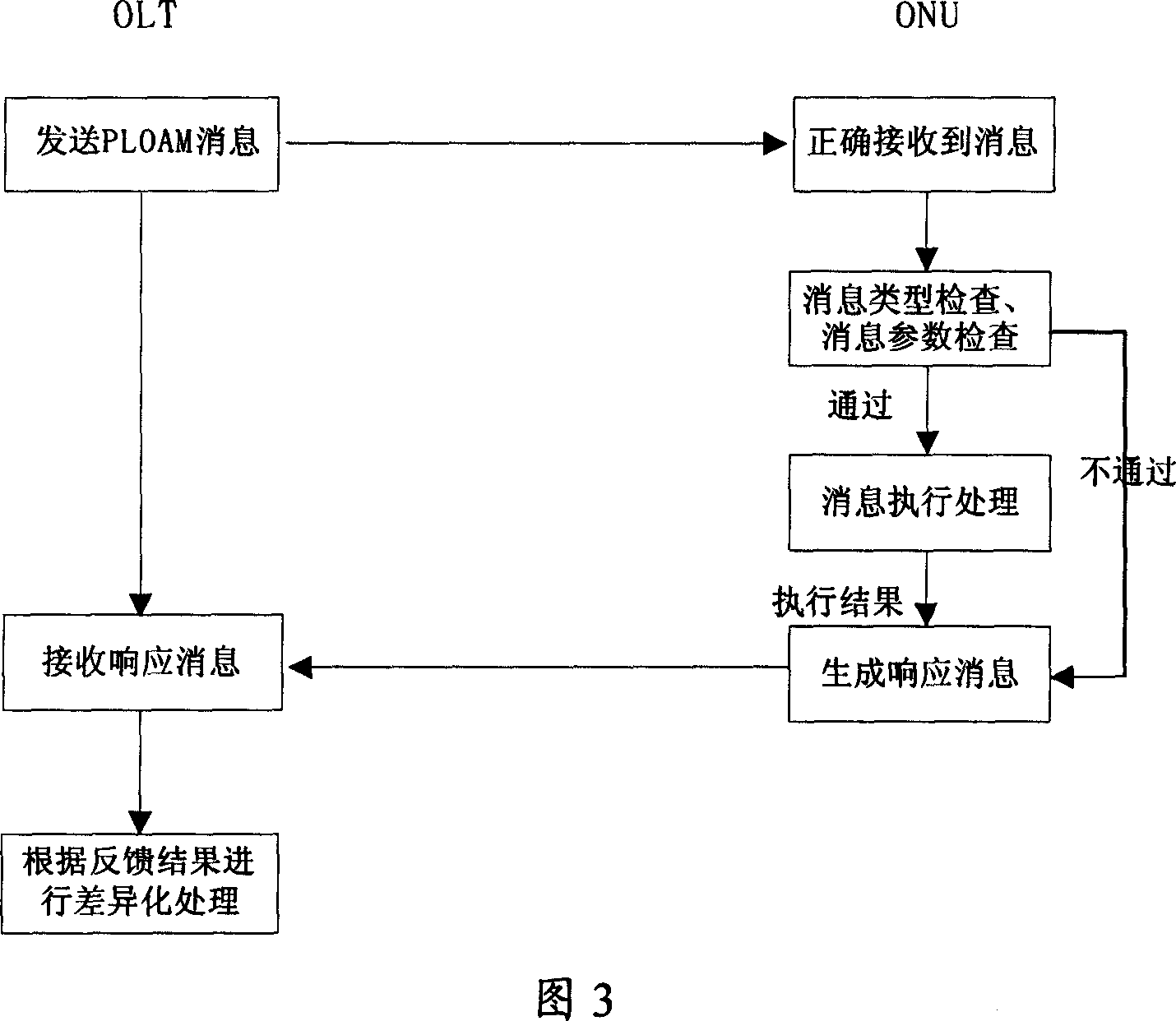

A method and system for solving the errors under the PON PLOAM system

ActiveCN101060369AAvoid inconsistenciesAvoid wastingMultiplex system selection arrangementsTransmission monitoring/testing/fault-measurement systemsProcess errorDependability

The provided PON PLOAM based error process method comprises: 1. the optical terminal sends PLOAM message to the optical network unit; 2. the optical network unit processes the received message; 3. the optical network unit generates the response message as results; and 4. the terminal receives response from network, and takes differential process according to the feedback message. This invention avoids error and resource waste led by difference between network terminal and network unit, and improves system reliability and utility.

Owner:HUAWEI TECH CO LTD

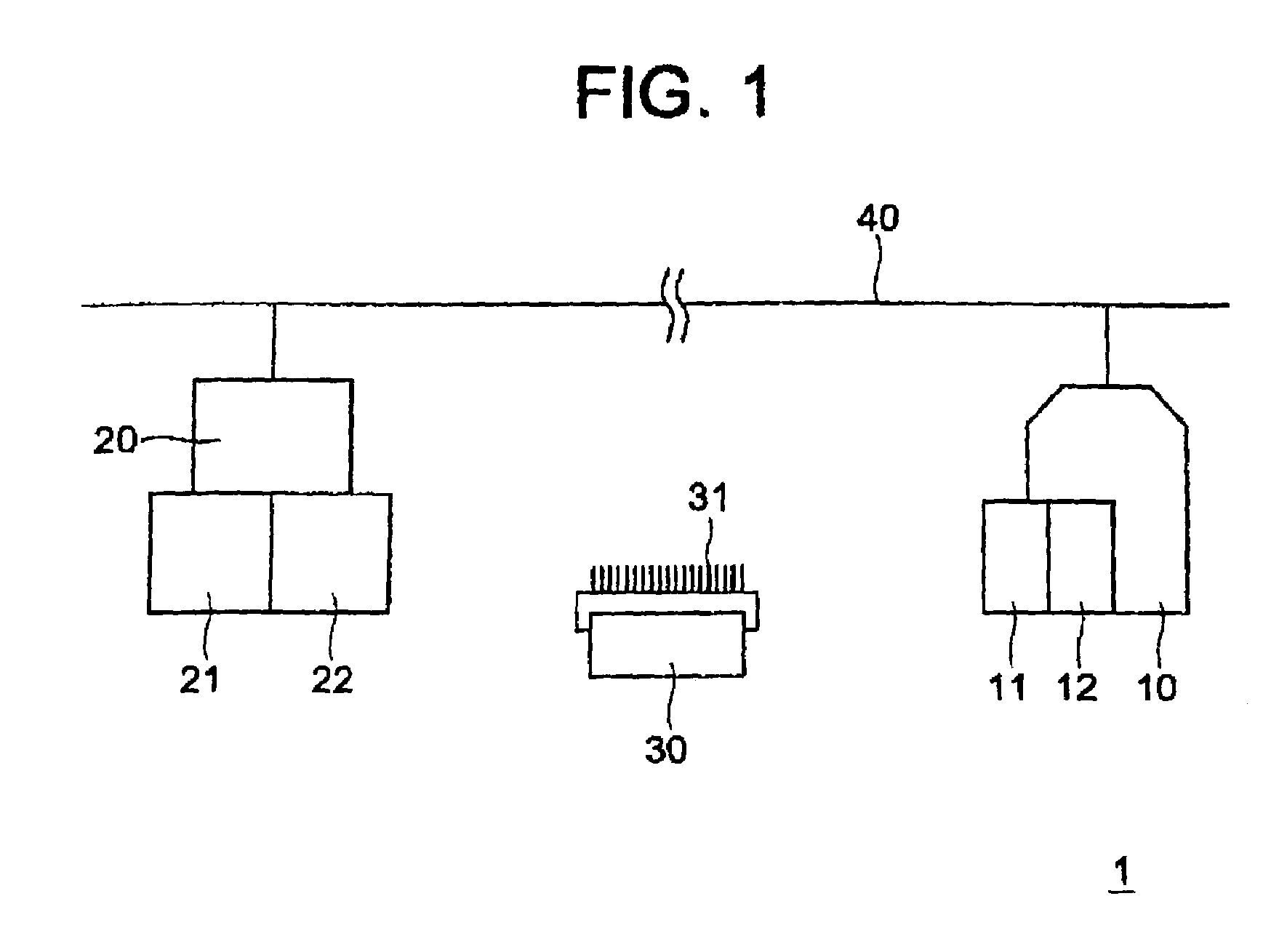

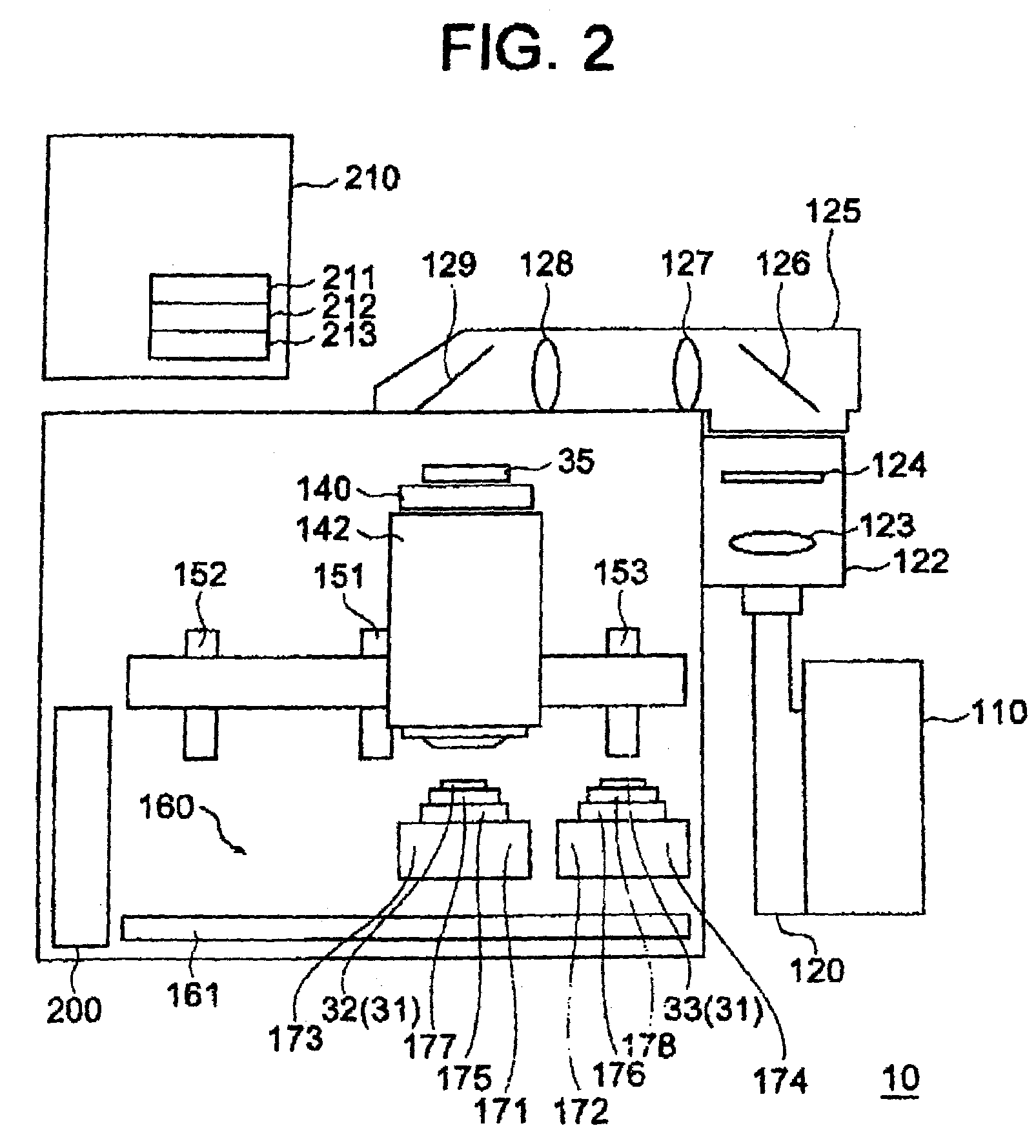

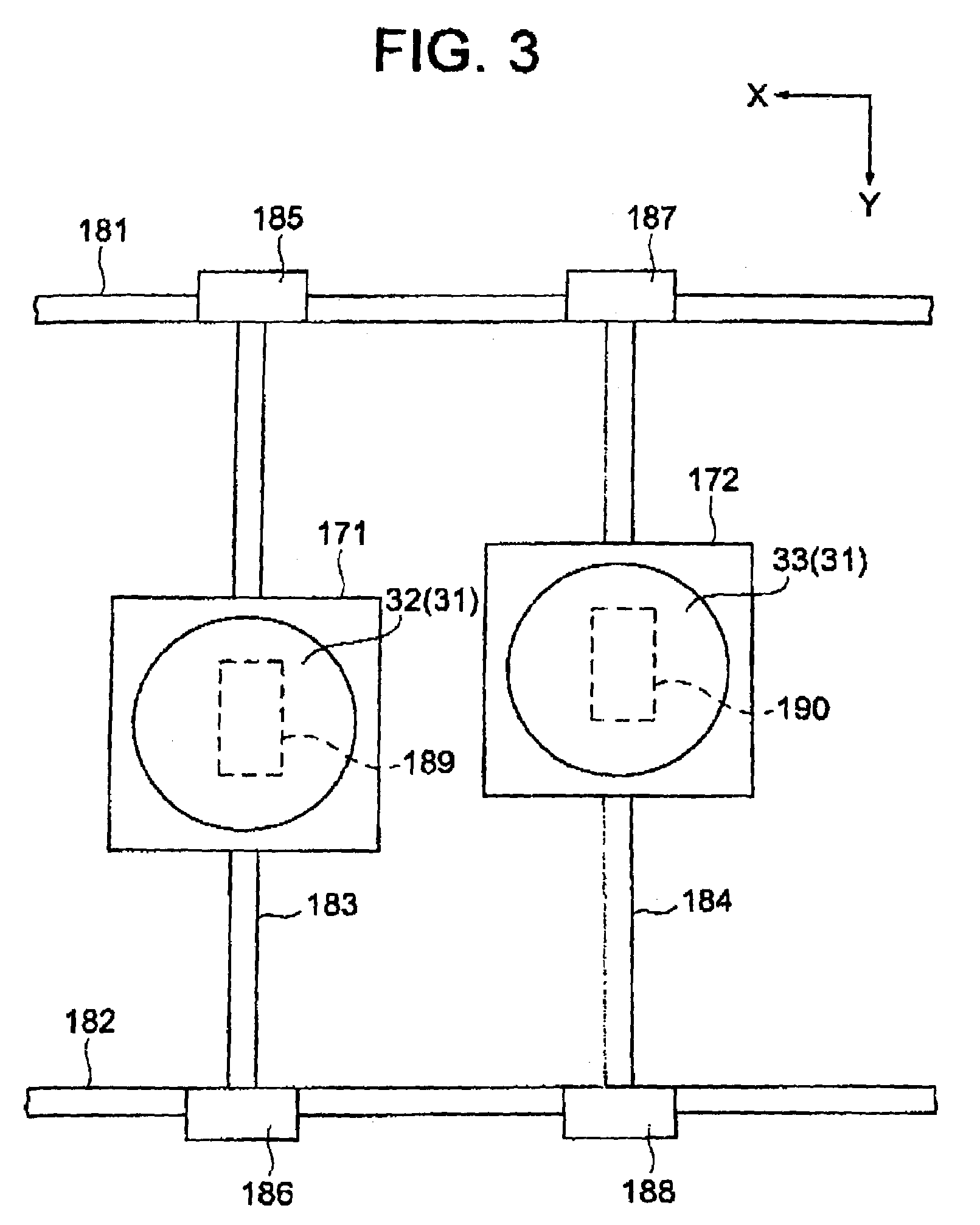

Exposure method, exposure apparatus, and method of production of device

InactiveUS7001674B2Accumulation of error and extremeError and extreme in overlay accuracyPropellersSemiconductor/solid-state device manufacturingProduction lineProcess error

An exposure method for preventing accumulation of process error for substrates processed by an apparatus designed for multiprocessing and producing high quality semiconductor chips. A semiconductor integrated circuit production line polishes wafers of individual lots at a first processing system and second processing system of a CMP system two at a time. Wafer processing information indicating at which processing system of the first processing system and second processing system each wafer has been processed is transmitted through a communication line to a later processing apparatus including an exposure apparatus. The wafers of a lot loaded in the exposure apparatus are allocated to a plurality of processing systems of the exposure apparatus so that wafers processed by the same processing system are processed by the same processing system among the two processing systems of the exposure apparatus and are exposed at those processing systems.

Owner:NIKON CORP

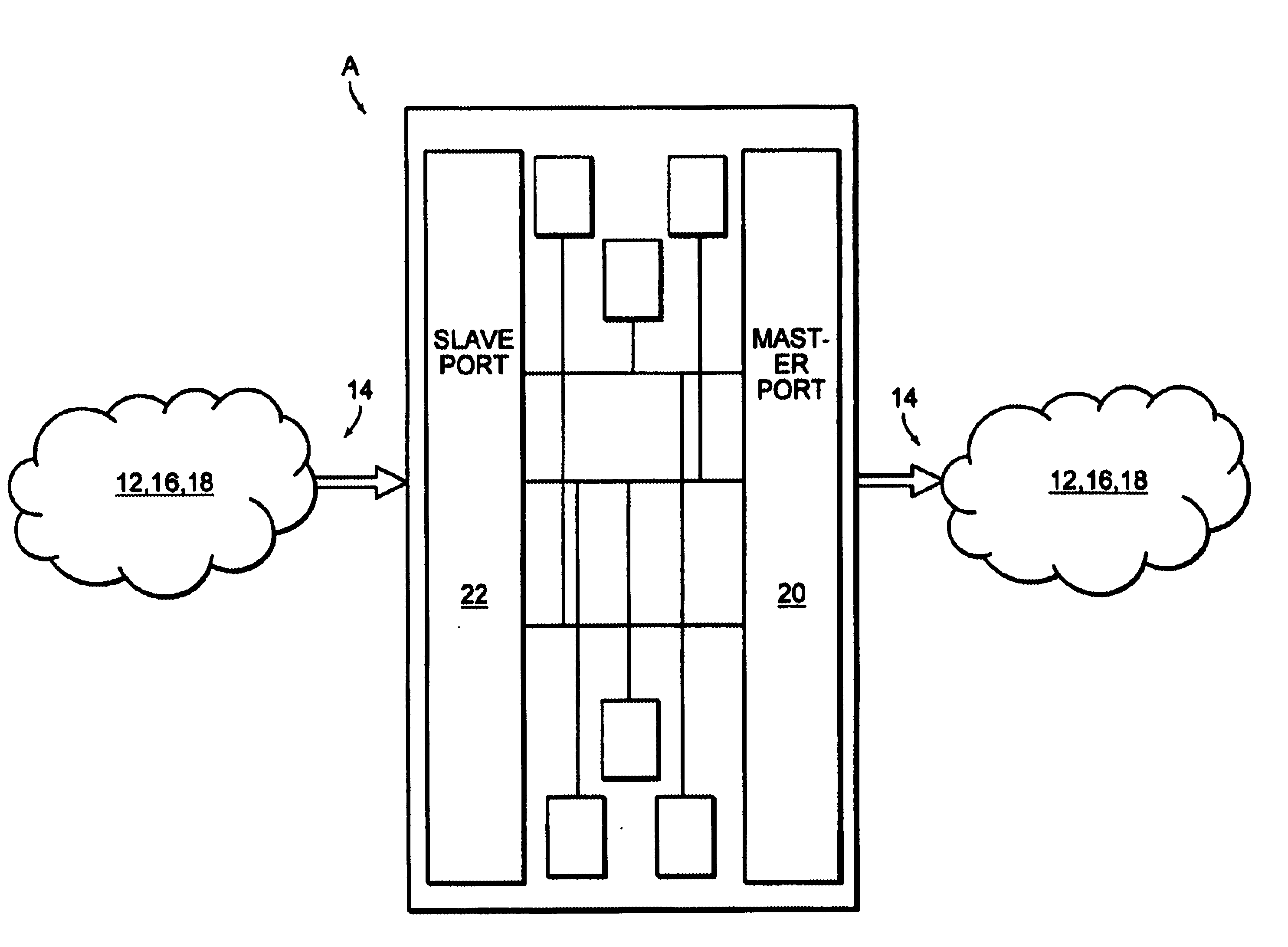

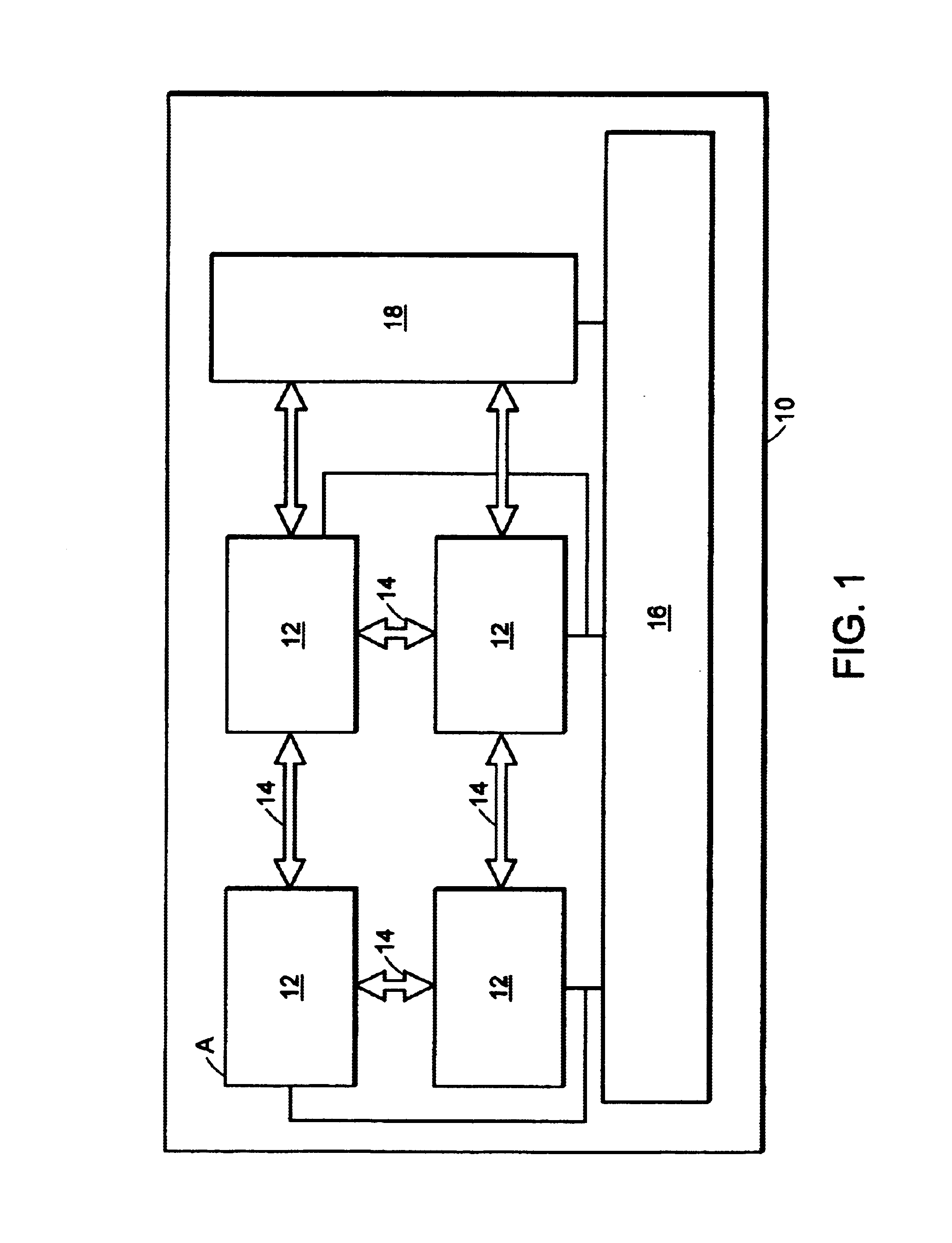

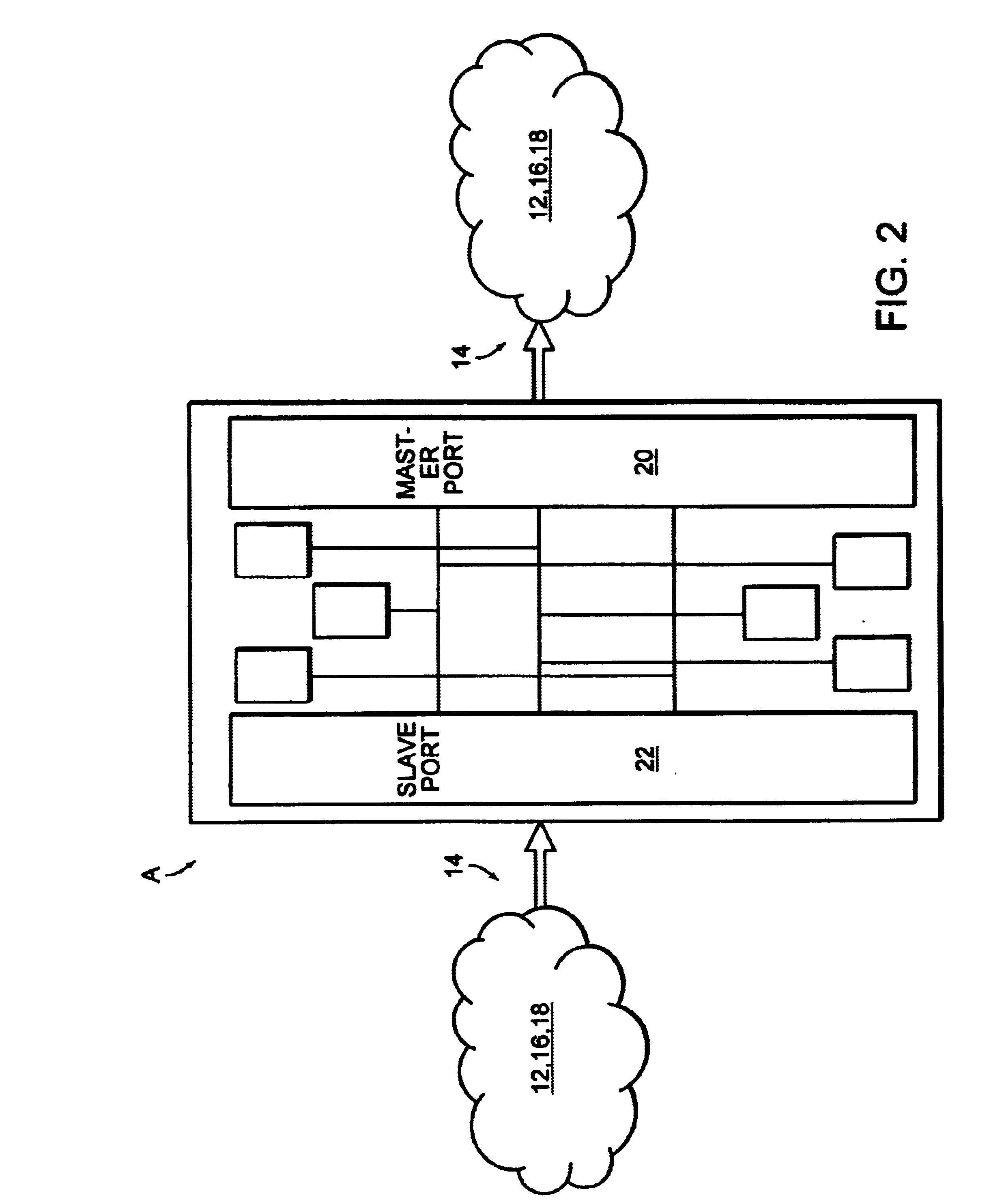

High speed access bus interface and protocol

InactiveUS6778526B1Fast transferSync fastNetworks interconnectionElectric digital data processingData streamBus interface

A high speed access bus interface for a communications network. The interface allows uni-directional transfer of data packets at a fast path processing rate of about 10 gigabits per second. The interface uses a master port and a slave port in a chip to chip data transfer scheme. The master and slave ports may have one or more than one data channel for transferring data packets. The master port includes a clock signal for synchronizing the transfer from the master port to the slave port. The slave may send an asynchronous signal to the master port in order to initiate the master port to stop or stall the pipeline transfer of data packets until space is made available in the slave port buffer. In addition to the clock synchronization, the interface utilizes an enable signal, a start of packet signal, an end of packet signal, an error signal (if necessary), a last valid byte signal, and a parity bit signal to identify, address, each data packet in the data stream. If a processing error occurs, the master port error signal to the slave port also initiates the slave port to disregard the previous data packet. The operating frequency of 50 MHz allows the data packet transfer to exceed 10 gigabits per second.

Owner:AVAYA MANAGEMENT LP

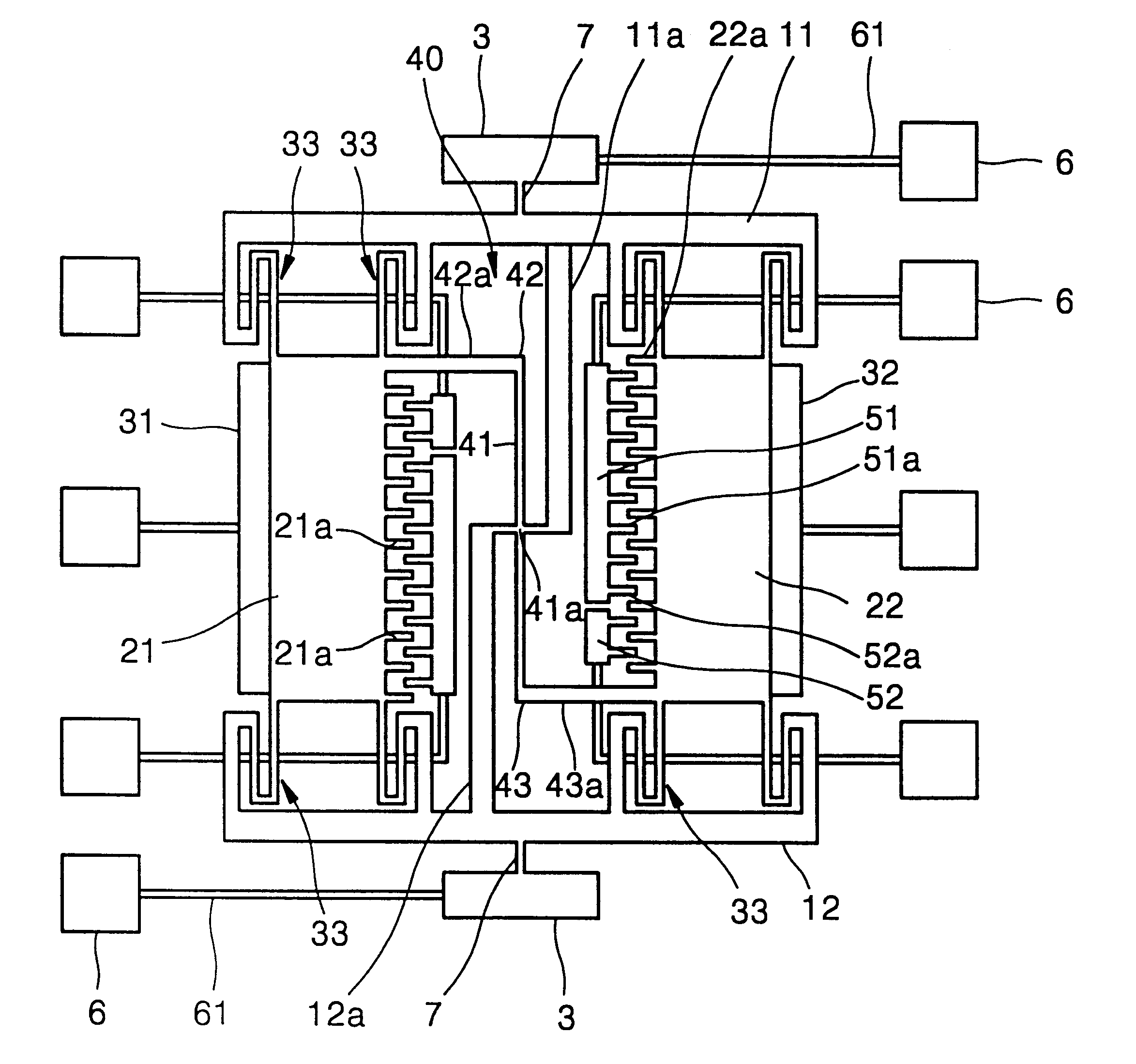

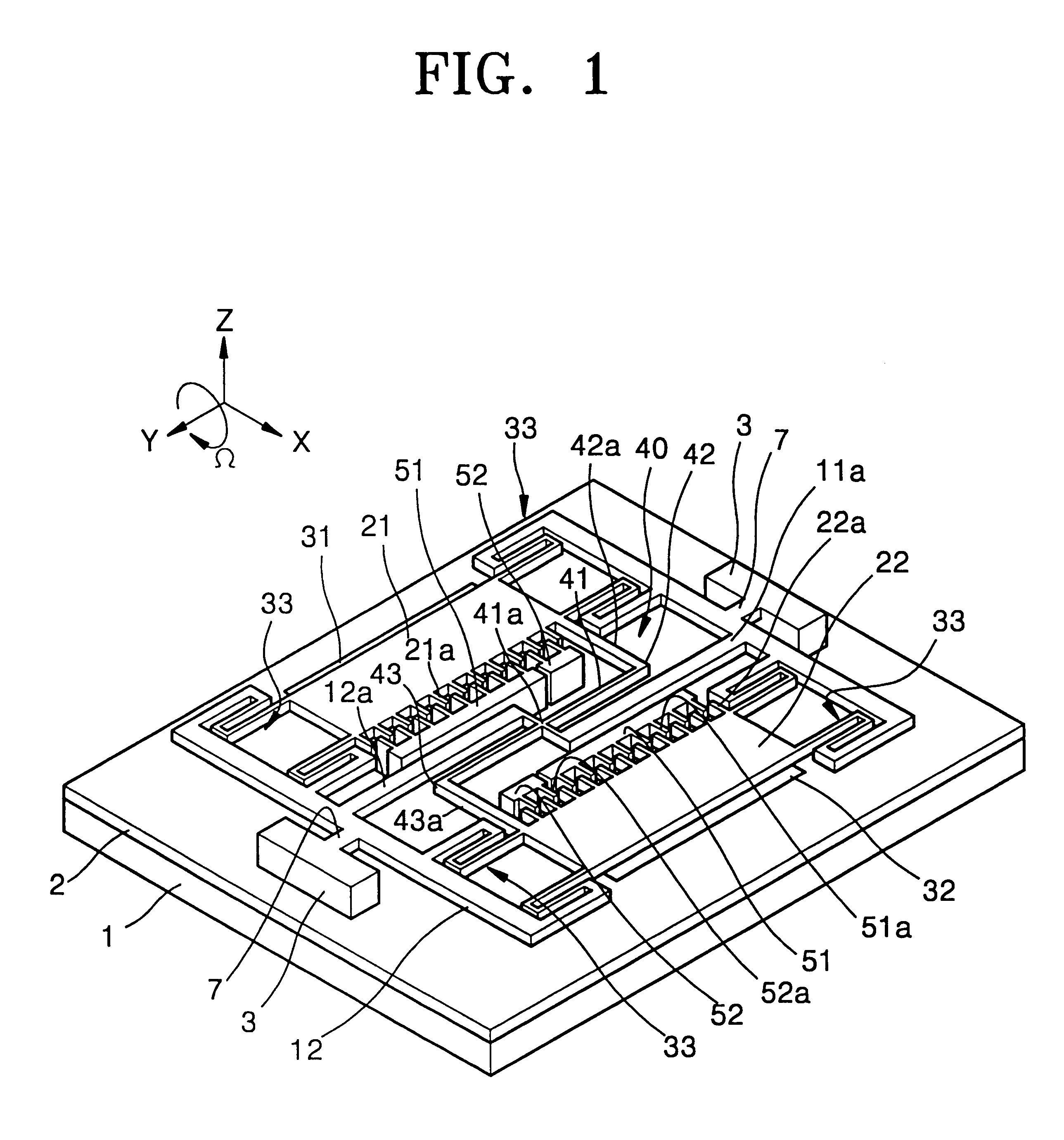

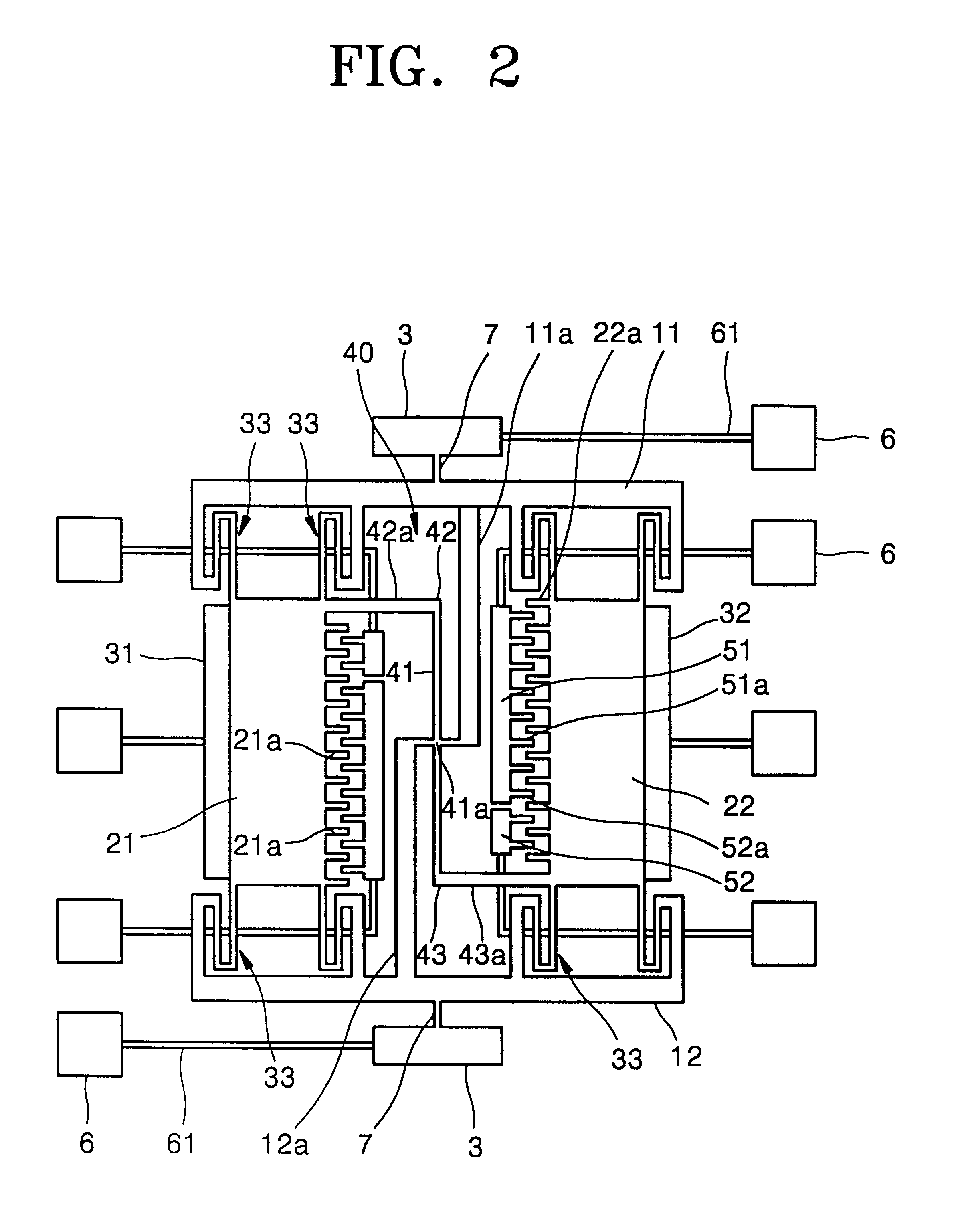

Microgyroscope with two resonant plates

InactiveUS6467348B1Lower manufacturing requirementsGood reproducibilityAcceleration measurement using interia forcesSolid-state devicesGyroscopeResonance

A microgyroscope with two resonant plates is provided. The microgyroscope includes a substrate; first and second frames provided on the substrate to have a predetermined height, the first and second frames facing each other; a plurality of anchors supporting the first and second frames with respect to the substrate; first and second resonant plates provided between the first and second frames to be separated from each other by a predetermined distance; and a matching link unit connected to the first and second resonant plates so that it links the motion of one resonant plate to the motion of the other resonant plate such that the matching link unit is moved by the motion of one resonant plate in a first direction and then moves the other resonant plate in a second direction opposite to the first direction. In the microgyroscope, the difference between the resonance frequencies of the two resonant plates is removed by a self resonant matching structure implemented by the matching link, so that the range of an allowable process error is large, and the microgyroscope can be easily manufactured. Additionally, the reliability and the linearity of a resonance structure are improved. Since the driving beam and the sensing beam are separately designed, mode coupling can be prevented, thereby increasing the sensing sensibility.

Owner:SAMSUNG ELECTRONICS CO LTD

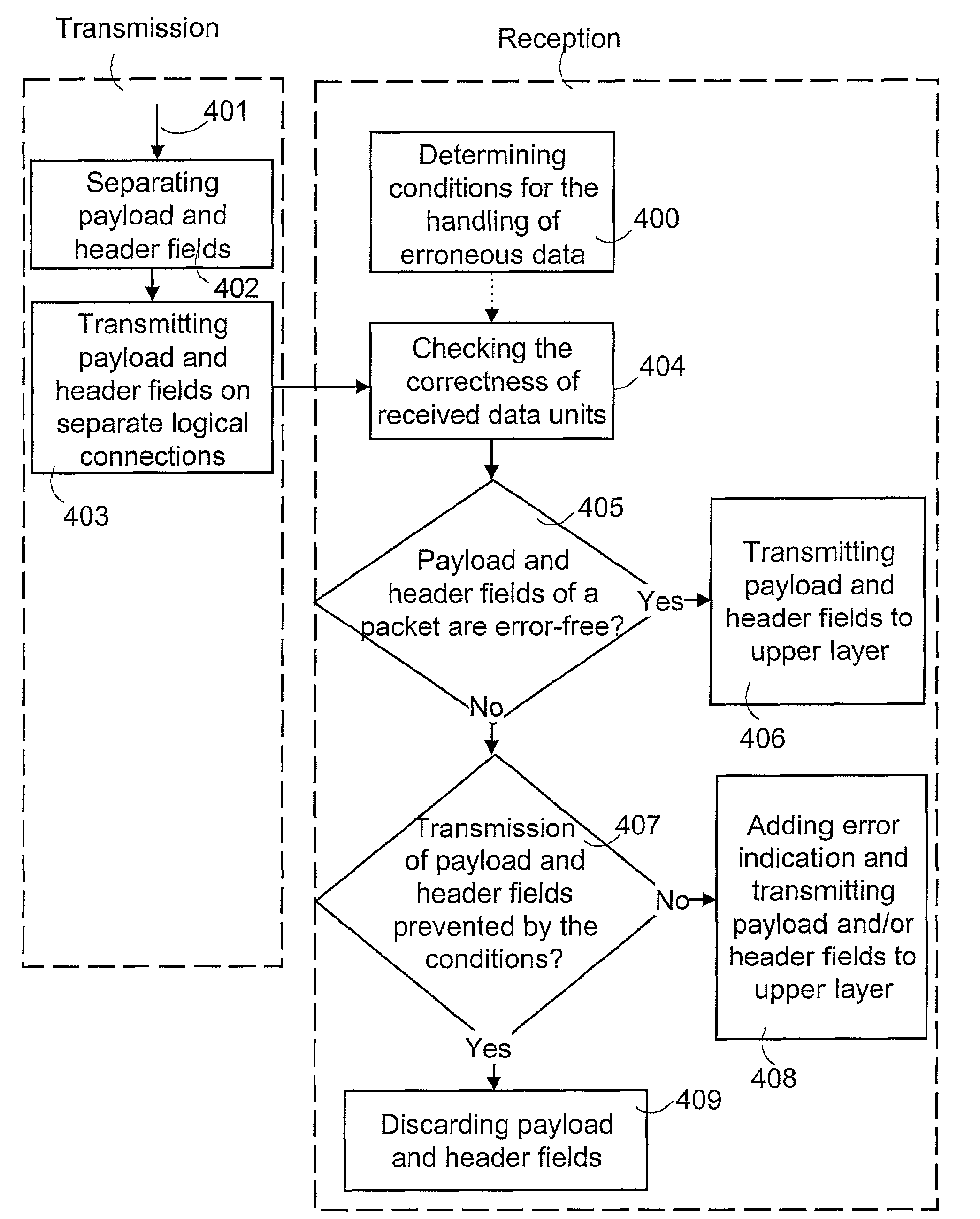

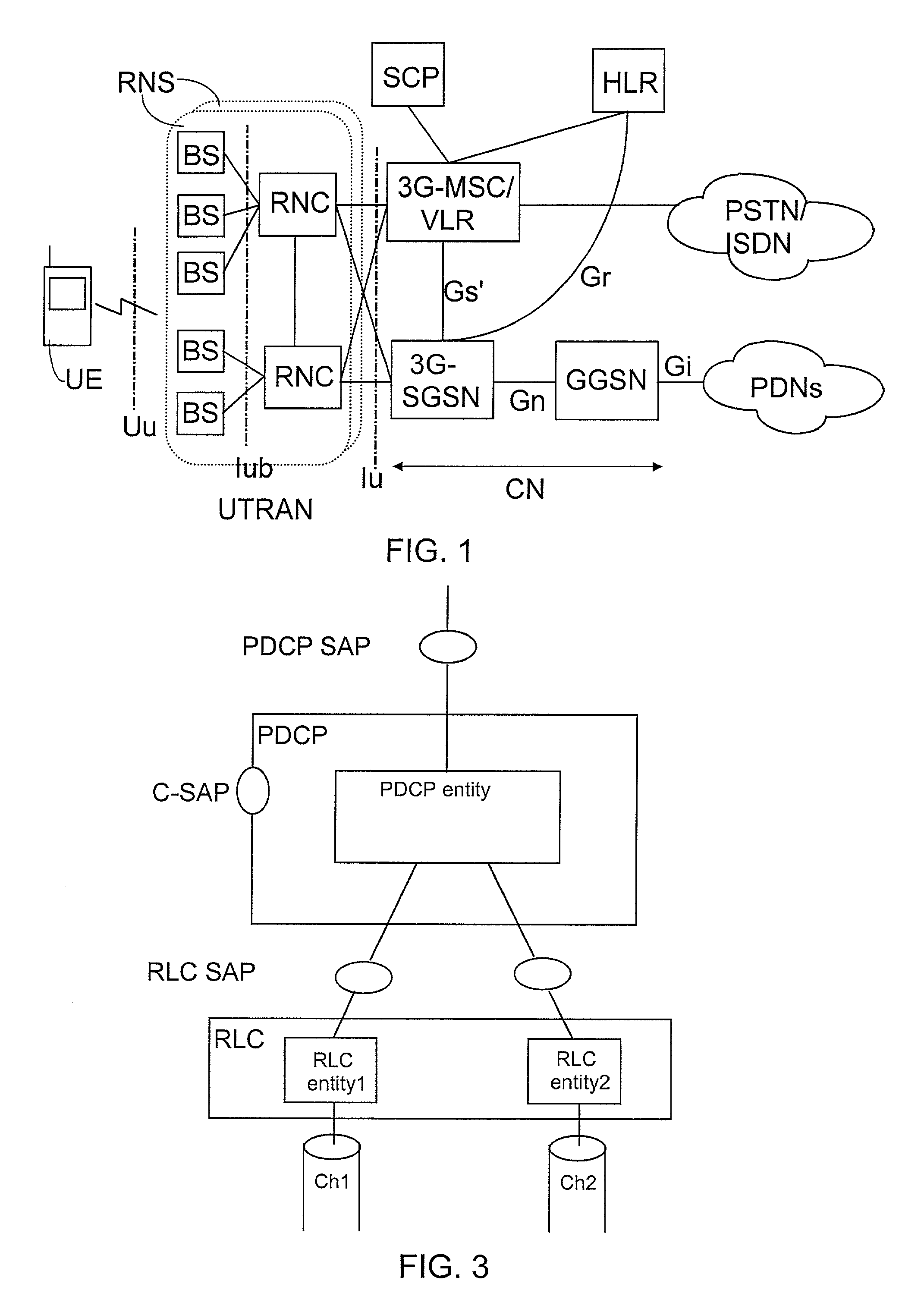

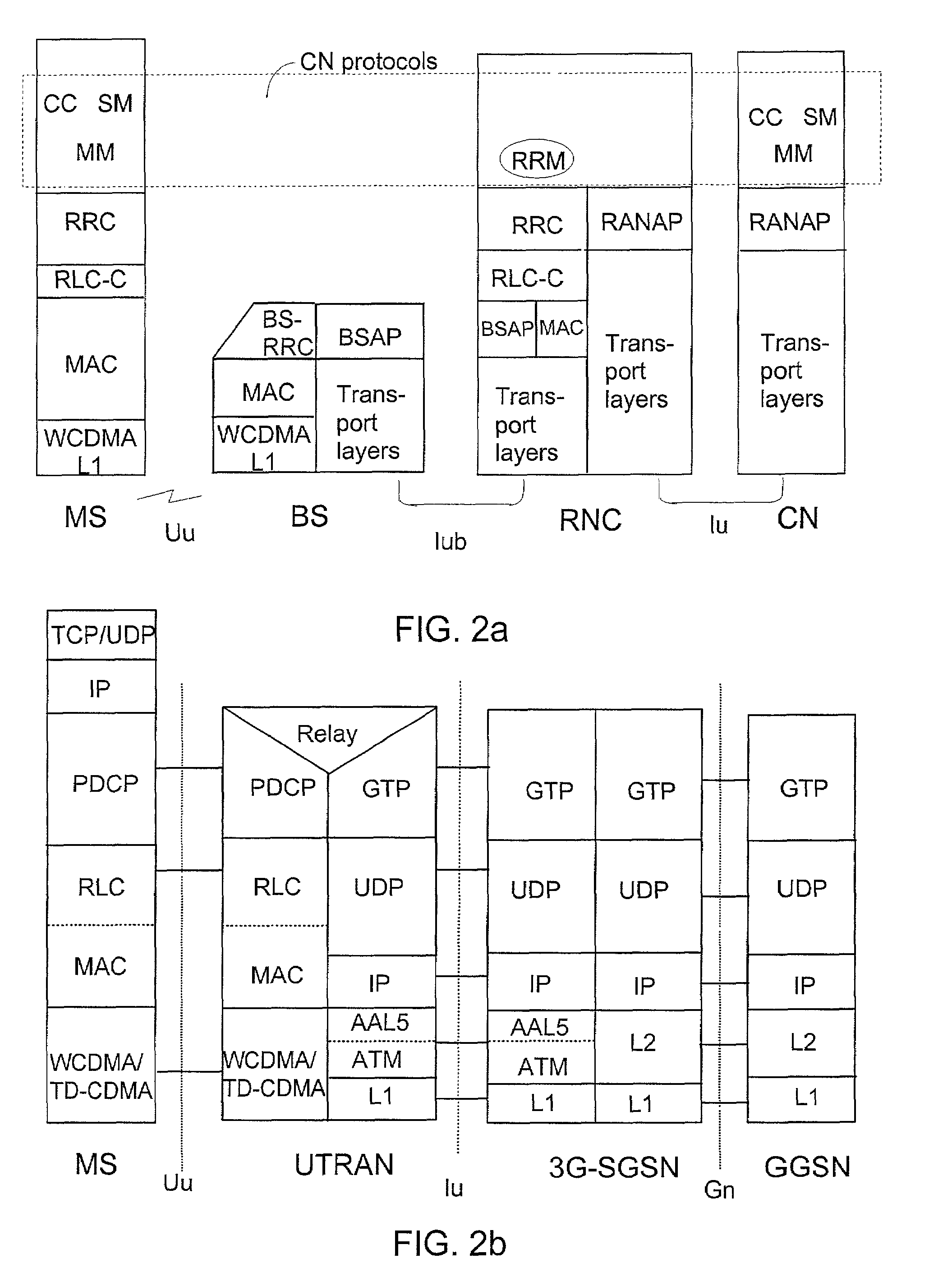

Processing of erroneous data in telecommunications system providing packet-switched data transfer

InactiveUS7346077B2Easy to detectError prevention/detection by using return channelTime-division multiplexProcess errorComputer science

A method for arranging error control of packet-switched data, in which method at least a first part and a second part can be separated from the packets. In the method, errors detected in received data are checked, and conditions are determined for handling errors detected at least in the first and the second part. If an error is detected in a received first part and / or second part, the routine checks whether the conditions allow the first part and / or second part to be transmitted to upper protocol layers. If this is allowed, the first part and / or second part are transmitted to upper protocol layers.

Owner:NOKIA CORP

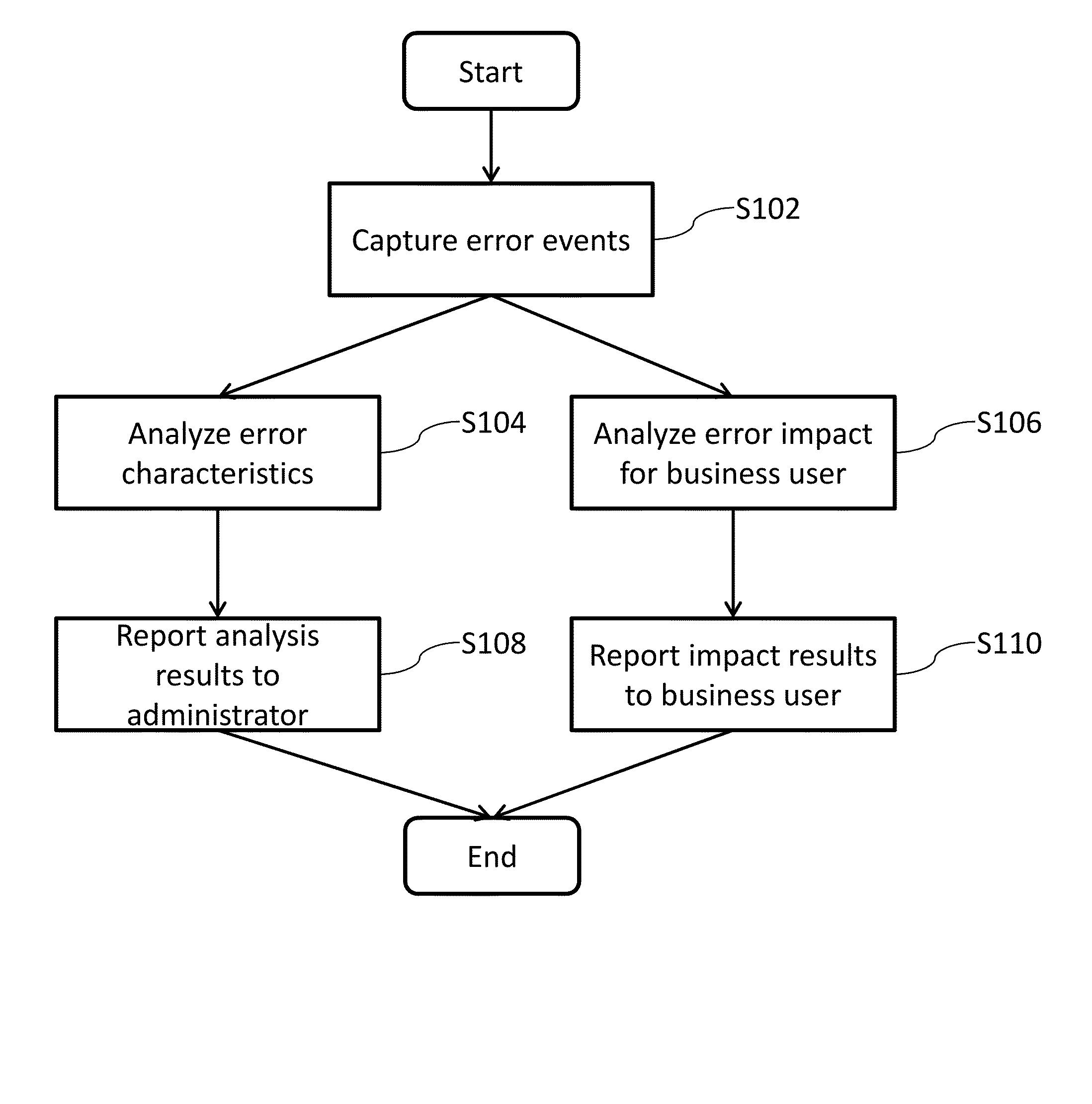

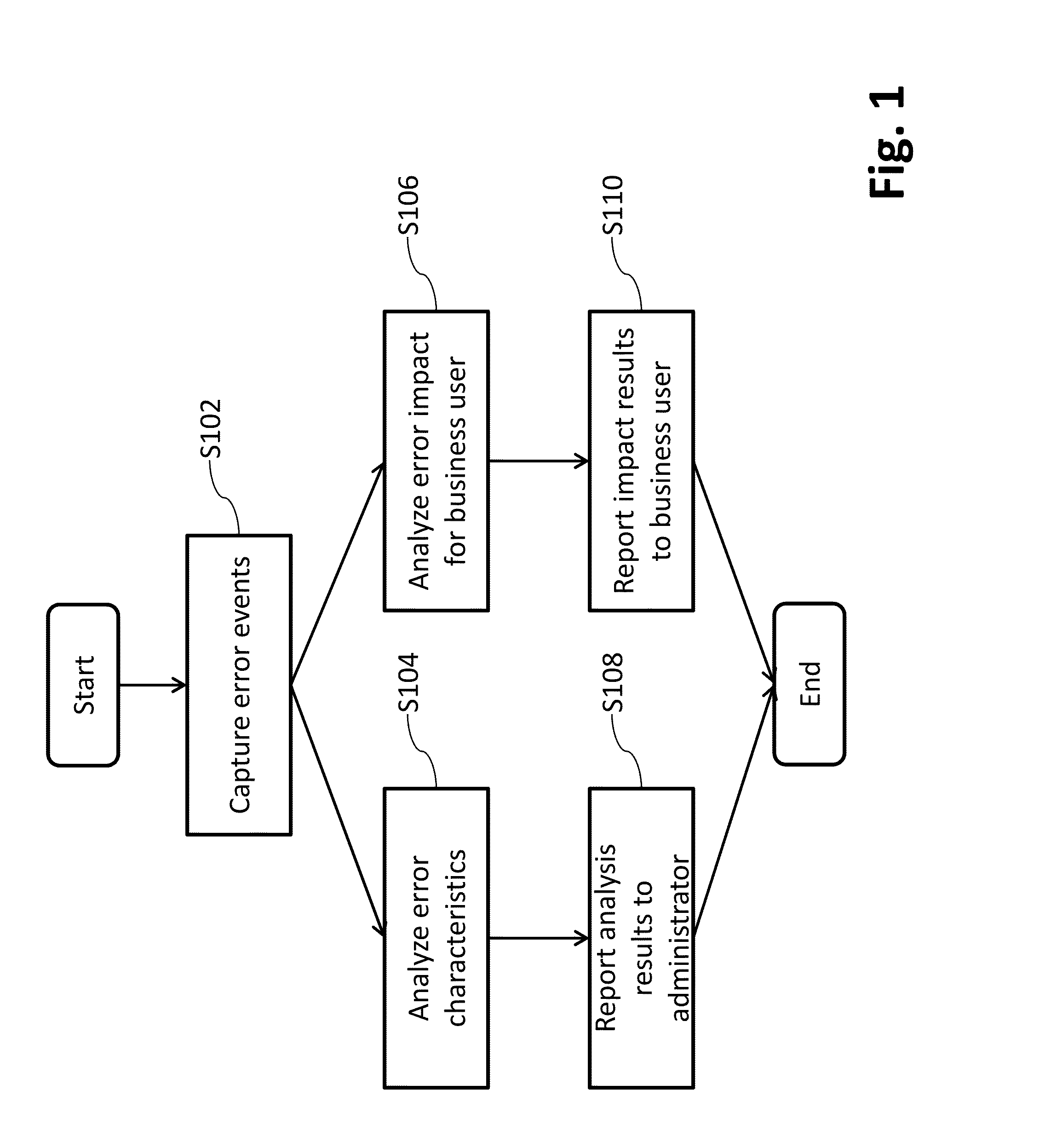

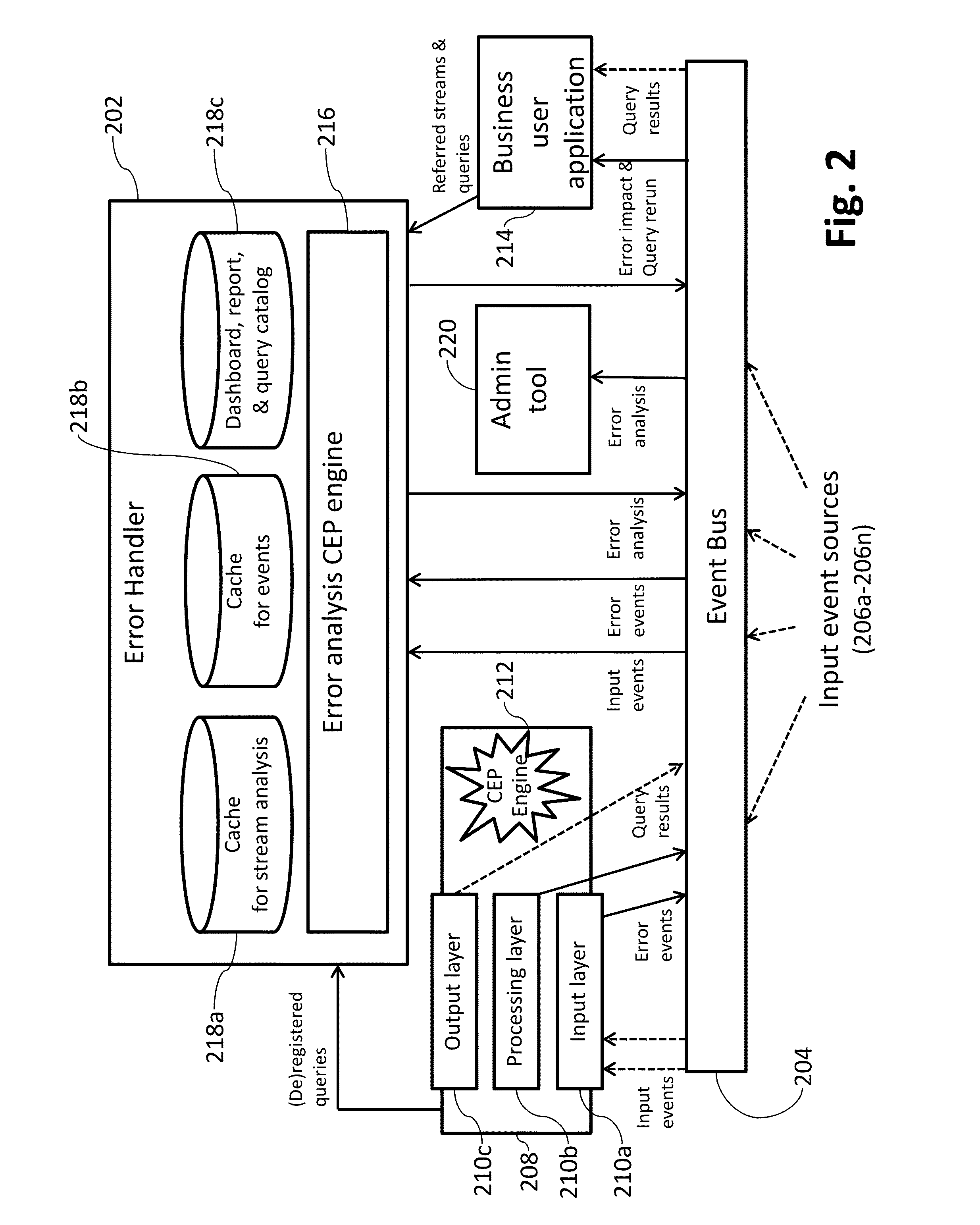

Systems and/or methods for handling erroneous events in complex event processing (CEP) applications

ActiveUS20160154692A1Improve data qualityExclude dataNon-redundant fault processingComplex event processingApplication software

Certain example embodiments address issues associated with erroneous events produced in Complex Event Processing (CEP) applications. An error handler is controlled to at least: receive, via an event bus, events from external input event sources; receive, via the event bus, error events from an application configured to process events received from the event bus, and to provide to the event bus results obtained from processing received events, and error events corresponding to errors detected at its input and / or processing layer(s); generate, for a given error, an error analysis event and an error impact event by executing a CEP query on at least a corresponding received error event; and provide to the event bus generated error analysis events and generated error impact events. Error analysis events describe for administrators detailed information analyzing corresponding errors. Error impact events describe for business users impacts corresponding errors have for their business user applications.

Owner:SOFTWARE AG

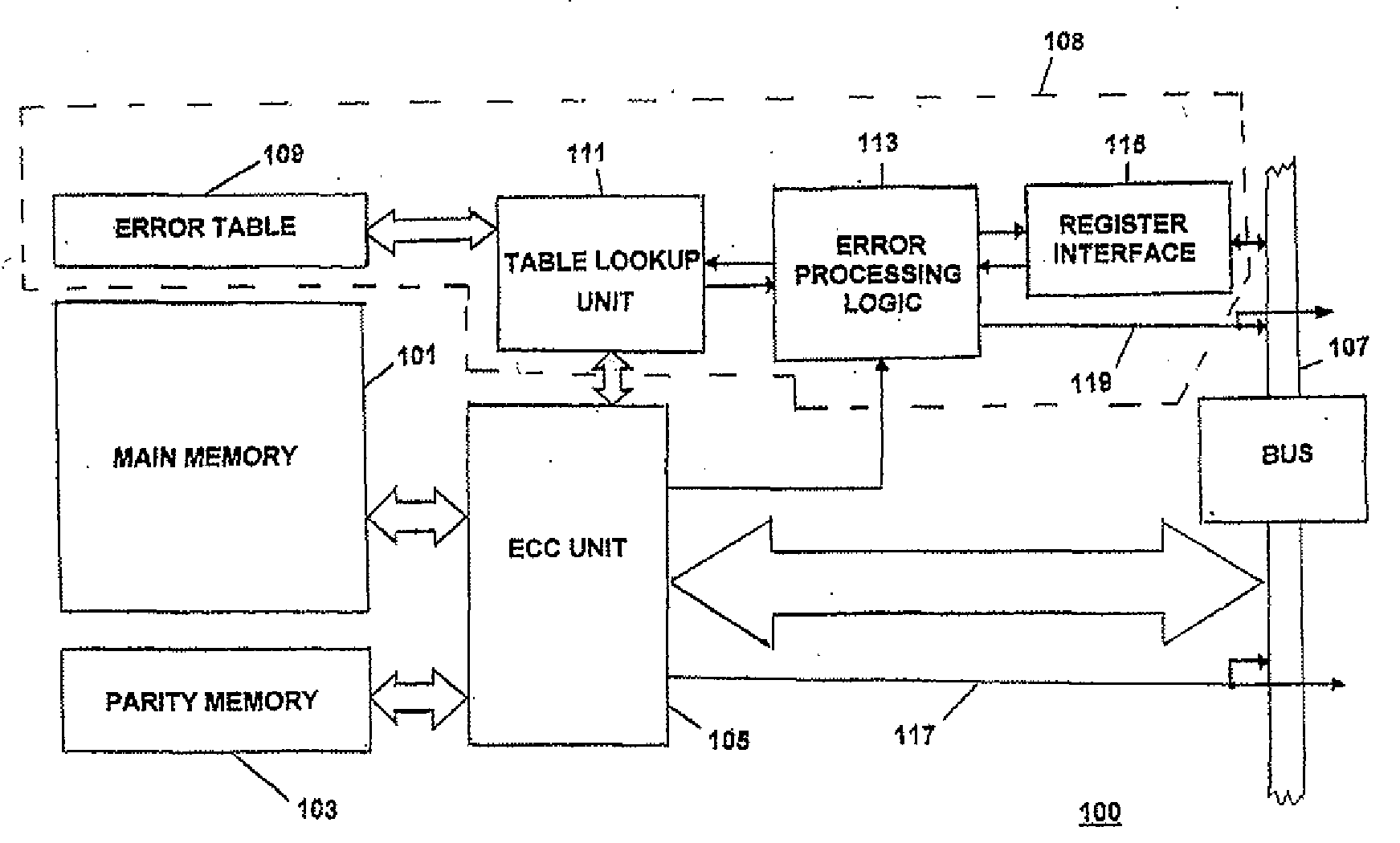

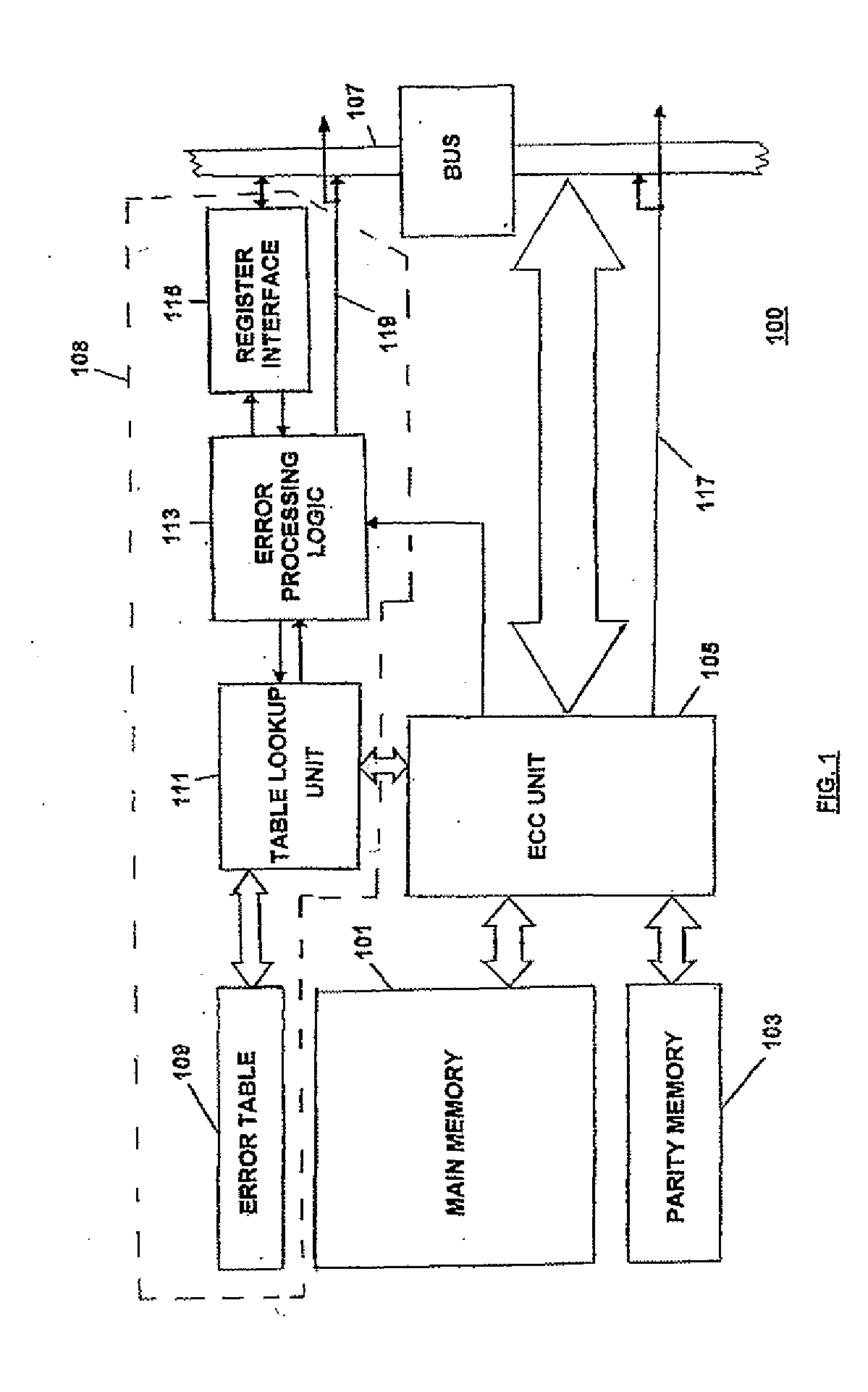

Memory system with ecc-unit and further processing arrangement

ActiveUS20100058144A1Code conversionError correction/detection using block codesComputer hardwareProcess error

A memory system including a first memory for storing data and an ECC unit for accessing the first memory and for detecting errors in data retrieved from the first memory, and characterised by an error further processing arrangement operable to process errors detected by the ECC unit, the error further processing arrangement including a second memory for recording information relating to the detected errors.Also described is a method of operation in the memory system.

Owner:NXP USA INC

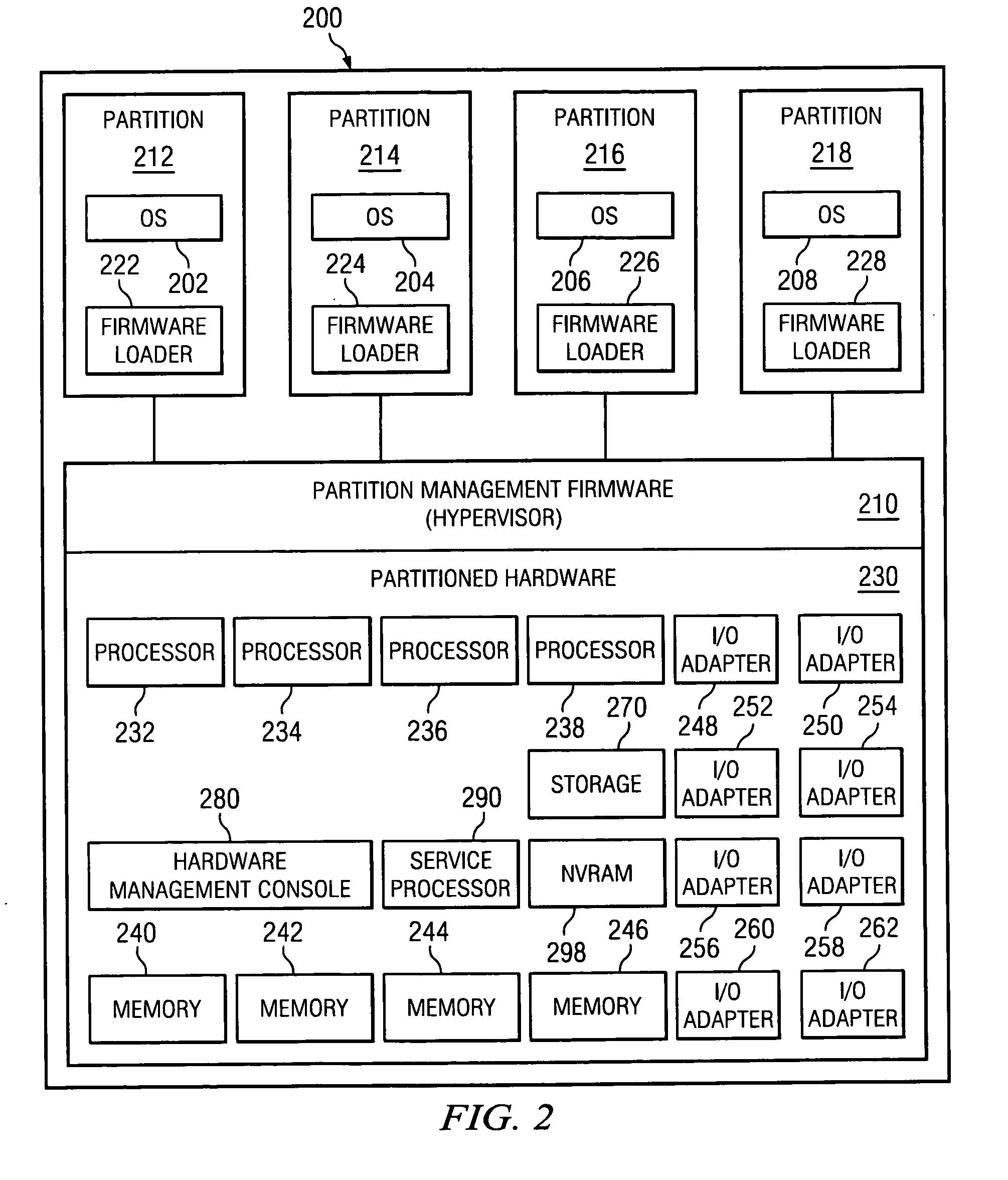

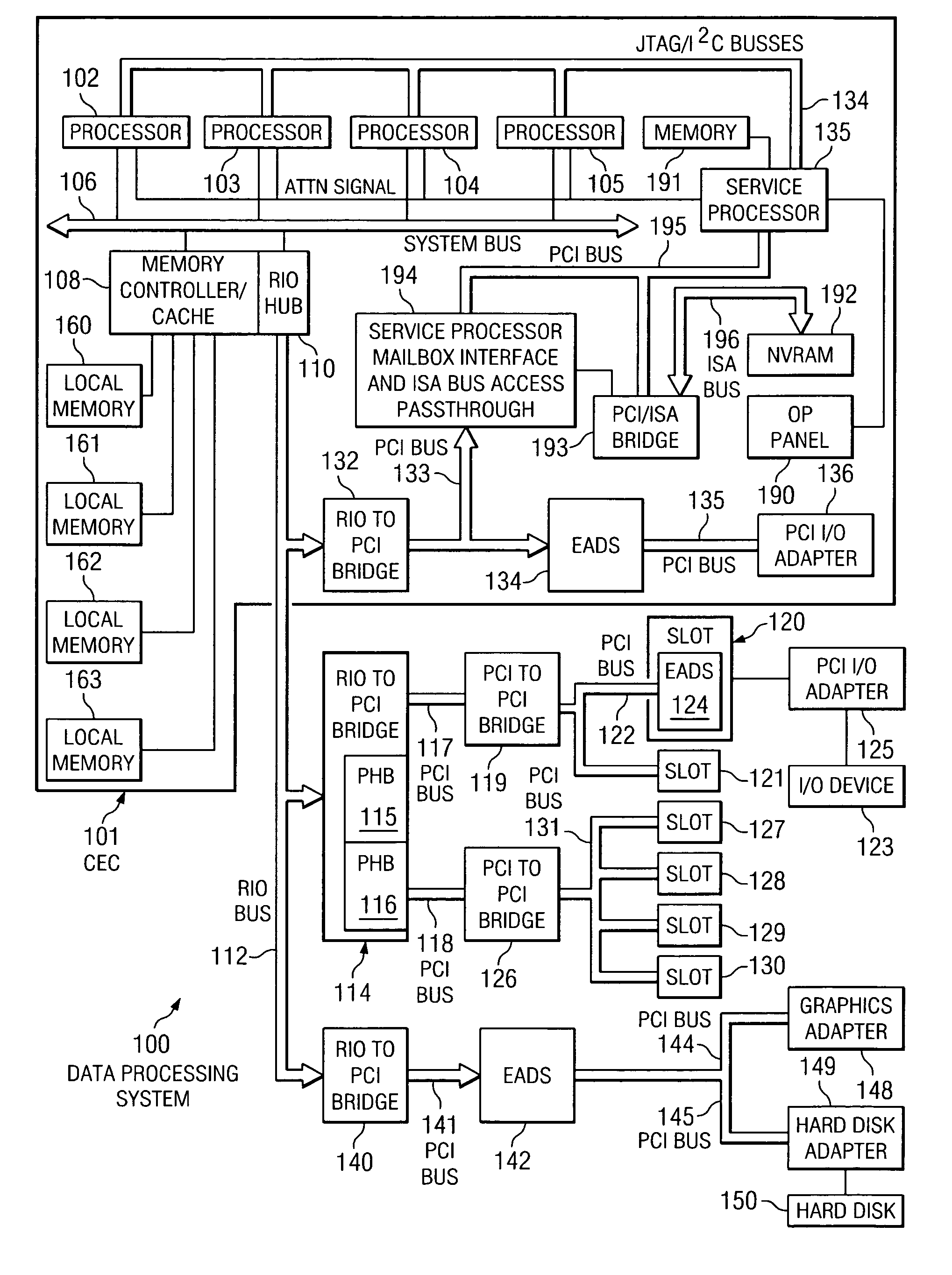

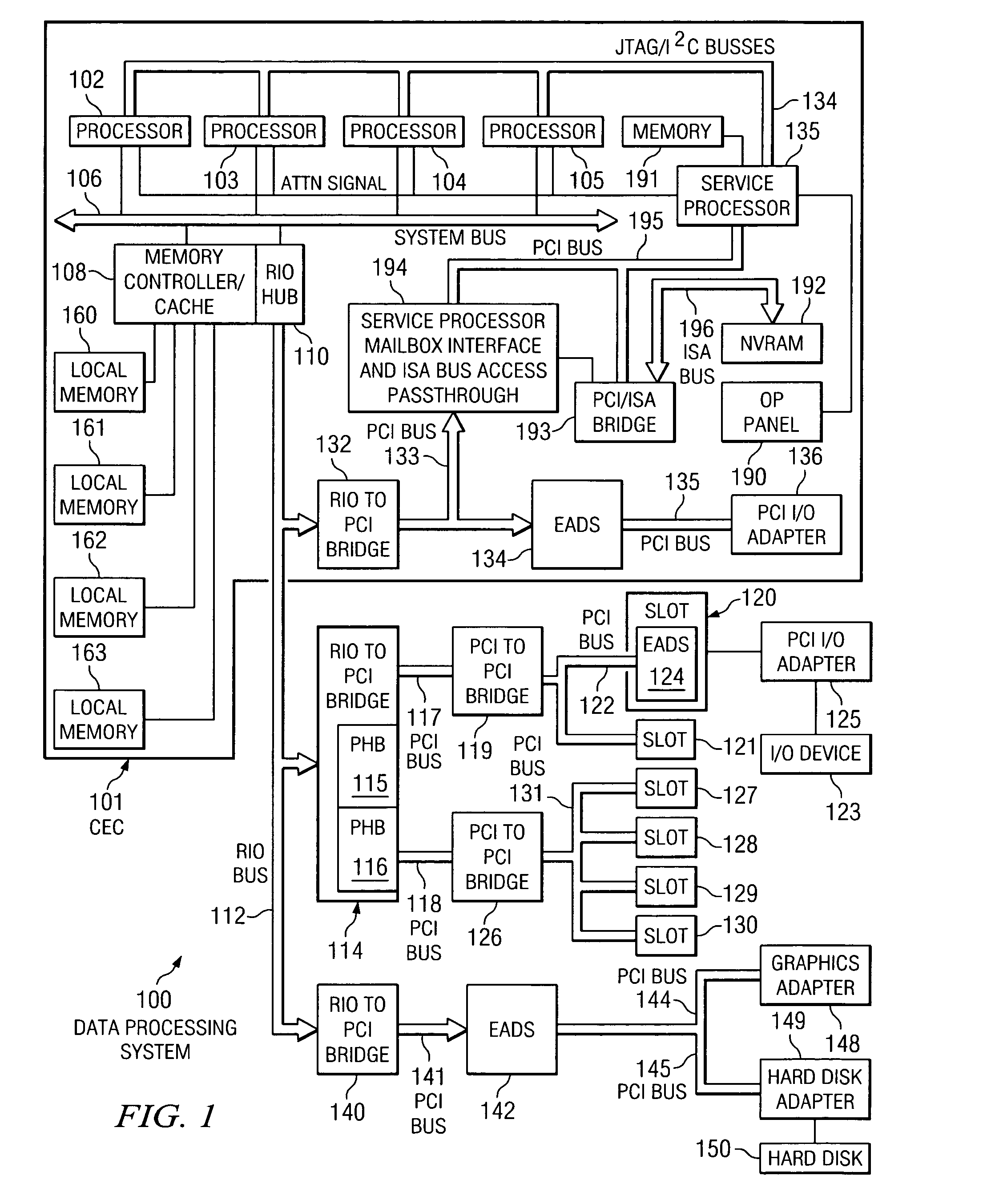

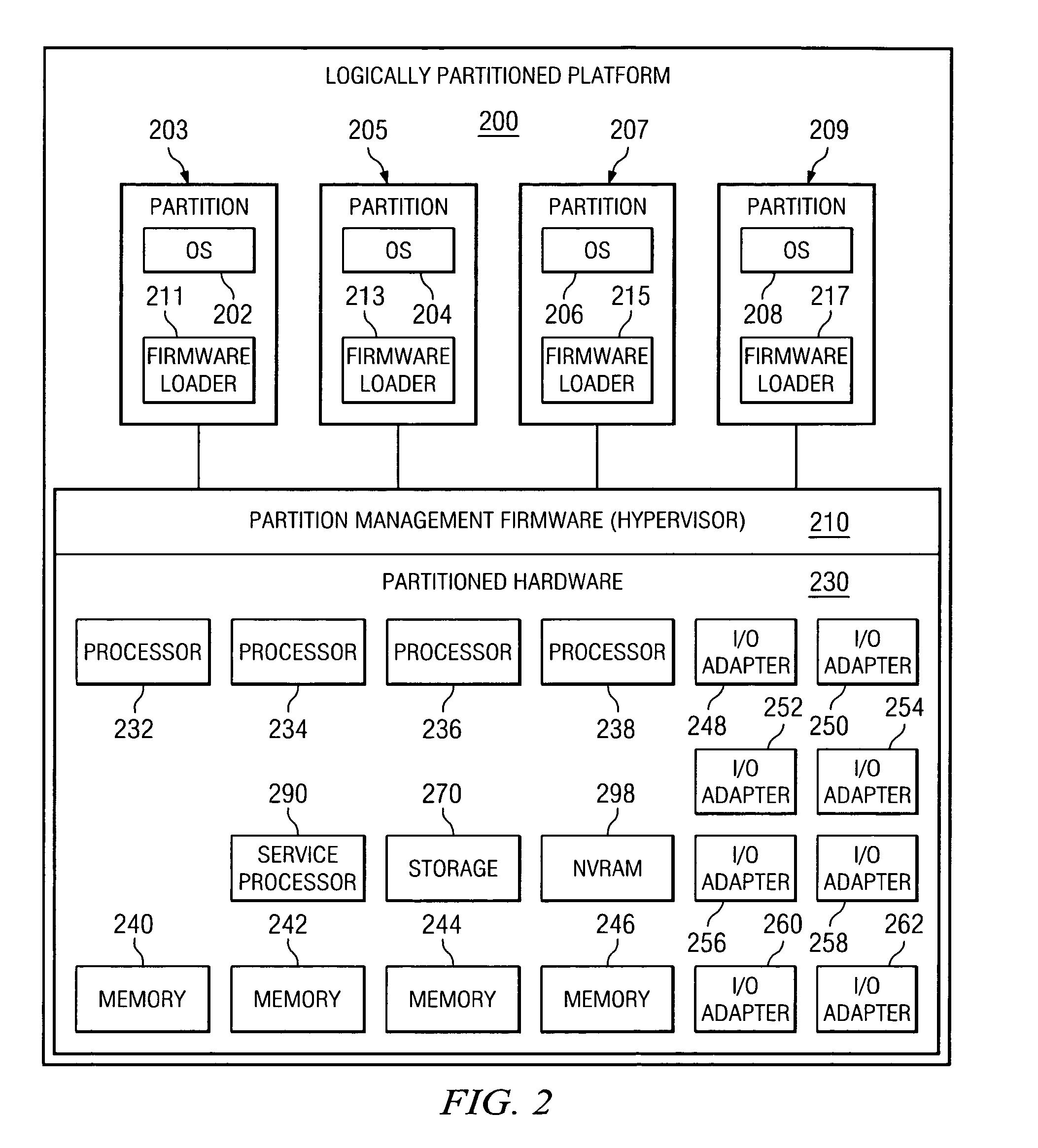

Method, system, and product for providing extended error handling capability in host bridges

ActiveUS20050081126A1Detecting faulty hardware by power-on testNon-redundant fault processingData processing systemProcess error

A method, system, and computer program product in a logical partitioned data processing system are disclosed for providing a host bridge that implements extended error handling (EEH). If all devices coupled to the host bridge implement EEH, the host bridge is initialized to operate in EEH mode. In EEH mode, the devices handle any error that occurs within the devices without reporting the error to the host bridge. All partitions that share the host bridge continue to operate without being terminated while the devices are handling the error. If at least one device does not implement EEH, the host bridge is initialized to operate in non-EEH mode. In non-EEH mode, a machine check is generated by the host bridge when an error occurs within one of the devices resulting in the termination of all partitions that share the host bridge in response to a receipt of the machine check.

Owner:IBM CORP

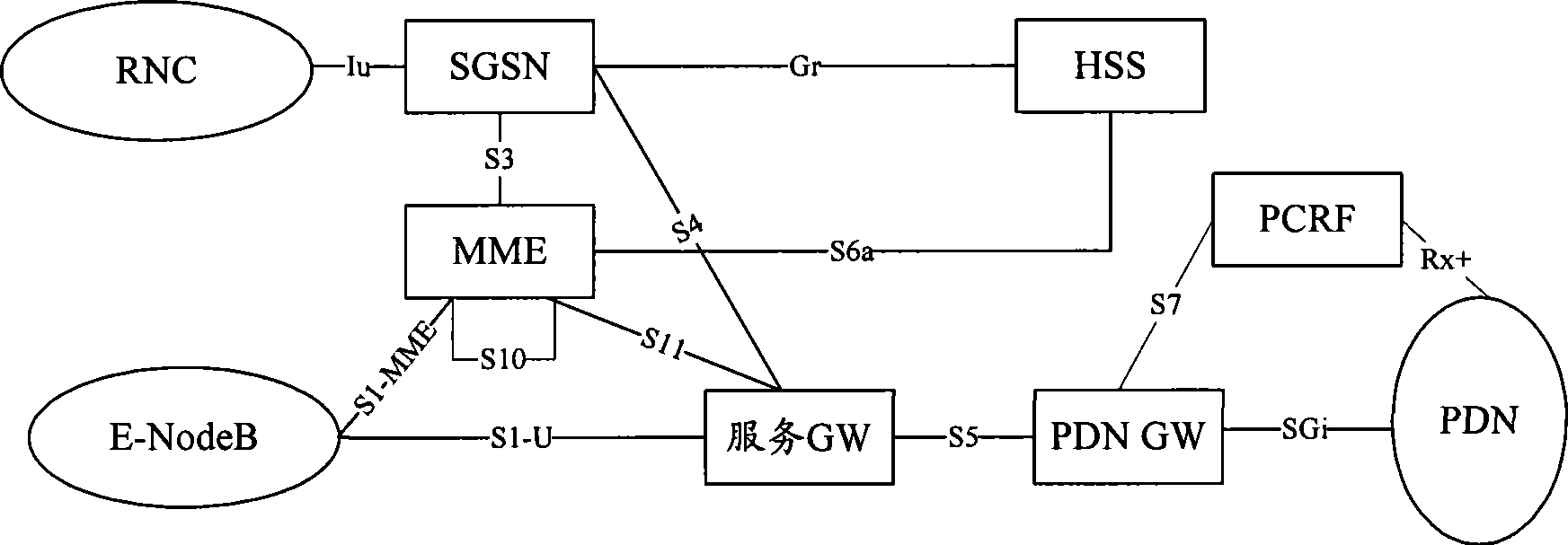

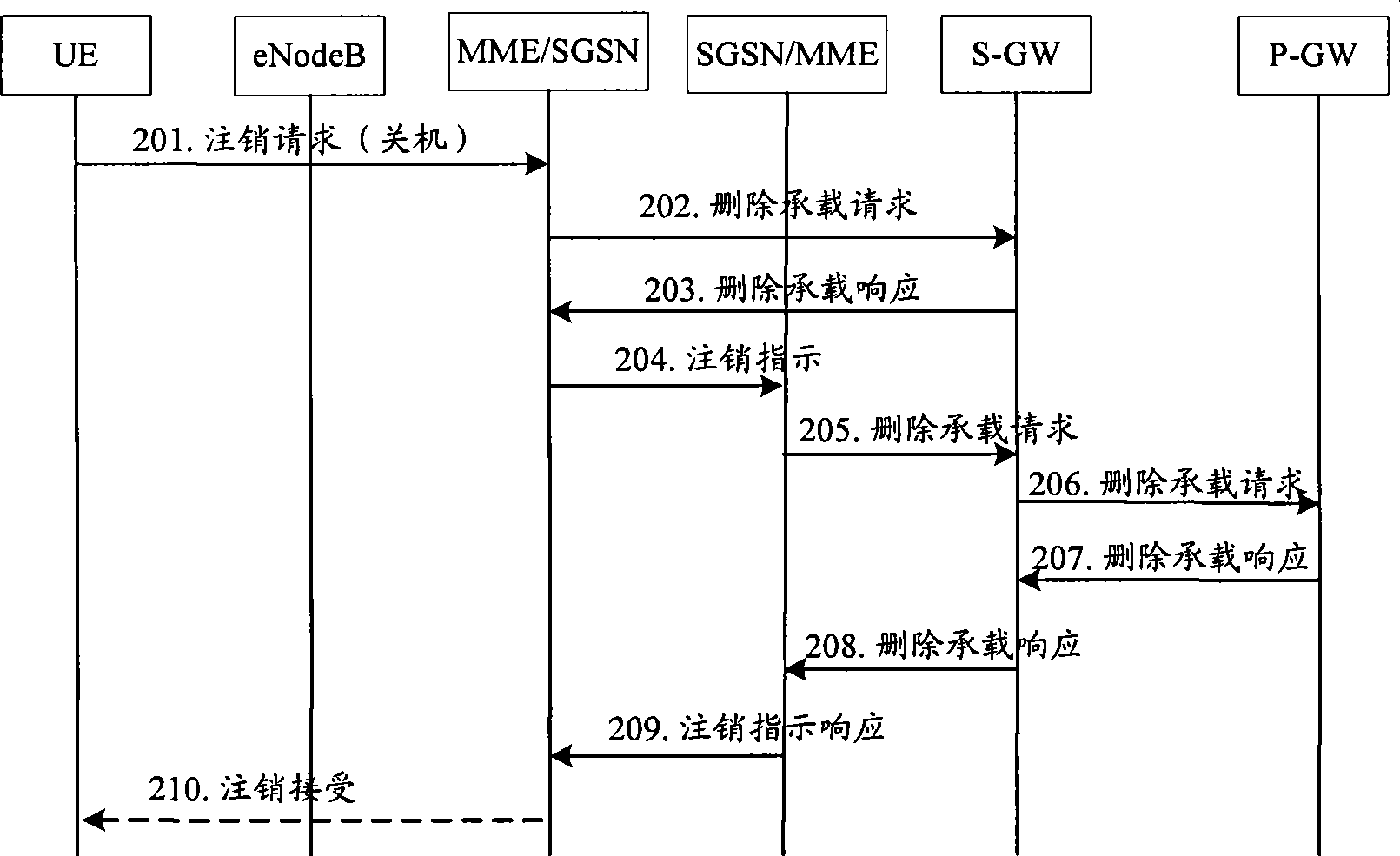

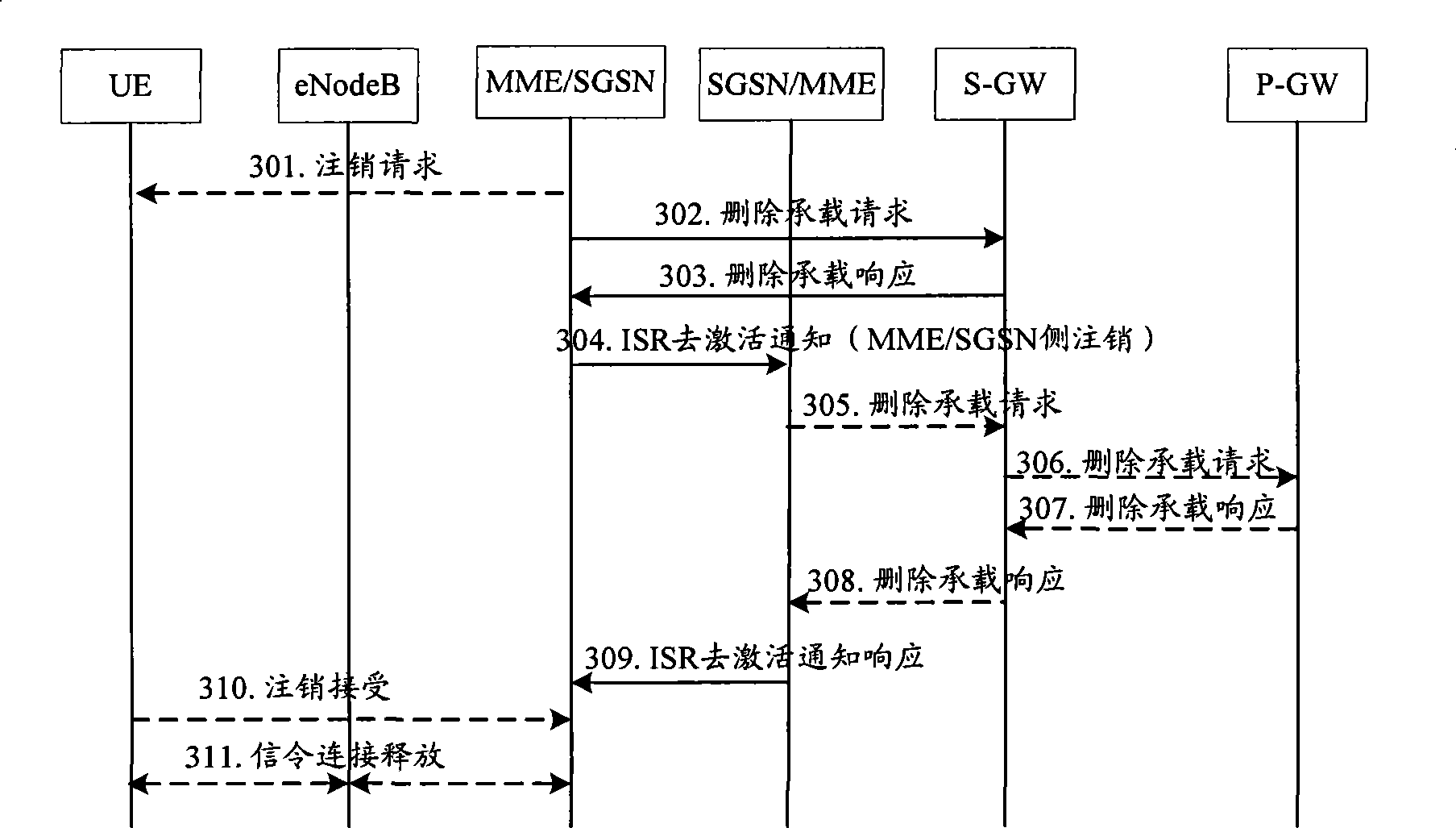

ISR deactivation method, ISR deactivation indicating apparatus

InactiveCN101459905APrevent process errorsConnection managementNetwork data managementProcess errorMobility management

The invention discloses an ISR deactivation method and an ISR deactivation indicating device, wherein the method comprises sending an ISR deactivation message to a corresponding core network node when the register state of a user device of a current core network node in a pair of core network nodes used for activating the ISR function changes, and indicating the corresponding core network node to conduct related operations, wherein the related operations comprise one of ISR deactivation, and ISR deactivation and loading deletion. In addition, the invention further discloses a mobility management entity and a service GPRS support node. Through the technical scheme, the process errors caused by the asynchronous ISR state can be prevented.

Owner:ZTE CORP