High-performance multistandard FEC (Forward Error Correction) decoder

A decoder, multi-standard technology, used in digital transmission systems, electrical components, error prevention, etc., can solve problems such as deficiencies, and achieve the effect of flexible configuration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

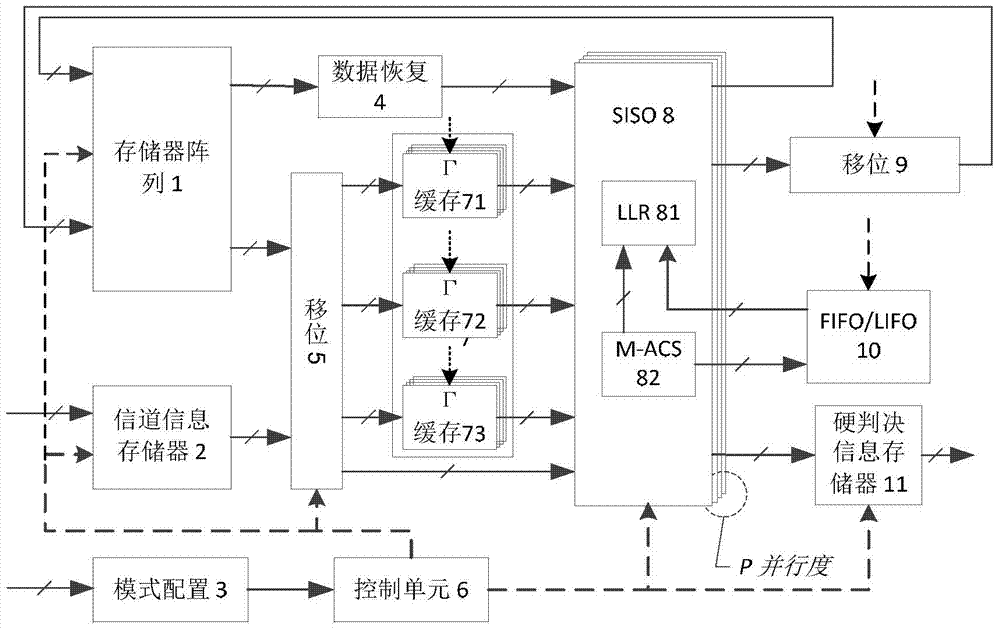

[0086] figure 1 Shown is the designed multi-mode configurable FEC decoder compatible with LDPC code and Turbo code. Among them, the dark part represents the memory, the rest is the logic module, and the dotted line part is the control part of the whole decoder. The decoder contains a large amount of memory, a very flexible permutation network, a configurable calculation unit SISO capable of supporting two kinds of error correction code logic operations at the same time, and a global control unit. Among them, the memory can be further divided into a memory array required for iteration, a channel information memory, a buffer for preventing memory access conflicts, an intermediate temporary storage unit FIFO / LIFO, and a hard judgment information memory. The permutation network not only needs to support LDPC configurable cyclic shift, but also needs to support the conflict-free QPP interleaver of Turbo codes. The SISO module needs to complete the forward and backward updates of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More