Method and System for Performing Functional Formal Verification of Logic Circuits

a logic circuit and functional verification technology, applied in the field of logic circuit functional formal verification, can solve the problems of inherently difficult functional formal verification of a dput at the register-transfer level, enormous input signal value space cannot be completely verified by logic simulation, and the complexity of hardware designs of the day is much more complex

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

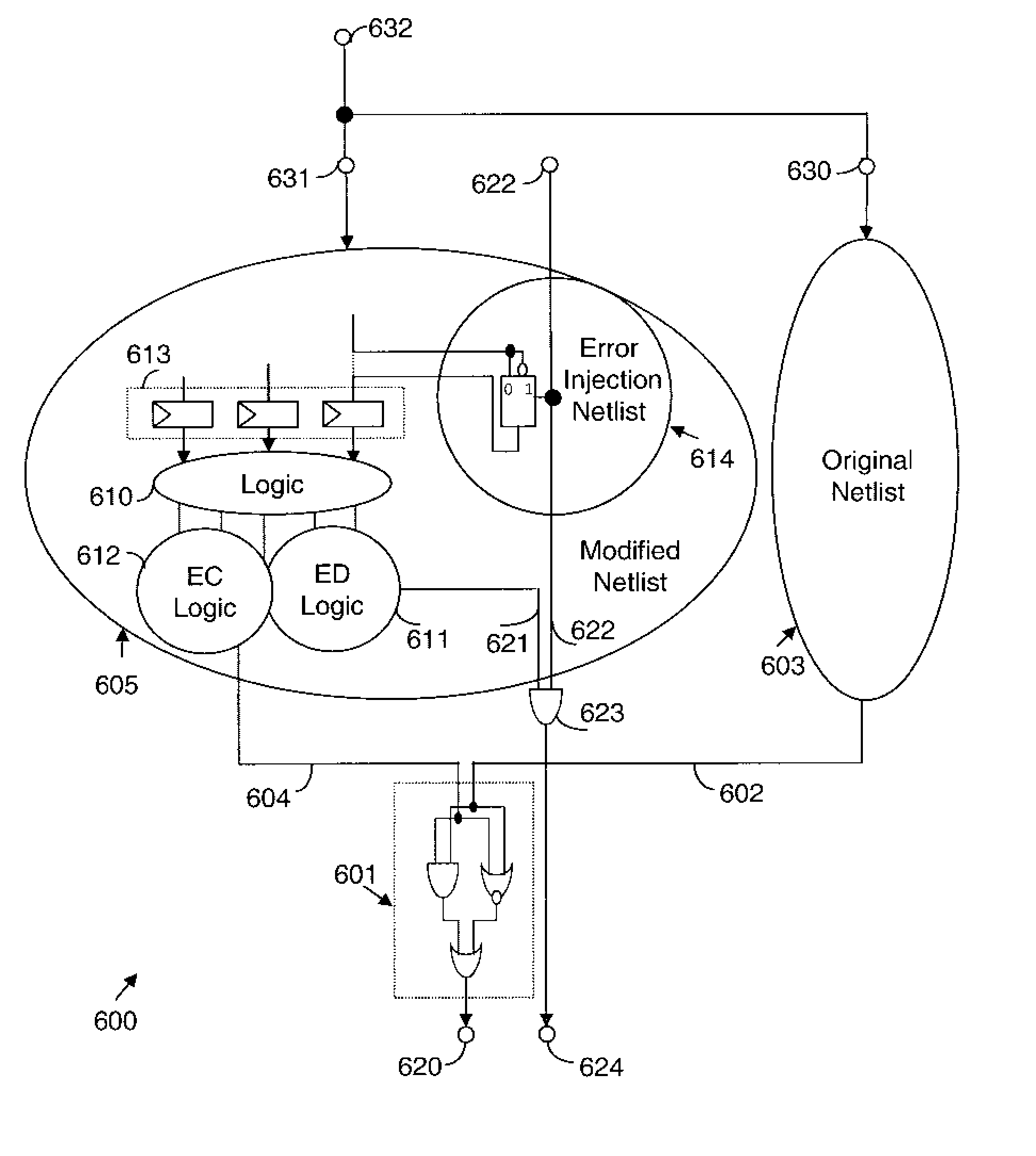

[0053] In the standard hardware design development processes the latches survive every automatic design transformation, for example a transformation from the RTL to the gate level using logic synthesis methods. In the preferred embodiment of the invention the injection of errors using fault models is performed at the RTL if an automatic transformation step from the RTL to the gate level is used, and the fault models are based on modifications of the latches. If no automatic transformation step from the RTL to the gate level is used in the hardware design development process, the error injection should be performed at the gate level in order to detect the errors introduced during the transformation step.

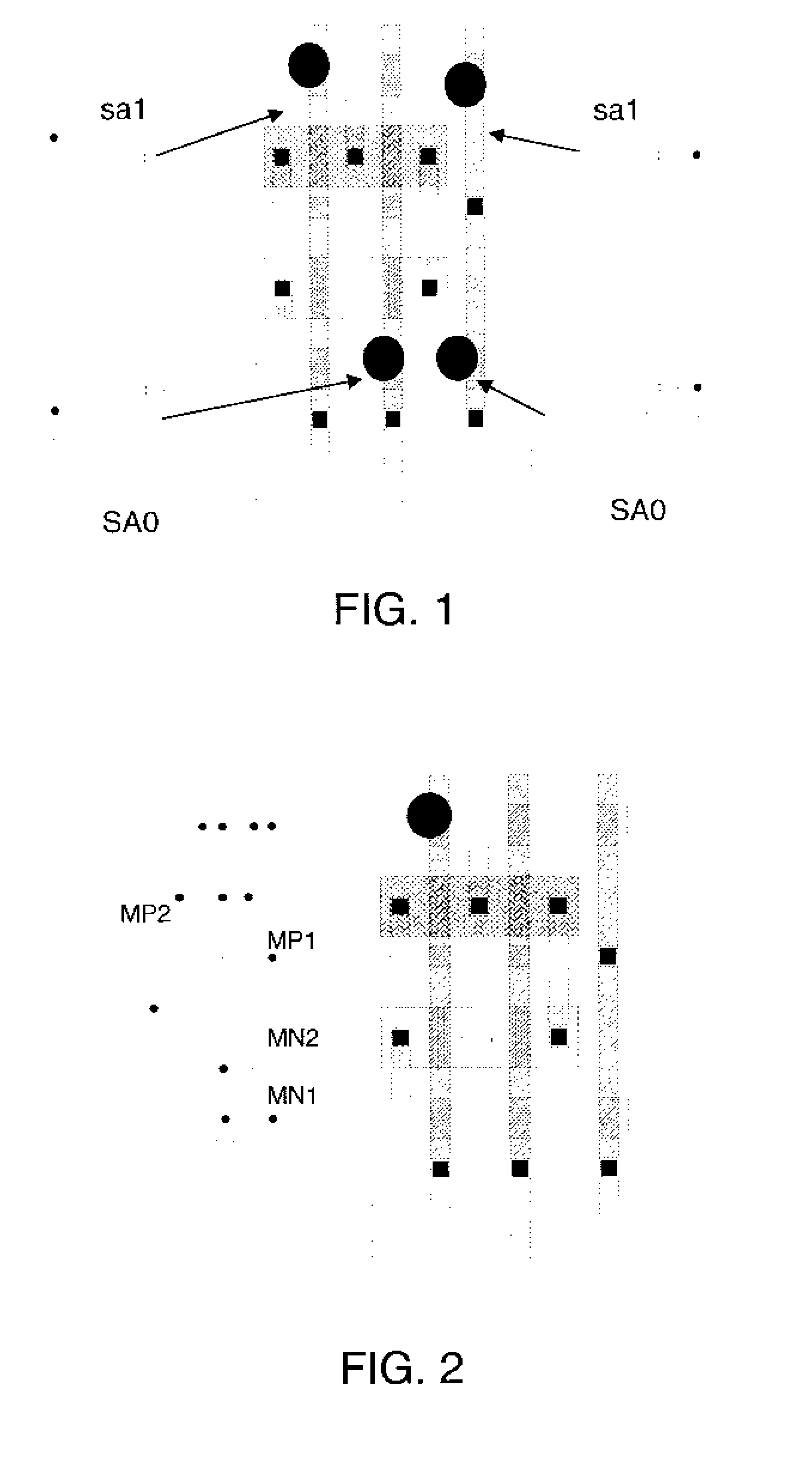

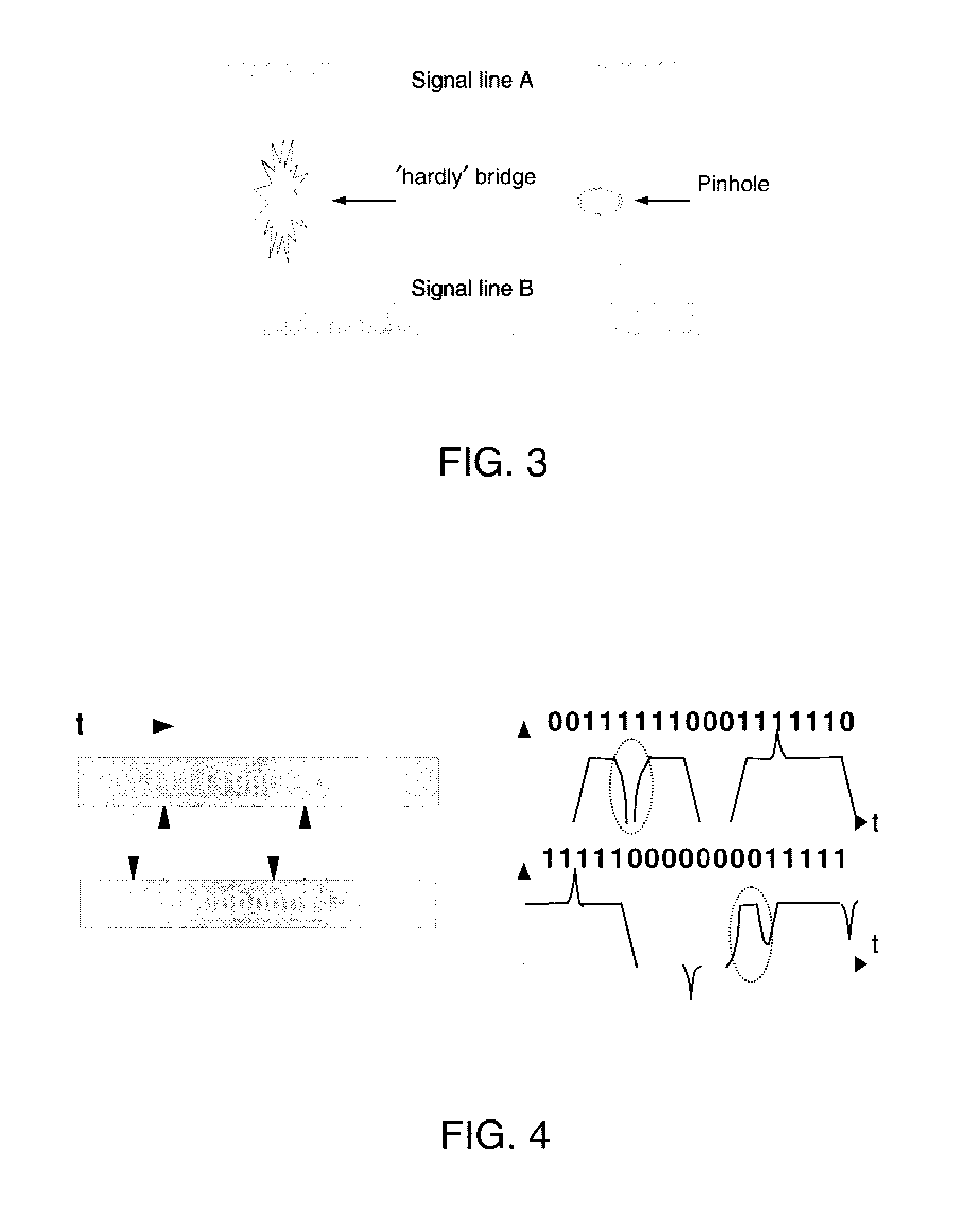

[0054] The injection of a permanent fault (e.g., stuck faults as in FIG. 1 and FIG. 2) can be done by simply switching a signal value. Examples for gate level models of transient faults (for example the faults in FIG. 3 and FIG. 4) in accordance with the present invention are given i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More