Compiler apparatus, compiler method, and compiler program

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment

[0206]A compiler apparatus according to an embodiment of the present invention: reads a source program; performs word / phrase analysis to resolve the program into word / phrase strings; performs a syntax analysis for creating a syntax tree in a programming language based on the word / phrase strings; creates an intermediate program that is written with intermediate codes inside the apparatus based on the syntax tree created by the syntax analysis; performs optimization such as instruction scheduling for the intermediate program; and converts the intermediate program after allocation of resources such as registers are performed with respect to variables, into an execution format program.

[0207](Structure)

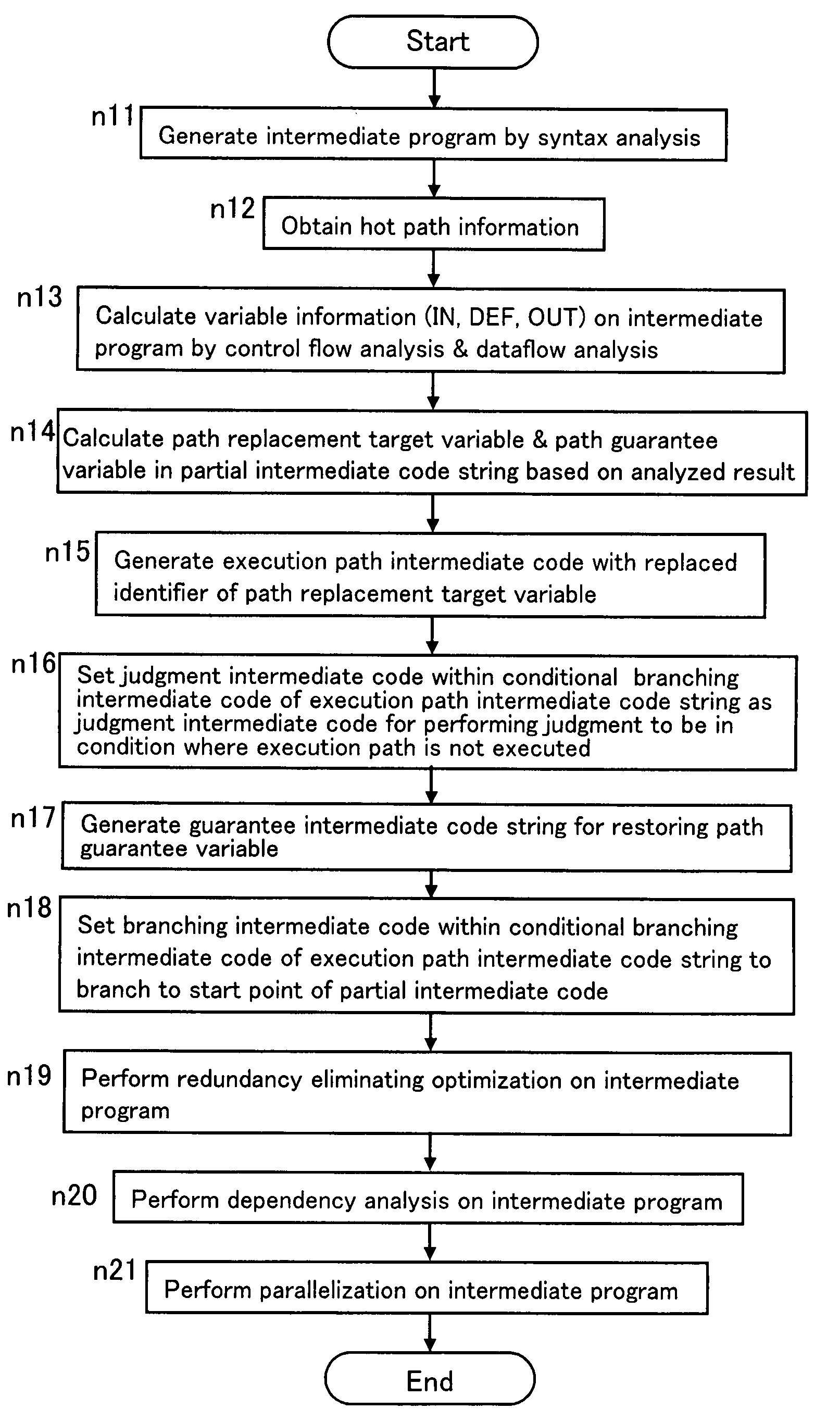

[0208]FIG. 1 is a functional block diagram showing the entire structure of a compiler apparatus A according to the embodiment of the present invention. The compiler apparatus A comprises a syntax analysis unit 1, an optimizing unit 2, a resource allocation unit 3, and an execution code gen...

operation example

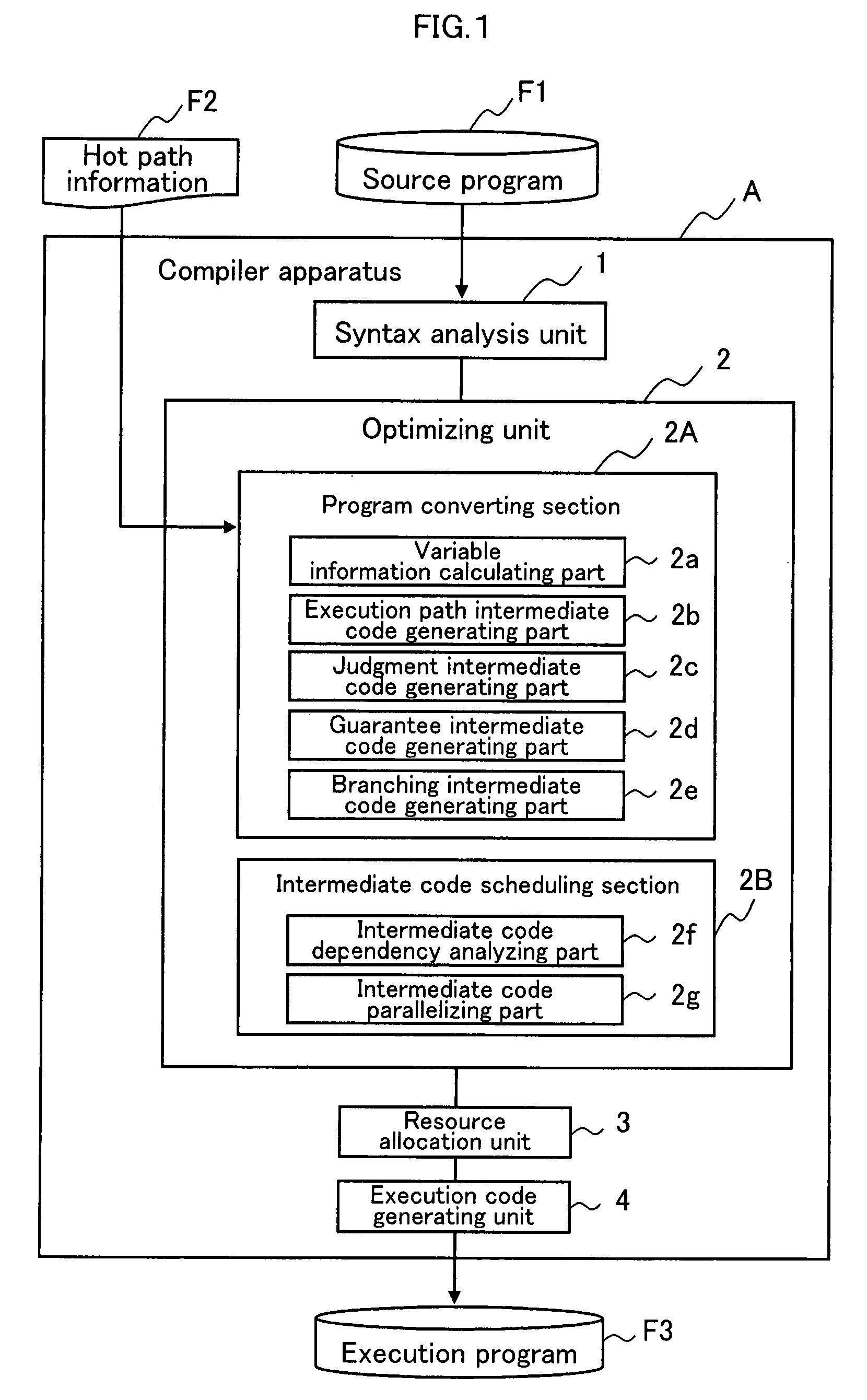

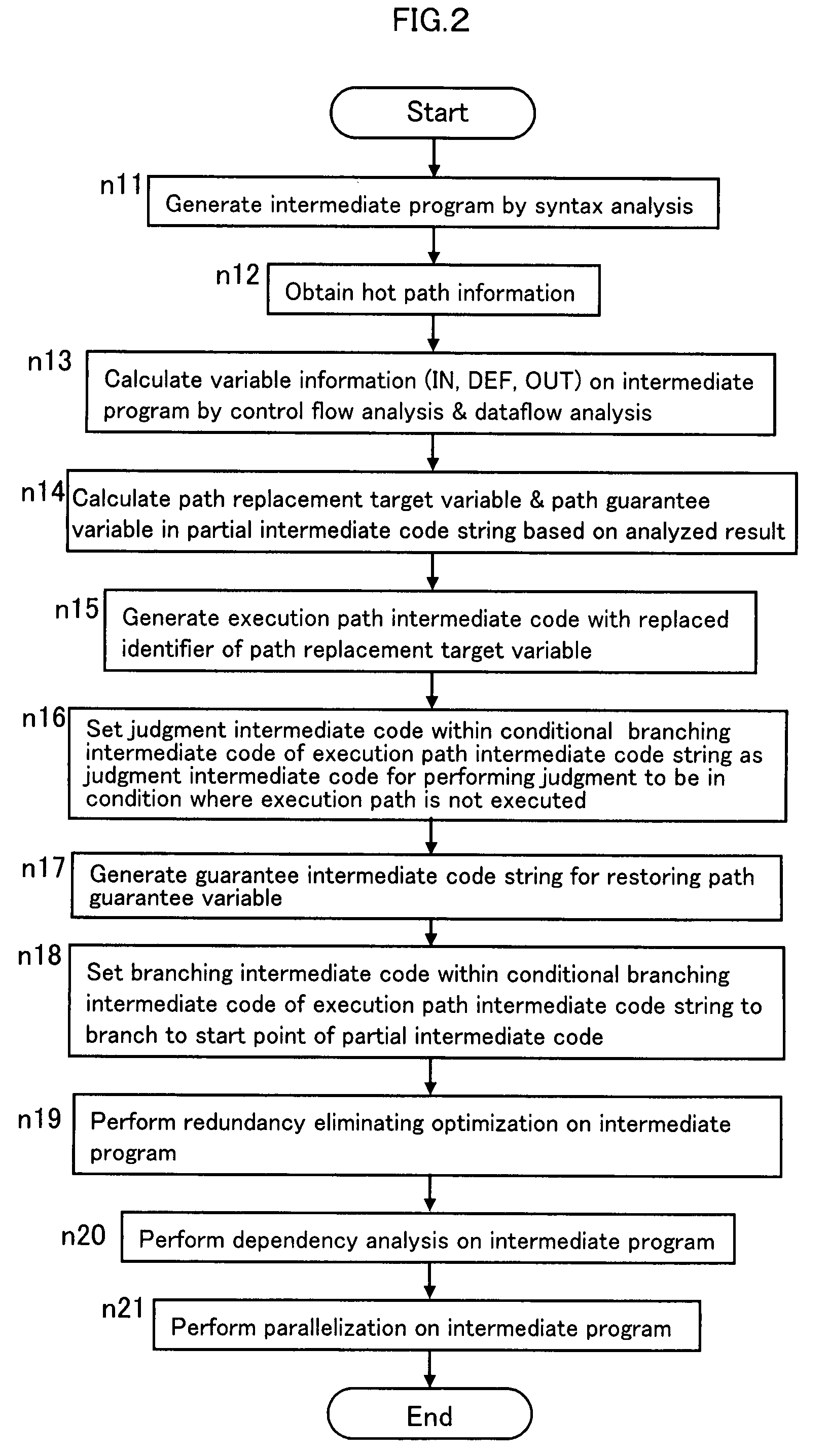

[0262]Next, referring to FIG. 5, FIG. 9-FIG. 12, a specific example of the operation flow shown in FIG. 2 will be described exemplifying the case of a partial program that is a part of the source program F1 of FIG. 5A. It is assumed here that the intermediate code in this example is expressed with the intermediate code close to the source program F1.

[0263]In a step n11, the syntax analysis unit 1 performs the syntax analysis to the partial program in order to generate the partial intermediate code, and stores it in the inside the compiler apparatus A. Then, in the step n12, the program converting section 2A stores the hot path information F2 in the inside the program converting section 2A, upon receiving the input of the hot path information F2 where the path HP, that transits in order of the basic blocks B1, B2, B4, B5, B7 of the control flow graph, is made to be the hot path (see FIG. 5).

[0264]In the step n13, the optimizing unit 2 performs the control flow analysis and the datafl...

modification example 1

Acceptable Generation of Exception: See FIG. 14-FIG. 17

[0283]In the above-described embodiment, the intermediate code dependency analyzing part 2f generates dependency from the judgment intermediate code S203 to the exception generating intermediate code S102 in FIG. 12, so that an exception is not generated improperly. In Modification Example 1, however, such dependency is not generated. That is, the execution path intermediate code generating part 2b generates an intermediate code S401 anew as shown in a program of FIG. 14, and thereafter generates dependency from the intermediate code S401 to the exception generating intermediate code S102 as shown in a program of FIG. 15.

[0284]That is, the execution path intermediate code generating part 2b inserts the variable and the code to the head of the execution path intermediate code string which are generated as below.[0285]Generate a return point holding variable that is a special variable for holding the returning address in returning...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More