Patents

Literature

63 results about "Timing error detector" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Apparatus and method for detecting timing error based on cyclic correlation

InactiveUS20060126765A1Reduce complexityReduce processing timeTime-division multiplexAmplitude-modulated carrier systemsShift registerTiming error detector

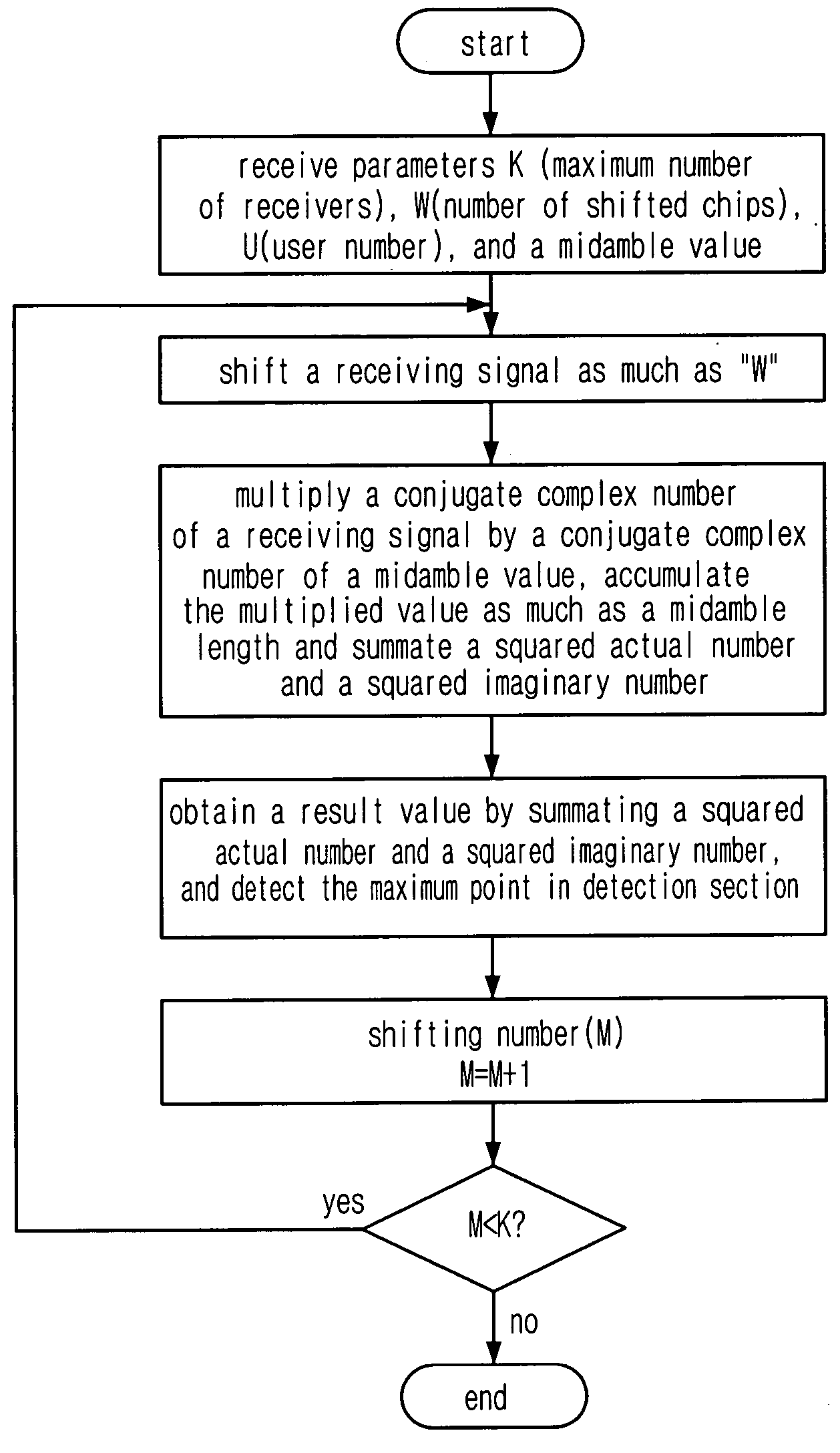

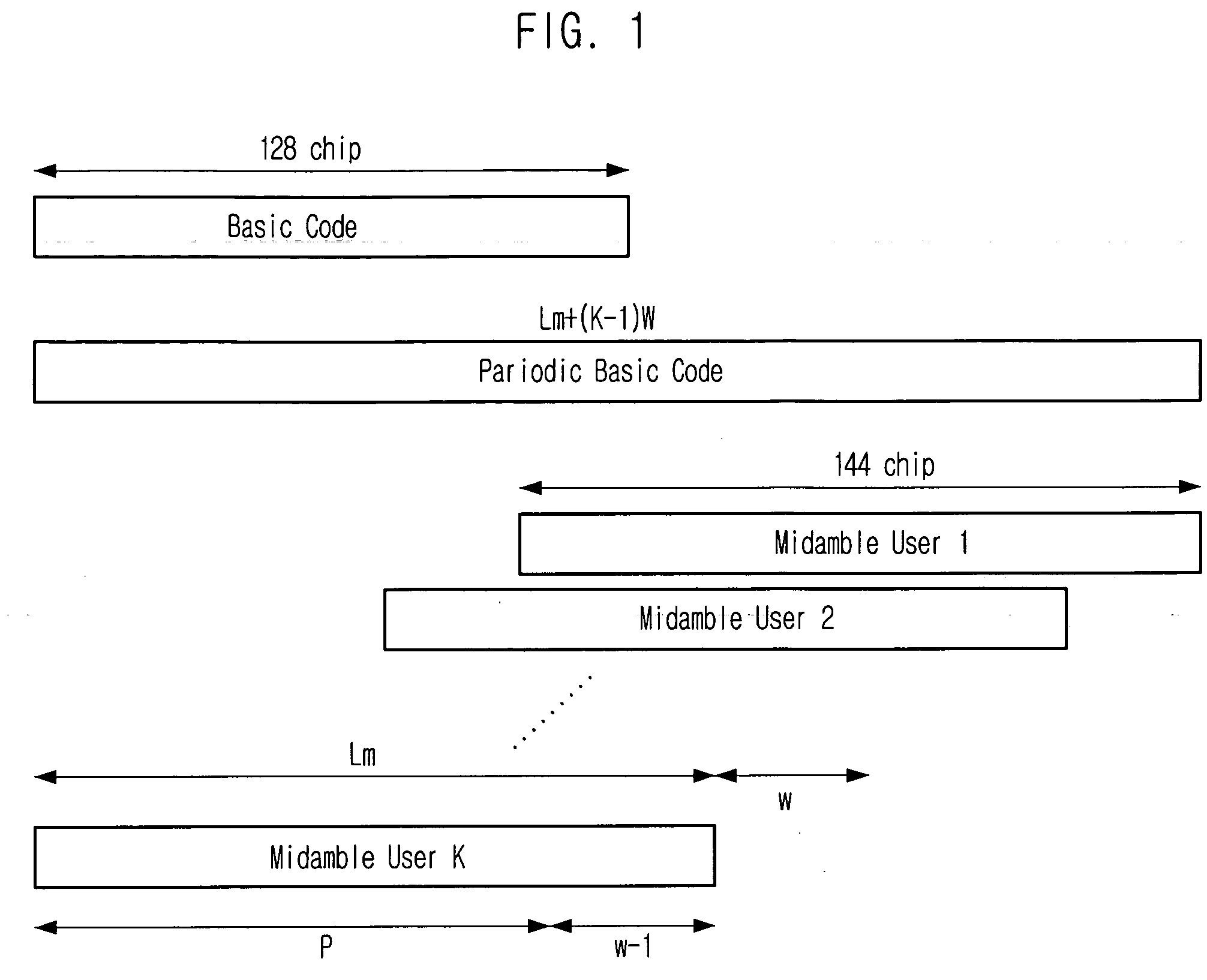

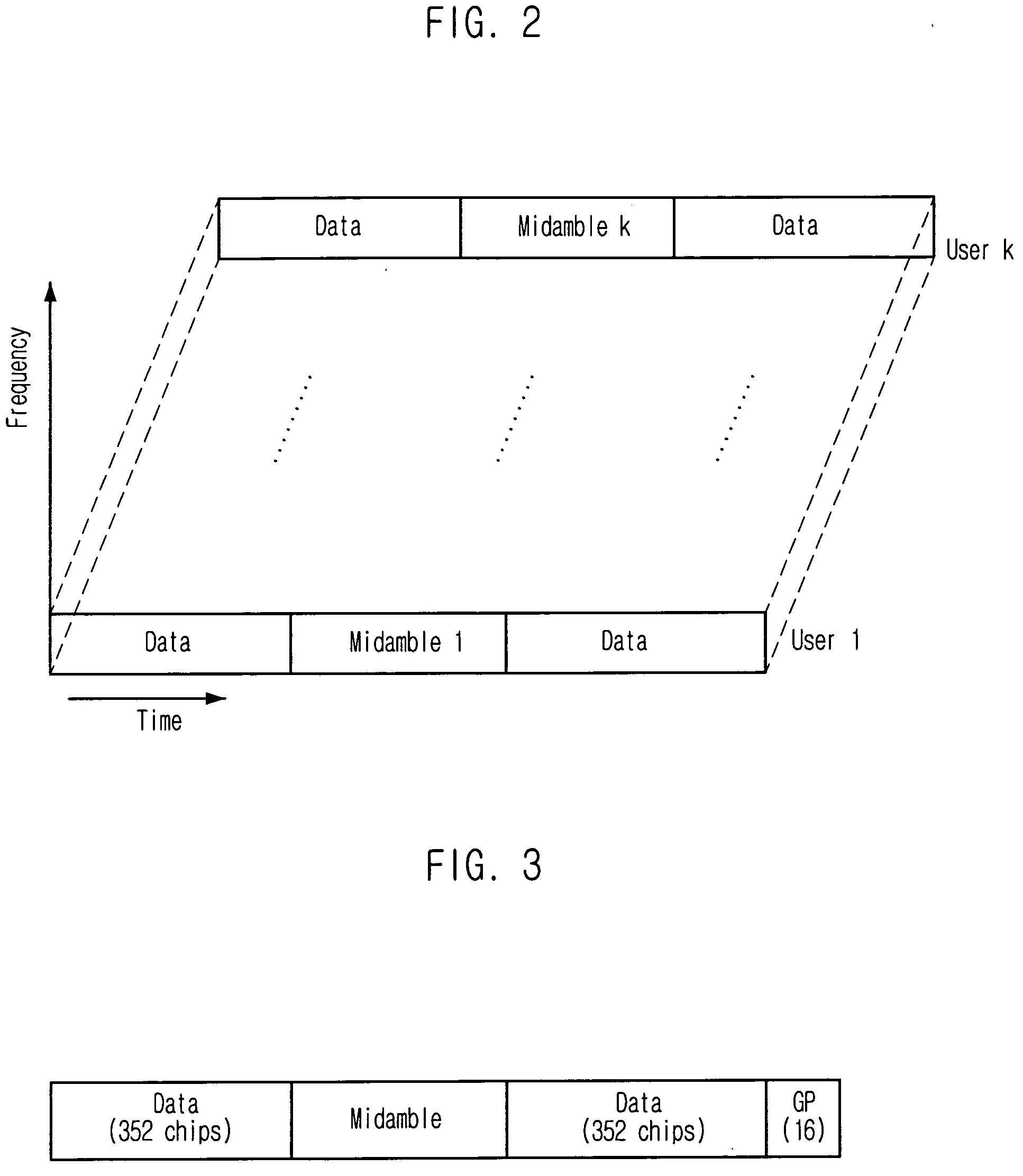

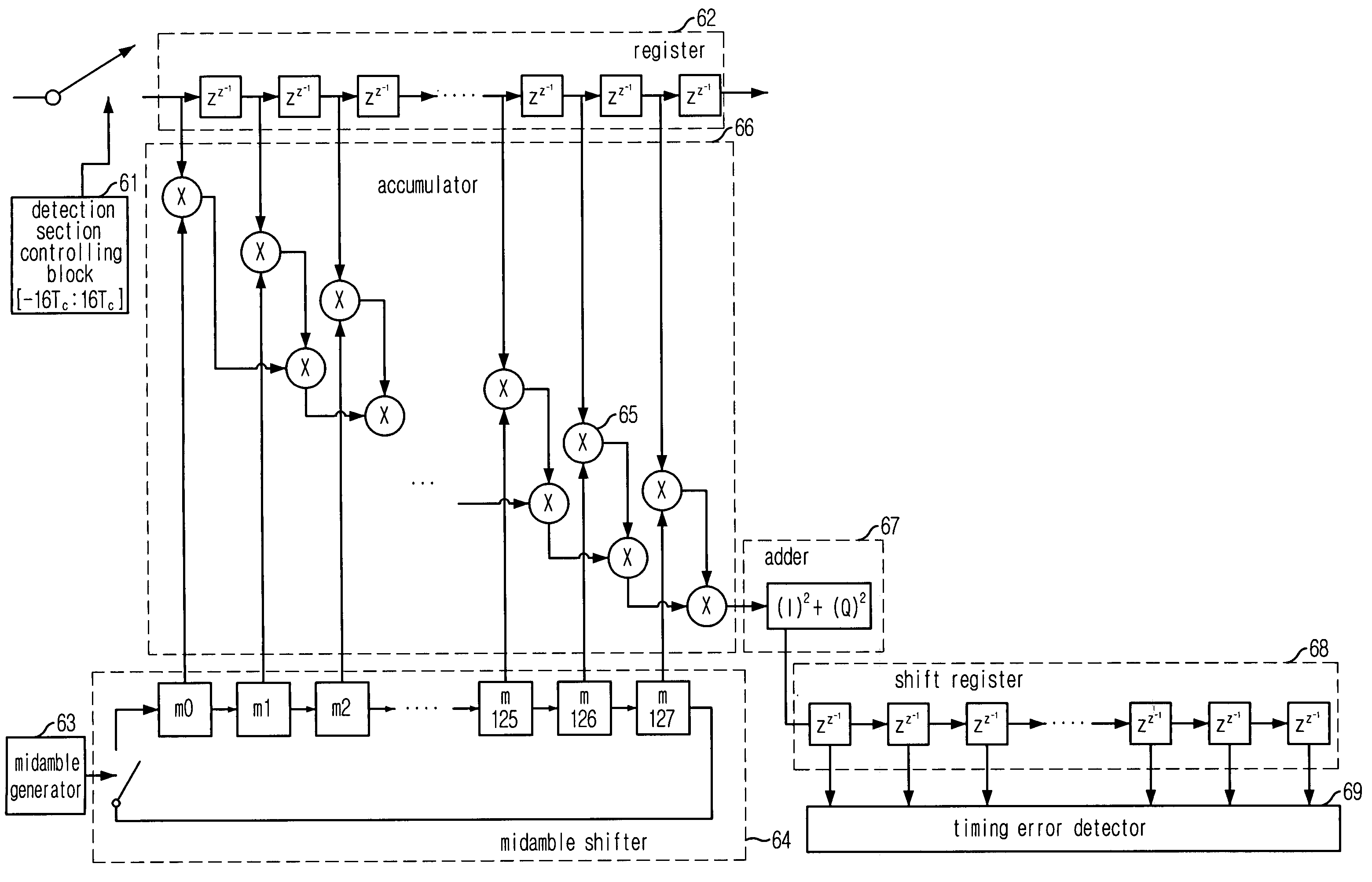

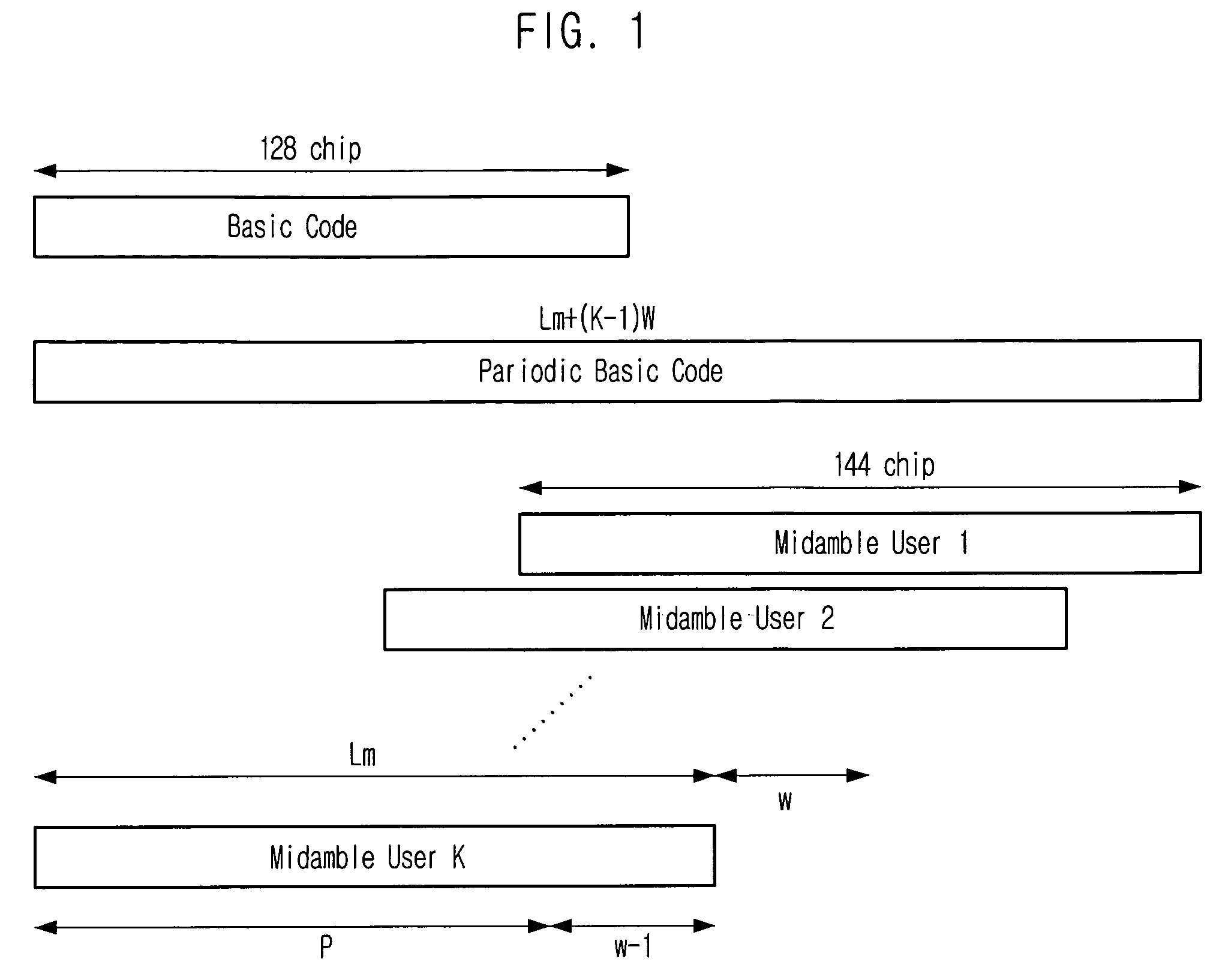

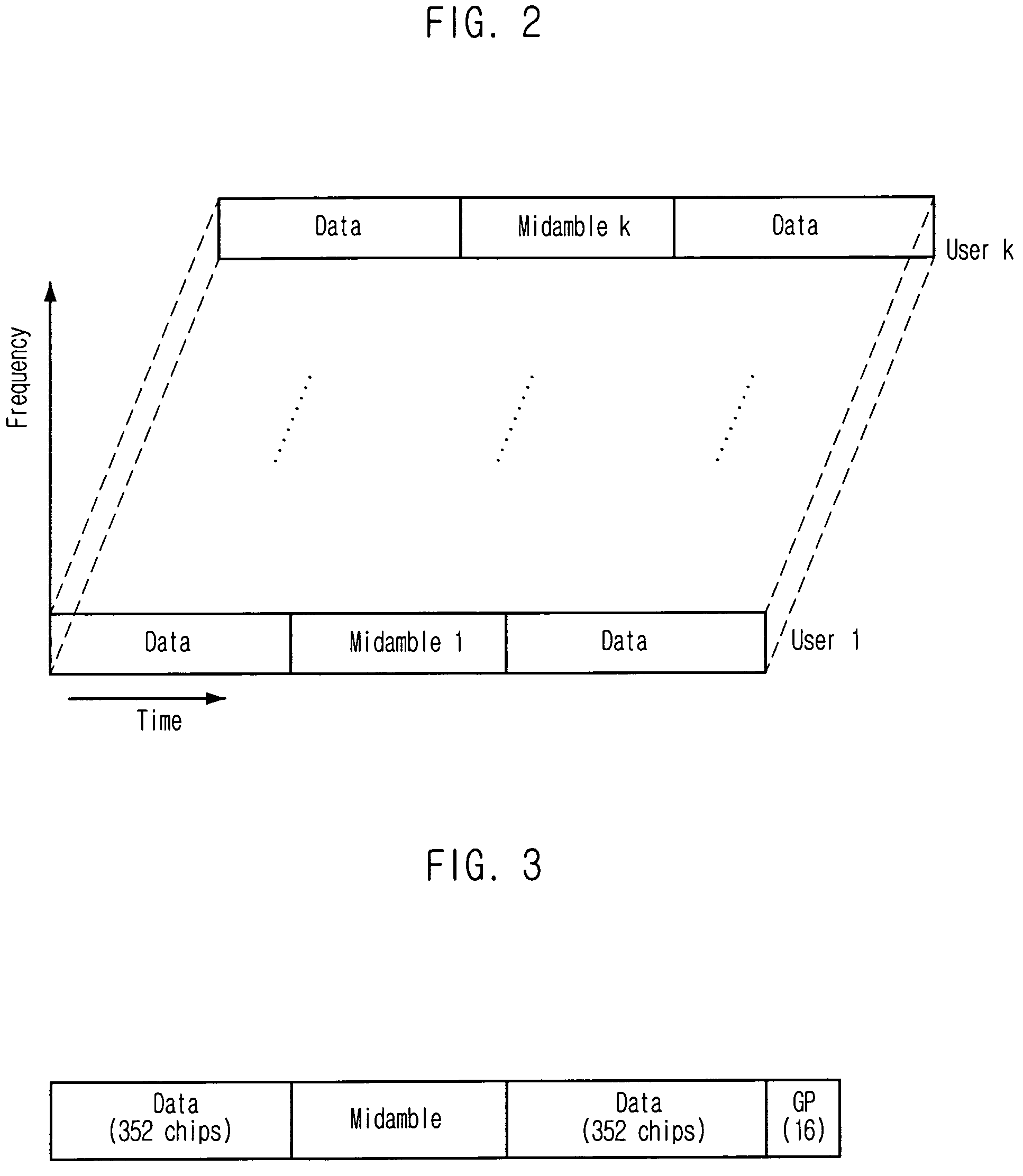

Provided is an apparatus and method for detecting timing errors based on characteristics of cyclic correlation. The apparatus and method can detect the timing errors of many users by using the cyclic characteristics of a midamble code at a time and detects the timing errors based on the characteristics of cyclic correlation to reduce the time required for detecting the users and lower the complexity in terms of Hardware. The apparatus includes a detection section controller, a register, a midamble generator, a midamble shifter, an accumulator, an adder, a shift register and a timing error detector.

Owner:ELECTRONICS & TELECOMM RES INST

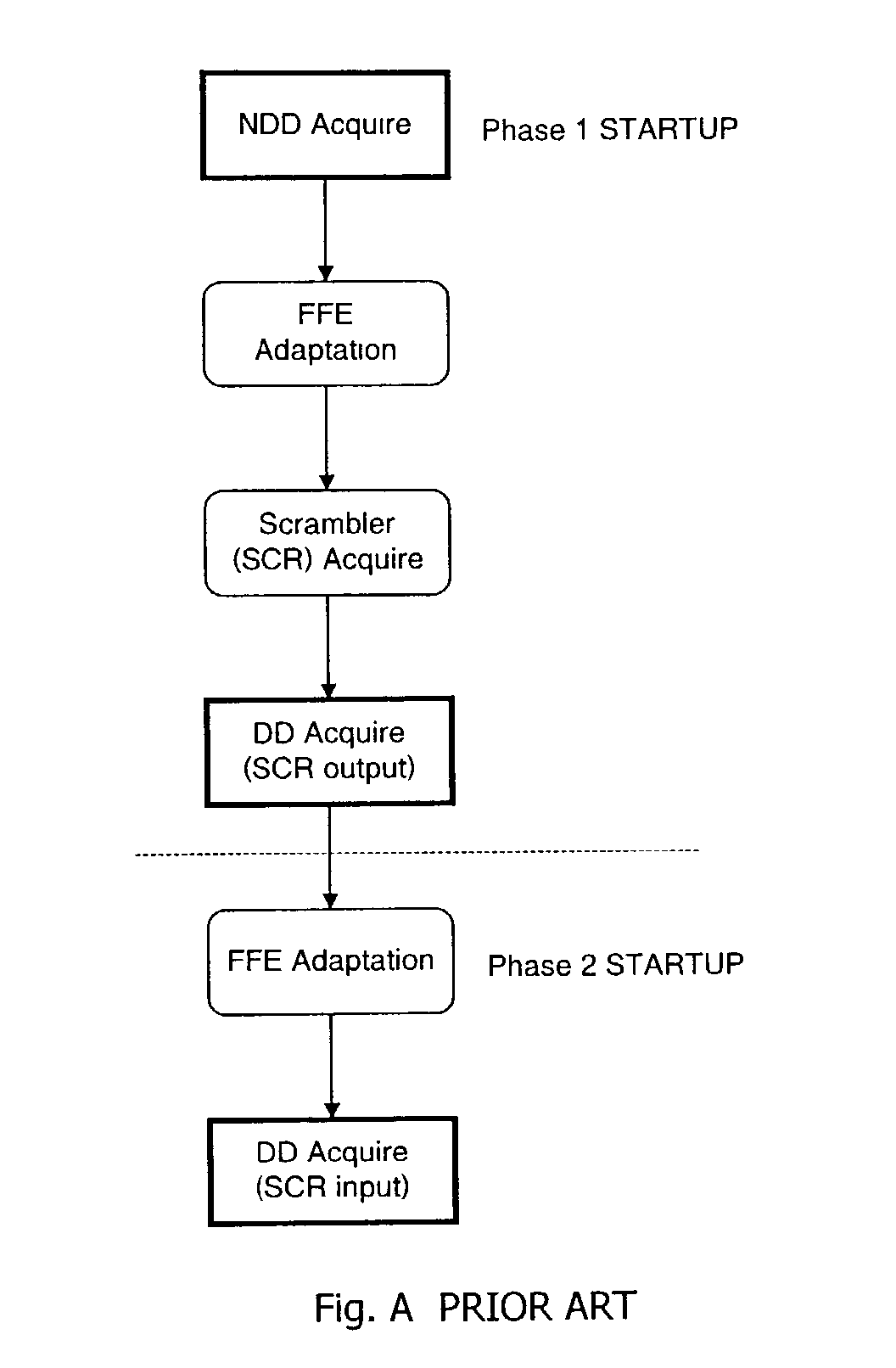

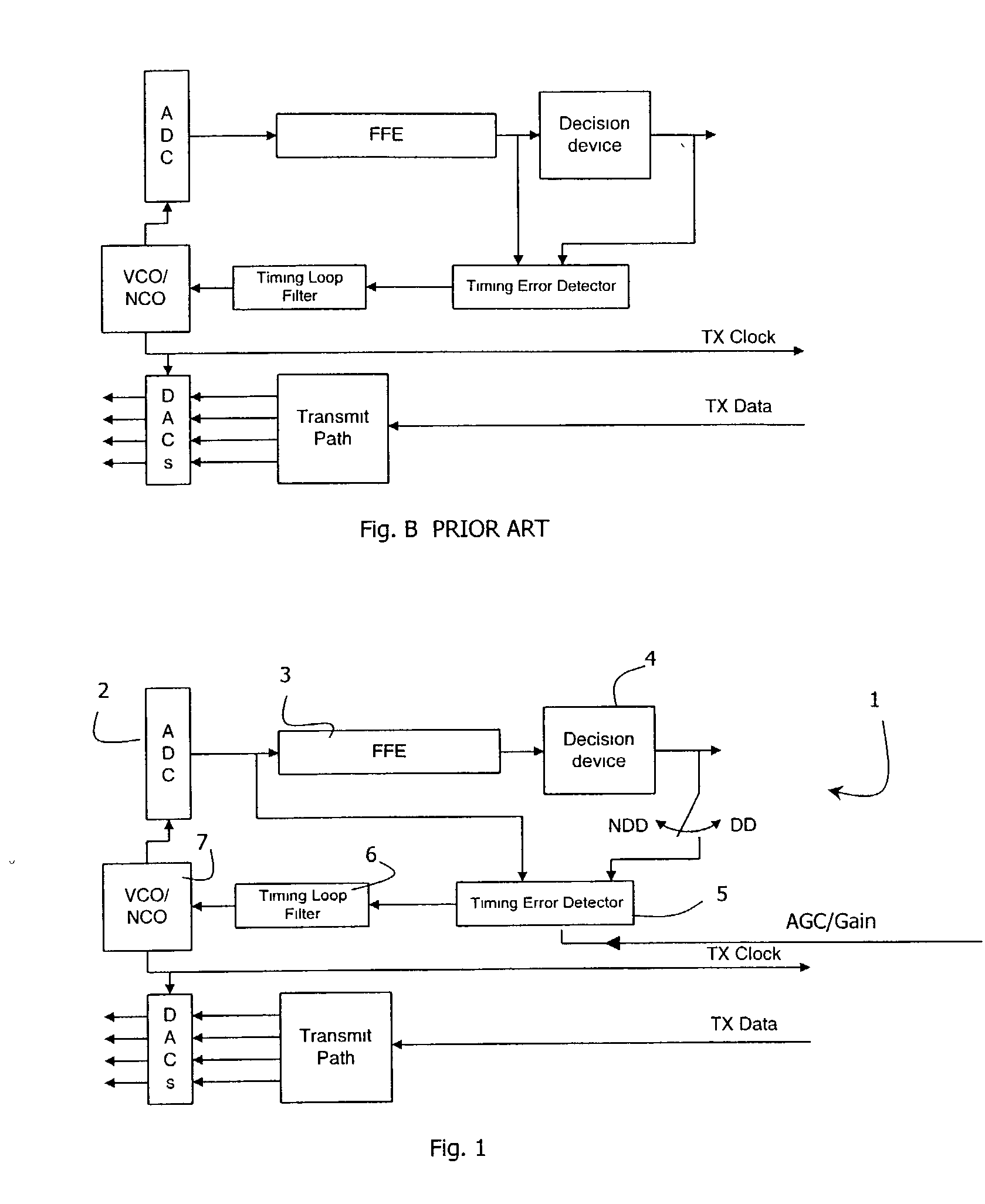

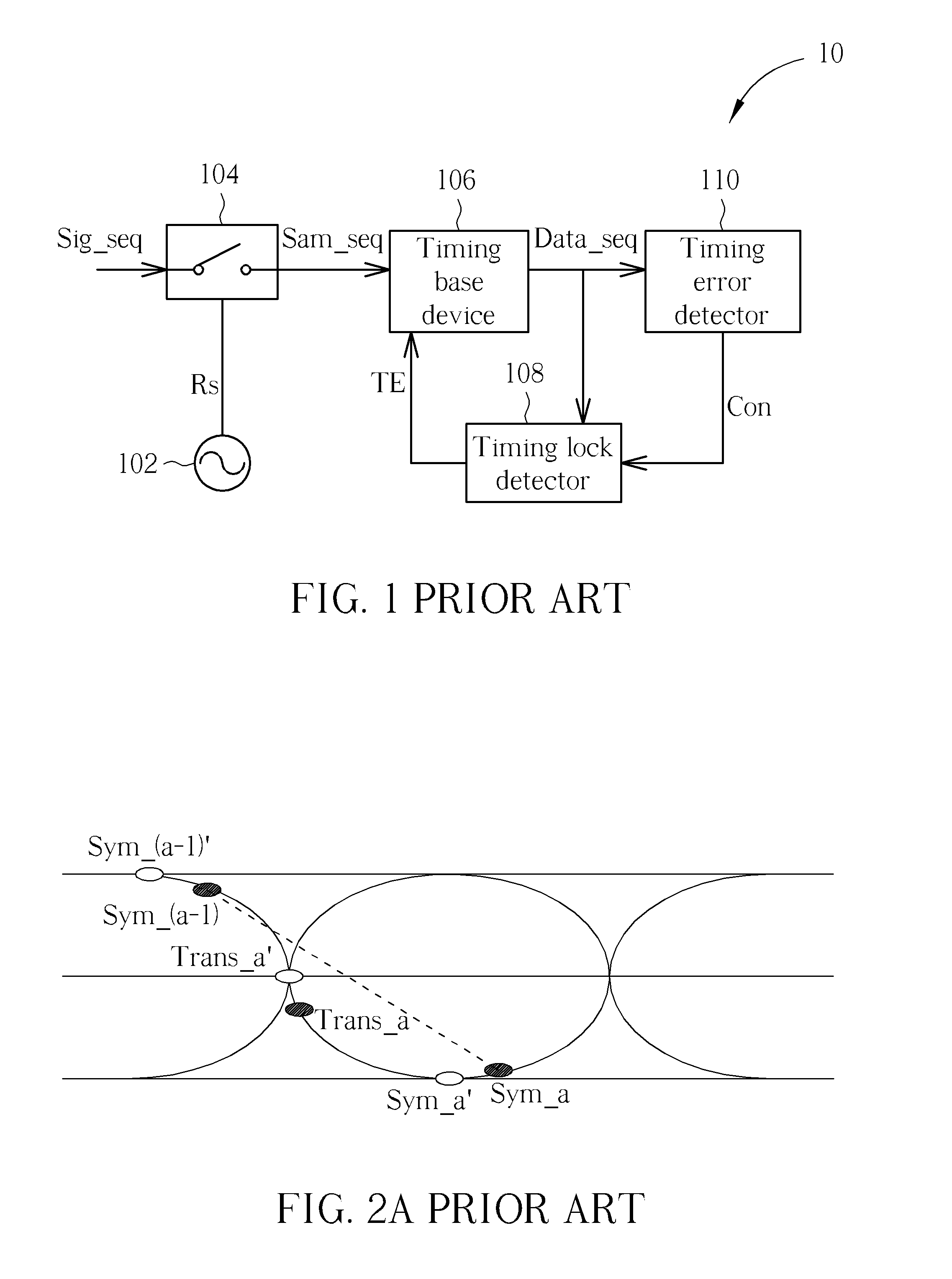

Timing recovery in data communication circuits

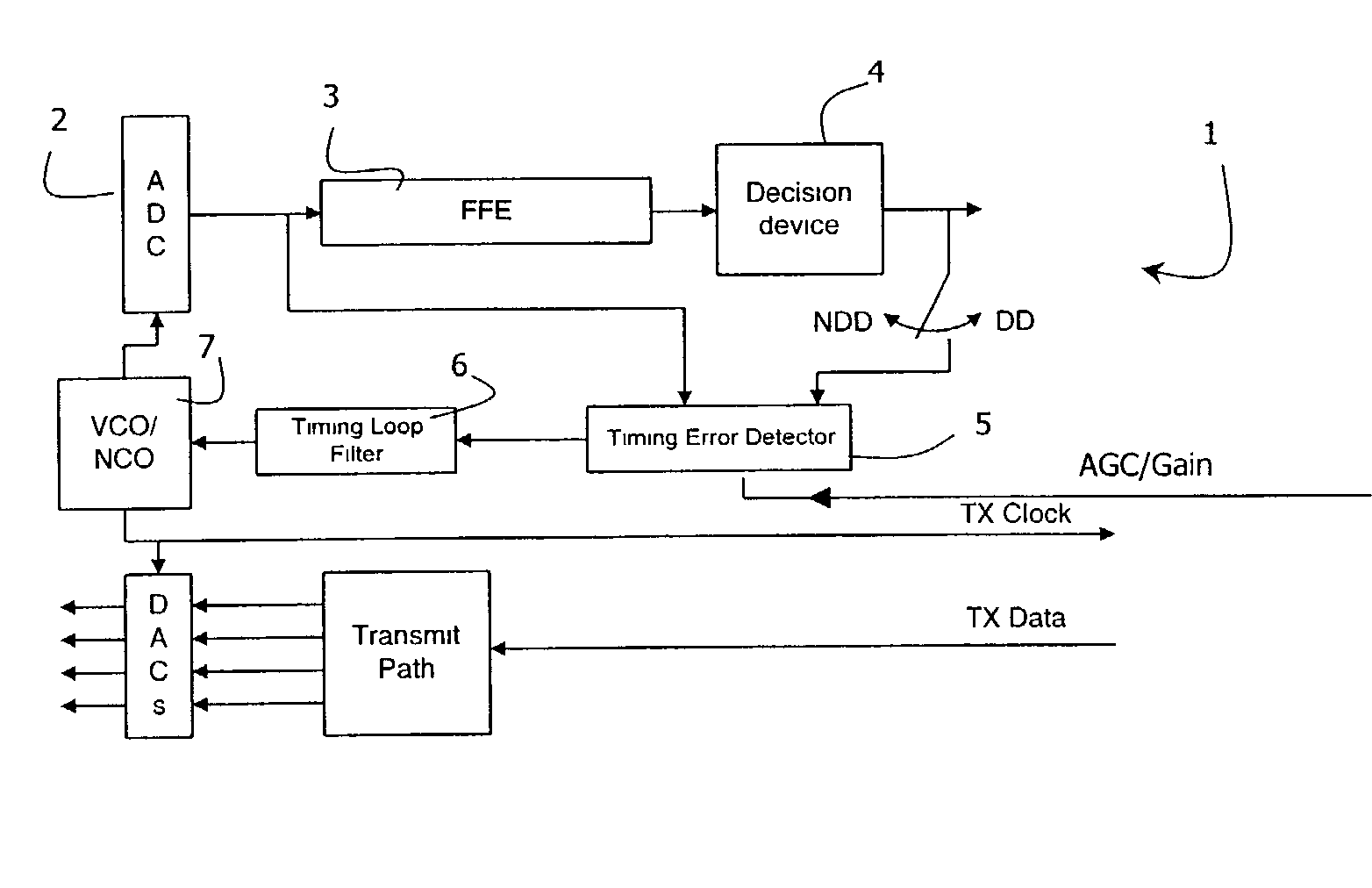

In a 1000 BASE-T transceiver, a timing error detector (TED, 5) receives its inputs directly from the output of an ADC (2) and from a decision device (4). Timing recovery is acquired in three stages: a non-decision directed (NDD) stage during which only the output of an ADC (2) are used for acquisition; a stage for acquiring the remote scrambler and predicting symbols; and a decision-directed (DD) stage during which locally predicted symbols are also used for acquisition. Because the timing error detector (TED, 5) does not take inputs from the FFE (3) there is no information about cable length, and so an input of gain from an AGC is used to indicate cable length.

Owner:LSI CORPORATION

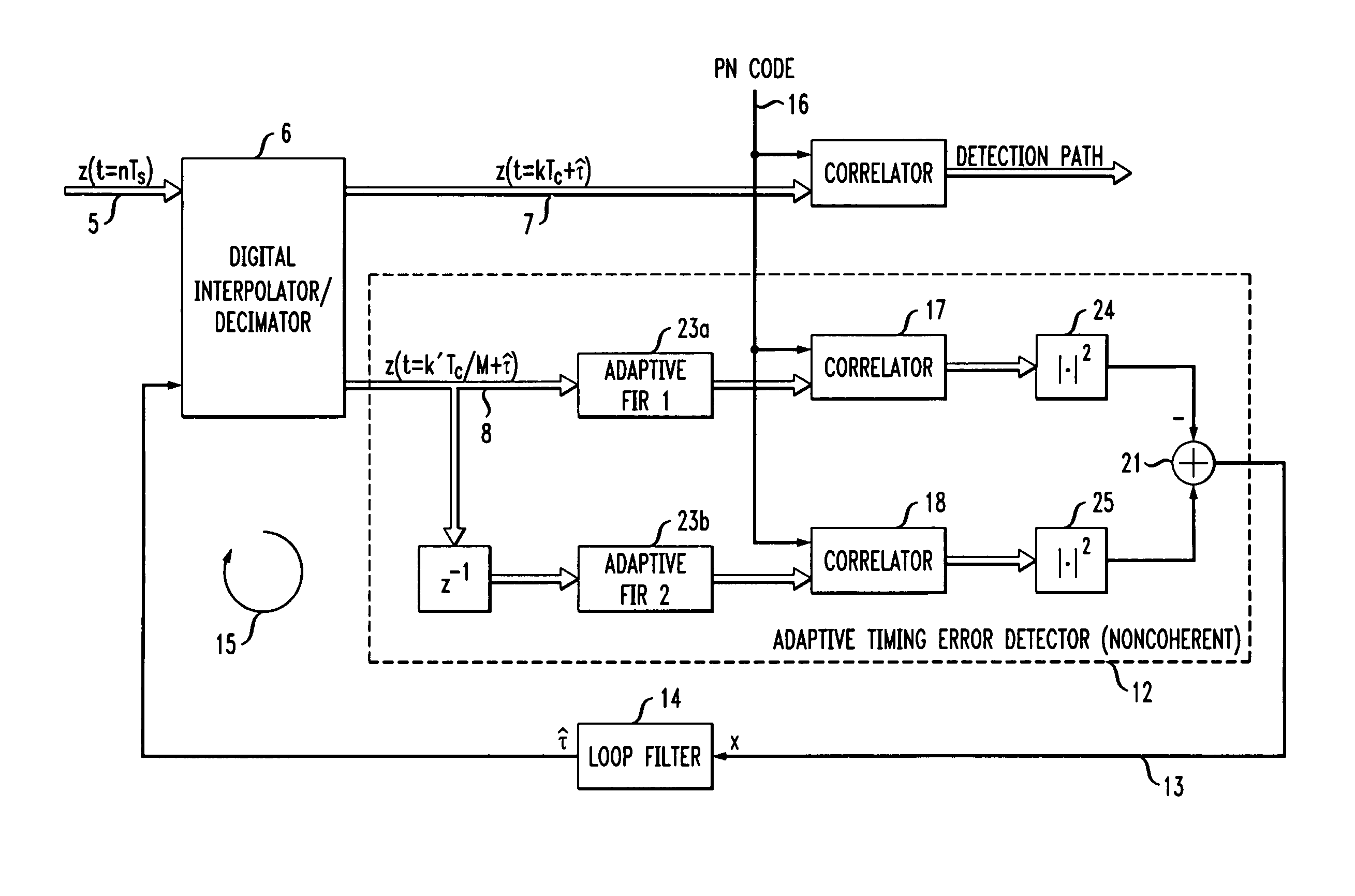

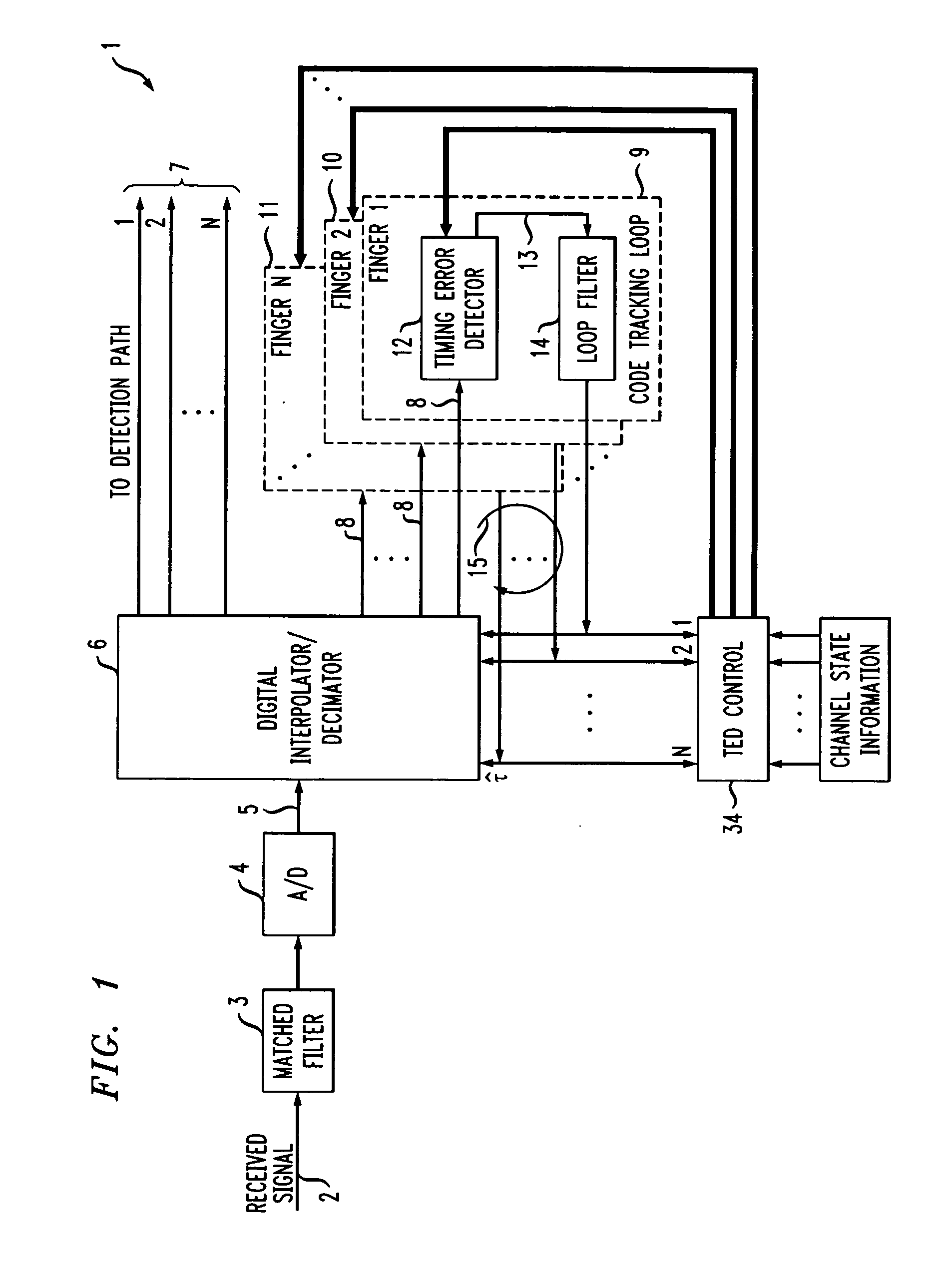

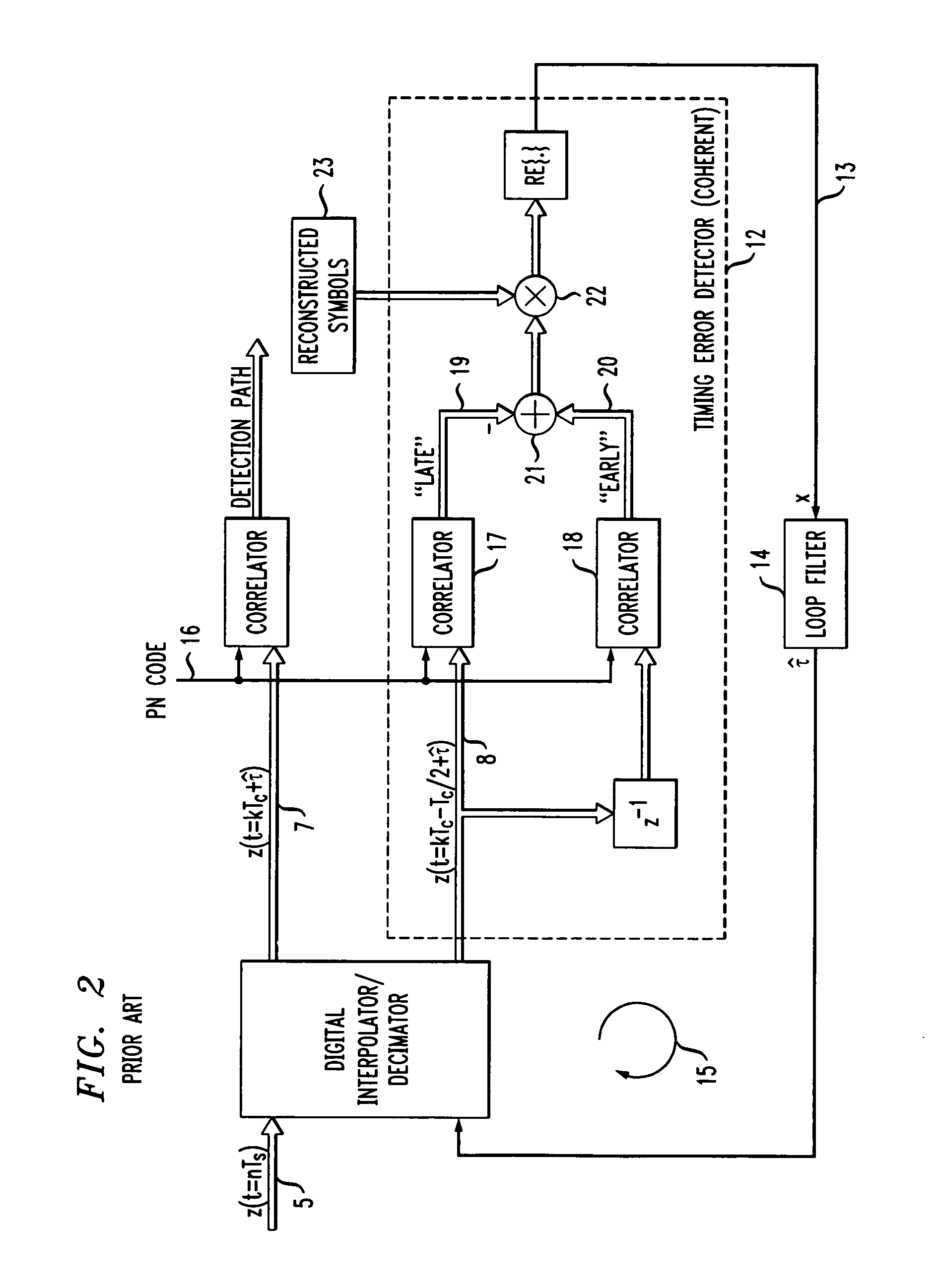

Adaptive code-tracking receiver for direct-sequence code-division multiple access (CDMA) communications over multipath fading channels and method for signal processing in a rake receiver

InactiveUS7142585B2Improve tracking performanceTransmissionSignal-to-noise ratio (imaging)Time division multiple access

The invention is directed to a method for signal processing in a rake receiver for spread spectrum signals and is directed to a rake receiver for spread spectrum signals including a plurality of rake fingers (9, 10, 11) each rake finger being adapted to receive a signal (7, 8) being part of a multipath signal (2) and associated with a path of the multipath, the signal (7, 8) having a delay (τ) relative to an other signal associated with an other path of the multipath (7, 8), the receiver comprises a summation unit (37) for generating an output signal from the signals received from of at least some of the rake fingers (9, 10, 11), the output signal being a summation signal having and improved signal to noise ratio (SNR) if compared with the signal to noise ratio (SNR) of at least, one of the rake fingers (9, 10, 11), a timing error detector (12) for detecting a delay (τ) between signals of at least two rake fingers (9, 10, 11) and for generating a timing error signal which is sent to a unit (6) for compensating the error of the respective delay (τ); to provide a code-tracking unit for a direct-sequence code division multiple access (DS-CDMA) receiver having an improved tracking performance, especially in cases where delay times of multipath signals are in the order of the chip duration the timing error detector (12) generates a timing error signal (x, 13) based on the signals (7, 8) associated with paths of the multipath of more than one rake finger (9, 10, 11).

Owner:LUCENT TECH INC

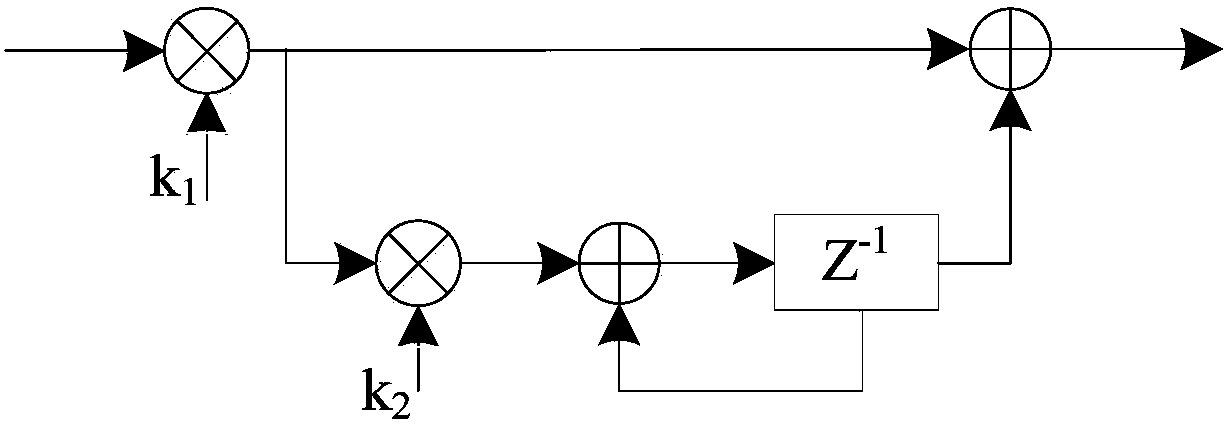

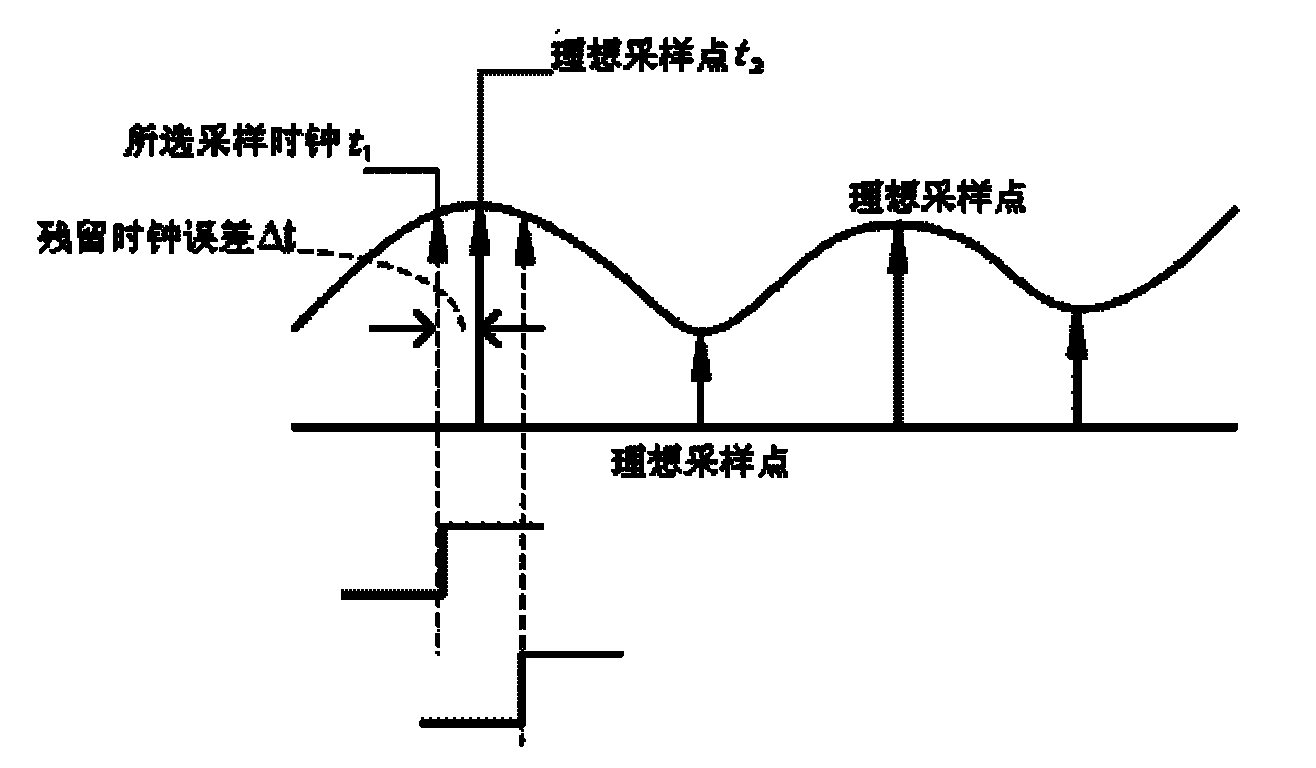

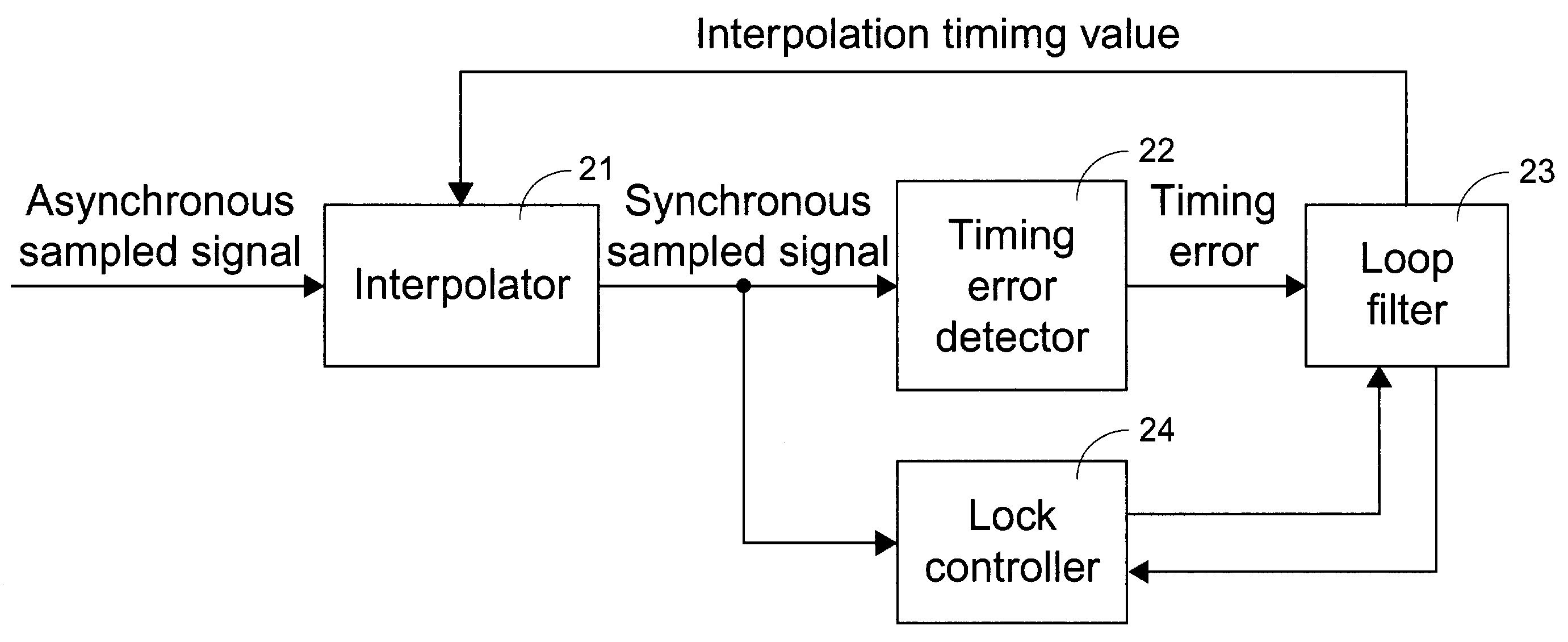

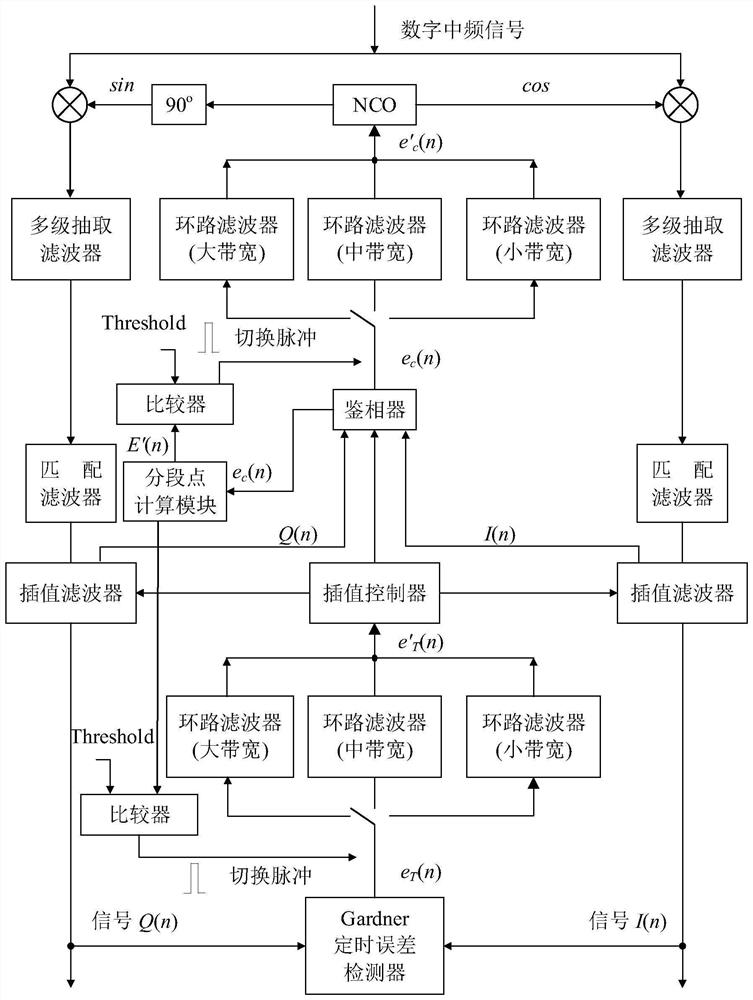

Interpolation-based all-digital high-speed parallel timing synchronization method

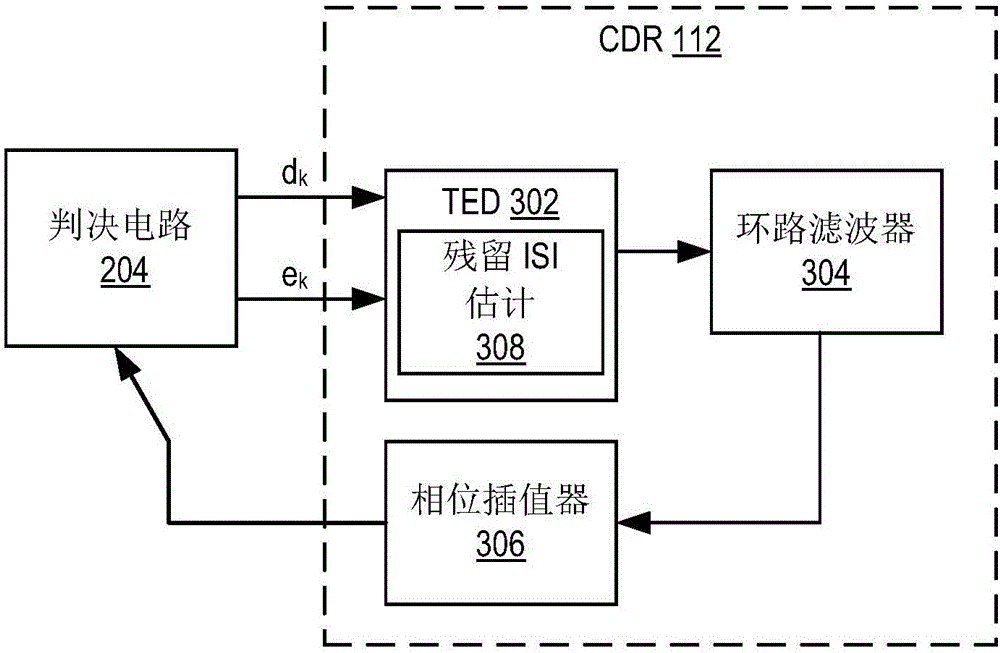

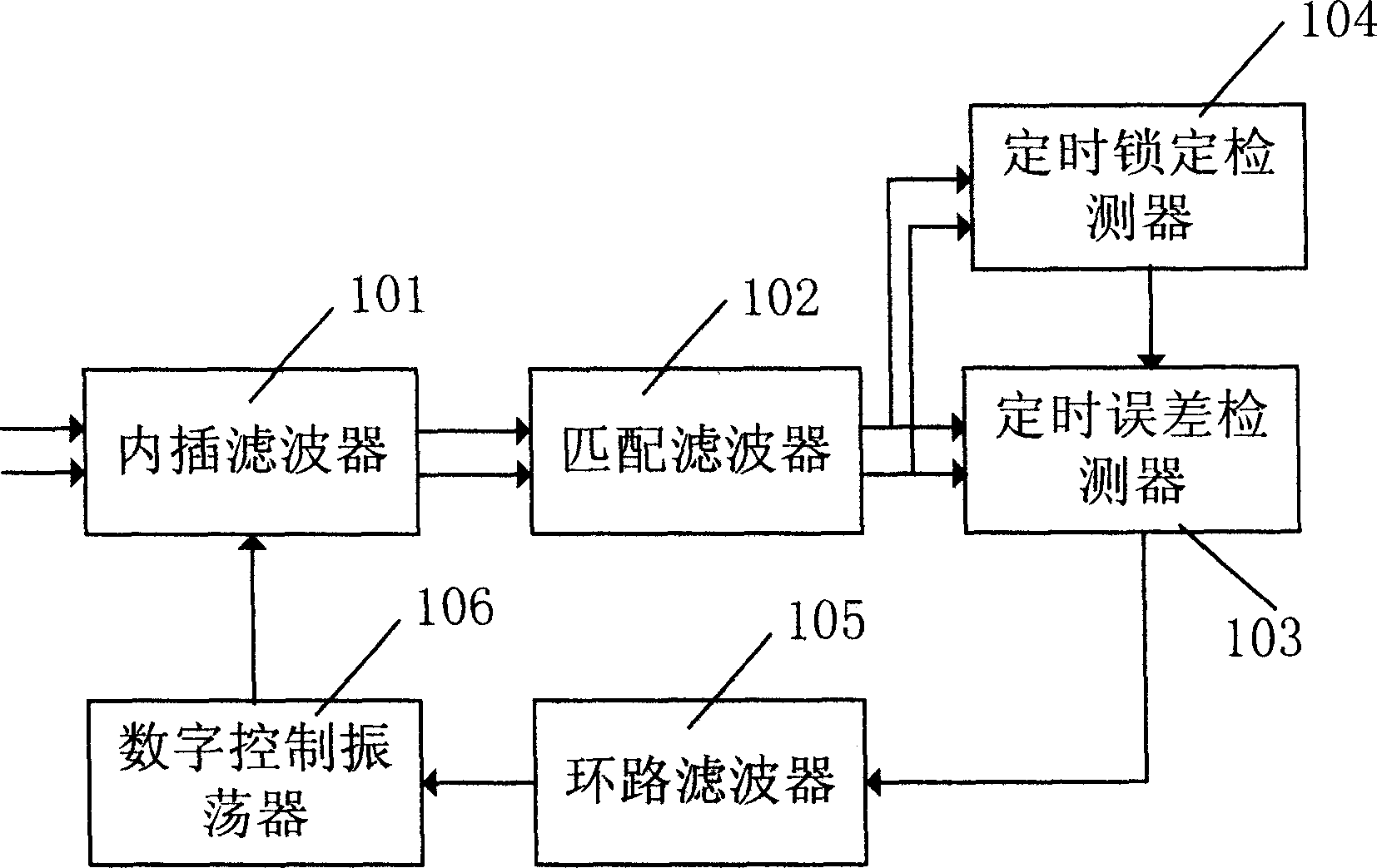

InactiveCN103746790AReduce demandAccurate timing synchronizationSynchronising arrangementLoop filterDigital control oscillator

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

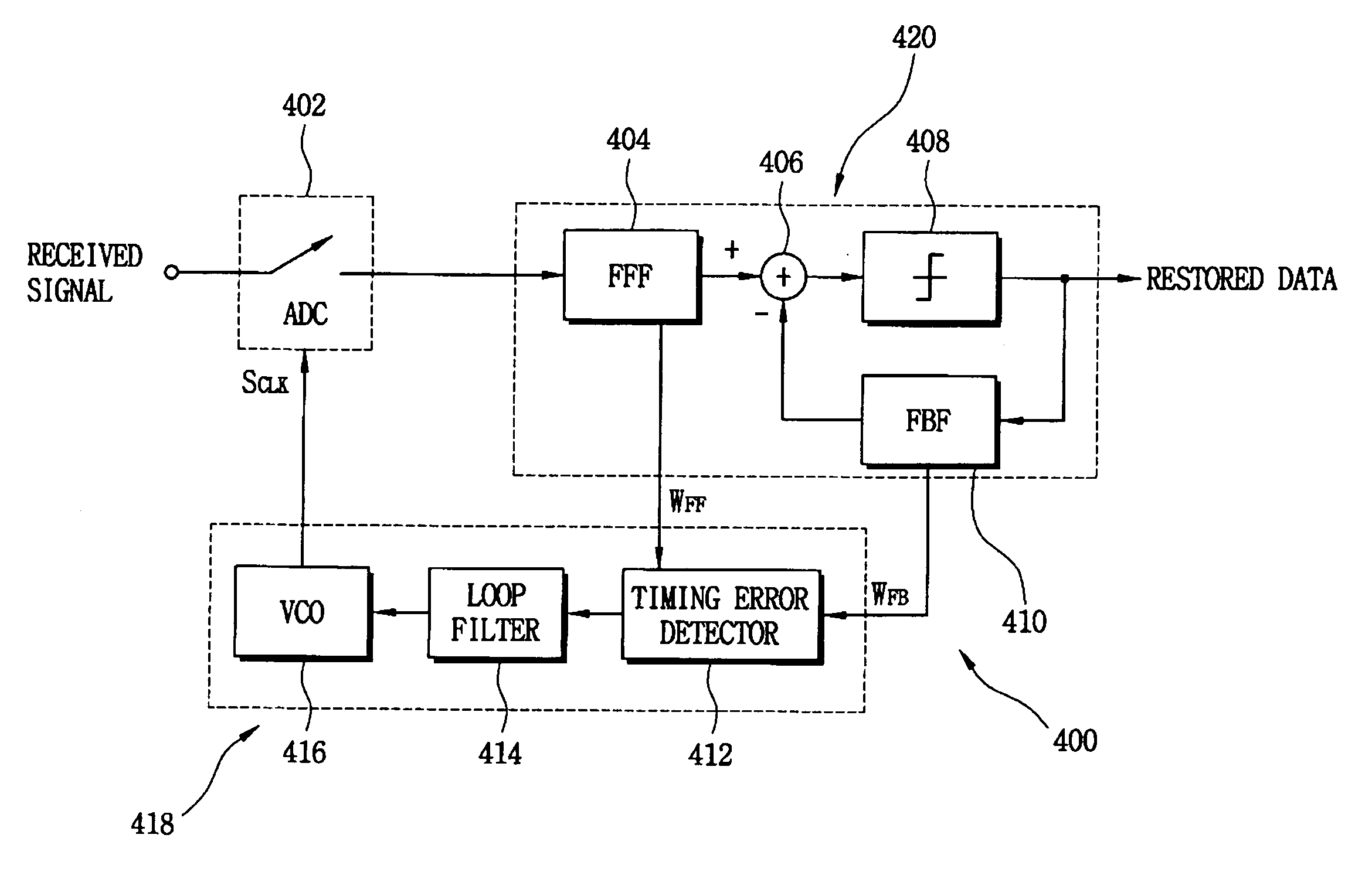

Timing recovery circuit and timing recovery method

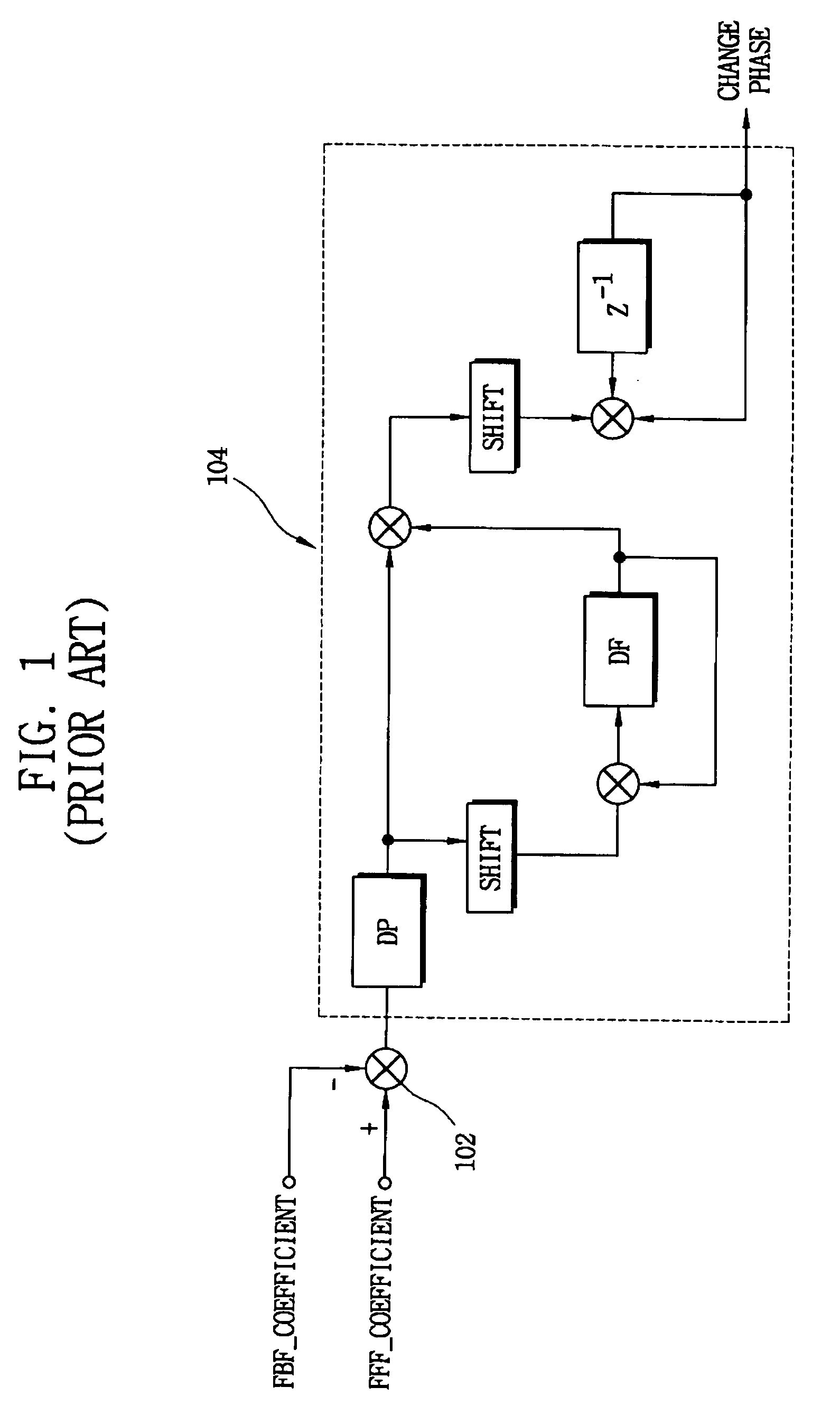

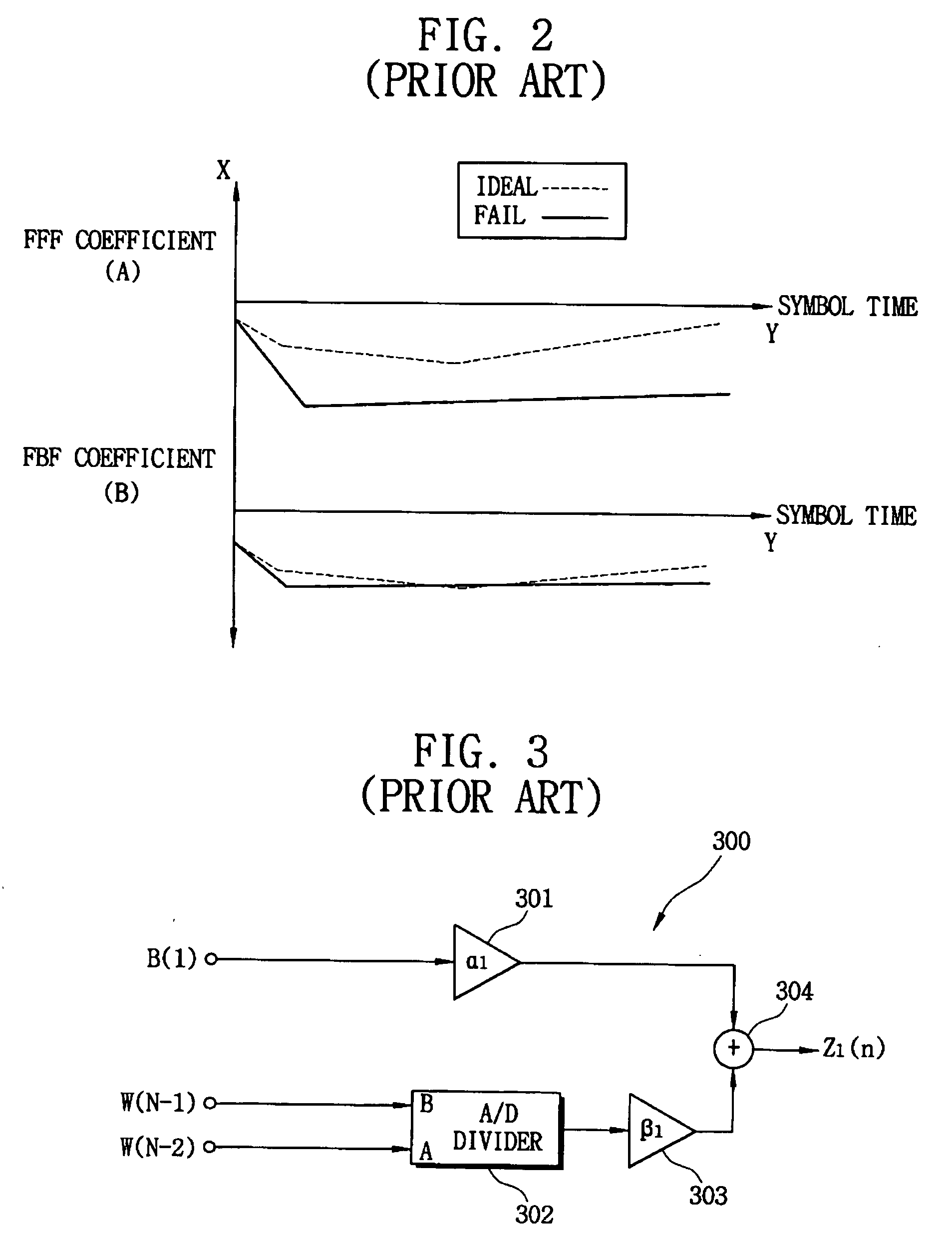

A timing recovery circuit for a receiver may include a timing error detector that generates a timing error based on differences between coefficients of a feed-forward filter and a feed-back filter. The timing recovery circuit may include a loop filter which generates a control voltage signal based on the timing error, and a voltage controlled oscillator that generates a sampling clock for the receiver based on the generated control voltage signal.

Owner:SAMSUNG ELECTRONICS CO LTD

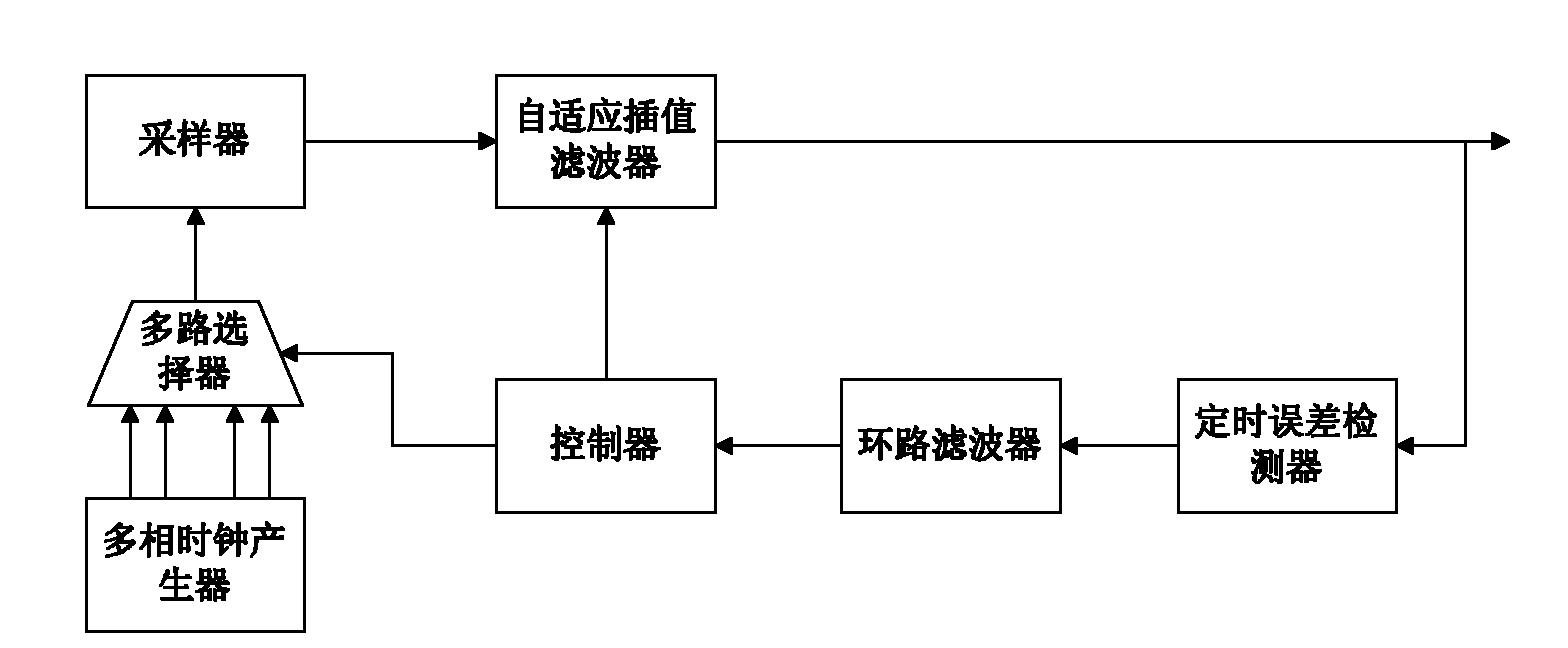

Timing synchronization device based on symbol rate adaptive-interpolation and synchronization method thereof

InactiveCN101895334AReduce the sampling frequencyReduce power consumptionRadio transmission for post communicationHigh level techniquesLoop filterMultiplexer

The invention provides a timing synchronization device based on a symbol rate adaptive-interpolation and a synchronization method thereof, belonging to the wireless communication technical field. The device comprises a sampler, an adaptive-interpolation filter, a timing error detector, a loop filter, a controller, a multi-phase clock generator and a multiplexer, wherein, the sampler is connected with the adaptive-interpolation filter; the adaptive-interpolation filter is connected with the timing error detector; the timing error detector is connected with the loop filter; the loop filter is connected with the controller; the controller is connected with the adaptive-interpolation filter and the multiplexer; the multi-phase clock generator is connected with the multiplexer; and the multiplexer is connected with the sampler. The invention greatly lowers sampling frequency so as to reduce power consumption, obtains the result close to an ideal sampling value, reduces the number of multiphase clocks and lowers complexity.

Owner:SHANGHAI JIAO TONG UNIV

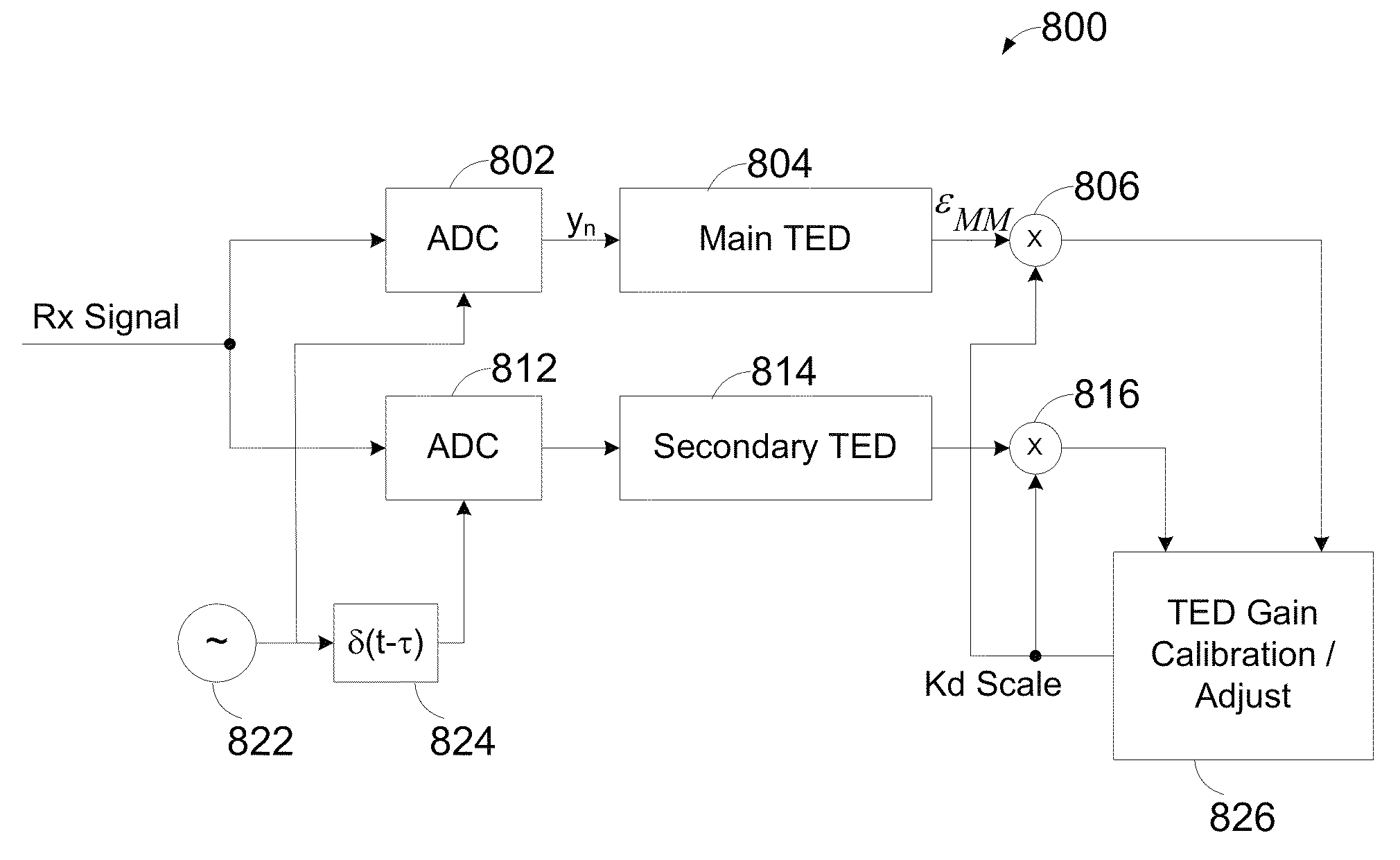

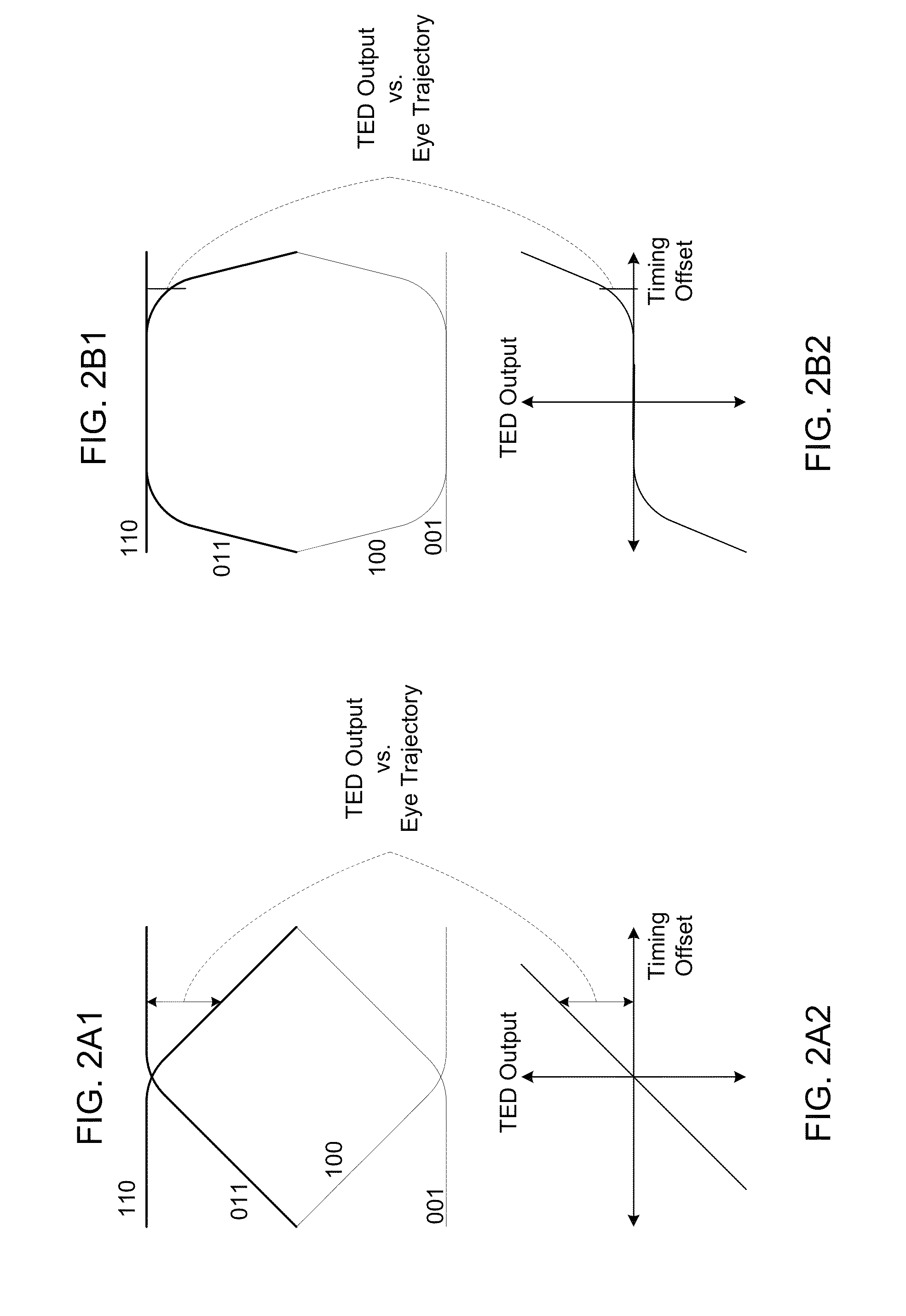

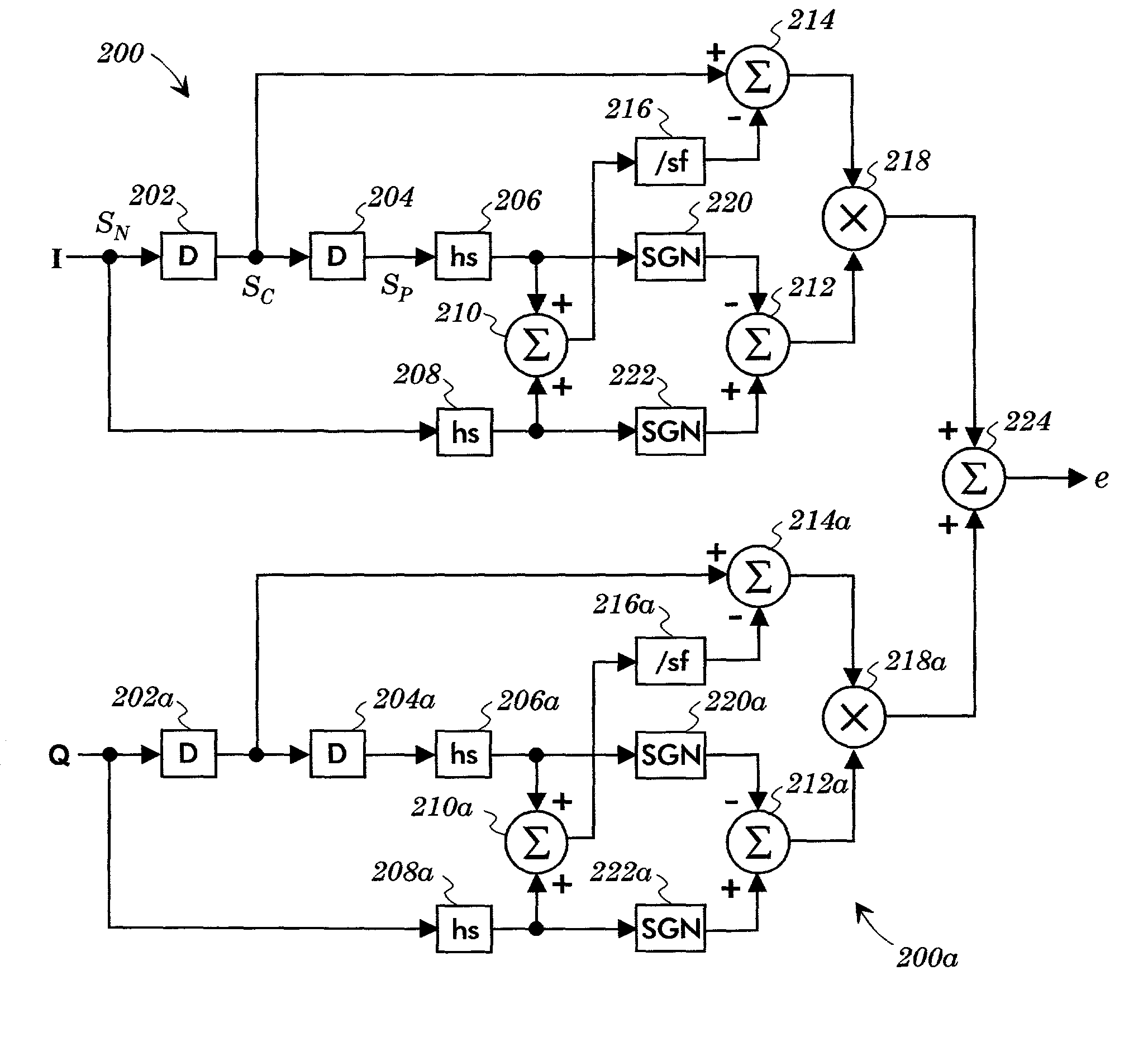

Gain calibration for a Mueller-Muller type timing error detector

ActiveUS8693596B1Less powerReduce unpredictabilityGain controlData switching by path configurationClock recoveryTiming error detector

Apparatus and methods calibrate and control detector gain in a Mueller-Muller timing detector. A main signal path includes a Mueller-Muller based timing error detector (MM TED). The main signal path generates a main error signal for clock recovery. A secondary signal path that includes a secondary MM TED. Each signal path samples soft symbols from a received signal. The sampling of the secondary MM TED is deliberately offset in time. A scale factor applied to the main error signal and to a secondary error signal is adaptively adjusted based on a comparison between the main error signal and the secondary error signal.

Owner:MICROSEMI STORAGE SOLUTIONS

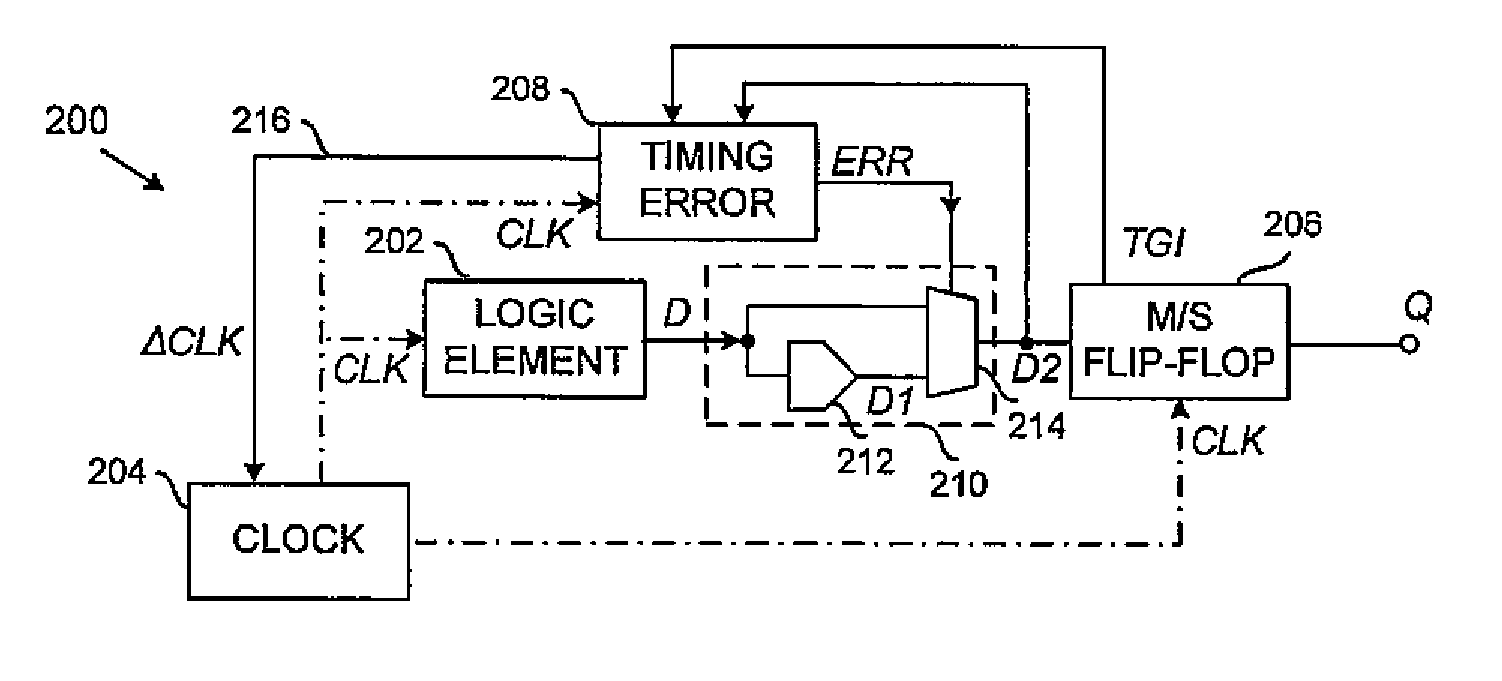

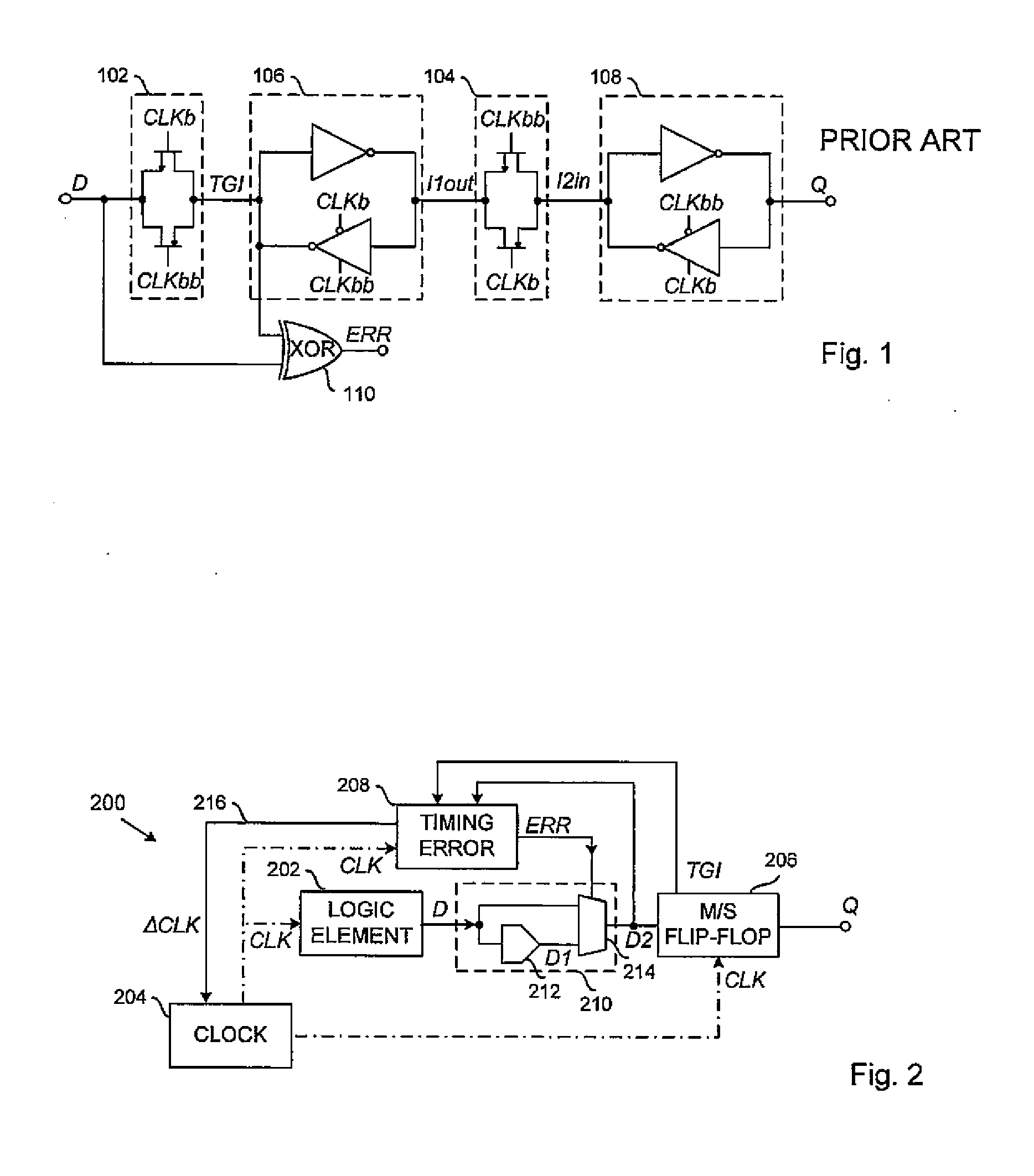

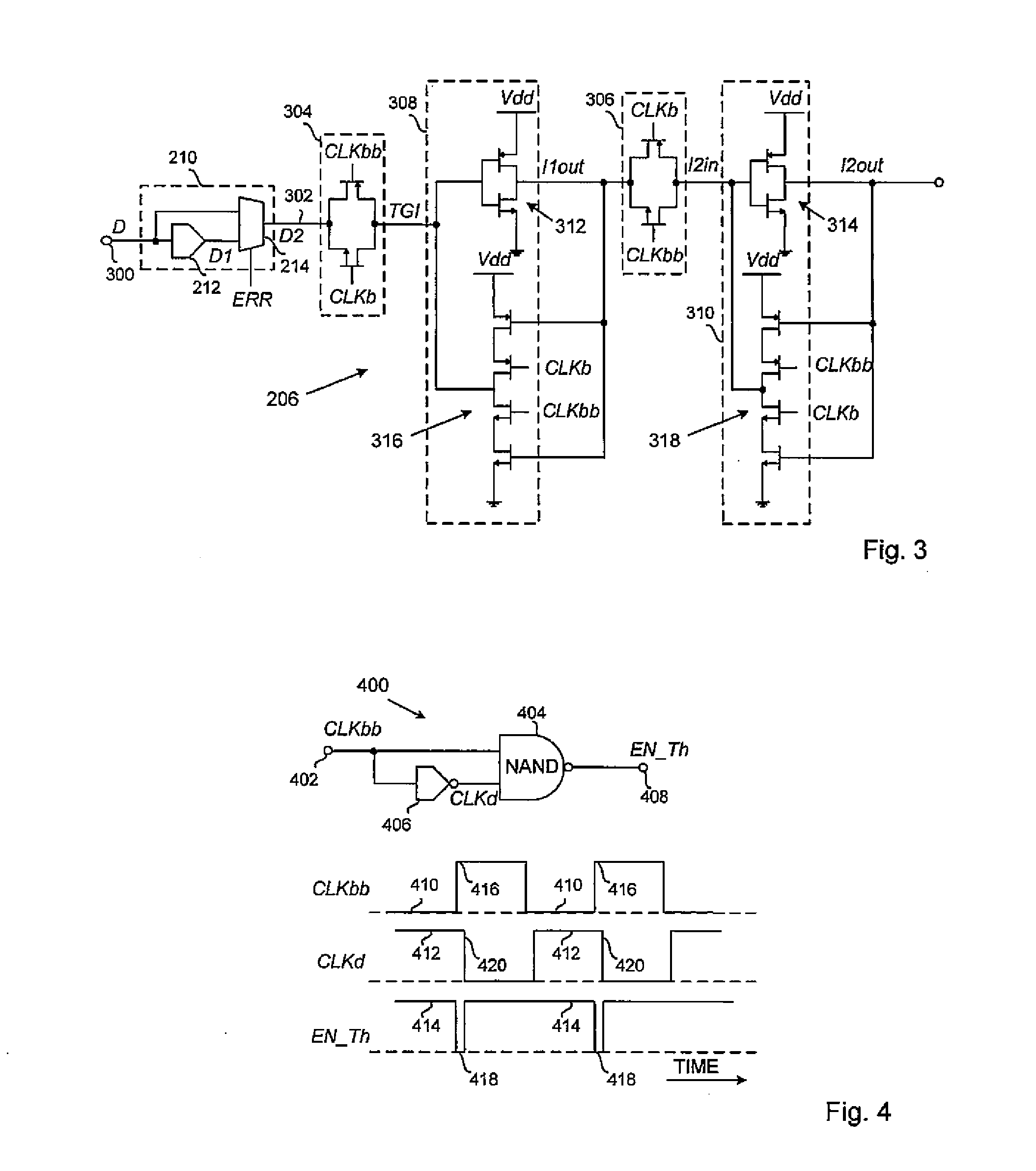

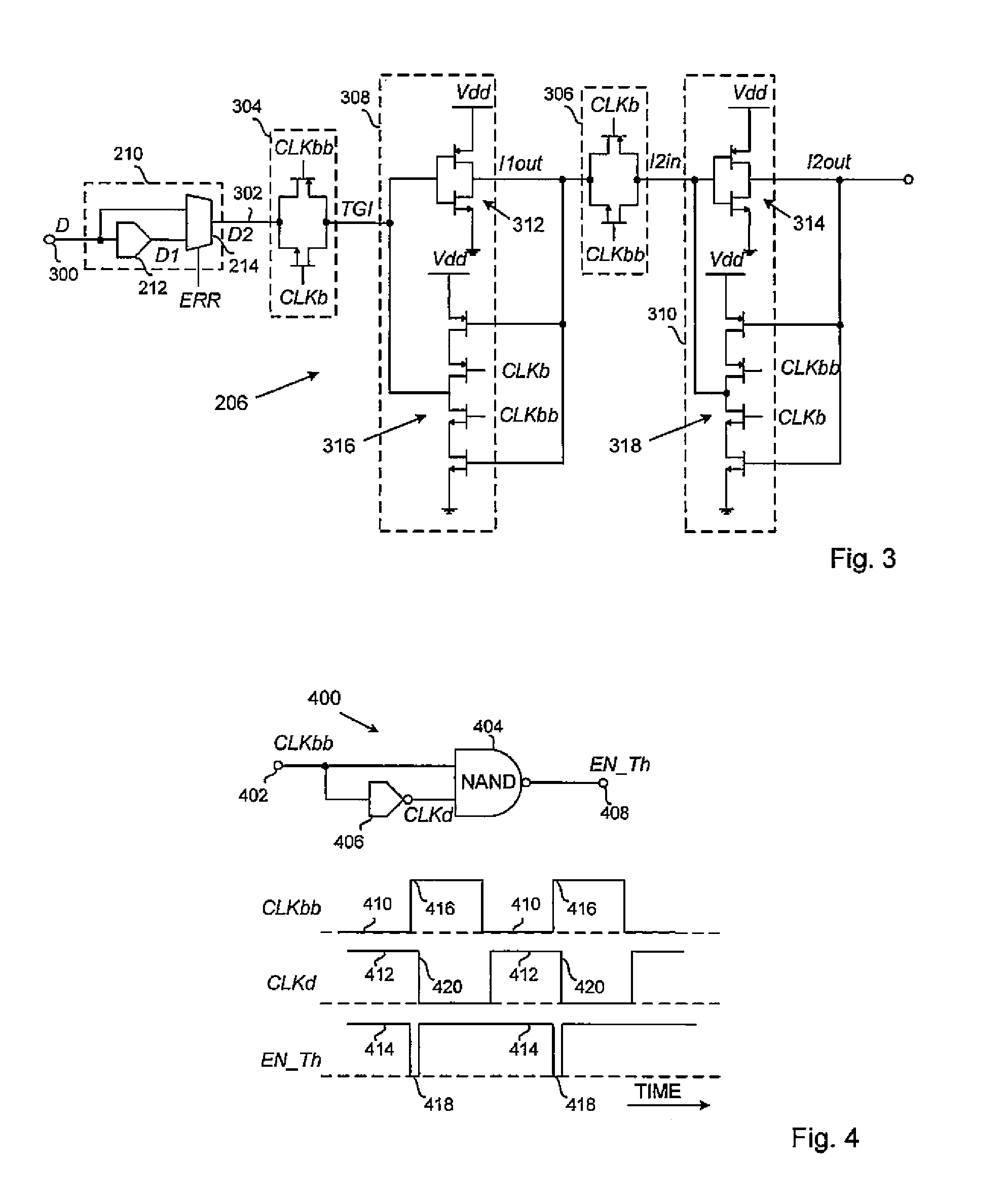

Master-slave flip-flop with timing error correction

A digital logic circuit includes a logic element for providing a data signal, a clock for providing a clock signal and a master-slave flip-flop. The master-slave flip-flop includes a master latch for storing data on a master latch input at a first active edge of the clock signal and a slave latch for storing data on an output of the master latch at a second active edge of the clock signal following the first active edge. A timing error detector asserts an error signal in response to a change in the data signal during a detection period following the first active edge of the clock signal. A timing correction module selectively increases a propagation delay of the data signal from the logic element to the master latch input in response to the error signal.

Owner:NXP USA INC

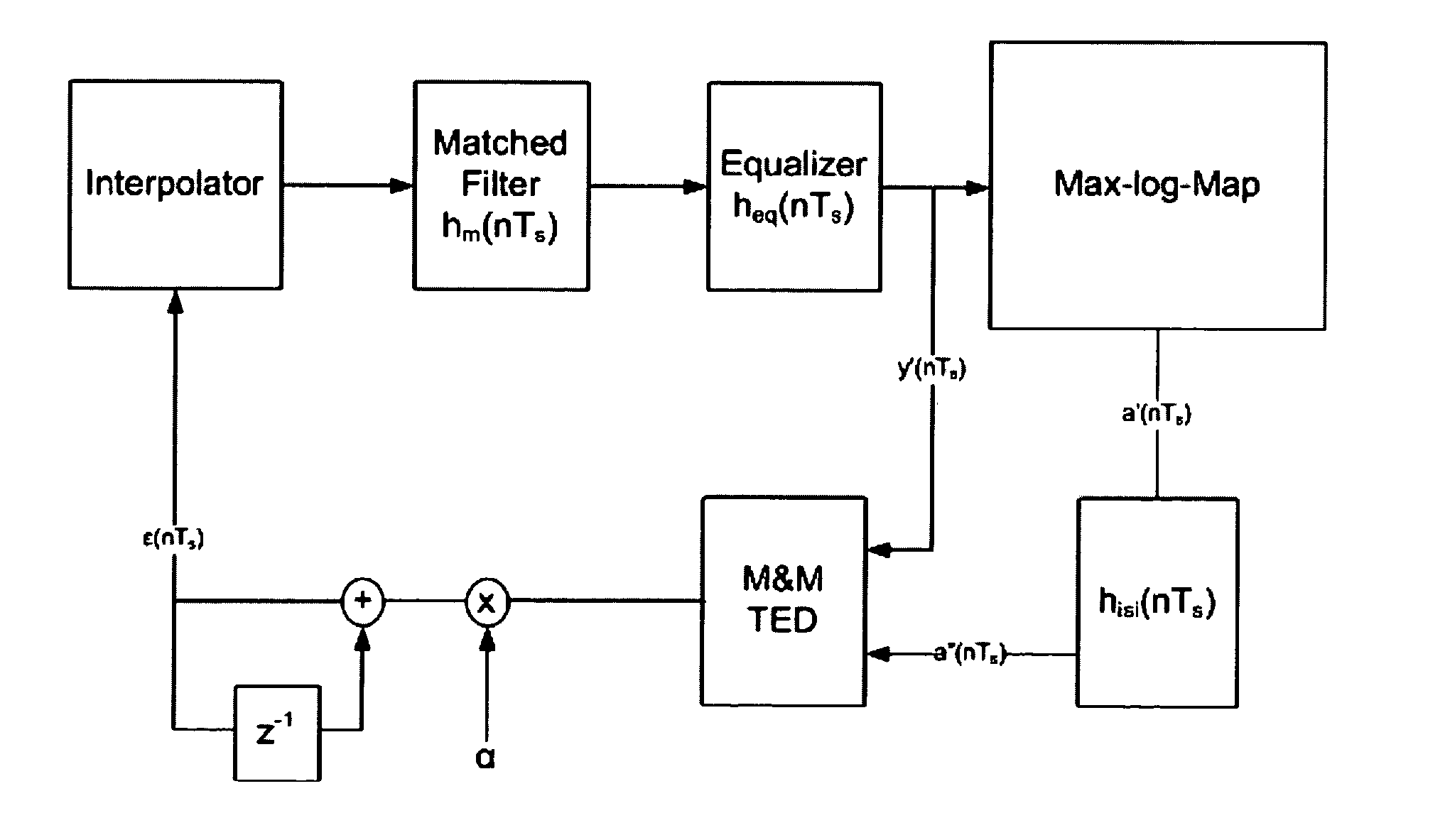

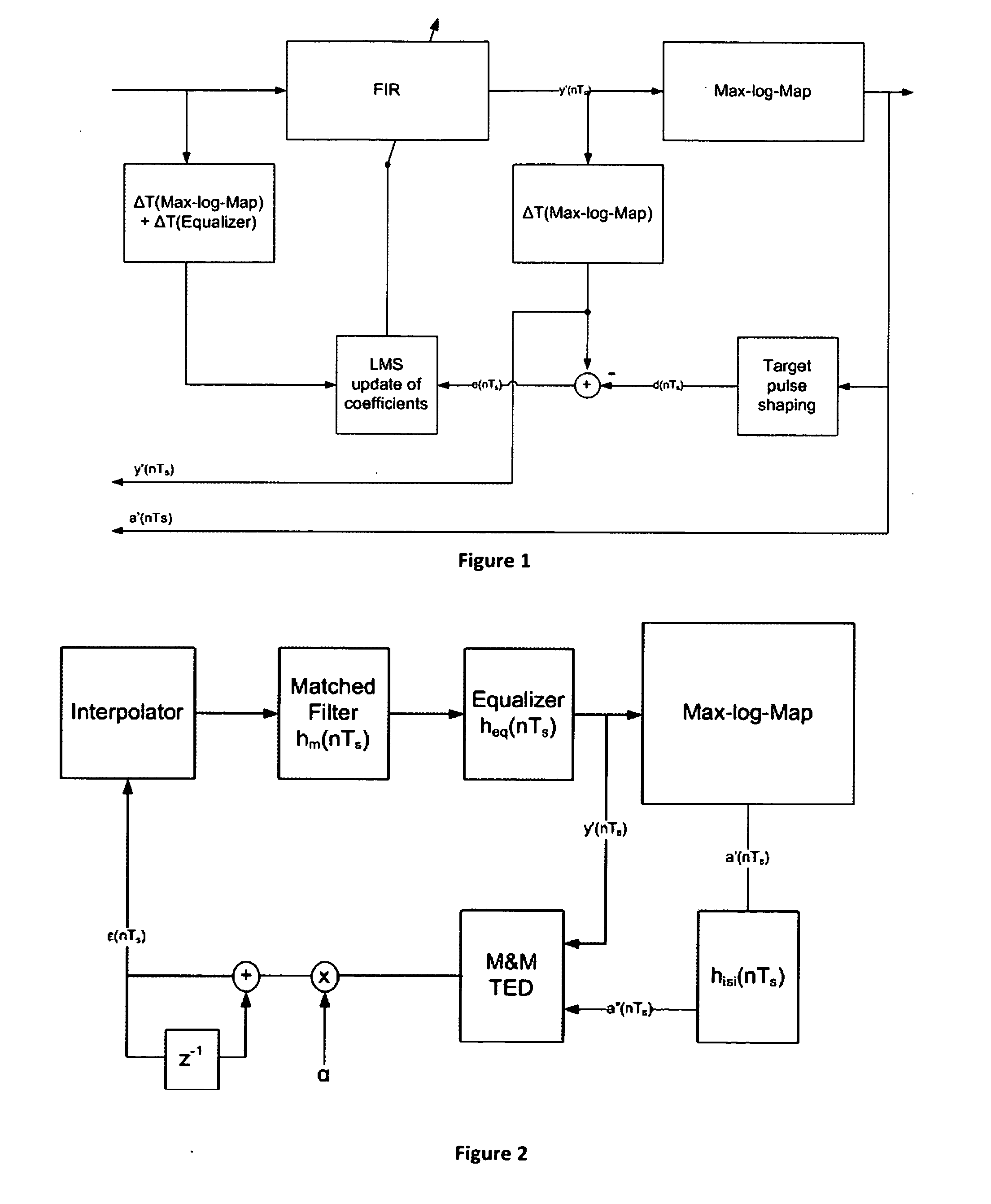

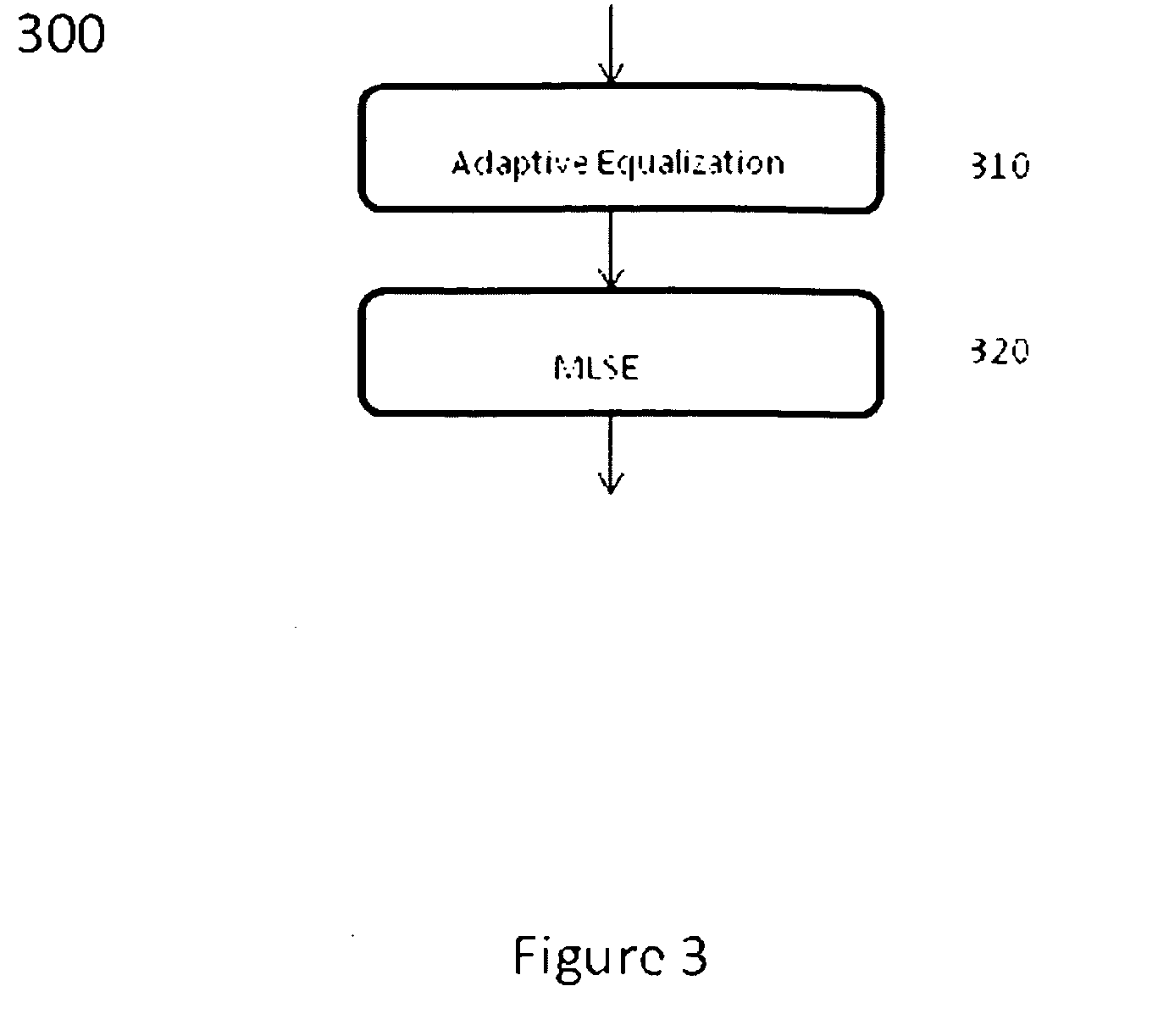

Method and apparatus for iterative timing and carrier recovery

InactiveUS20120039380A1Multiple-port networksSatellite broadcast receivingRecovery methodForward error correction

Method and apparatus for iterative timing recovery for FTN signaling are provided. The iterative timing recovery method and apparatus uses a feedback timing error signal from a forward error correction block with an additional equalizer prior to a maximum a posteriori (MAP) decoder which matches the equalized FTN signal to a truncated inter-symbol interference (ISI) target. A timing error is then generated using a modified M&M timing error detector.

Owner:THOMSON LICENSING SA

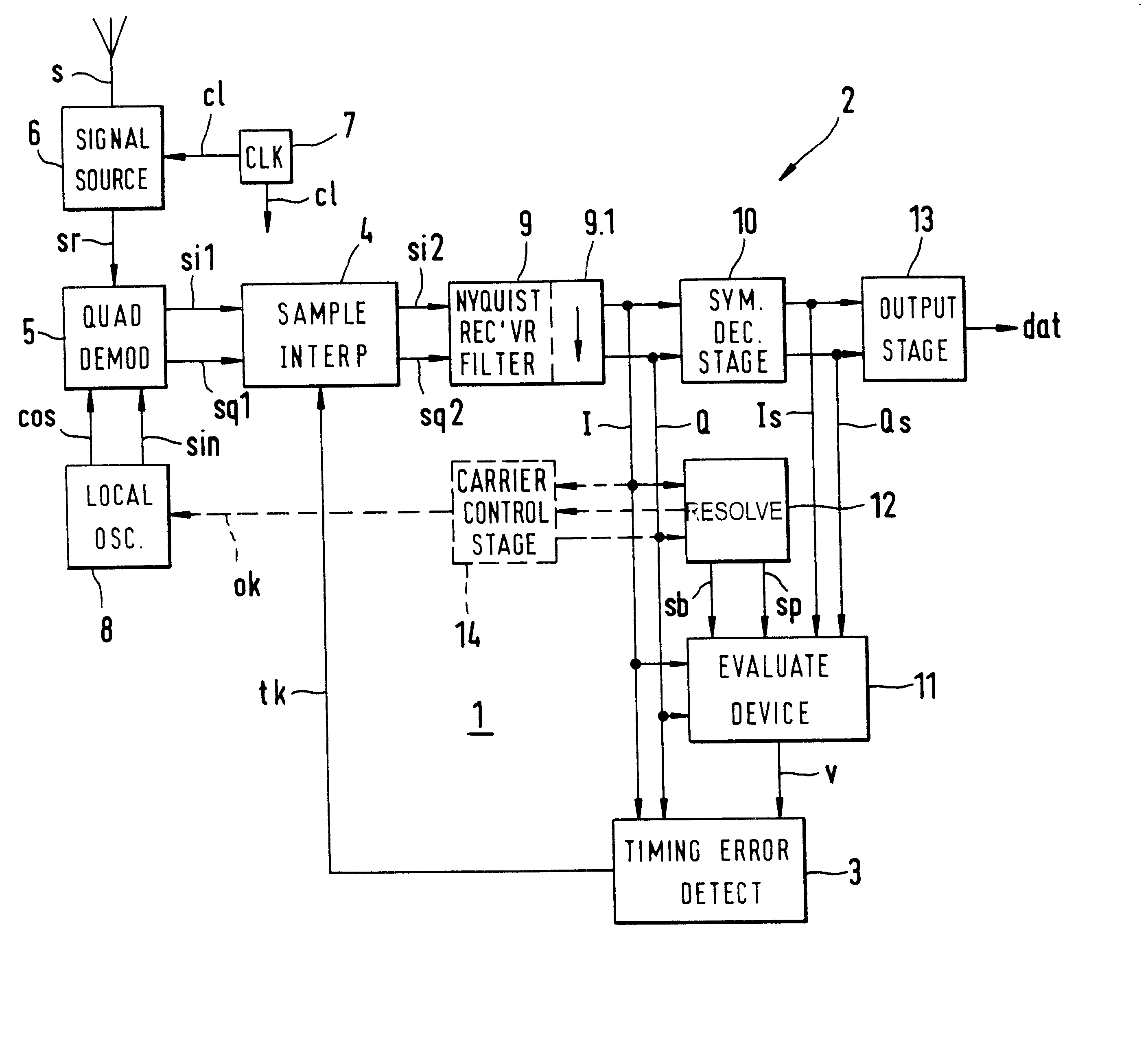

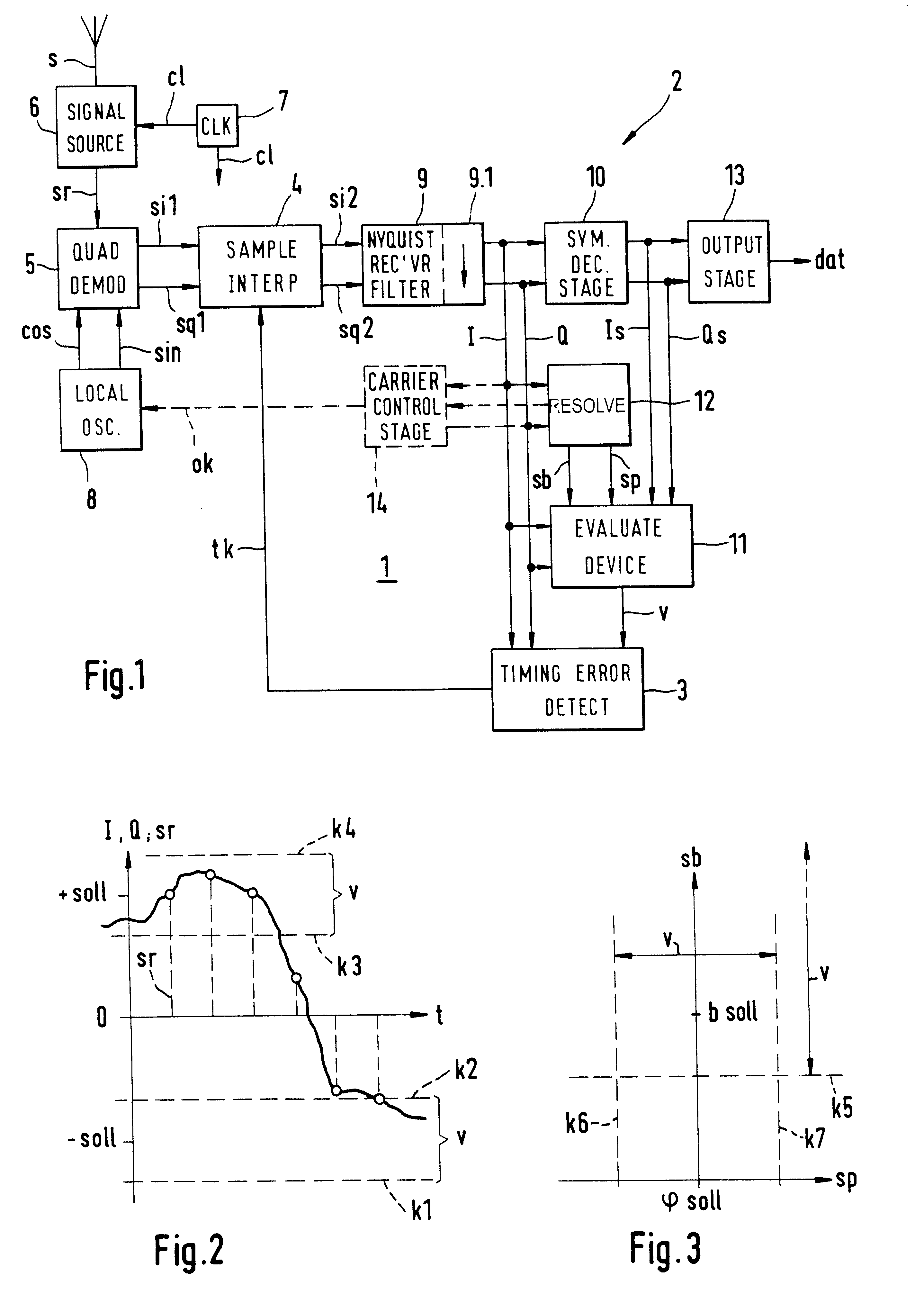

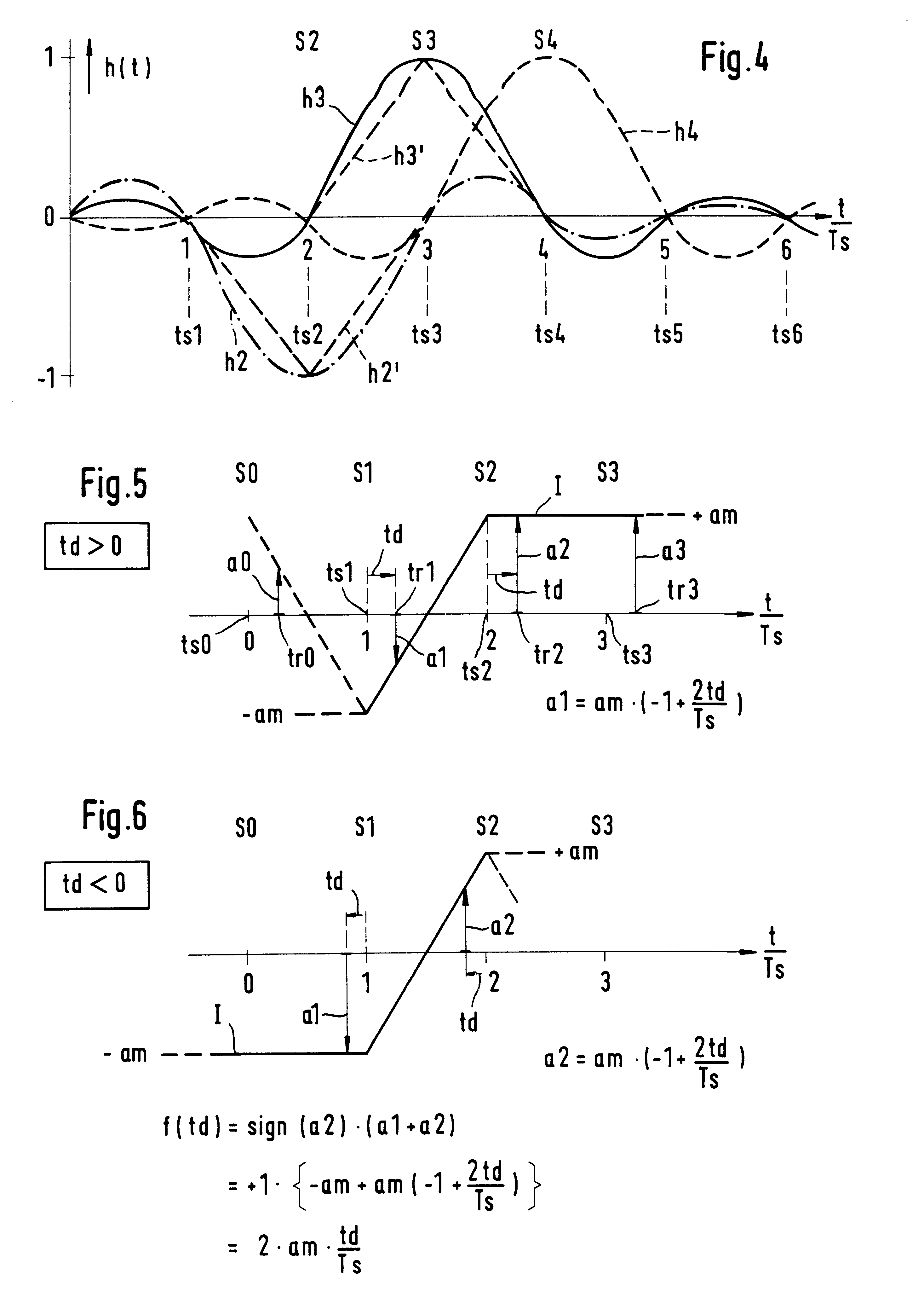

Sampling control loop for a receiver for digitally transmitted signals

InactiveUS6477215B1Frequency-modulated carrier systemsPhase-modulated carrier systemsEngineeringTiming error detector

To optimize the sampling of individual symbols (S0 to S3), a sampling control loop (1) for a circuit (2) for receiving digitally transmitted signals (s) is connected to a timing error detector (3) which determines the respective timing error values (td). To improve the control action of the sampling control loop (1), an evaluating device (11) determines a reliability value (v) from signals (I, Q; Is, Qs; sb, sp; sr) of the receiving circuit (2) and controls the sampling control loop (1) in accordance with the reliability value (v).

Owner:ENTROPIC COMM INC

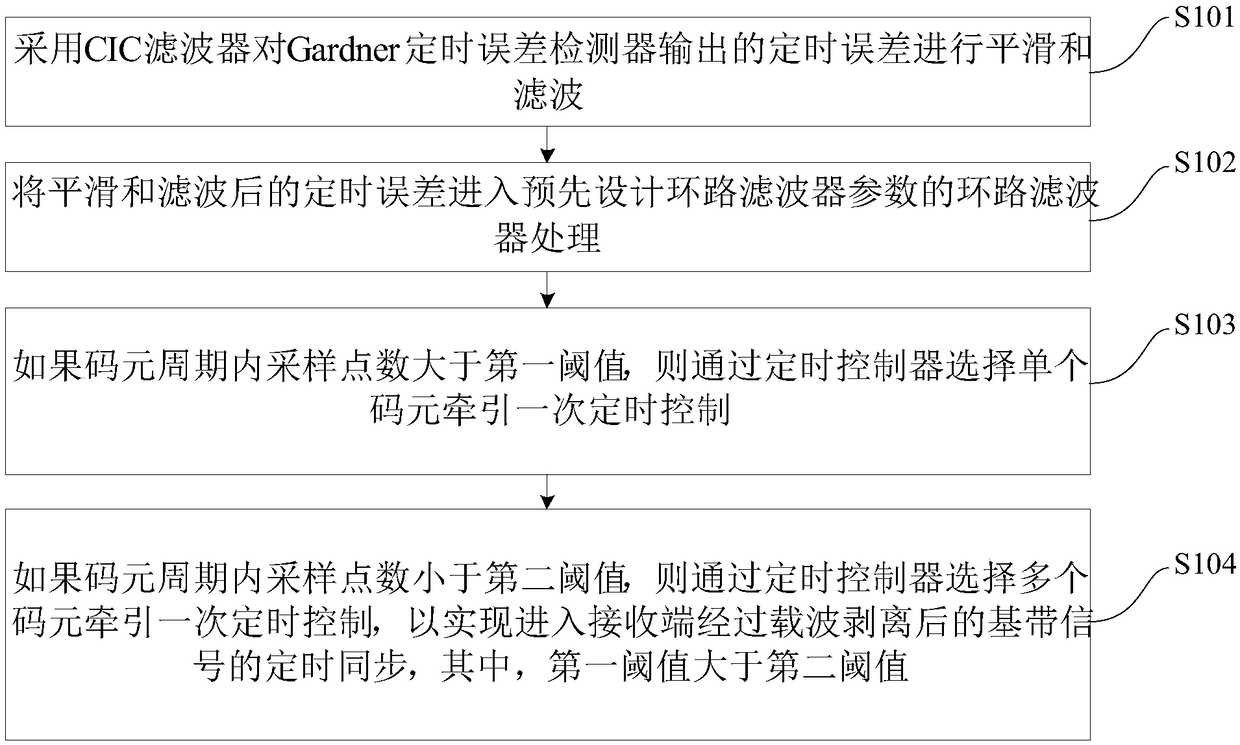

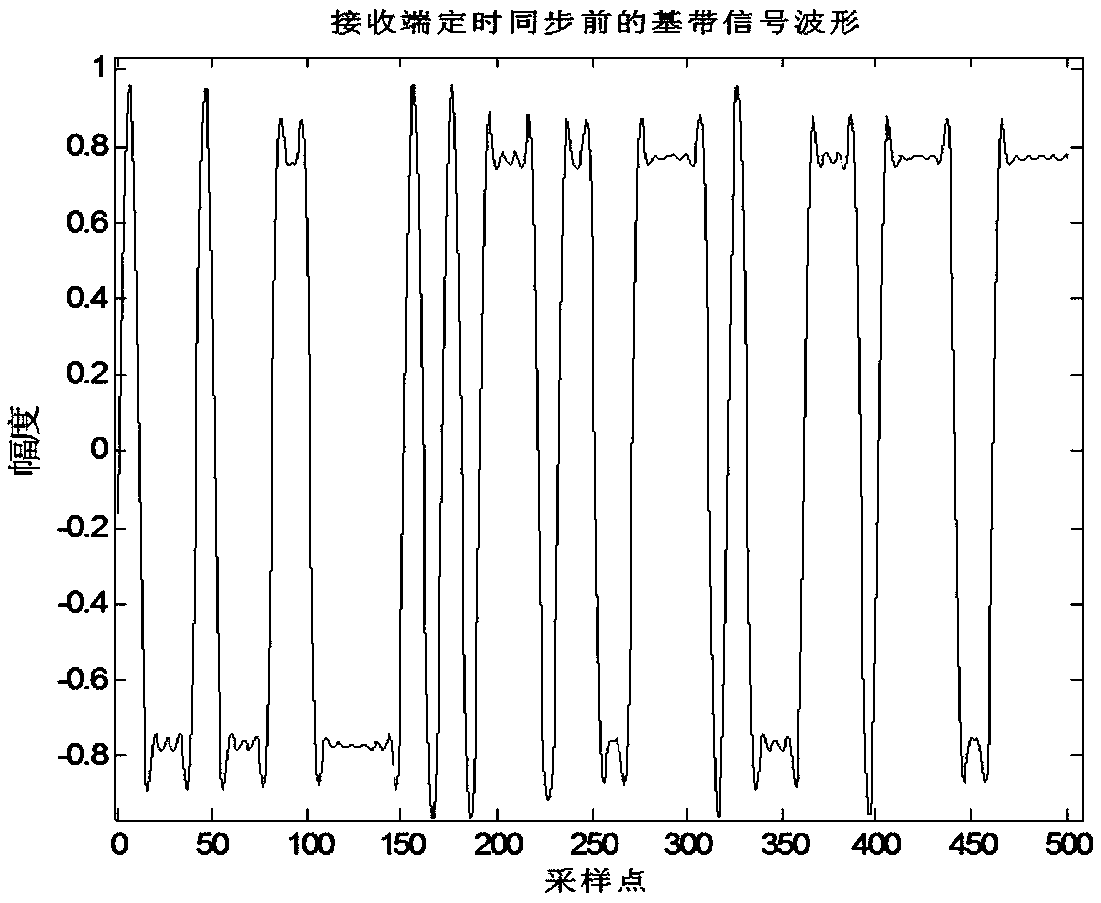

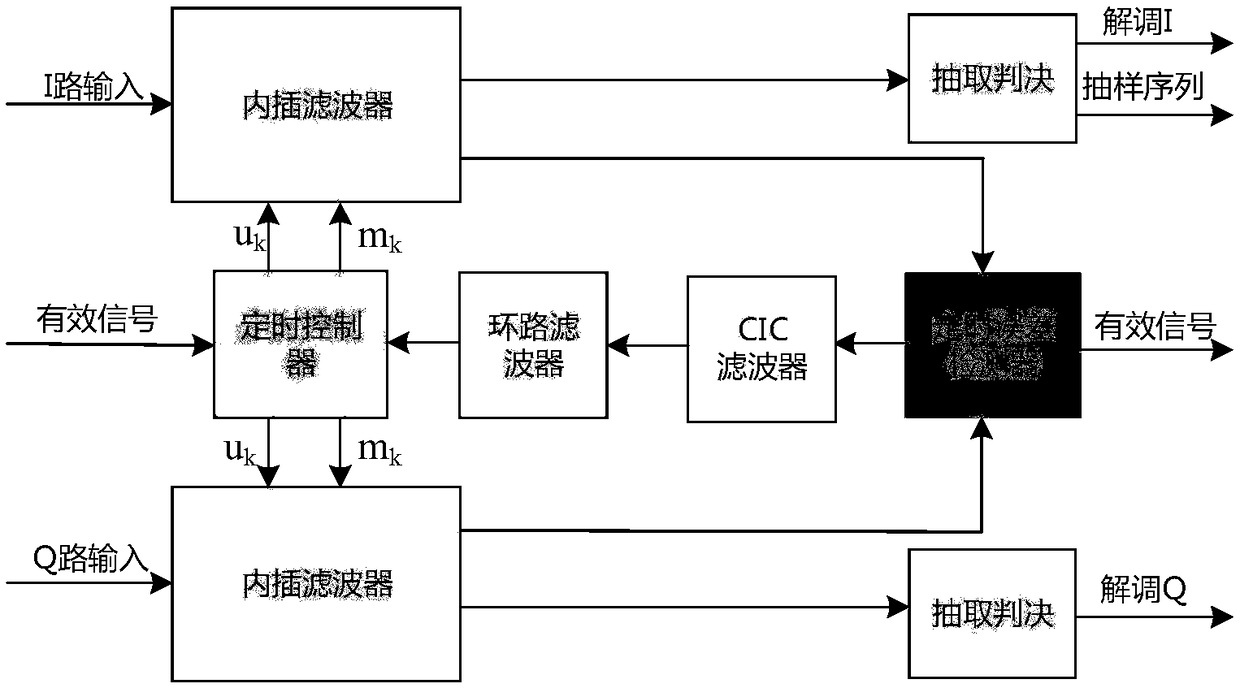

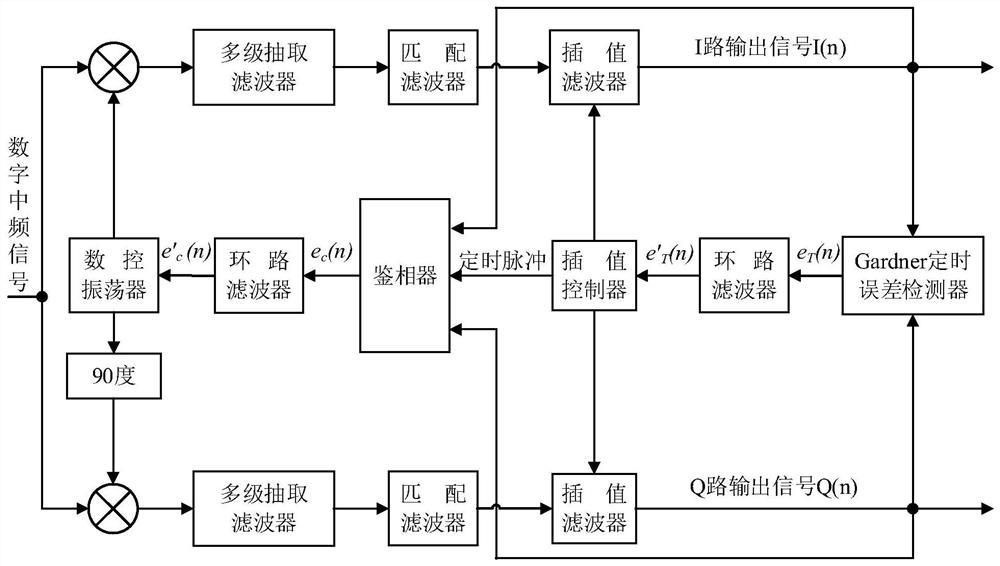

Improved all-digital timing synchronization method and device based on Gardner

ActiveCN108989260AImprove reliabilityImprove applicabilityPhase-modulated carrier systemsMulti-frequency code systemsLoop filterCarrier signal

Owner:TSINGHUA UNIV

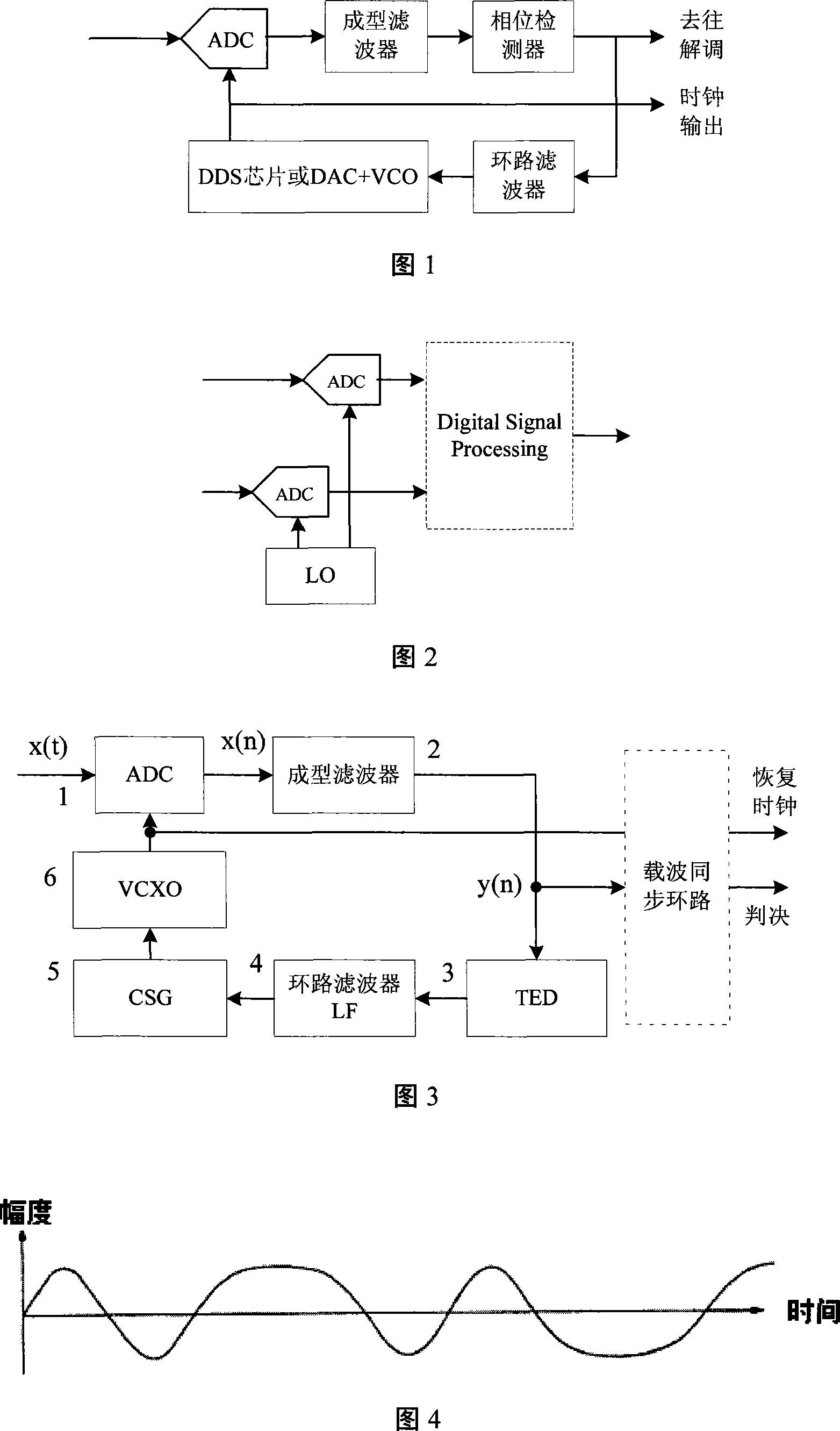

High dynamic scope quick clock recovery system based on voltage crystal oscillator

InactiveCN101170398AImprove capture speedLarge capture rangePulse automatic controlSynchronising arrangementControl signalCarrier signal

A fast clock recovery system with a large dynamic range based on a voltage-controlled crystal oscillator, the clock recovery system is placed before a carrier synchronization loop, and includes: an analog-to-digital conversion ADC, a shaping filter, a timing error detector TED, Loop filter LF, control signal generator CSG, voltage controlled crystal oscillator VCXO, among which TED calculates the phase detection error signal P value according to the output data of the shaping filter, and then performs two consecutive phase detection error signal P values. Differential processing, multiply the multiplication factor and the differential processing result, and send the multiplication result to the loop filter LF until the sampling frequency offset is captured, and finally send the phase detection error signal P value to the loop filter LF to achieve Sampling frequency offset tracking. After continuous correction of the loop, the oscillation frequency of the VCXO is finally locked with the sampling clock of the transmitter to realize clock recovery. The invention has the advantages of wide dynamic range and fast clock recovery.

Owner:BEIJING SATELLITE INFORMATION ENG RES INST

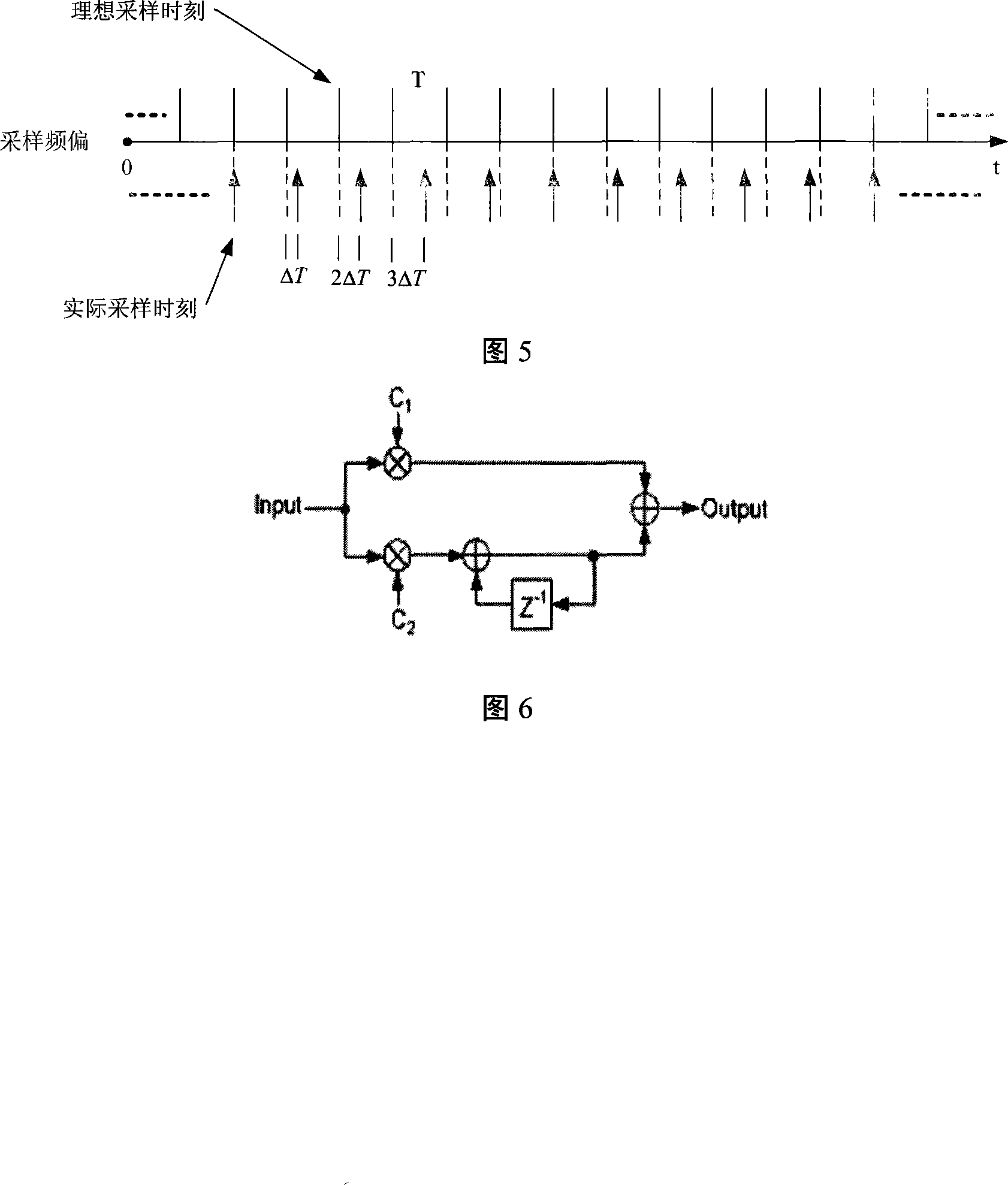

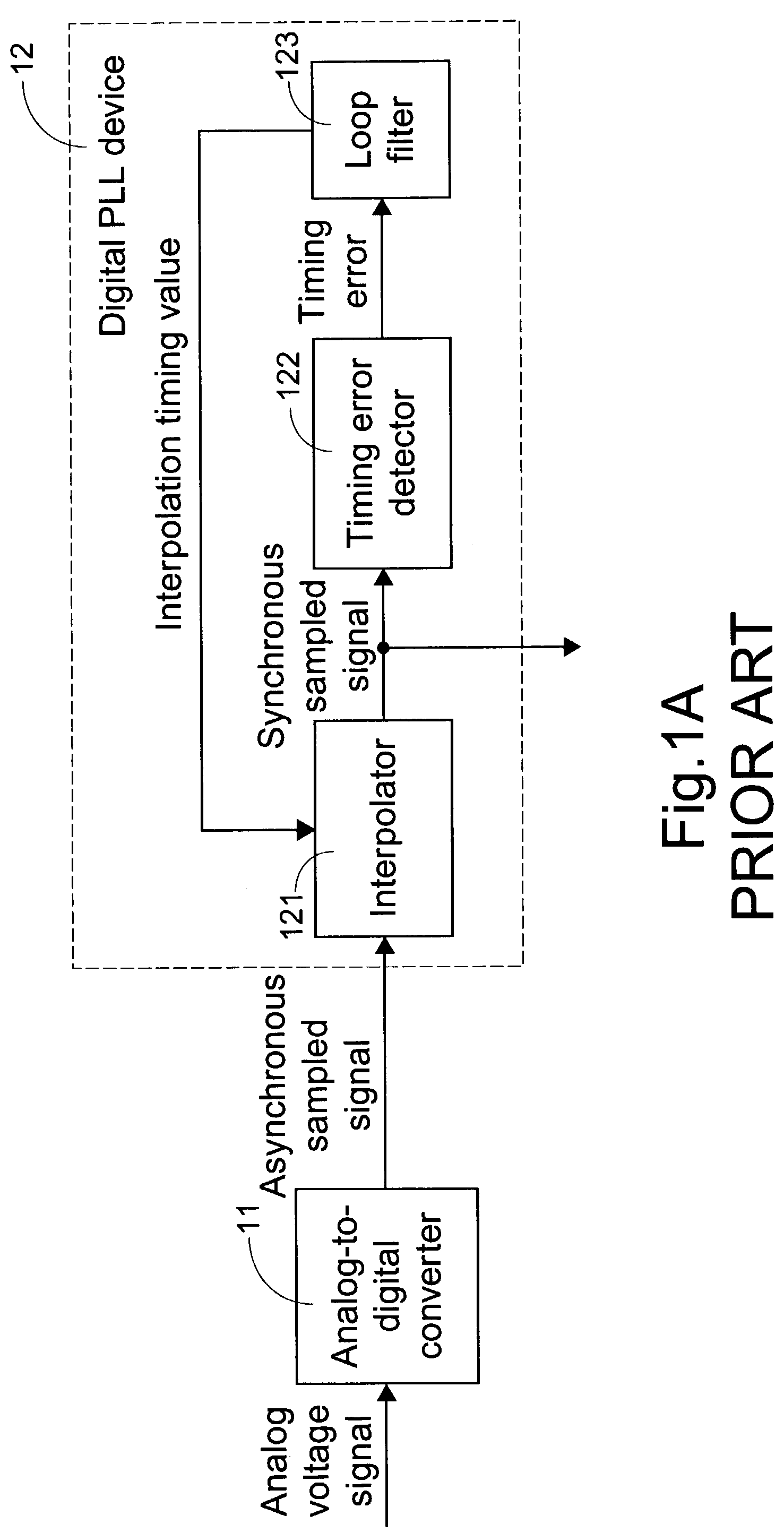

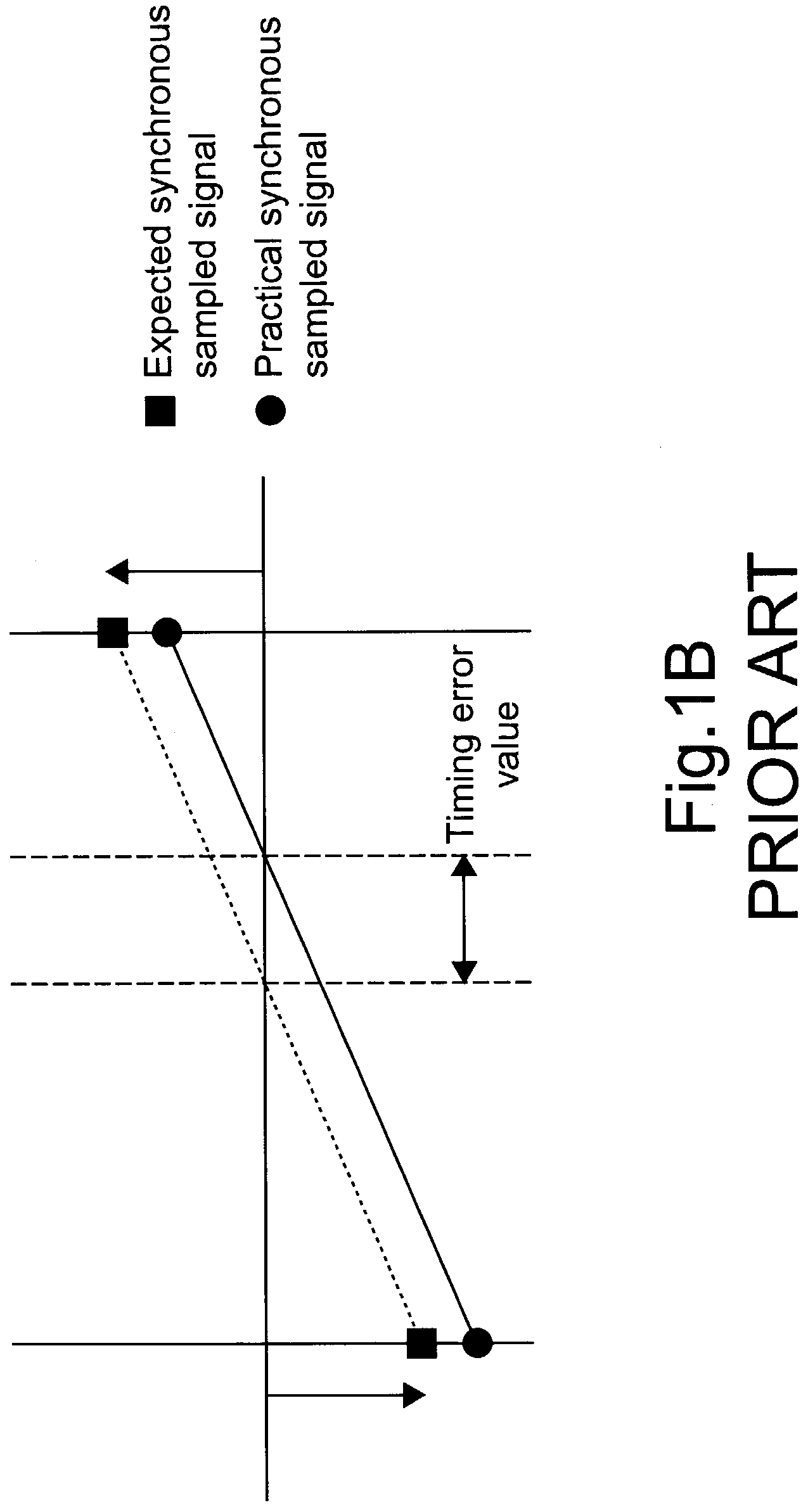

Digital phase-locked loop device for synchronizing signal and method for generating stable synchronous signal

InactiveUS7245687B2Shorten convergence timePulse automatic controlAngle demodulation by phase difference detectionLoop filterTiming error detector

A phase-locked loop (PLL) device is disclosed. The PLL device includes an interpolator receiving and processing an input signal by an interpolation operation in response to an interpolation timing value to obtain an output signal, a timing error detector in communication with the interpolator for detecting a timing error value of the output signal, a loop filter in communication with the timing error detector for outputting the interpolation timing value to the interpolator in response to the timing error value, and a lock controller in communication with the loop filter for adjusting the interpolation timing value according to a timing quality of the output signal, and providing the adjusted interpolation timing value for the interpolator. A signal generation method for use in the data pick-up device with the aid of the digital phase-locked loop (PLL) device is also disclosed.

Owner:TIAN HLDG

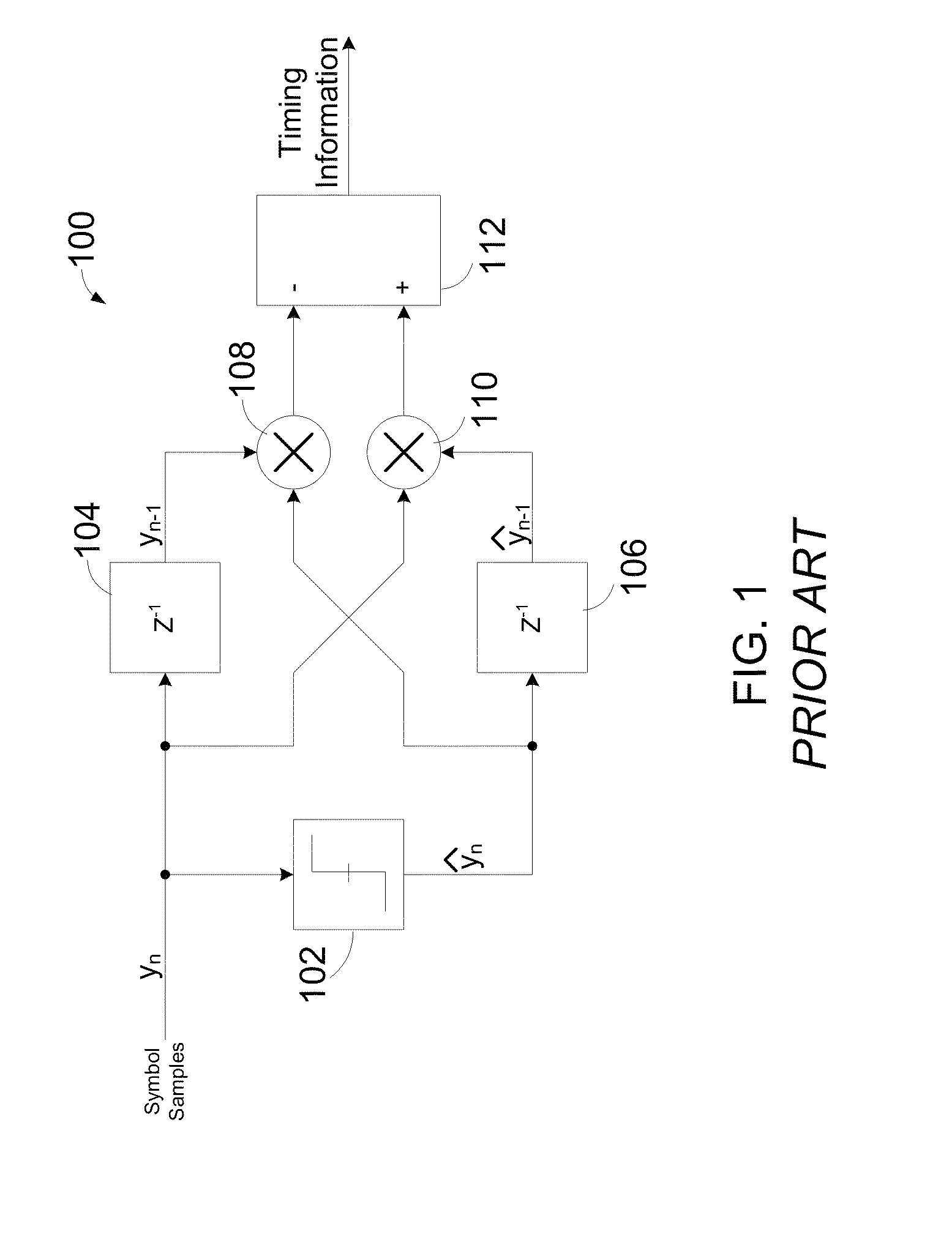

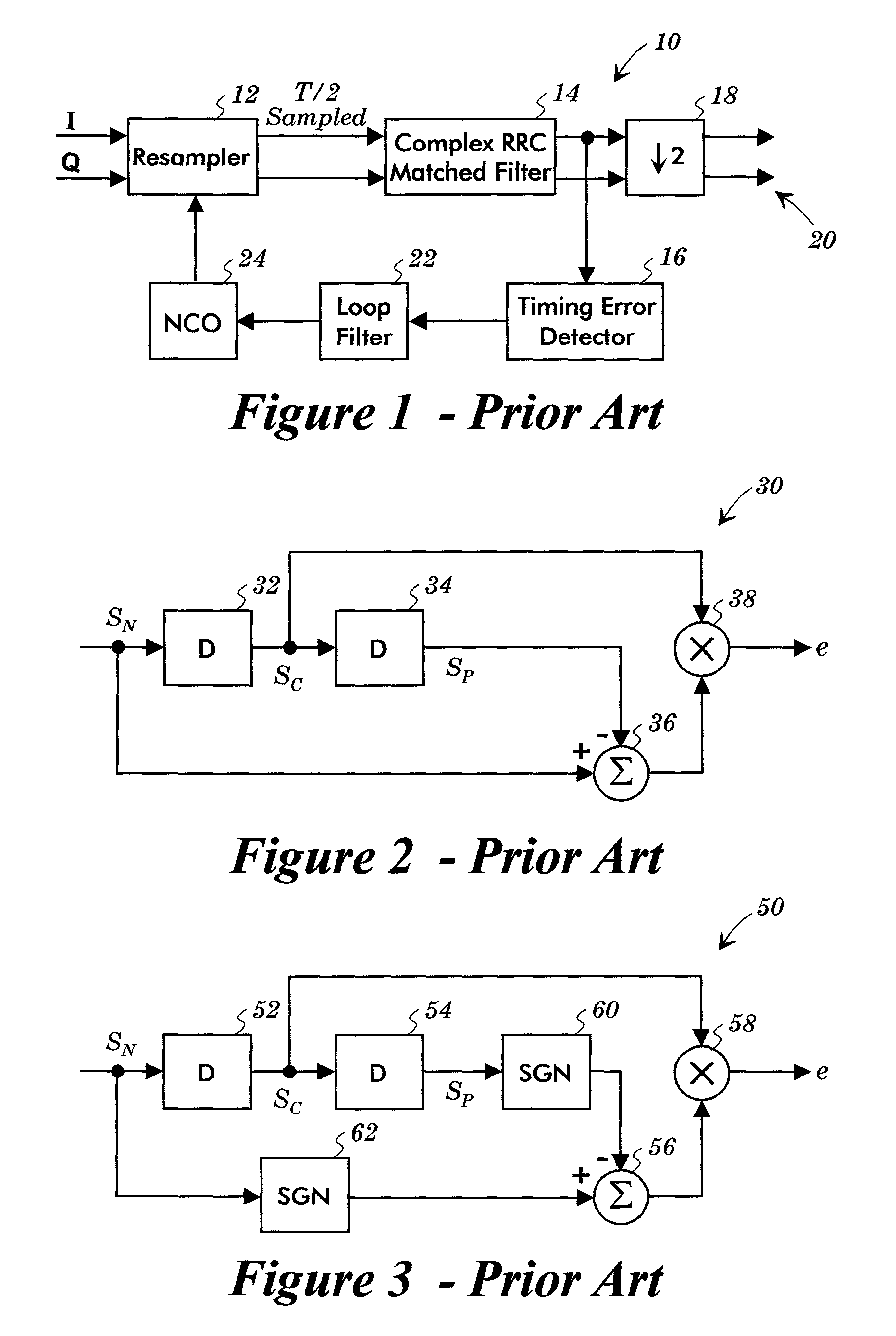

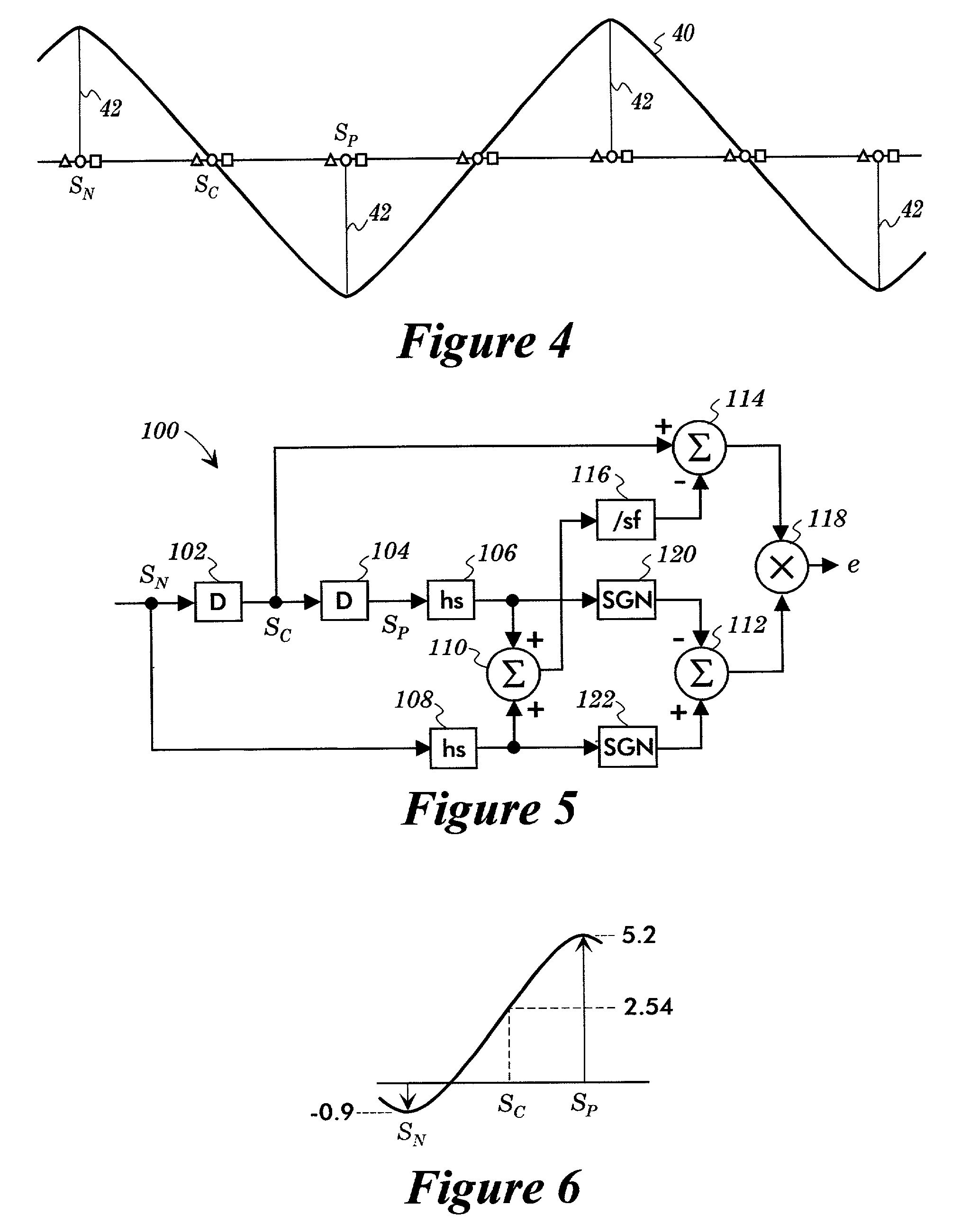

Timing error detector for digital signal receiver

A received signal having a series of T-spaced symbols having more than two levels is sampled at a rate that produces successive samples SP, SC, and SN substantially equally spaced by T / 2. An output representing the difference between the sign of the sample SN and the sign of the sample SP is generated, and the value of the sample SC is offset so that the value of the sample SC approaches zero. The offset value of the sample SC and the generated output are multiplied together in order to provide a timing error signal. The sampling of the received signal is controlled in accordance with the timing error signal.

Owner:ZENITH RADIO CORP

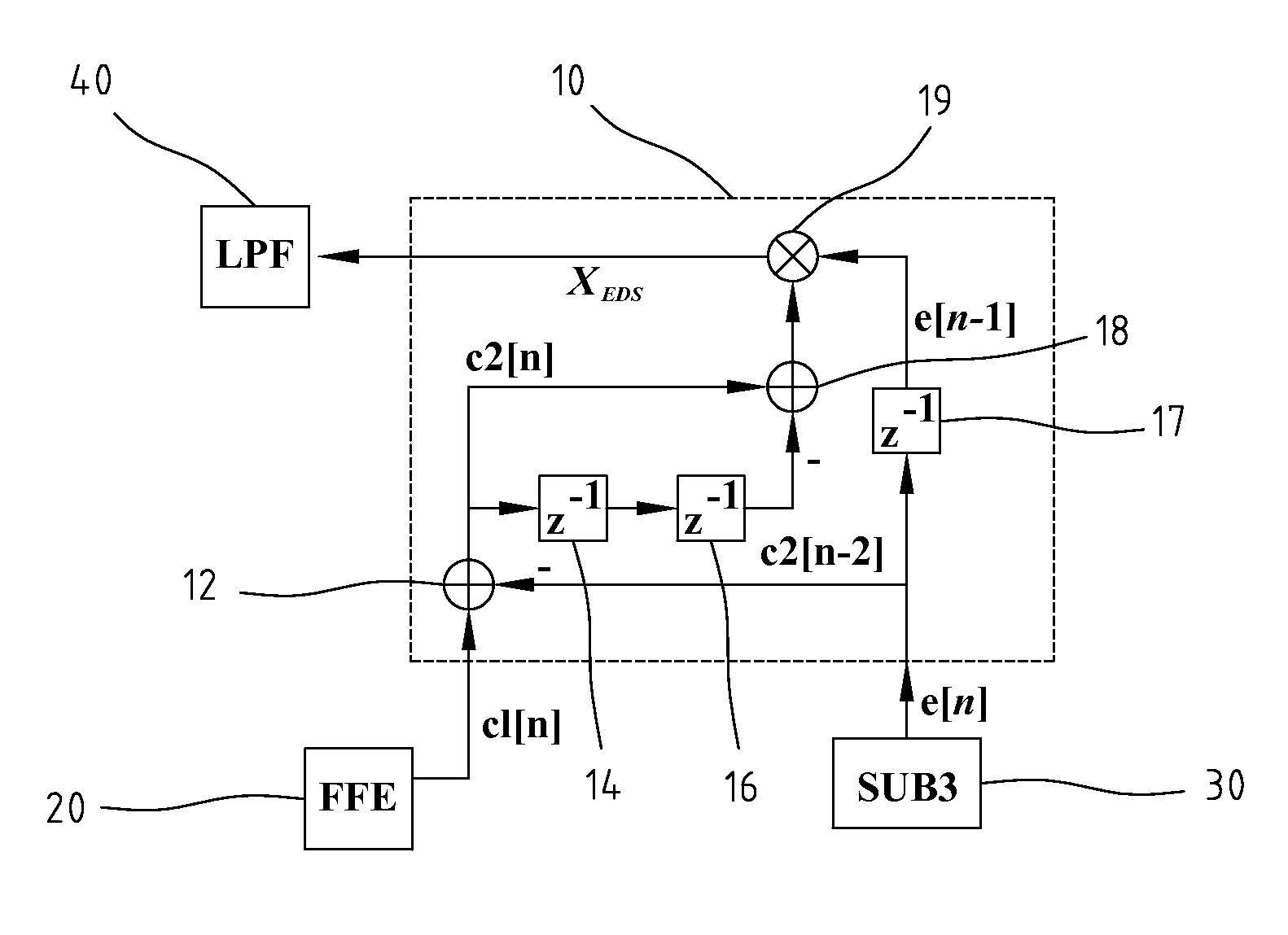

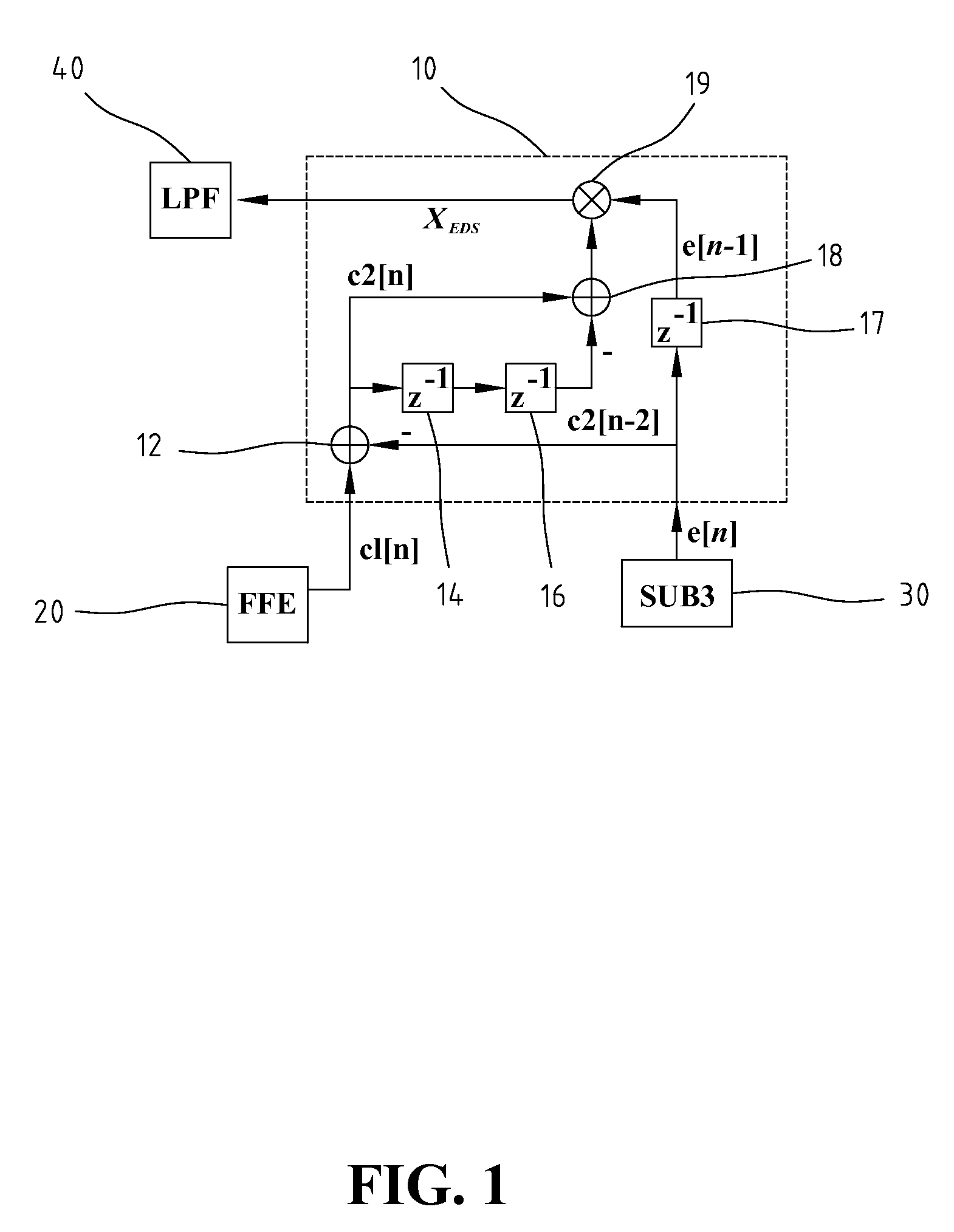

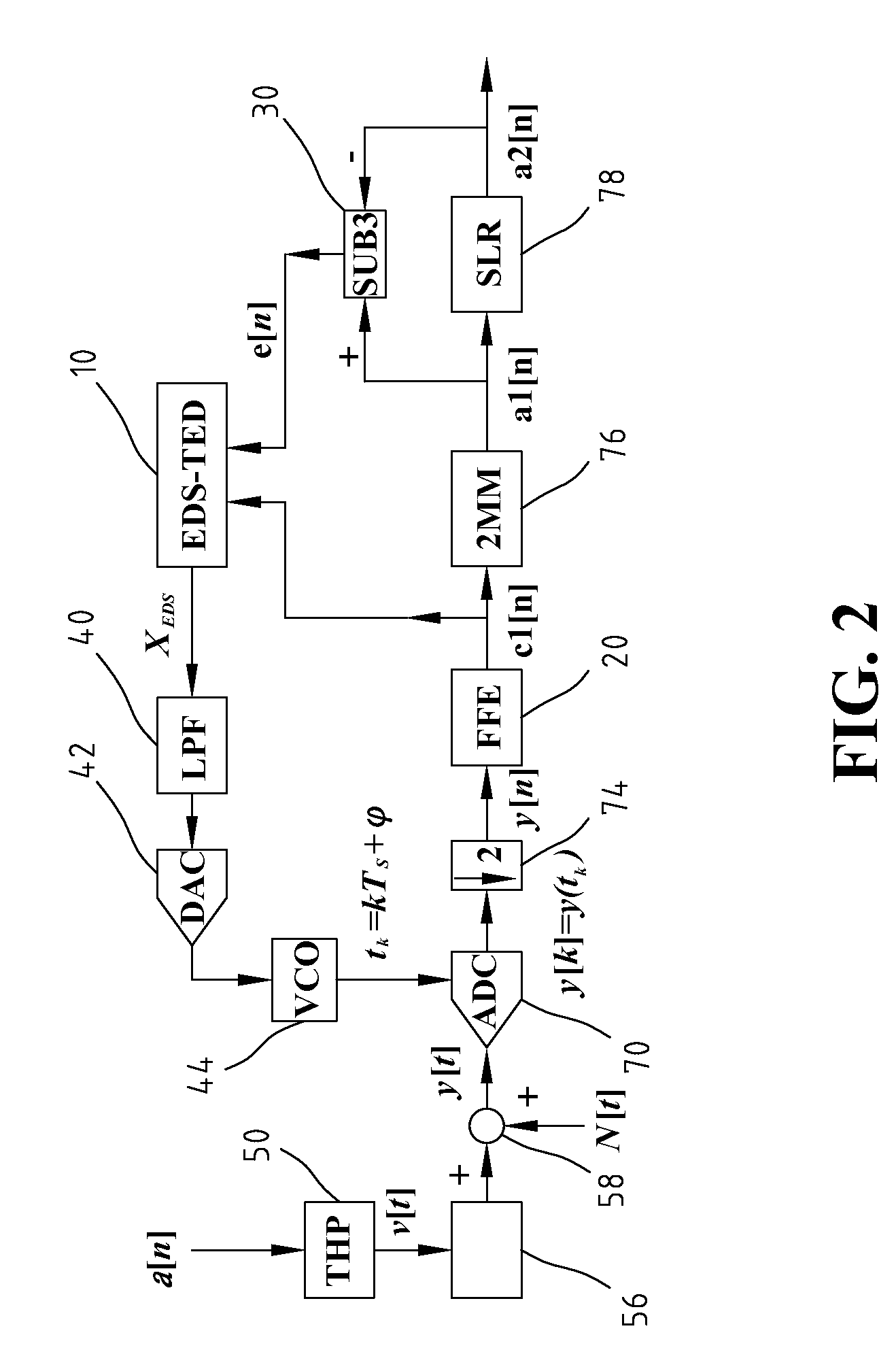

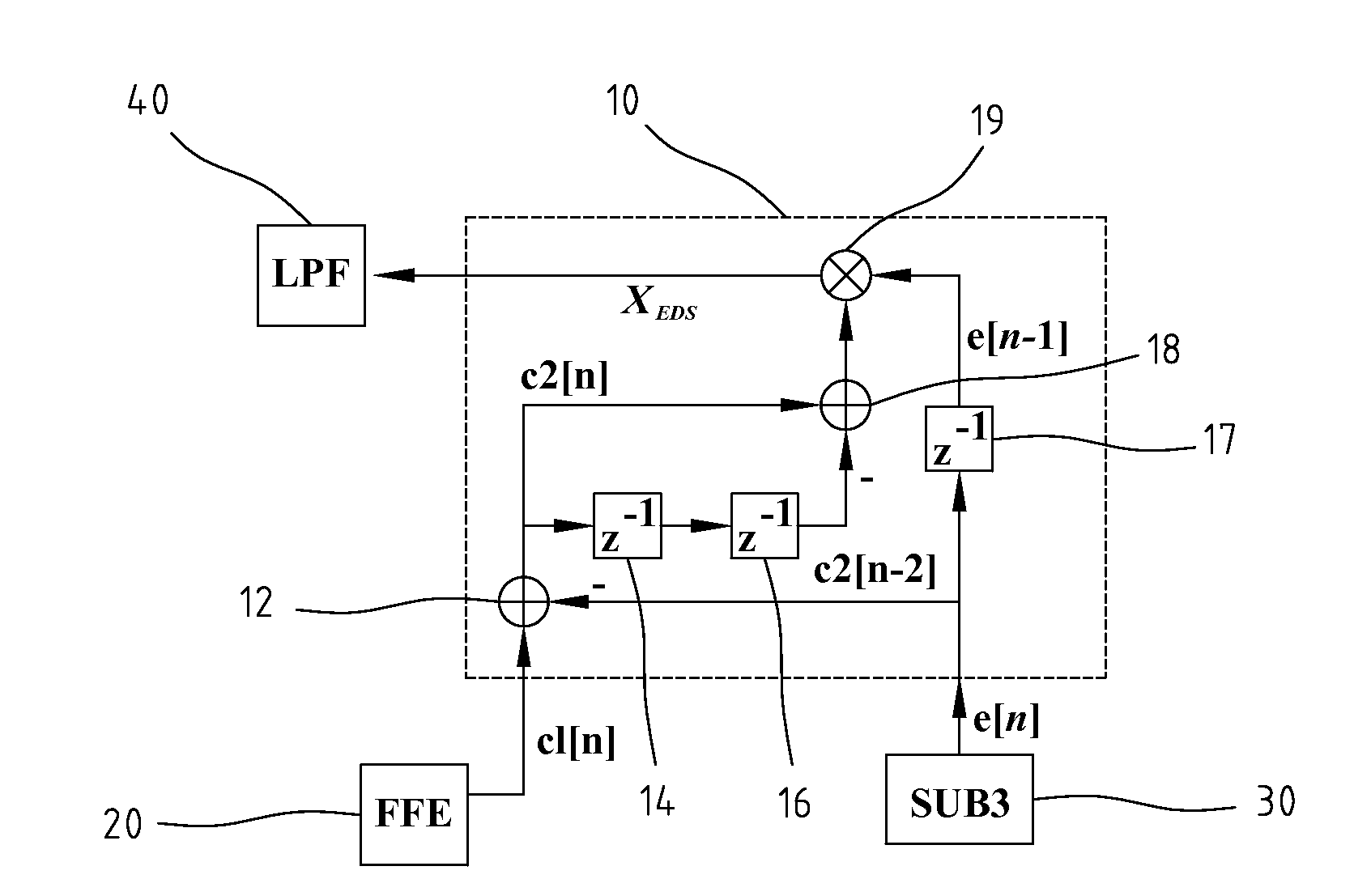

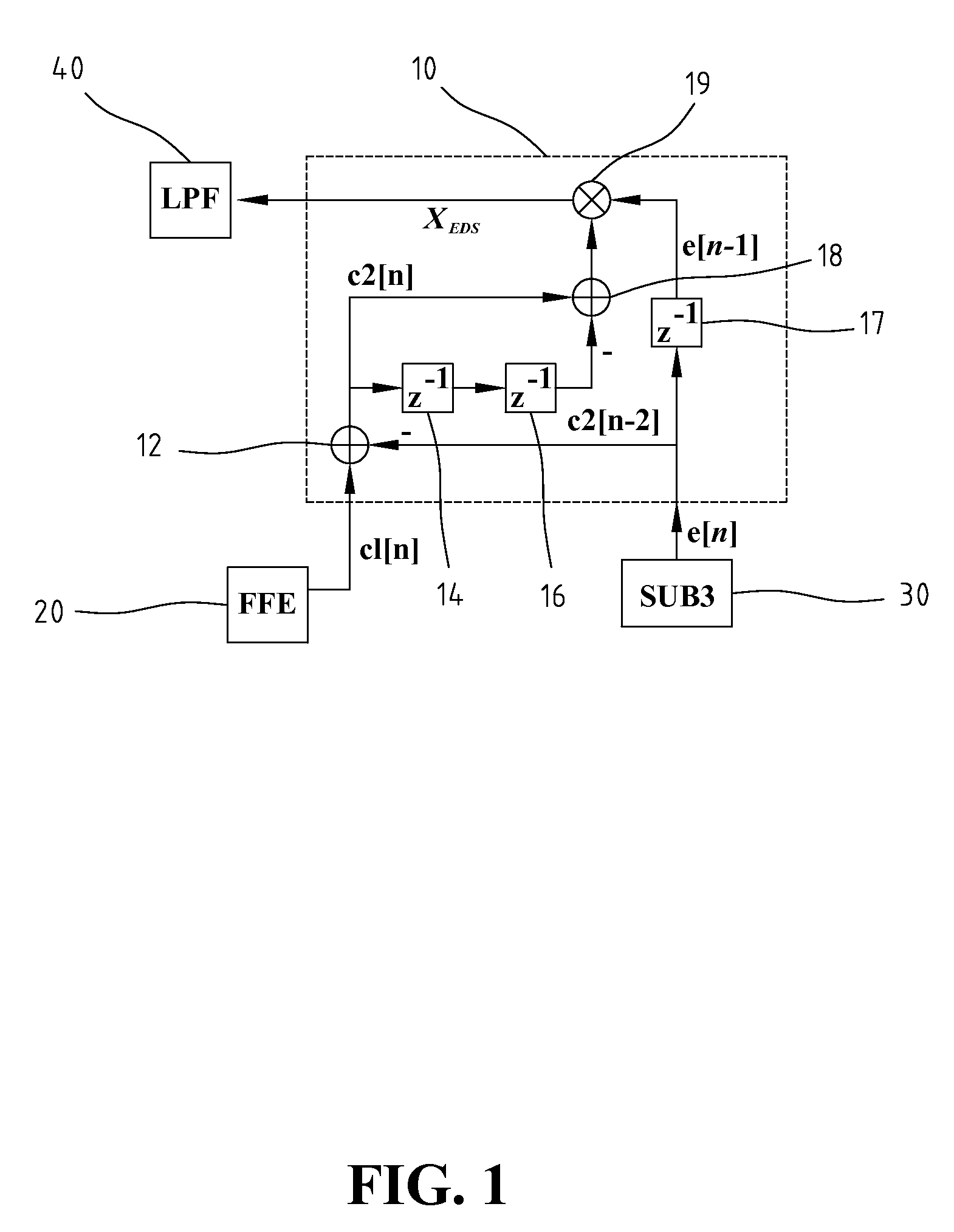

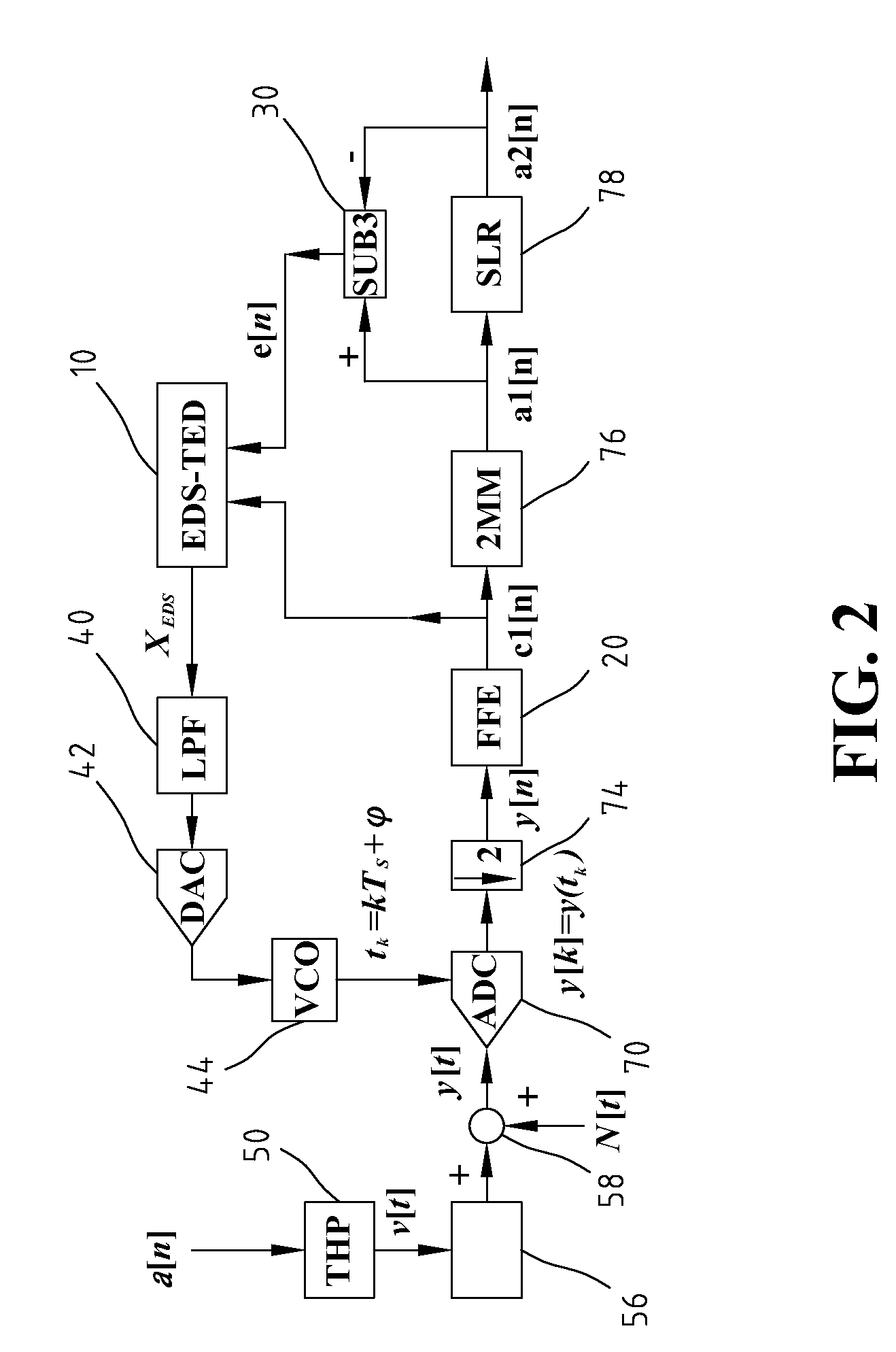

Timing error detector and method thereof

ActiveUS8218612B2Quality improvementReducing the peak-to-peak jitter of the recovered clock pulseError preventionModulated-carrier systemsMean squarePeak value

An effective data sequence based timing error detector (EDS-TED) for baseband transmission system using Tomlinson-Harashima Precoder is disclosed. The EDS-TED extracts timing error information embedded in the received signal to build up autocorrelation between the ESD signals and minimize the mean square error between the received and desired EDS so as to improve the performance of the TED in terms of Peak-to-Peak Jitter and TED gain. Thus the quality of the received signal increases and the error rate decreases.

Owner:NAT TAIWAN UNIV

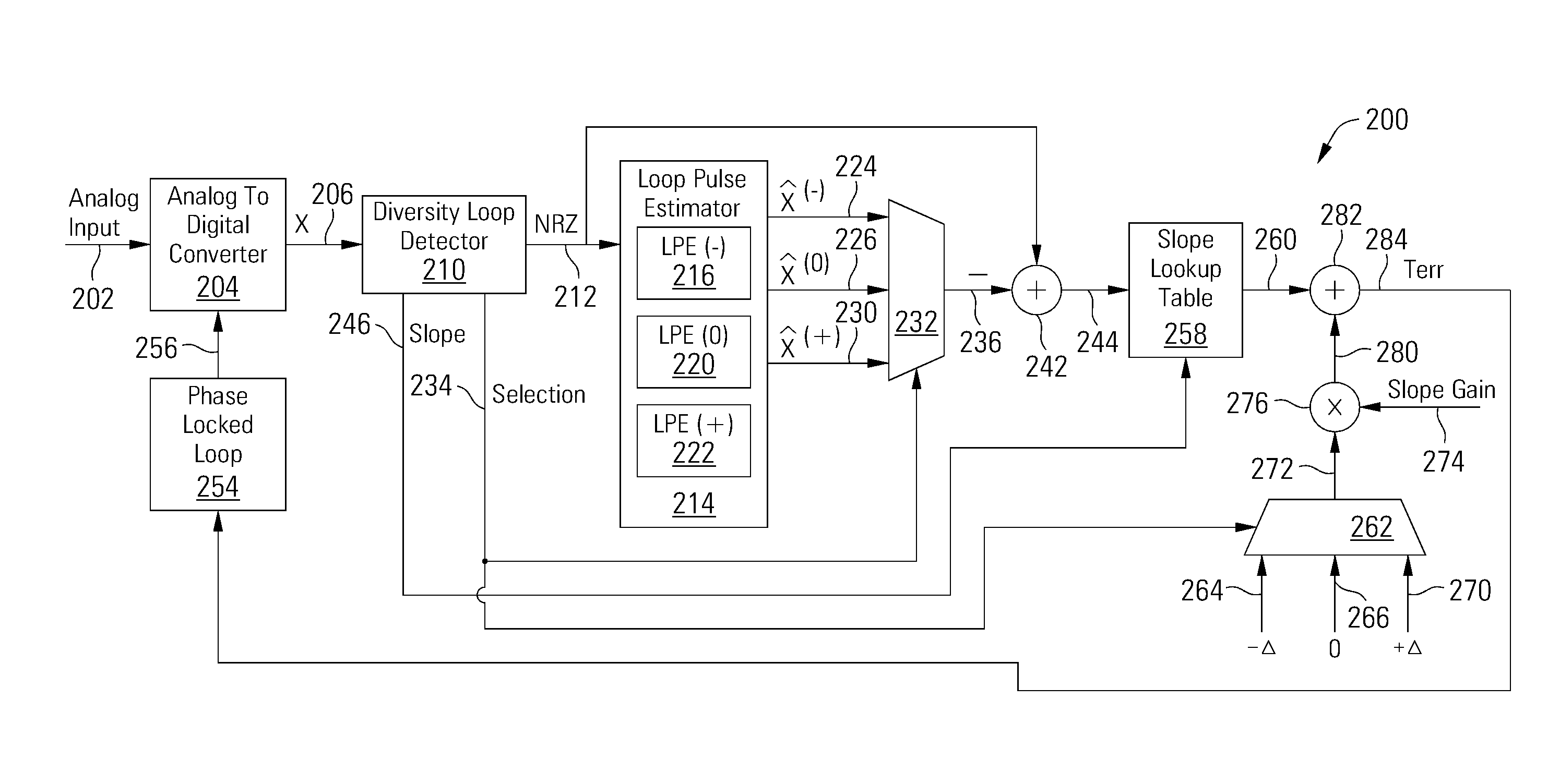

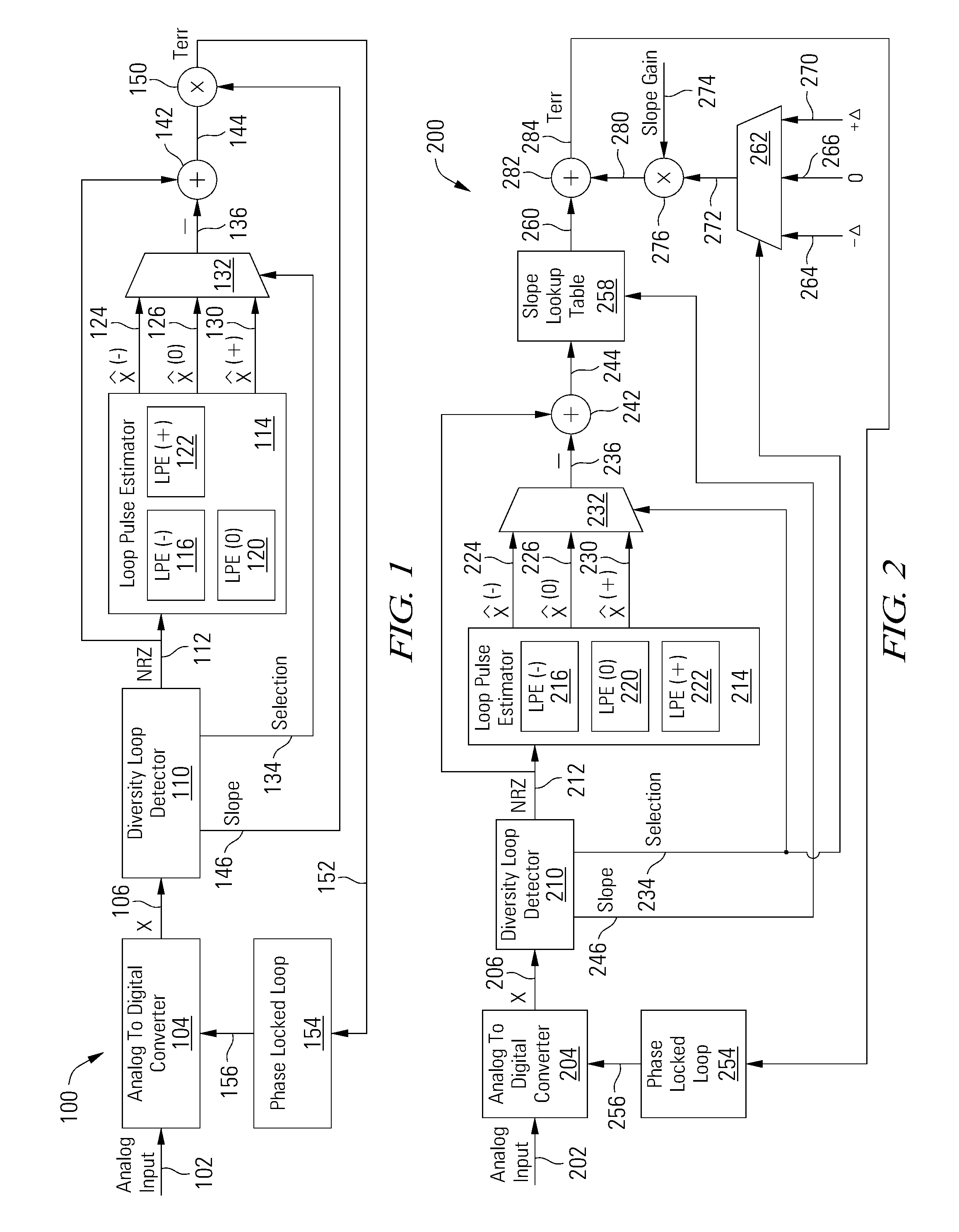

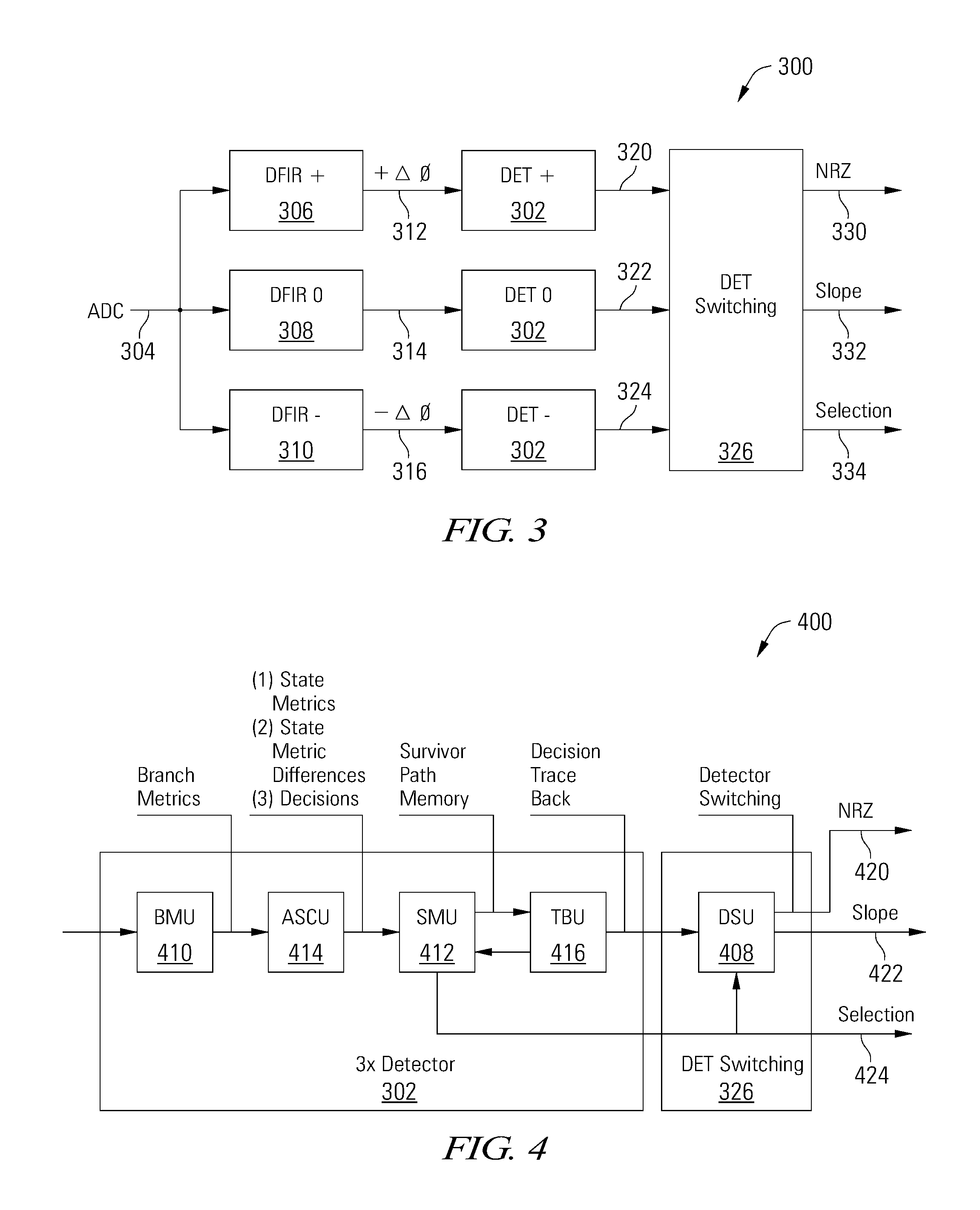

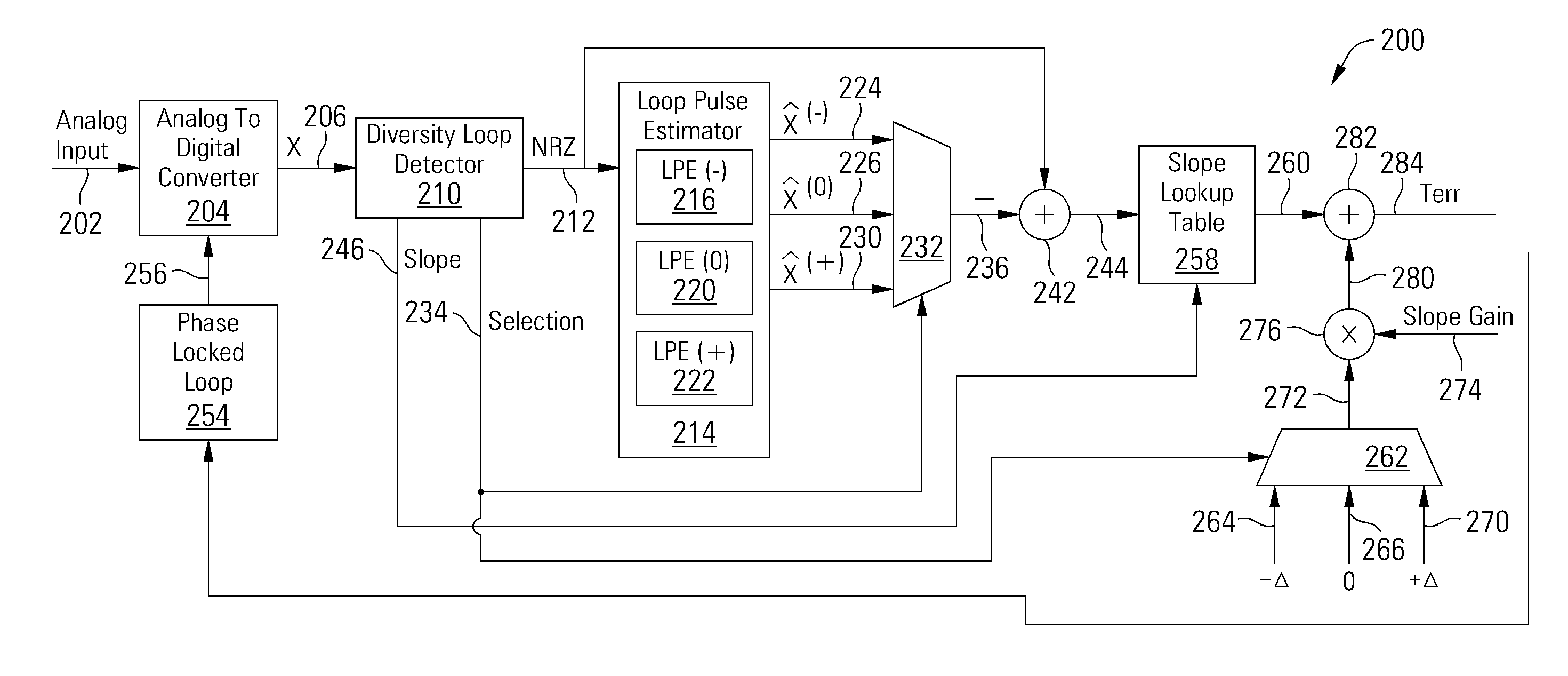

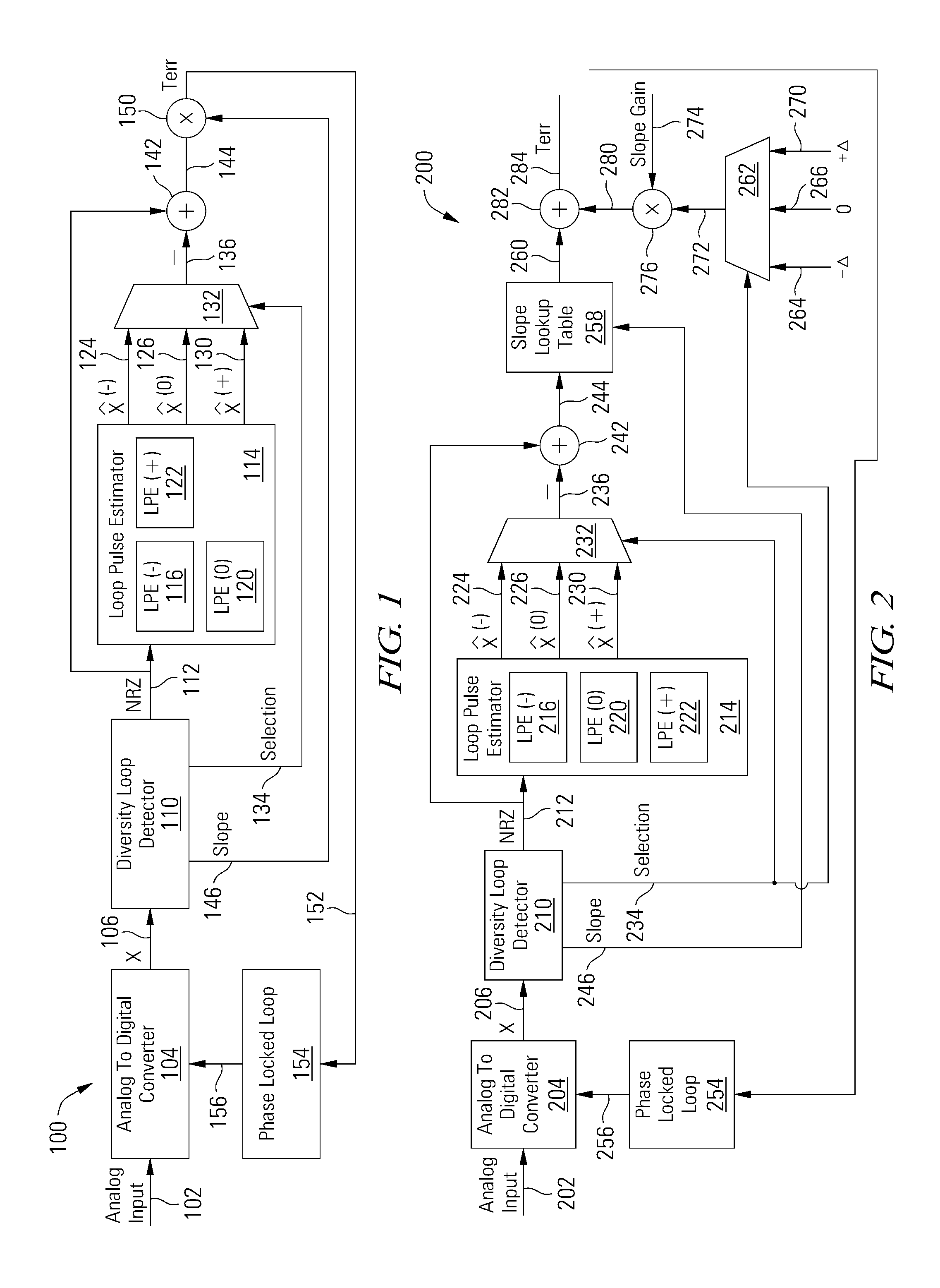

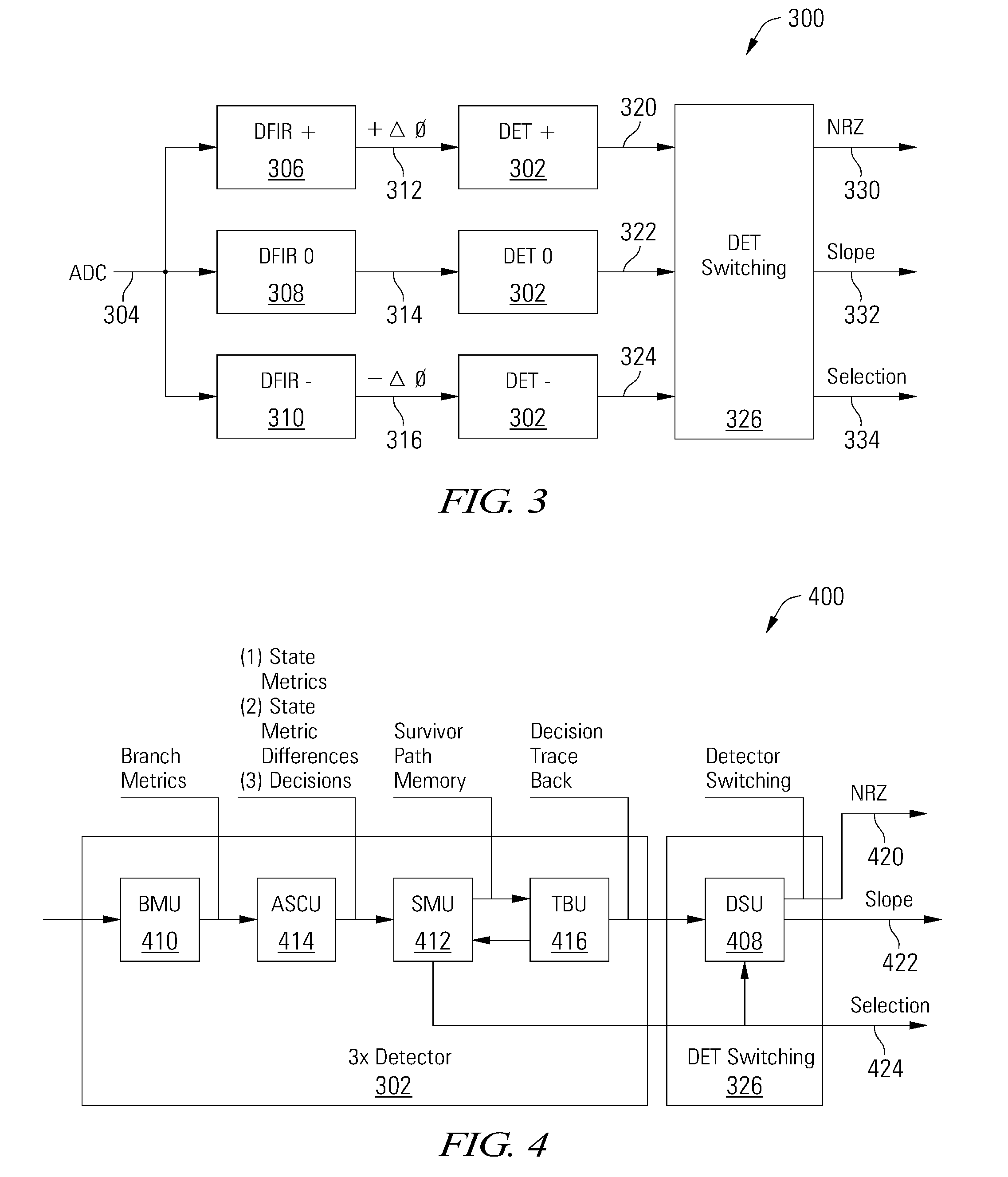

Timing error detector with diversity loop detector decision feedback

ActiveUS9275655B2Modification of read/write signalsRecord information storageDiversity schemeTiming error detector

Aspects of the disclosure pertain to an apparatus for detecting timing errors including an analog to digital converter circuit, a diversity loop detector and a timing error calculation circuit. The analog to digital converter circuit is operable to convert an input signal into a series of digital samples. The diversity loop detector is operable to apply a data detection algorithm to a plurality of signals derived from the series of digital samples at different phase offsets, to select one of the phase offsets, and to yield a detected output with the selected phase offset. The timing error calculation circuit is operable to calculate a timing error of the analog to digital converter circuit based at least in part on the selected phase offset.

Owner:AVAGO TECH INT SALES PTE LTD

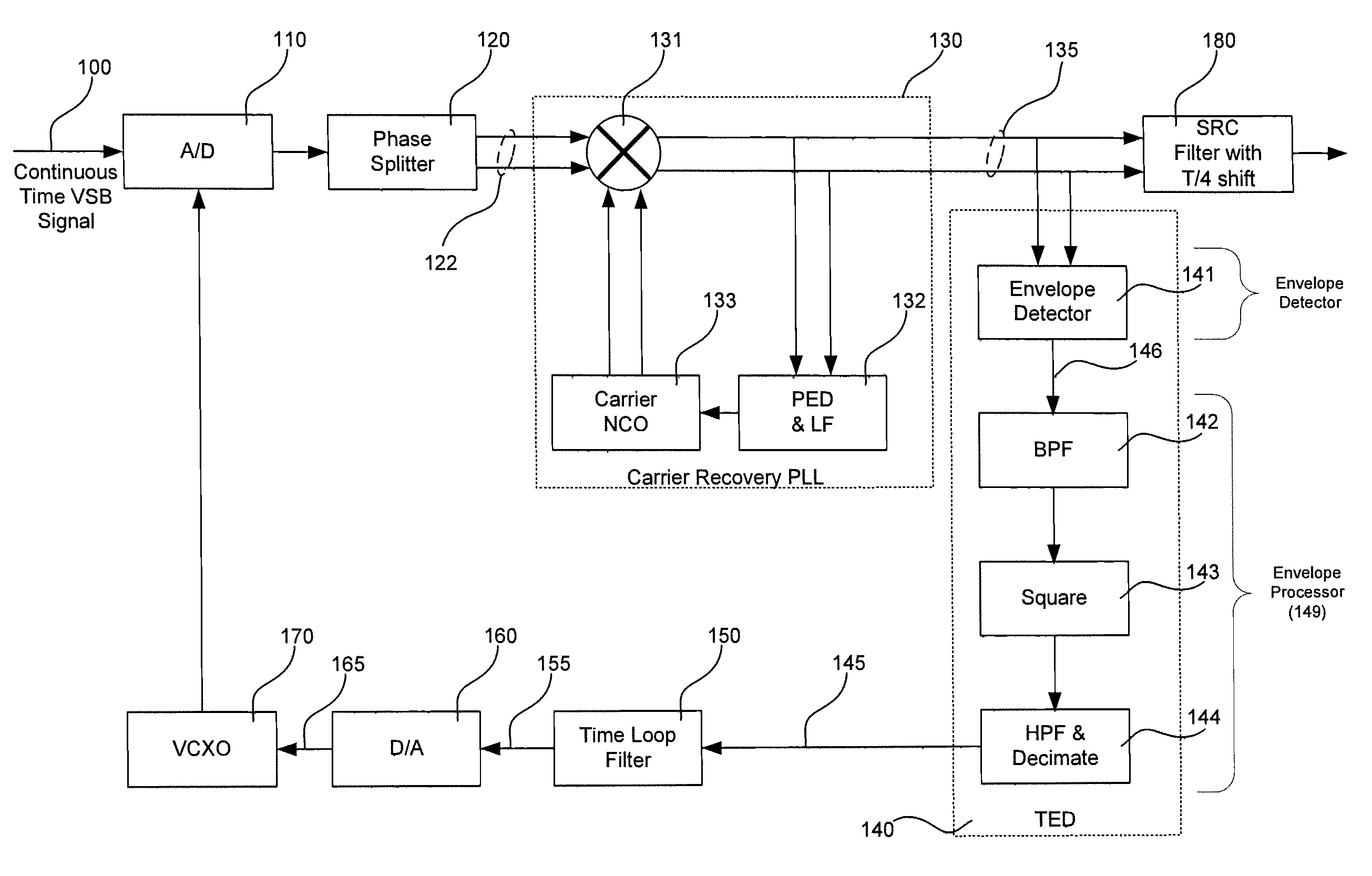

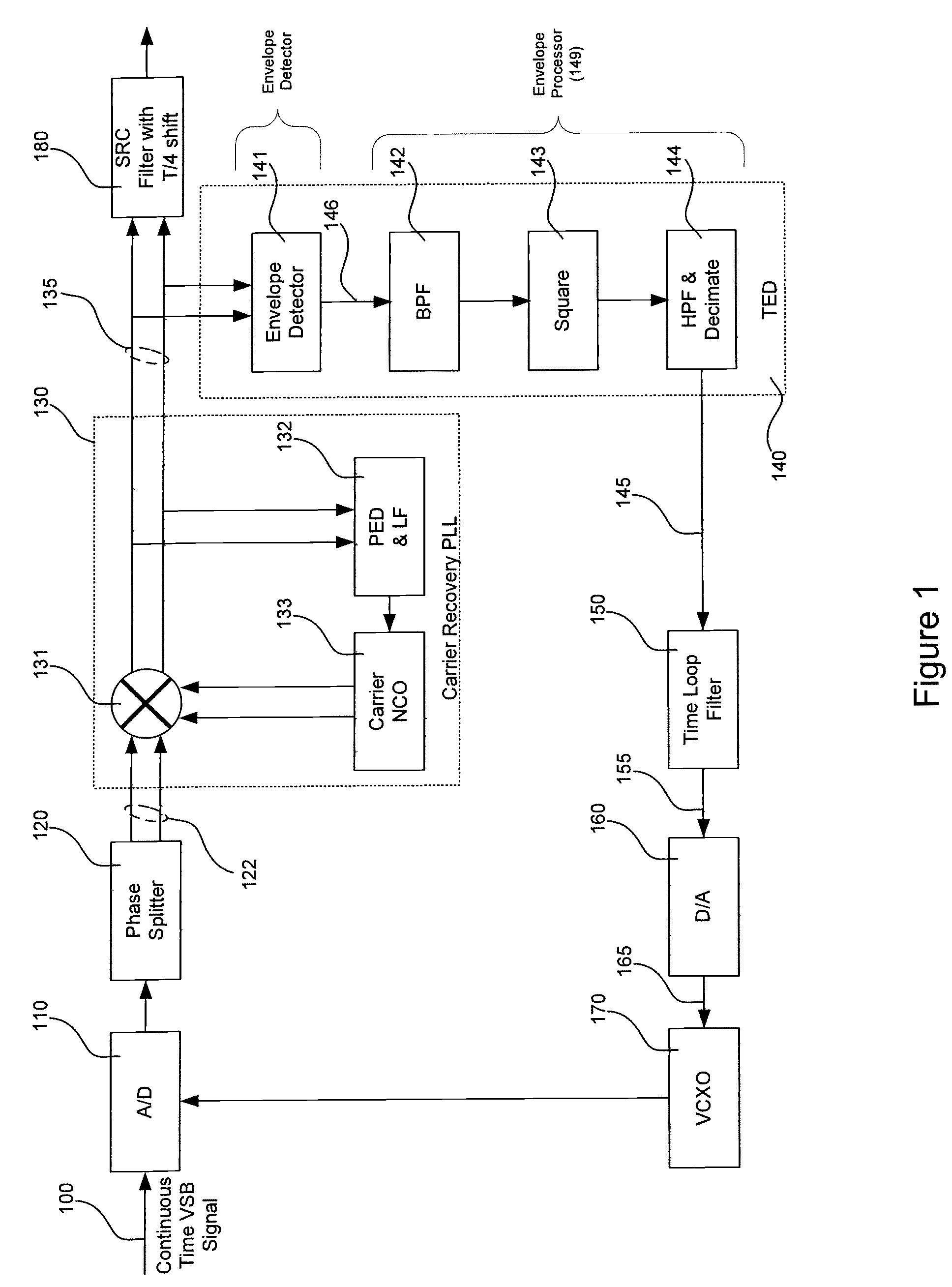

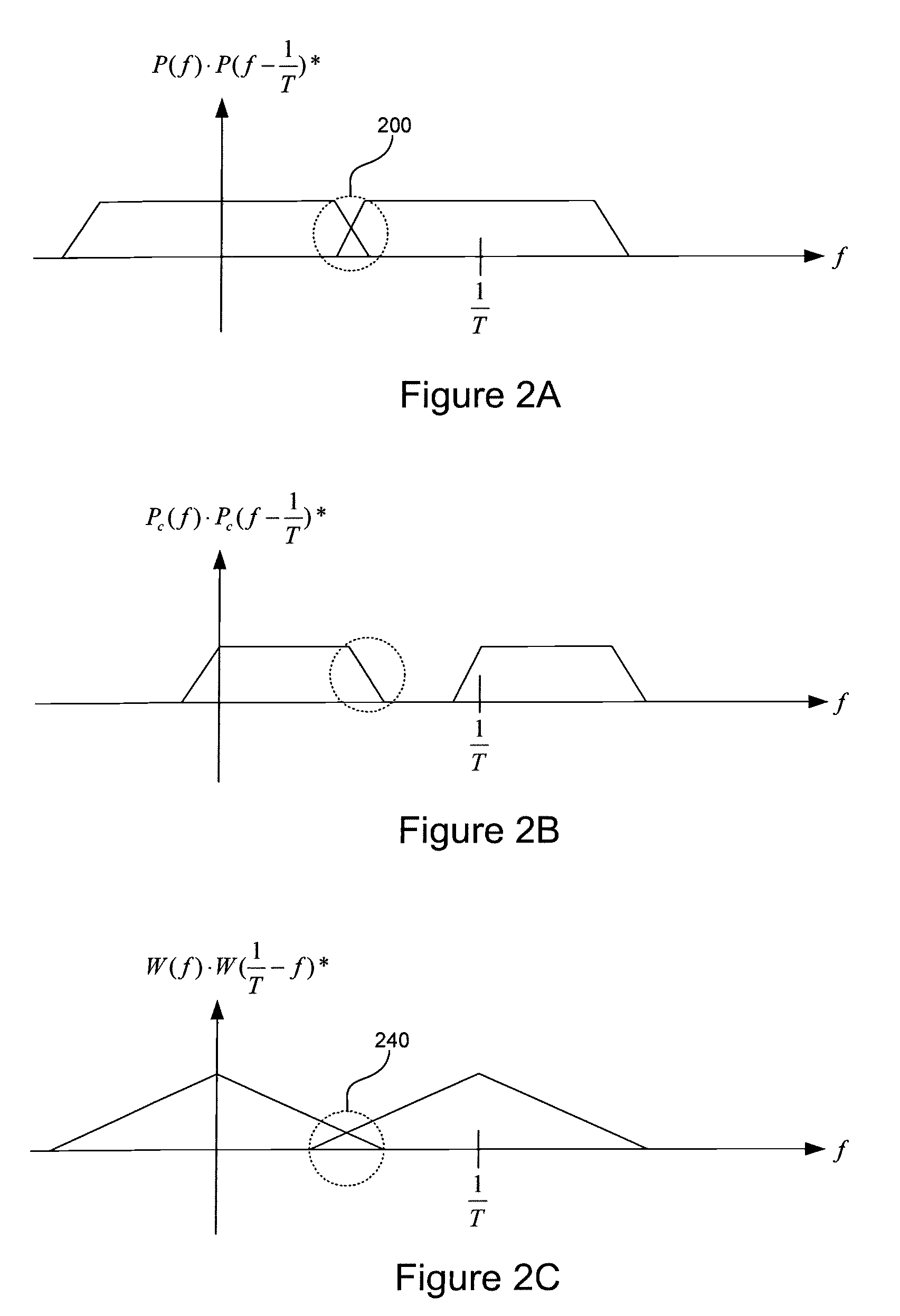

Timing error detector for vestigial side band (VSB)

Owner:INTERSIL INC

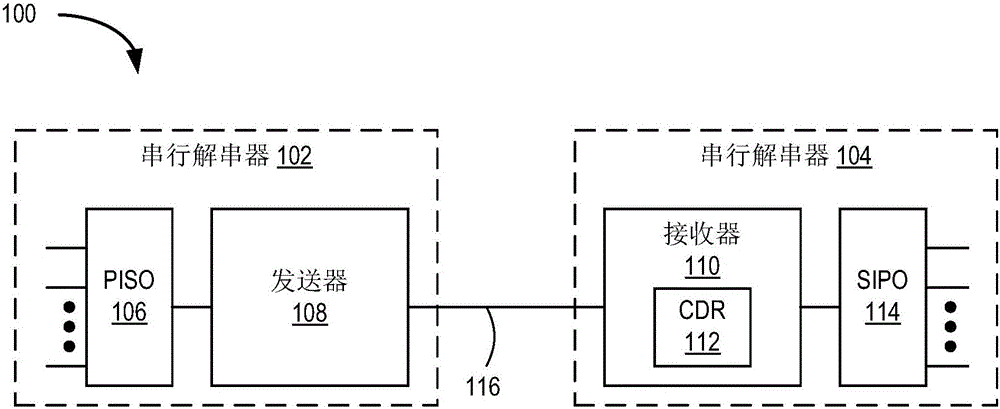

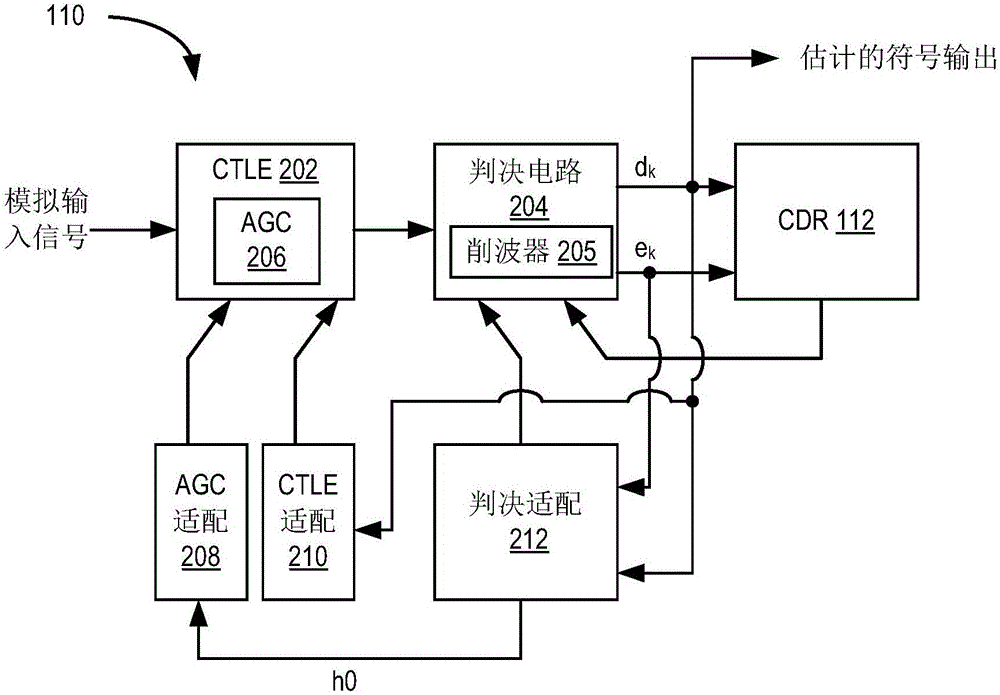

Baud-rate CDR circuit and method for low power applications

ActiveCN106253895APulse automatic controlSynchronisation signal speed/phase controlLoop filterPower application

In an example, a clock data recovery (CDR) circuit for a receiver includes a timing error detector circuit, a loop filter, and a phase interpolator. The timing error detector circuit is coupled to receive, at a baud-rate, data samples and error samples for symbols received by the receiver. The timing error detector circuit is operable to generate both a timing error value and an estimated waveform value per symbol based on the data samples and the error samples. The loop filter is coupled to the timing error detector to receive timing error values. The phase interpolator is coupled to the loop filter to receive filtered timing error values, the phase interpolator operable to generate a control signal to adjust a sampling phase used to generate the data samples and the error samples.

Owner:XILINX INC

Apparatus and method for detecting timing error based on cyclic correlation

InactiveUS7555034B2Reduce complexityReduce search timeTime-division multiplexAmplitude-modulated carrier systemsShift registerTiming error detector

Provided is an apparatus and method for detecting timing errors based on characteristics of cyclic correlation. The apparatus and method can detect the timing errors of many users by using the cyclic characteristics of a midamble code at a time and detects the timing errors based on the characteristics of cyclic correlation to reduce the time required for detecting the users and lower the complexity in terms of Hardware. The apparatus includes a detection section controller, a register, a midamble generator, a midamble shifter, an accumulator, an adder, a shift register and a timing error detector.

Owner:ELECTRONICS & TELECOMM RES INST

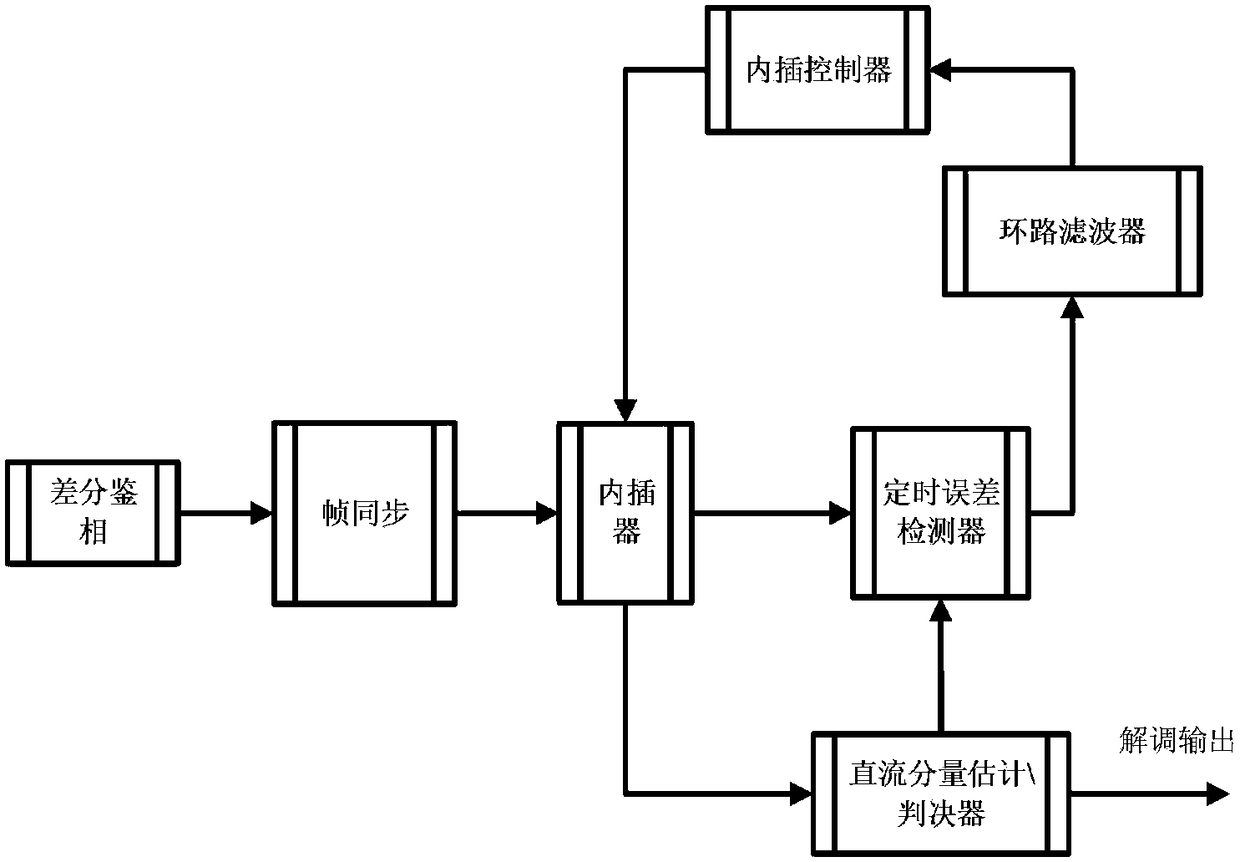

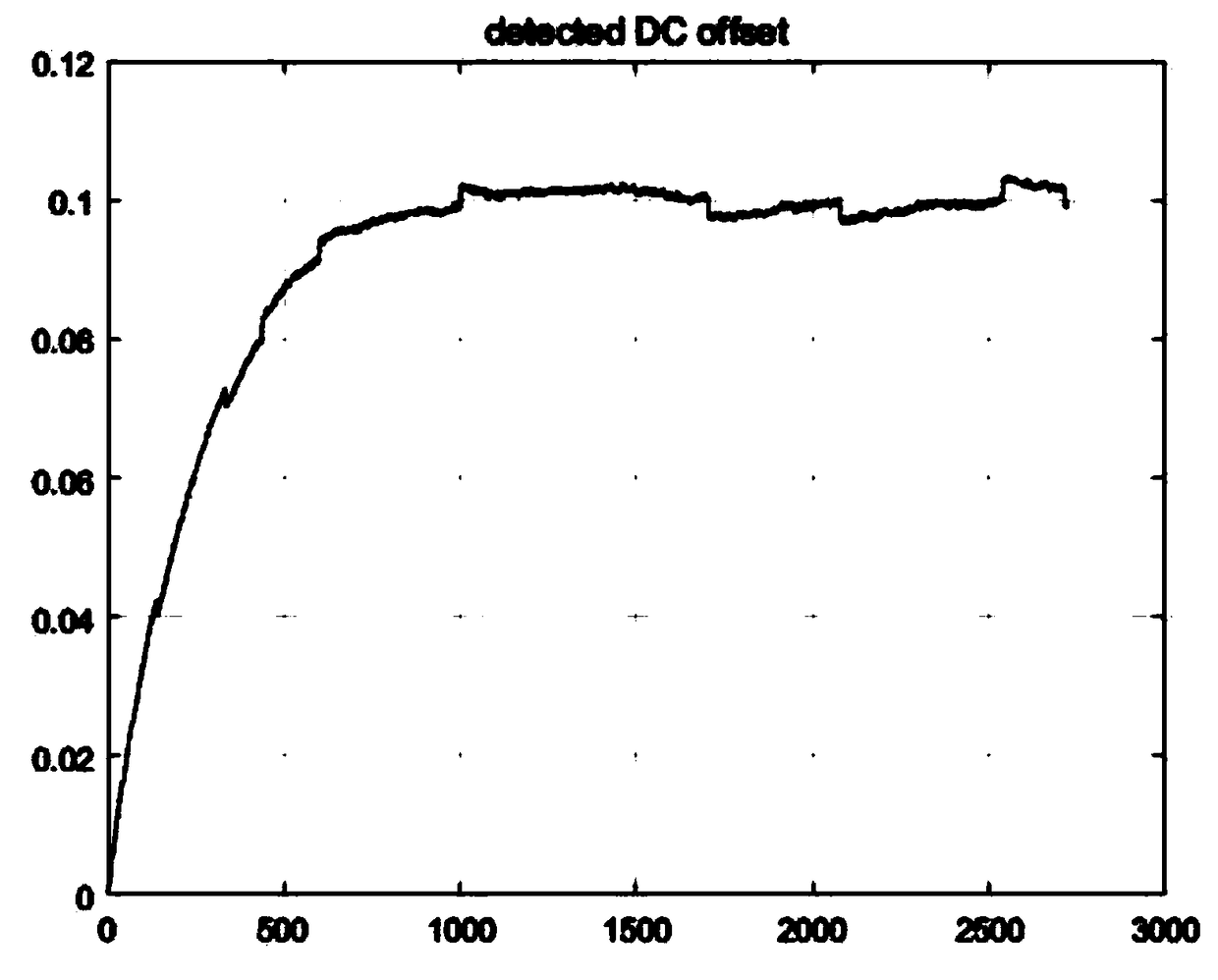

Demodulation circuit applied to GFSK receiver and building method thereof

InactiveCN108306839AAccurate recoverySimple structureFrequency-modulated carrier systemsLoop filterTime error

The invention provides a demodulation circuit applied to a GFSK receiver. The circuit comprises an interpolation filter used for processing a phase signal to acquire a signal with a double symbol rate; a timed error detector used for acquiring timed error information according to a signal input by the interpolation filter; and a loop filter used for processing the timed error information and inputting the processed timed error information into an interpolation controller, wherein the interpolation controller controls the interpolation filter to perform interpolation on a baseband signal, and finally a sampling clock of an interpolator is converged on a symbol clock, so that symbol synchronization of a sending terminal and a receiving terminal is achieved. According to the circuit providedby the invention, the functions of symbol synchronization, carrier frequency offset compensation and symbol judgment can be synchronously completely, and the characteristics of simple structure and good performance are achieved.

Owner:上海富芮坤微电子有限公司

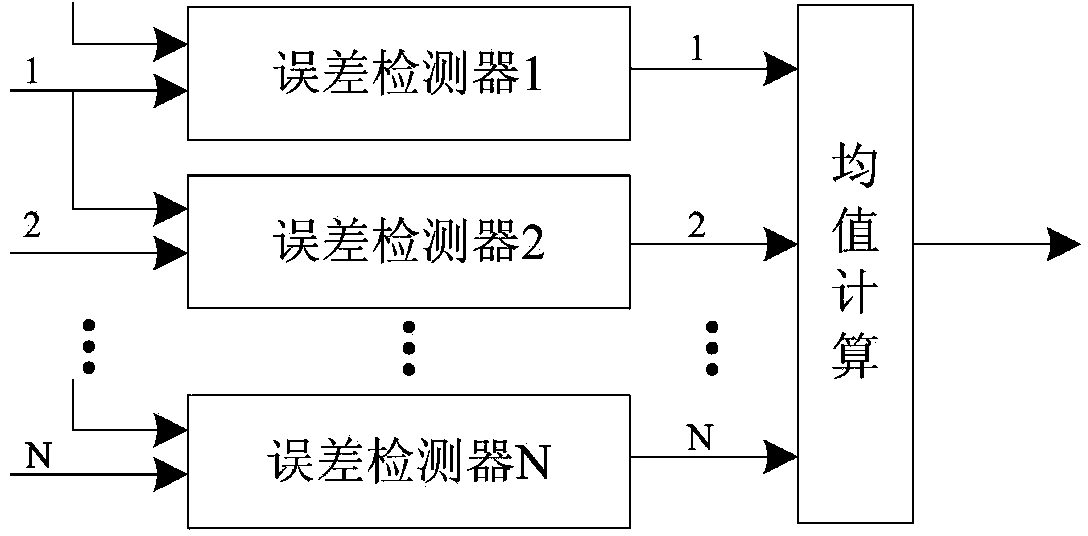

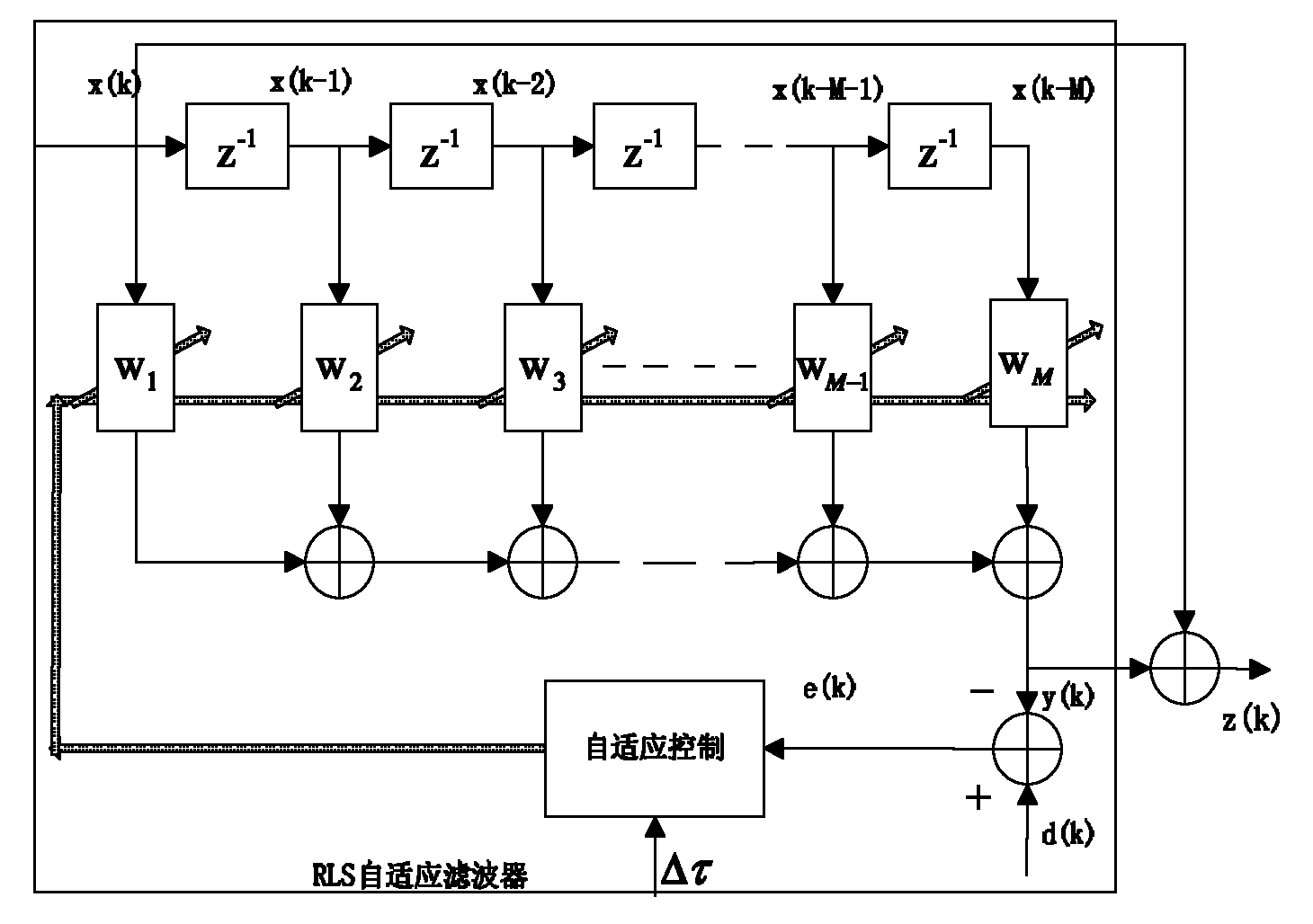

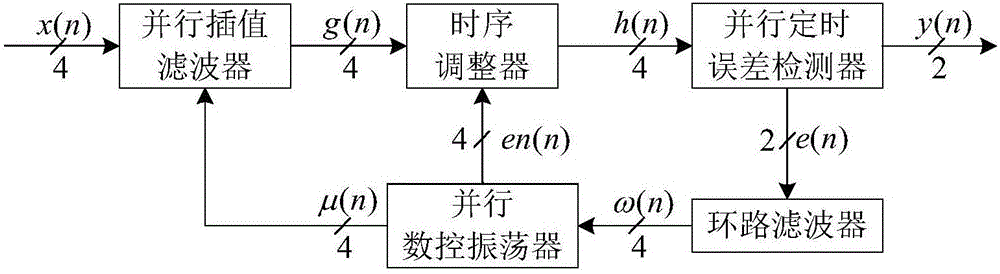

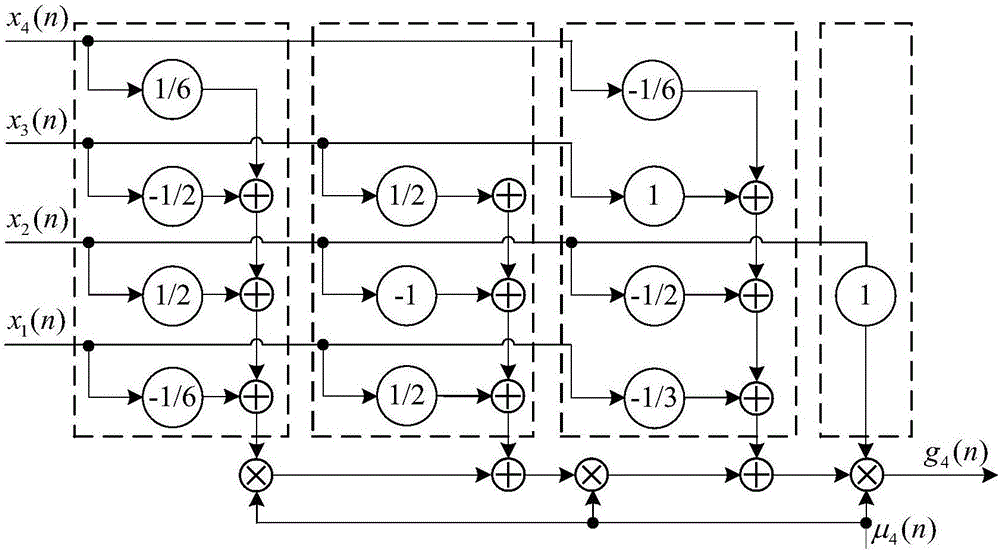

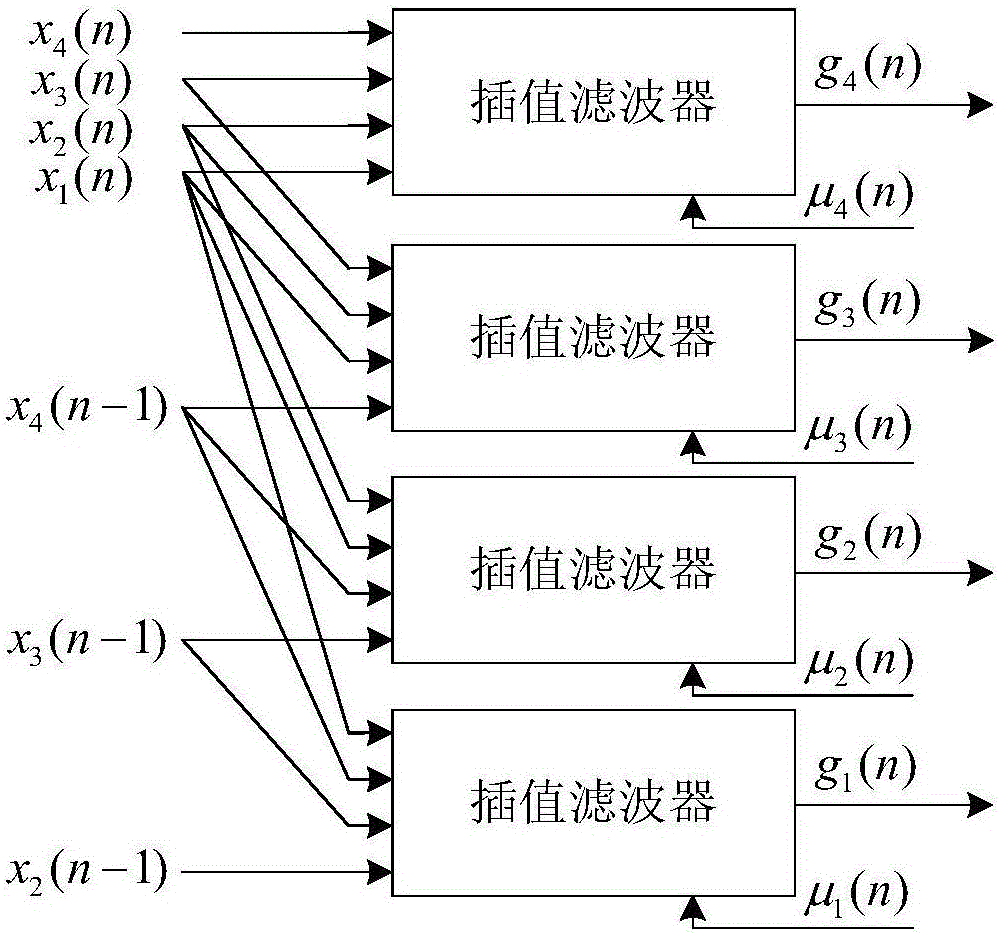

Full-digital time domain parallel timing synchronization system and method under gigabit rate

InactiveCN106506135AReduce speed requirementsSynchronisation error correctionDigital deviceSynchronization system

The invention discloses a full-digital time domain parallel timing synchronization system and method under a gigabit rate. The system comprises a parallel interpolation filter, a time sequence adjuster, a parallel digital-controlled oscillator, a parallel timing error detector and a loop filter. When a timing synchronization module of a communication system is started, the parallel interpolation filter carries out timing synchronization interpolation on received parallel digital signals. The method comprises the steps of carrying out interpolation filtering on N-way parallel digital signals x(n) according to fractional interval compensating signals mu(n); carrying out time sequence adjustment on the signals g(n) after the interpolation filtering according to enabling signals en(n), and outputting N-way parallel valid output values h(n); calculating to obtain timing errors e(n) through adoption of a Gardner algorithm according to the N-way parallel valid output values h(n), and obtaining timing restored N-way valid data y(n) according to the timing errors. According to the system and the method provided by the invention, timing synchronization of the multi-way parallel digital signals can be realized, and a demand of a digital timing synchronization system for the processing speed of digital devices and chips under a high-speed transmission condition of the gigabit rate is reduced.

Owner:HUAZHONG UNIV OF SCI & TECH

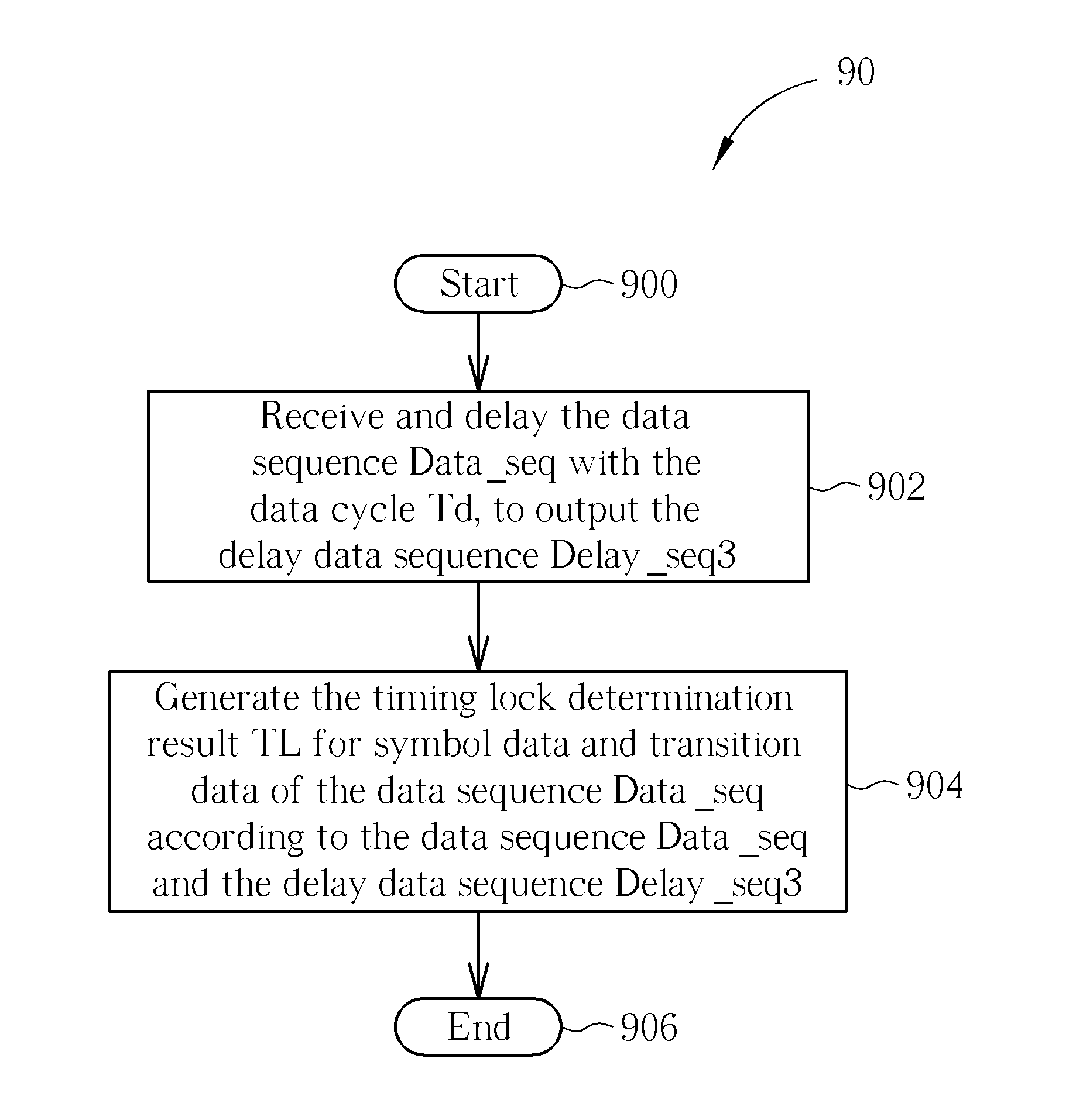

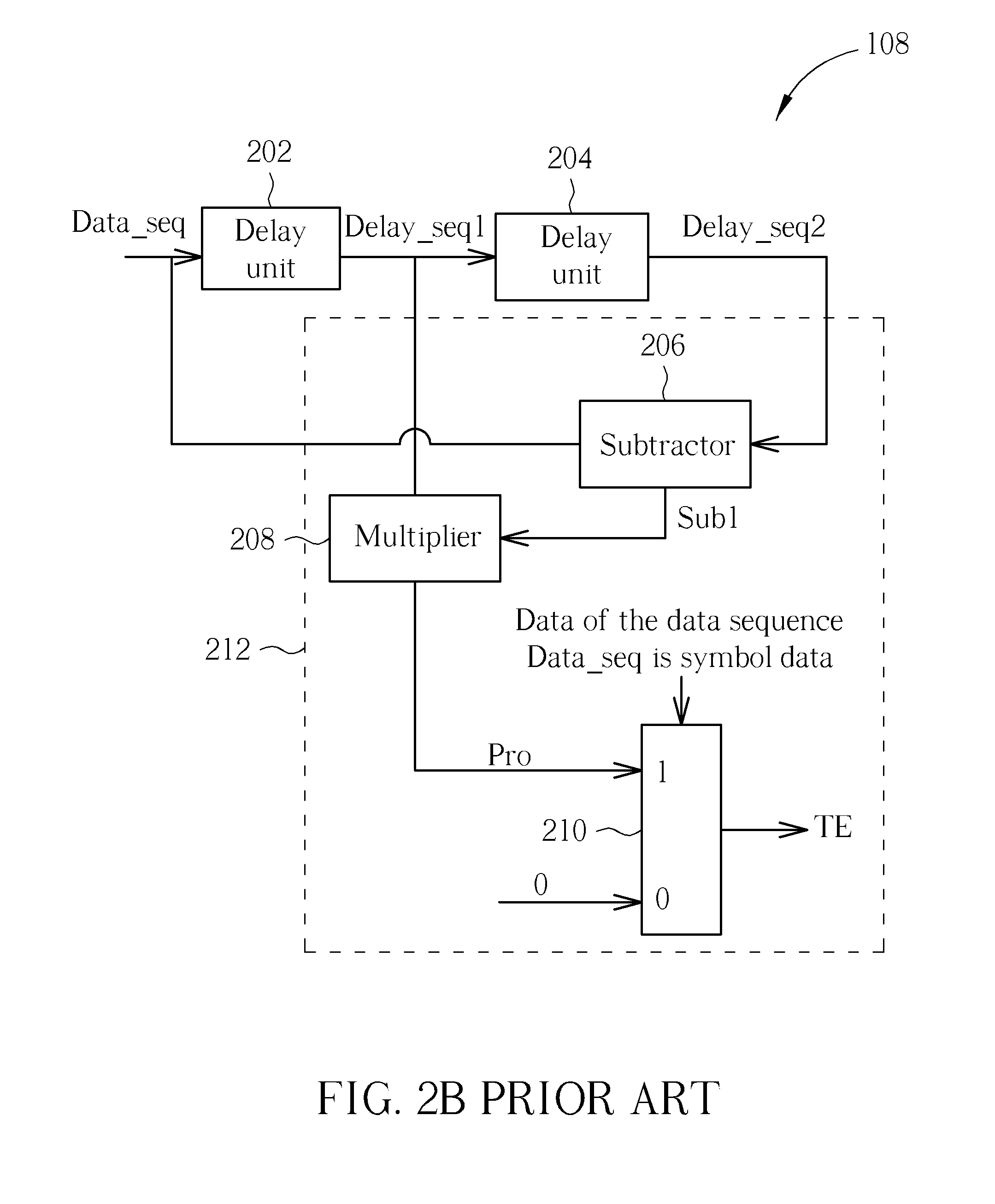

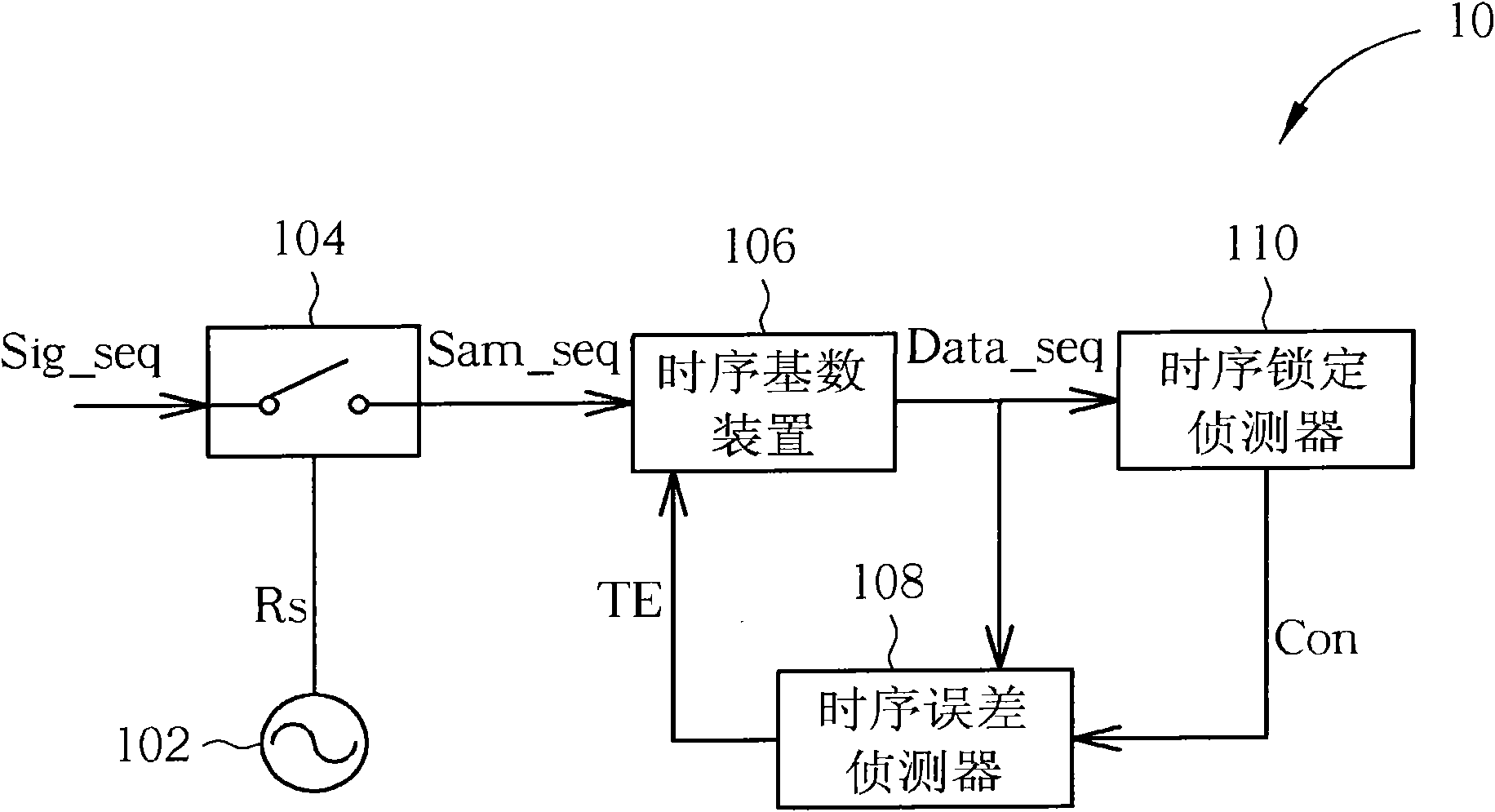

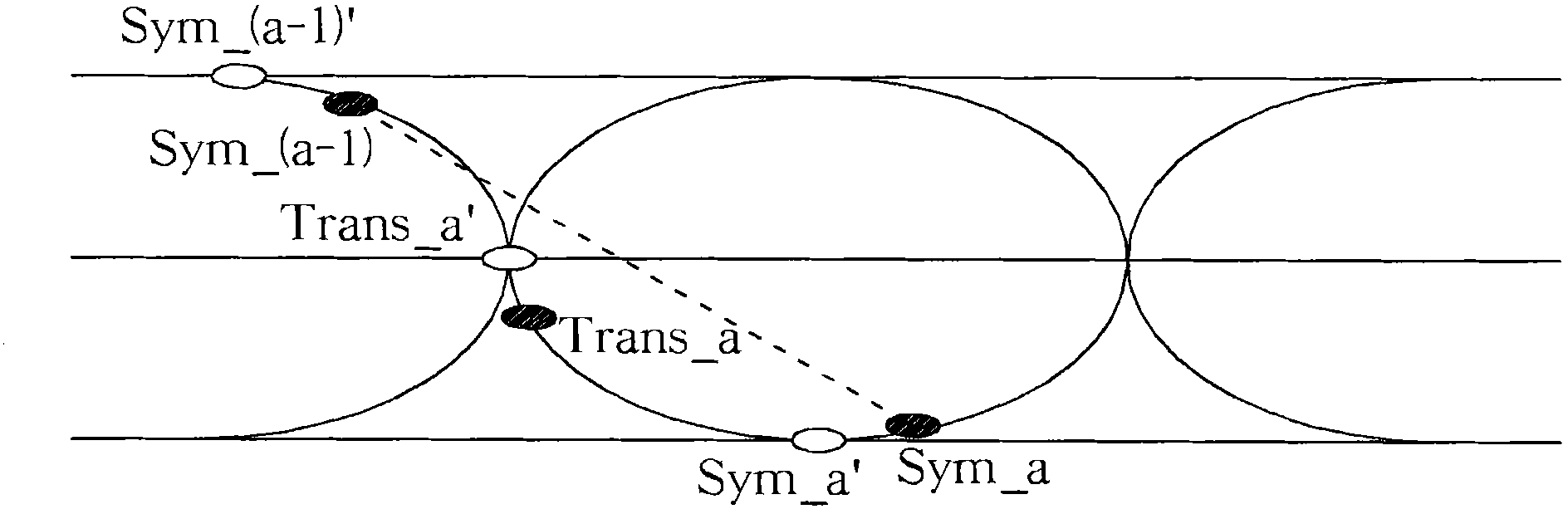

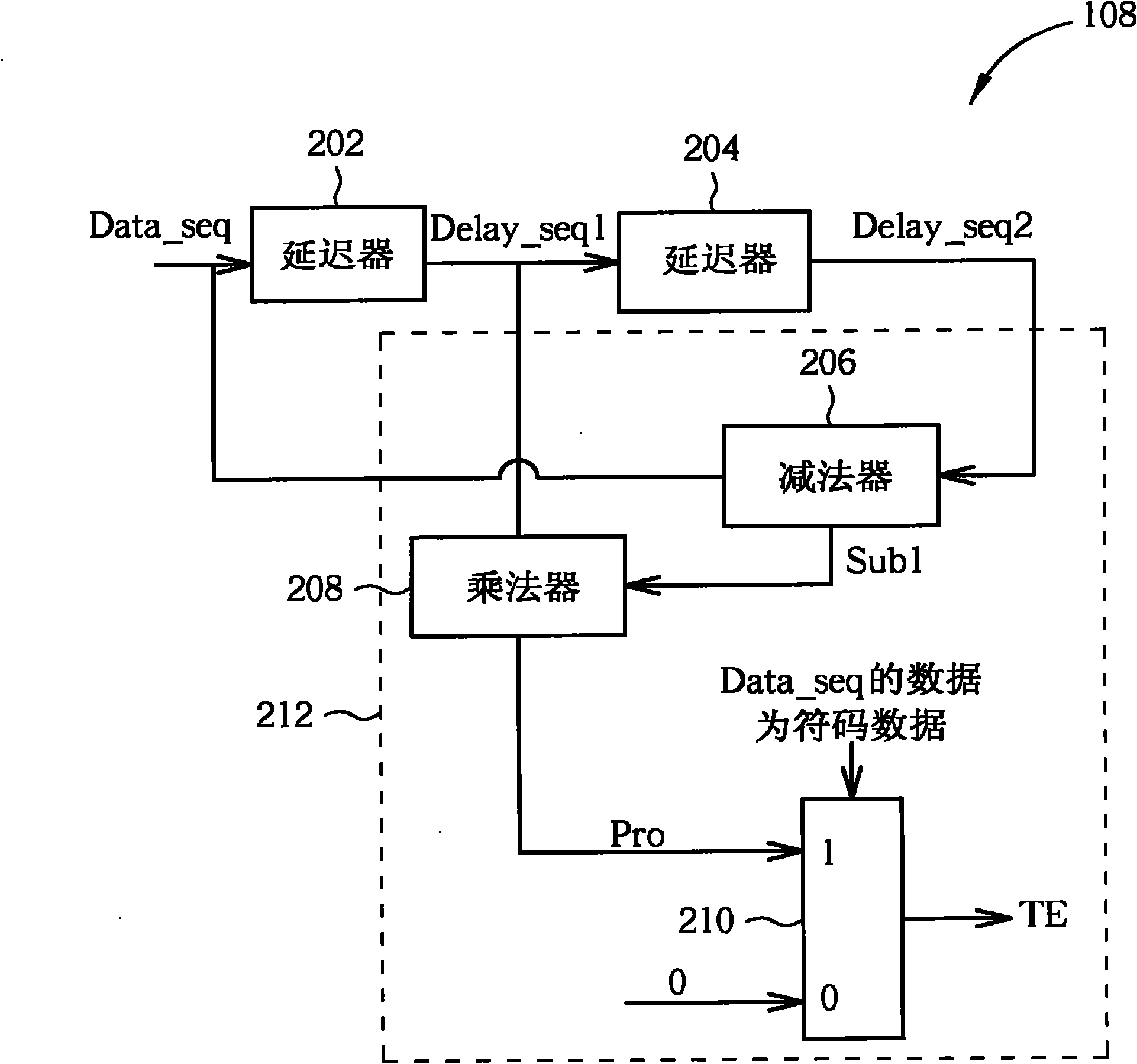

Timing Recovery Controller and Operation Method Thereof

InactiveUS20110299643A1Modulated-carrier systemsError detection/correctionComputer moduleSymbol rate

A timing recovery controller capable of performing timing recovery for a data sequence at twice a symbol rate includes a sampler, a timing base device, a timing error detector and a timing lock detector. The timing error detector includes a first delay unit and a second delay unit, for delaying a data sequence to output a first delay data sequence and a second delay data sequence, respectively, and a timing error calculating module, for generating a timing error value, to adjust a time base. The timing lock detector includes a third delay unit, for delaying the data sequence to output a third delay data sequence, and a timing lock determination module, for generating a timing lock determination result.

Owner:NOVATEK MICROELECTRONICS CORP

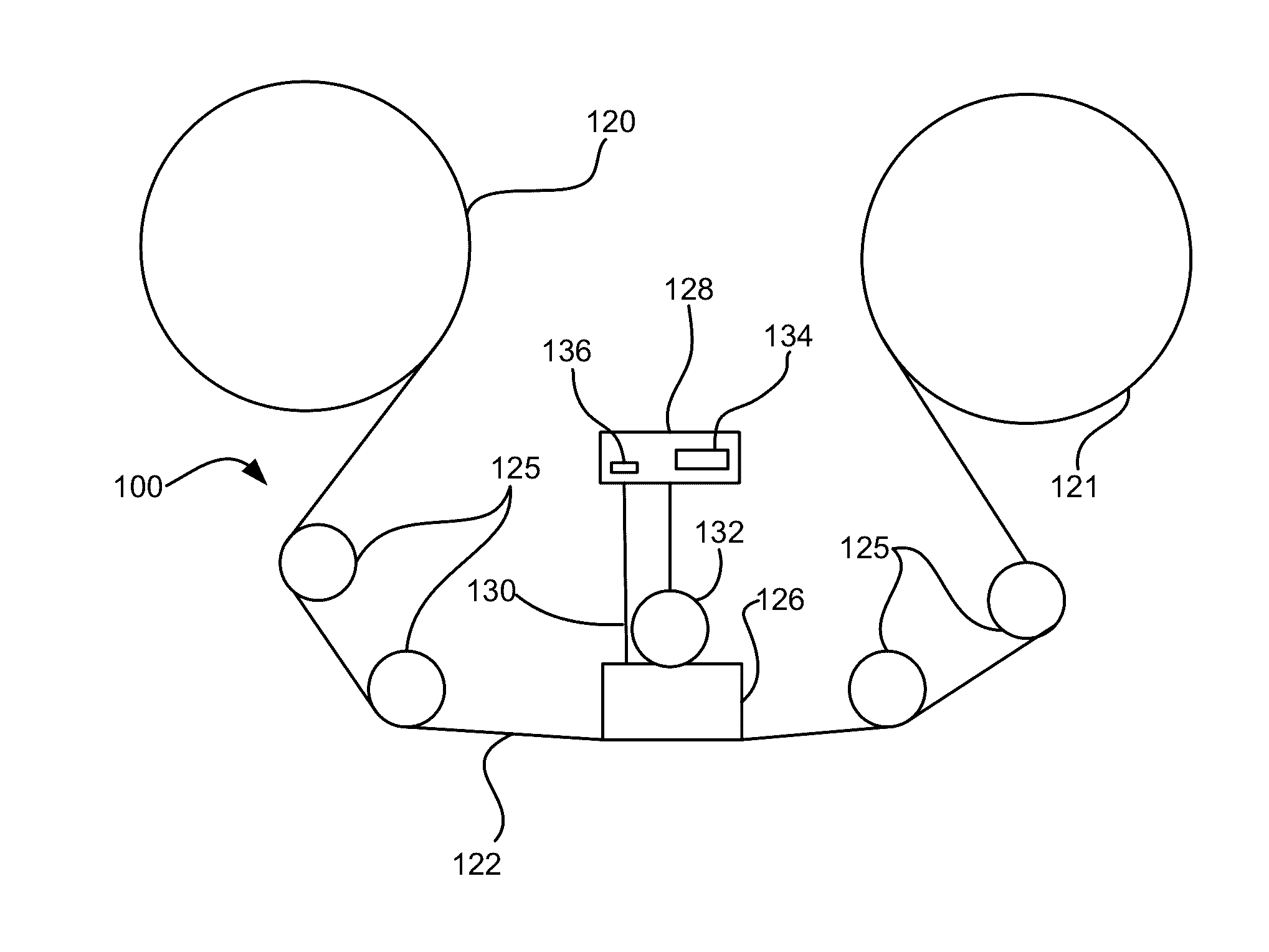

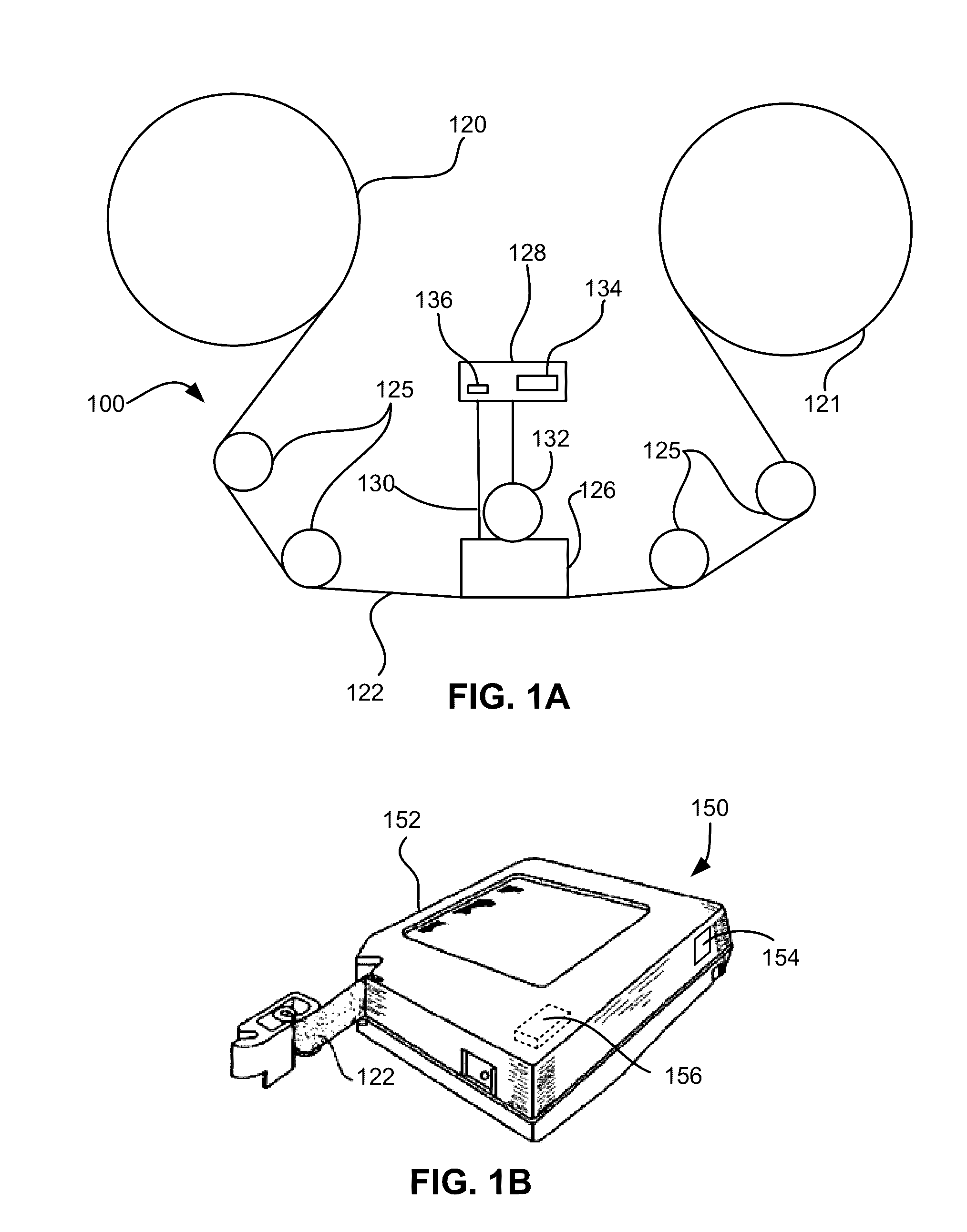

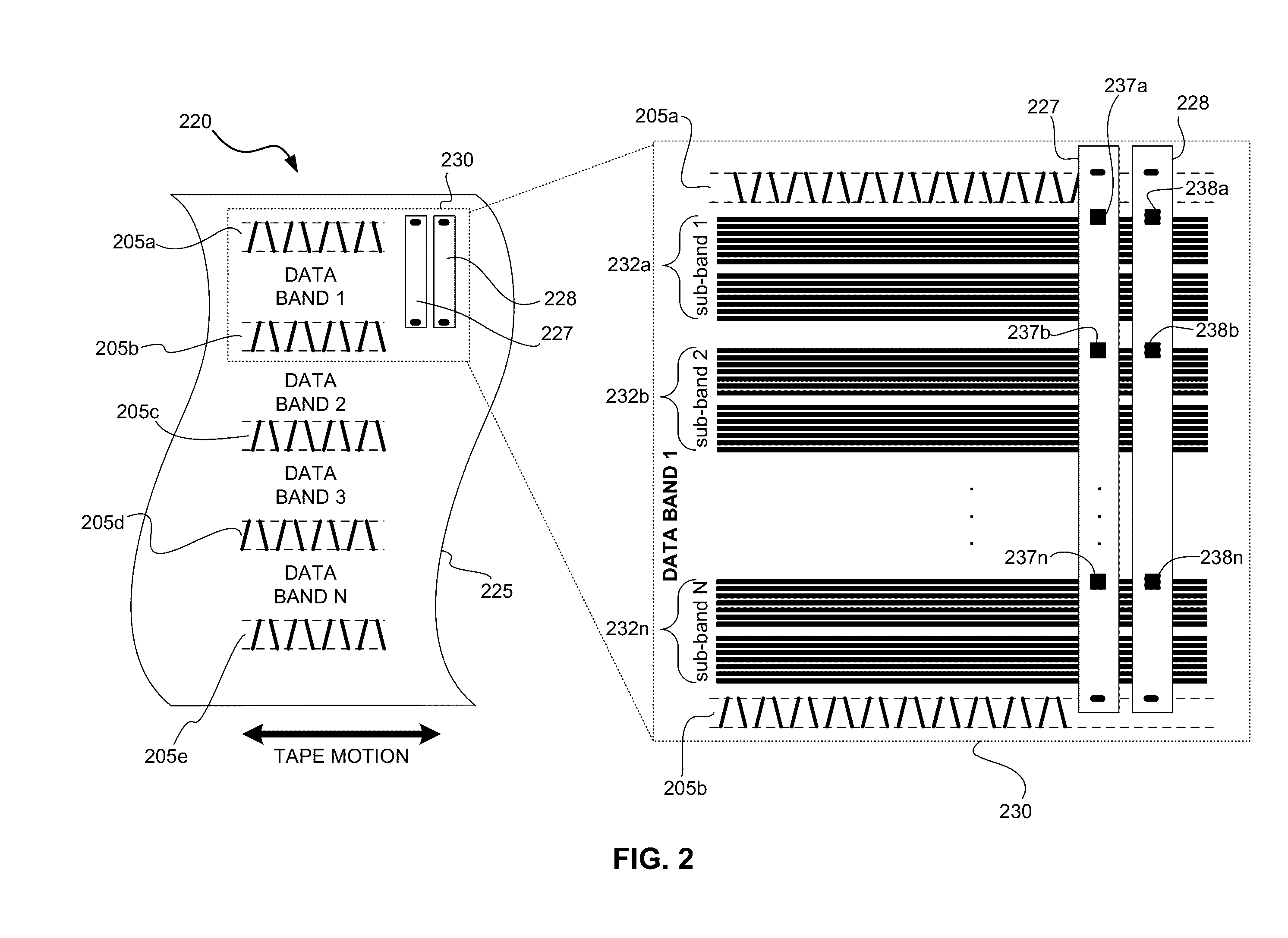

Symbol timing recovery scheme for parallel recording channel systems

ActiveUS20160365110A1Reduced rate of cycle slipManufacture unitary devices of plural headsAlignment for track following on tapesLoop filterTransducer

An apparatus includes a loop filter that receives a plurality of input signals. Each of the input signals is based on a different timing error detector output signal. The apparatus also includes a plurality of read channels, a plurality of interpolation filters, and an array of transducers. Each of the interpolation filters is in communication with a corresponding one of the read channels. Each of the transducers is in communication with a corresponding one of the read channels. The loop filter processes the plurality of input signals, and outputs a different total phase signal for each received input signal. Each of the interpolation filters samples the corresponding read channel based on one of the total phase signals output by the loop filter. The loop filter processes the plurality of input signals by calculating a phase estimate of the samples, and a skew estimate of the samples, relative to written data.

Owner:INT BUSINESS MASCH CORP

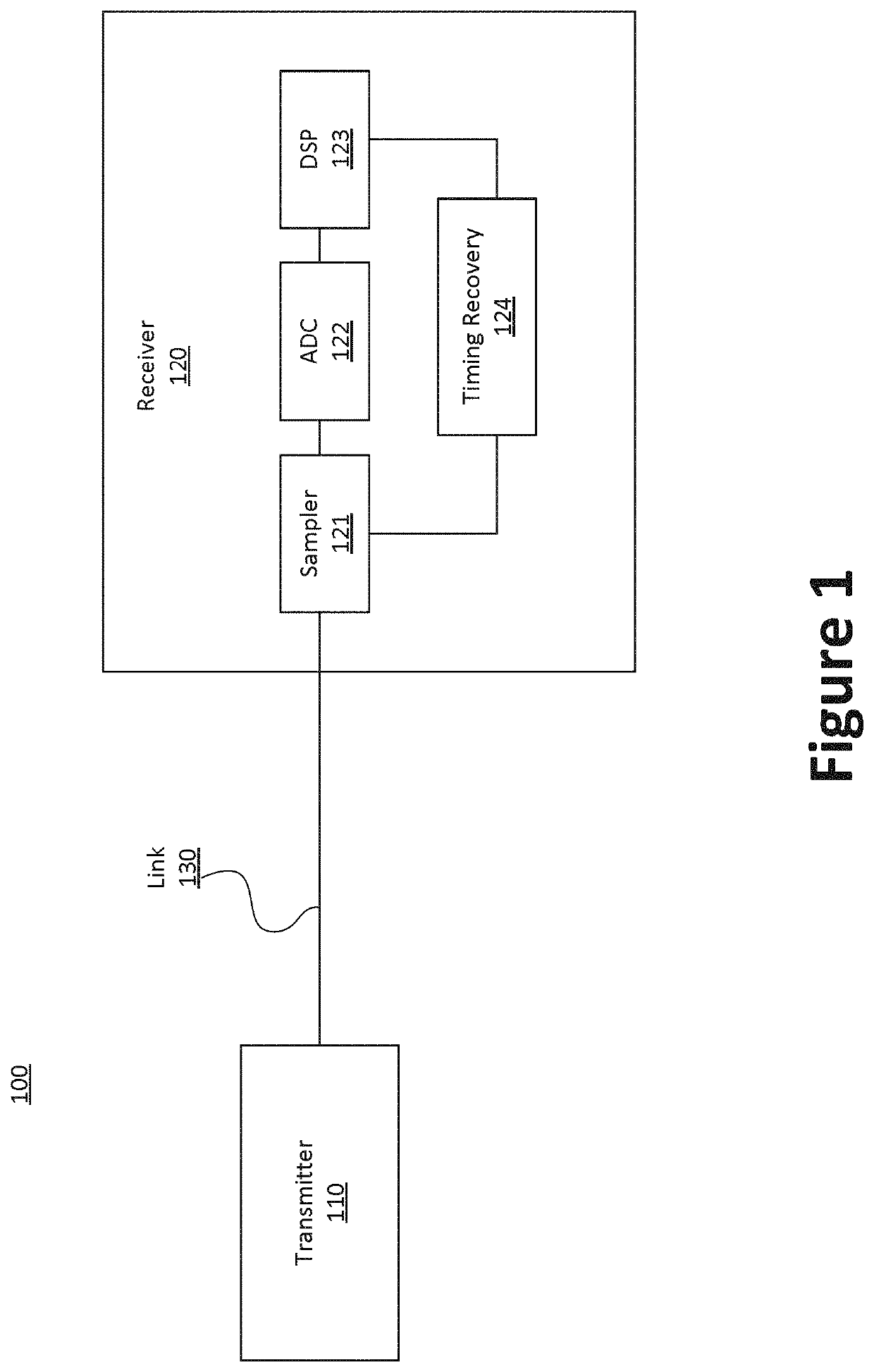

Systems and methods for timing recovery with bandwidth extension

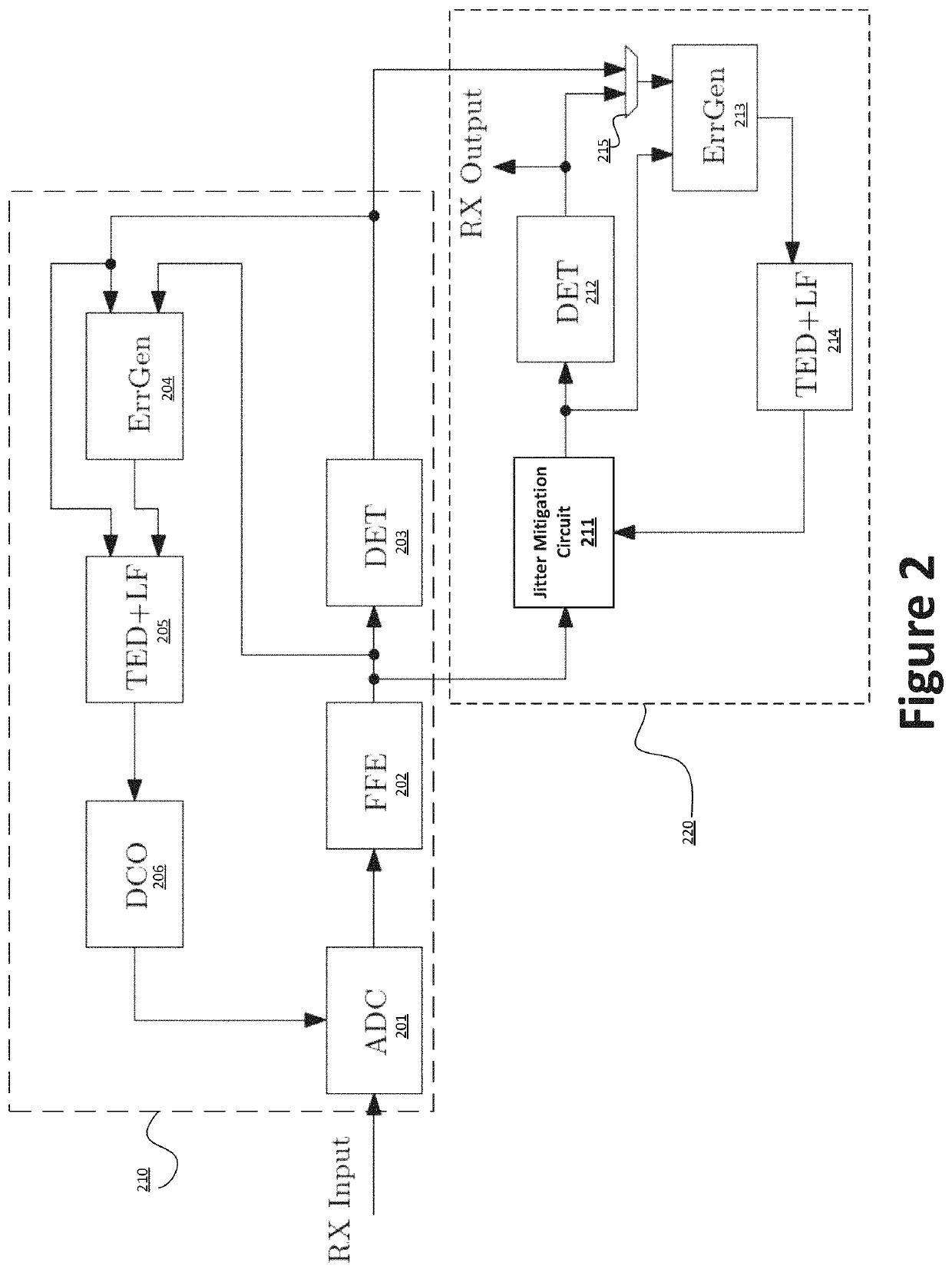

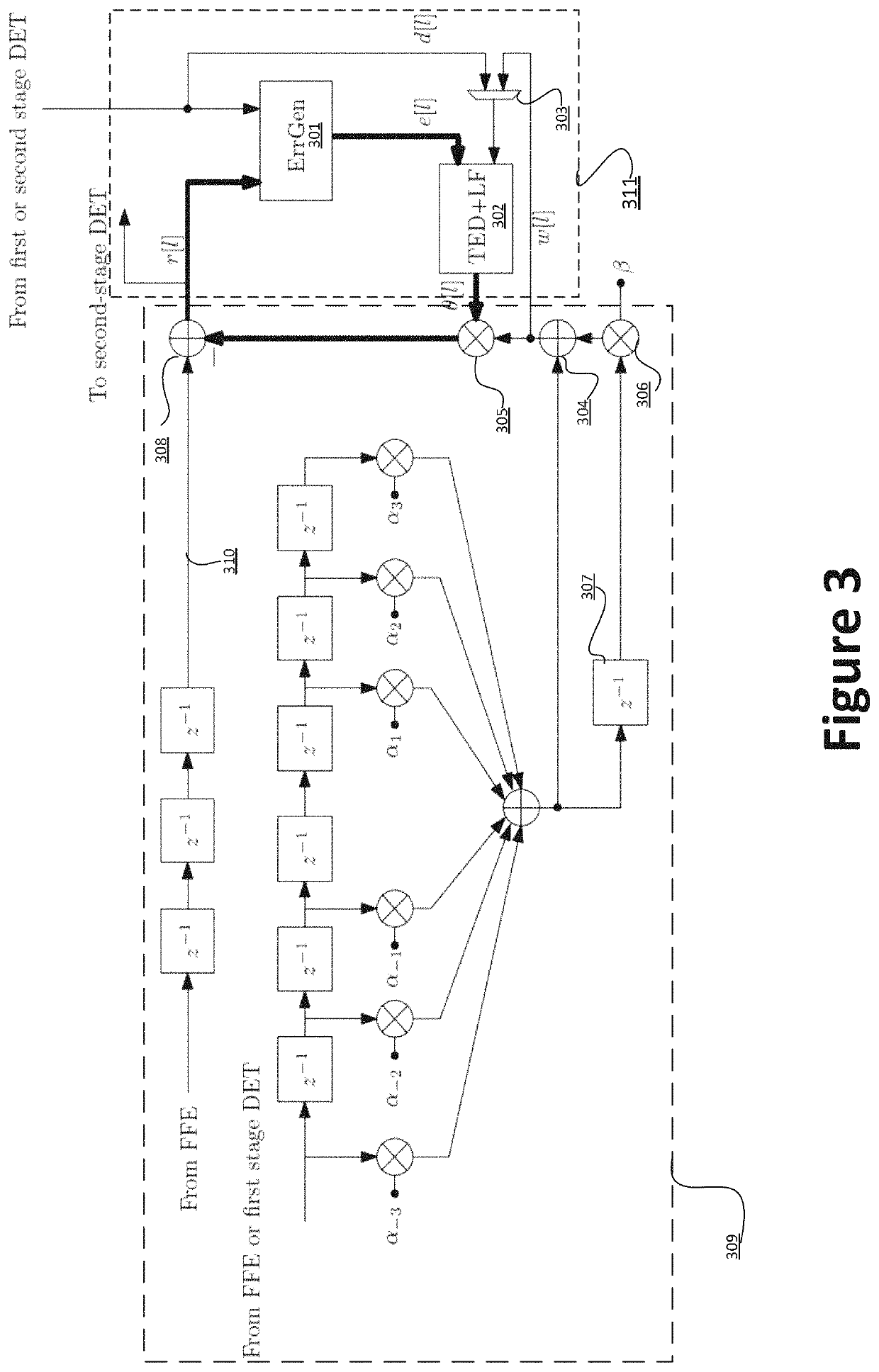

ActiveUS11239991B2Reduce jitterEffectively compensate for jitterError detection/prevention using signal quality detectorSynchronisation error correctionLoop filterTiming error detector

The present invention is directed to circuits and communication. More specifically, a specific embodiment of the present invention provides a timing recovery device with two stages. The first stage generates a clock signal to sample the received waveform, and the second stage provides timing-jitter mitigation. The second stage includes a jitter mitigation circuit with coefficients a function of the instantaneous jitter estimate, in addition to a jitter estimation tracking loop consisting of an error generator, a timing error detector and a loop filter to compensate for timing jitter associated with the clock signal. There are other embodiments as well.

Owner:MARVELL ASIA PTE LTD

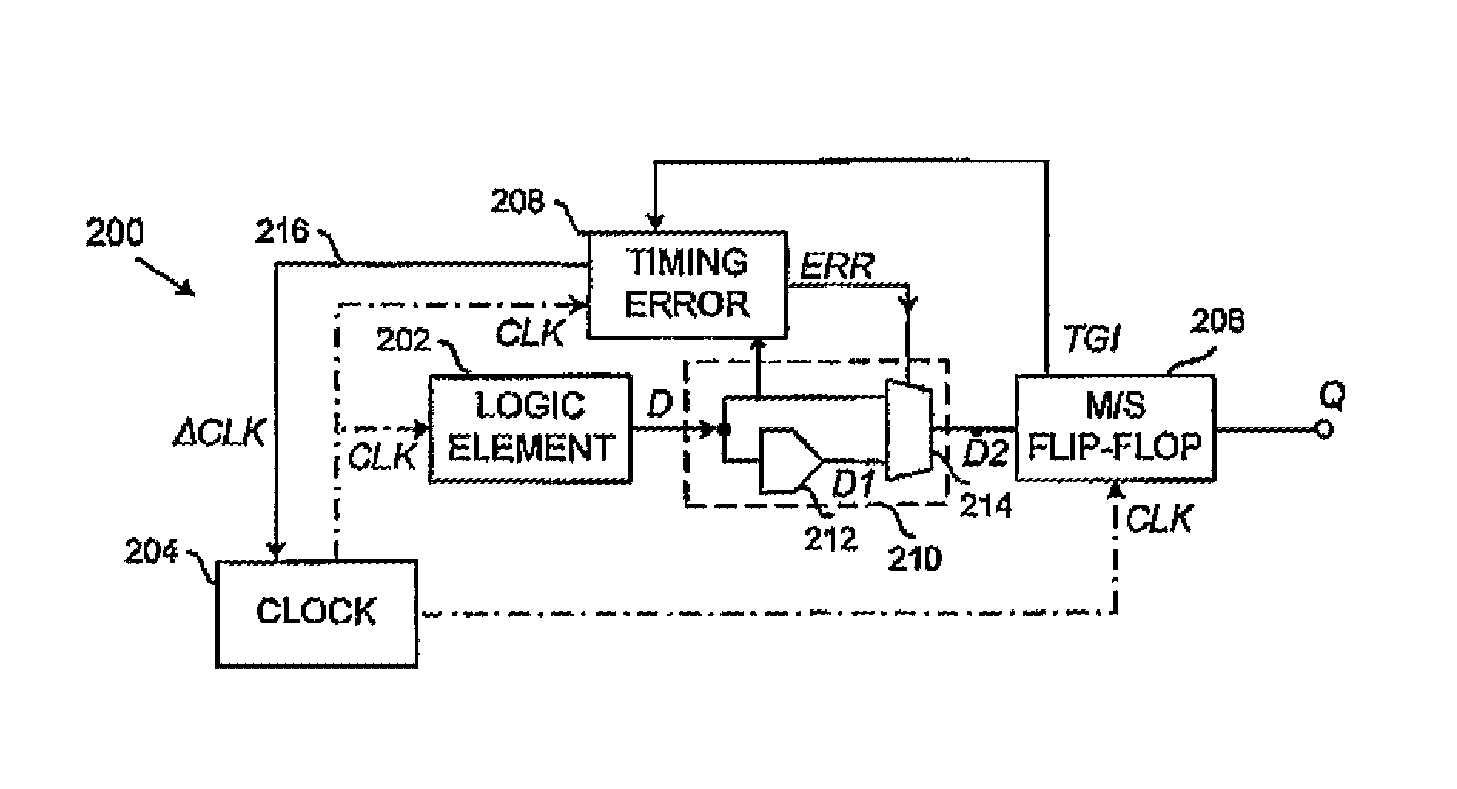

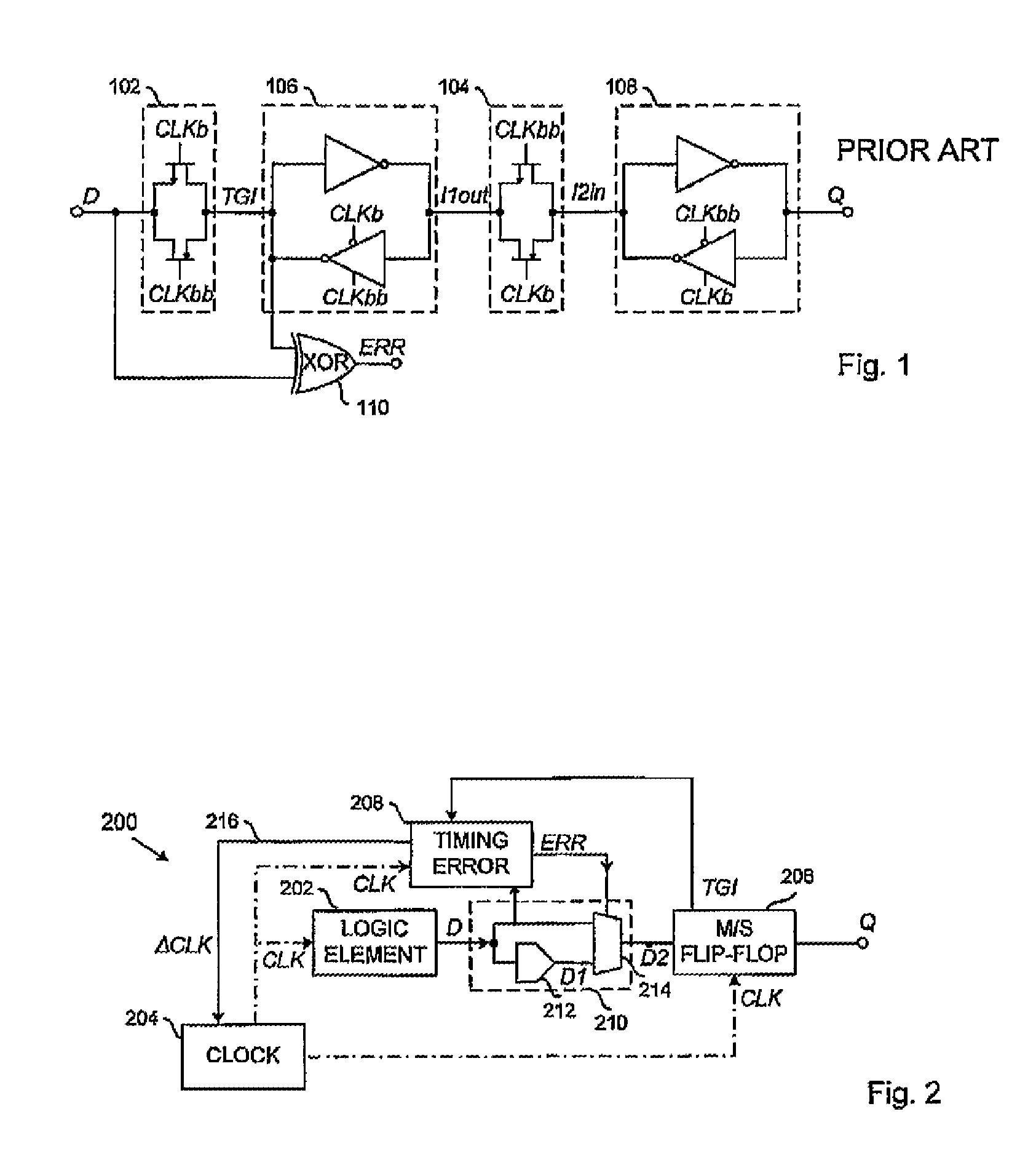

Master-slave flip-flop with timing error correction

A digital logic circuit includes a logic element for providing a data signal, a clock for providing a clock signal and a master-slave flip-flop. The master-slave flip-flop includes a master latch for storing data on a master latch input at a first active edge of the clock signal and a slave latch for storing data on an output of the master latch at a second active edge of the clock signal following the first active edge. A timing error detector asserts an error signal in response to a change in the data signal during a detection period following the first active edge of the clock signal. A timing correction module selectively increases a propagation delay of the data signal from the logic element to the master latch input in response to the error signal.

Owner:NXP USA INC

Timing Error Detector with Diversity Loop Detector Decision Feedback

ActiveUS20140362463A1Modification of read/write signalsRecord information storageDiversity schemeTiming error detector

Aspects of the disclosure pertain to an apparatus for detecting timing errors including an analog to digital converter circuit, a diversity loop detector and a timing error calculation circuit. The analog to digital converter circuit is operable to convert an input signal into a series of digital samples. The diversity loop detector is operable to apply a data detection algorithm to a plurality of signals derived from the series of digital samples at different phase offsets, to select one of the phase offsets, and to yield a detected output with the selected phase offset. The timing error calculation circuit is operable to calculate a timing error of the analog to digital converter circuit based at least in part on the selected phase offset.

Owner:AVAGO TECH INT SALES PTE LTD

Timing recovering method

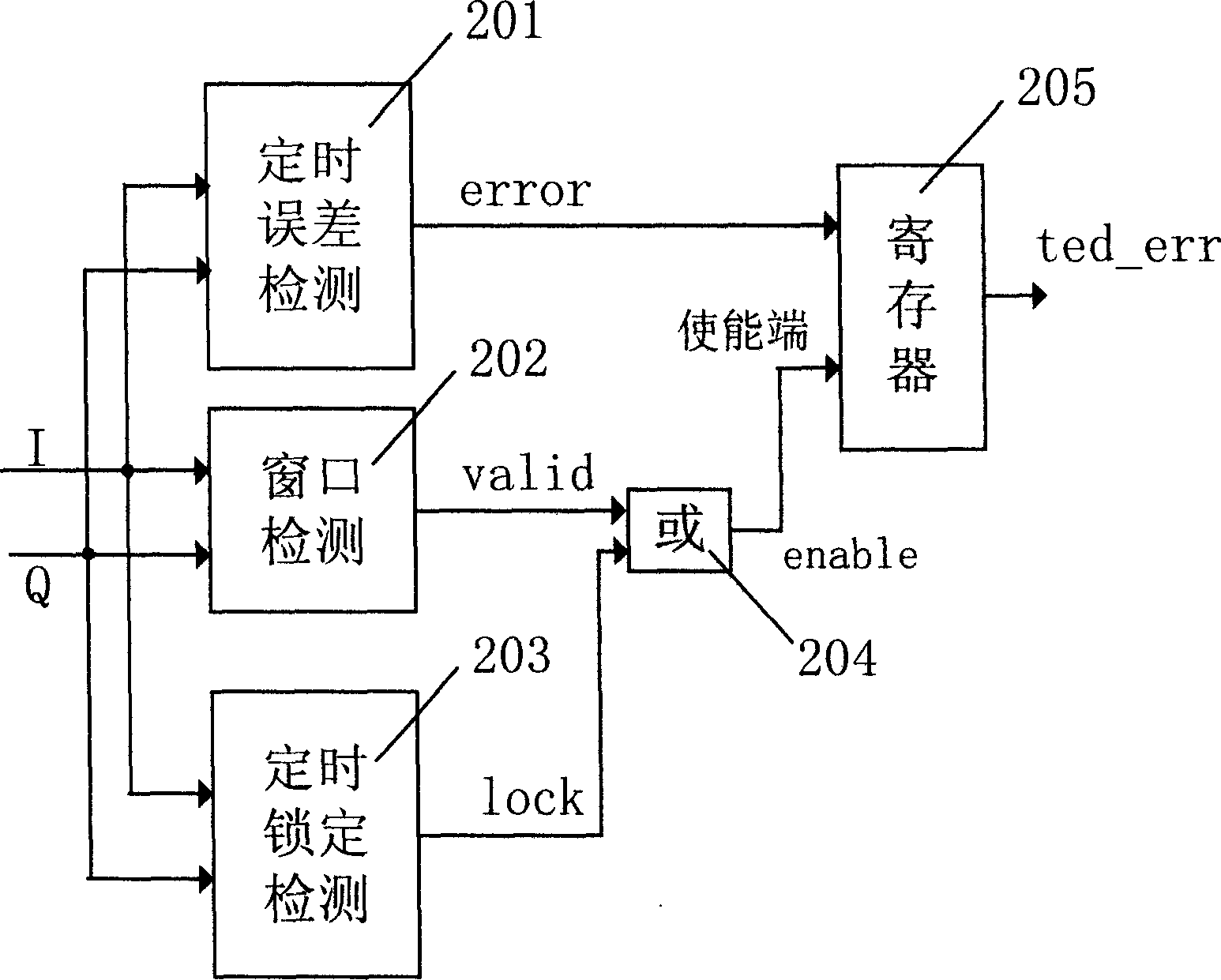

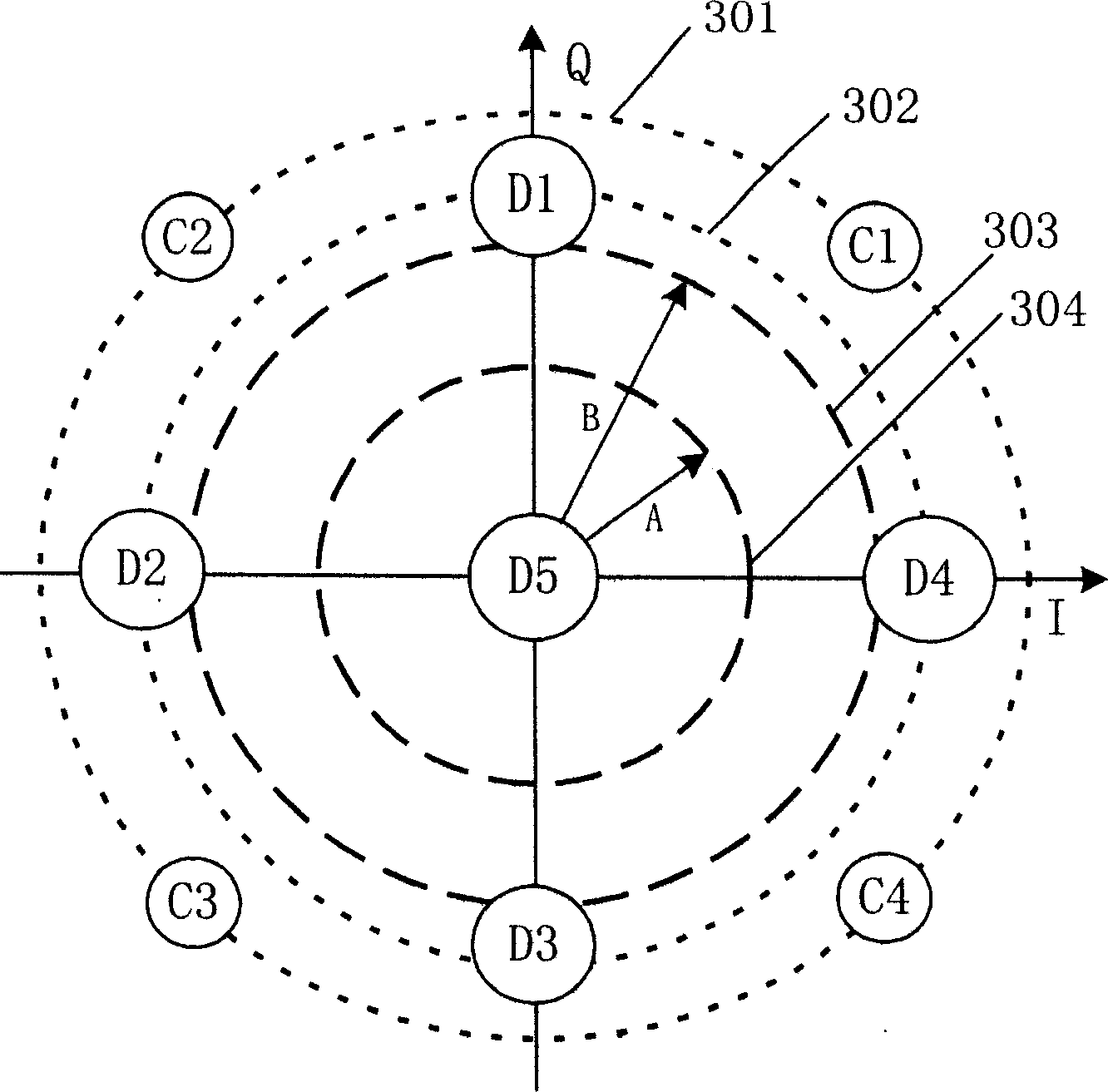

ActiveCN1614961AGuaranteed convergenceIncrease timing capture rangeBaseband systemsLoop filterWindow detection

The method includes following steps: the timing error is exacted and inputted; if the locking detector indicates the timing is locking, then the widows detecting is not made; the timing errors of inputted signal extracted at each time are all outputted to loop filter; if the locking detector indicates the timing is not locking, then the timing error will be decided if it is available according to the result of windows detecting.

Owner:HANGZHOU NATCHIP SCI & TECH

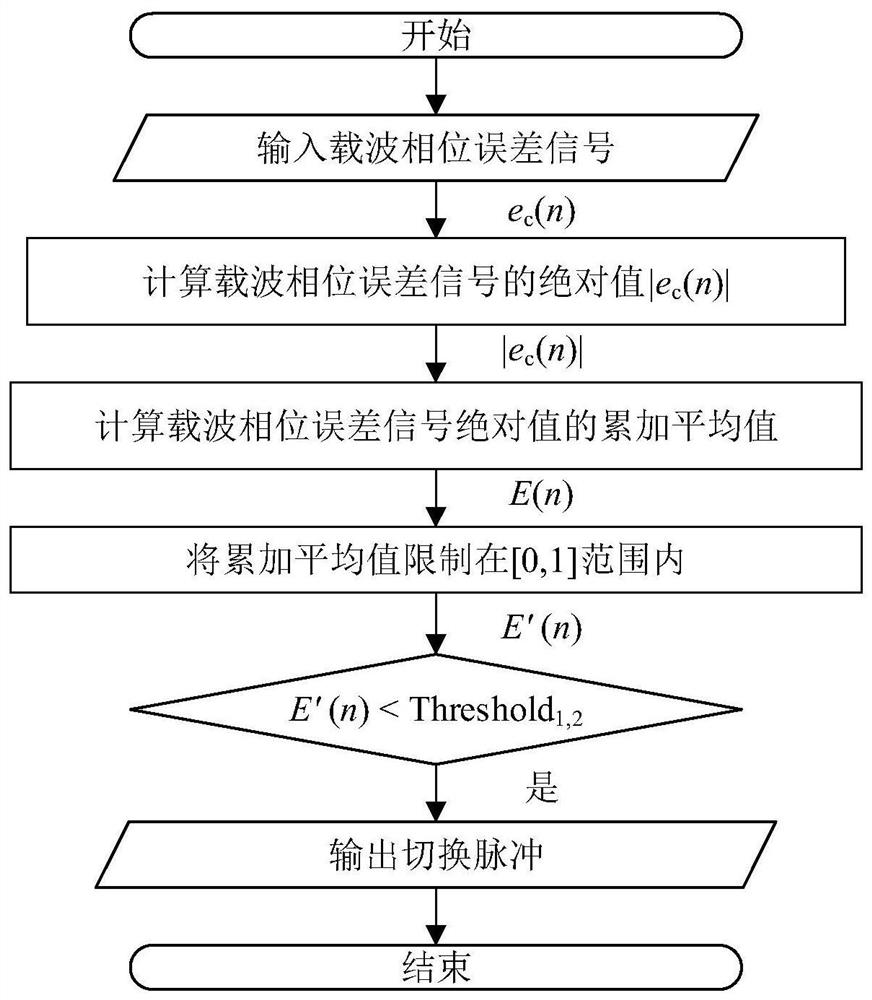

Adaptive carrier and symbol joint synchronization method of QPSK signal

ActiveCN111935052AAvoid the phenomenon of loss of lockImprove synchronicityMulti-frequency code systemsLoop filterPhase detector

The invention provides an adaptive carrier and symbol joint synchronization method of a QPSK signal. The method comprises the following steps: determining an input signal, obtaining two paths of QPSKbaseband signals which are orthogonal to each other, calculating a carrier phase error signal and a timing phase error signal of the baseband signals by using a phase discriminator and a Gardner timing error detector respectively, calculating a characteristic value, and dividing a synchronization process into three stages. In a coarse synchronization stage, a transition stage and a fine synchronization stage, corresponding loop filters are identified and selected in the existing synchronization stage, signals are corrected, and final judgment signals are output. According to the method, the two technical indexes of the synchronization speed and the synchronization precision of the synchronization loop can be effectively improved at the same time, and particularly, the synchronization effect of the QPSK signal with large deviation is obviously improved.

Owner:HARBIN INST OF TECH

Timing recovery controller and operating method thereof

The invention discloses a timing recovery controller which can perform timing recovery at a doubled code rate. The timing recovery controller comprises a sampler, a timing base device, a timing error detector and a timing lock detector, wherein the timing error detector comprises a first delayer and a second delayer which are used for delaying signals to output a first delayed data sequence and a second delayed data sequence, and a timing error calculation module for generating a timing error value to adjust a timing base; and the timing lock detector comprises a third delayer for delaying a signal to output a third delayed data sequence, and a timing lock judgment module for generating a timing lock judgment result.

Owner:NOVATEK MICROELECTRONICS CORP

Timing Error Detector and Method Thereof

ActiveUS20100054318A1Quality improvementDetection errorError preventionModulated-carrier systemsMean squarePeak value

An effective data sequence based timing error detector (EDS-TED) for baseband transmission system using Tomlinson-Harashima Precoder is disclosed. The EDS-TED extracts timing error information embedded in the received signal to build up autocorrelation between the ESD signals and minimize the mean square error between the received and desired EDS so as to improve the performance of the TED in terms of Peak-to-Peak Jitter and TED gain. Thus the quality of the received signal increases and the error rate decreases.

Owner:NAT TAIWAN UNIV