High dynamic scope quick clock recovery system based on voltage crystal oscillator

A technology of voltage-controlled crystal oscillation and large dynamic range, applied in transmission systems, digital transmission systems, automatic power control, etc., can solve the problem of increasing the time delay of the carrier synchronization loop and reducing the resistance of the clock recovery system to large sampling frequency offsets Capability and other issues, to achieve the effect of clock recovery, reduce loop delay and operating frequency, reduce hardware complexity and hardware cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

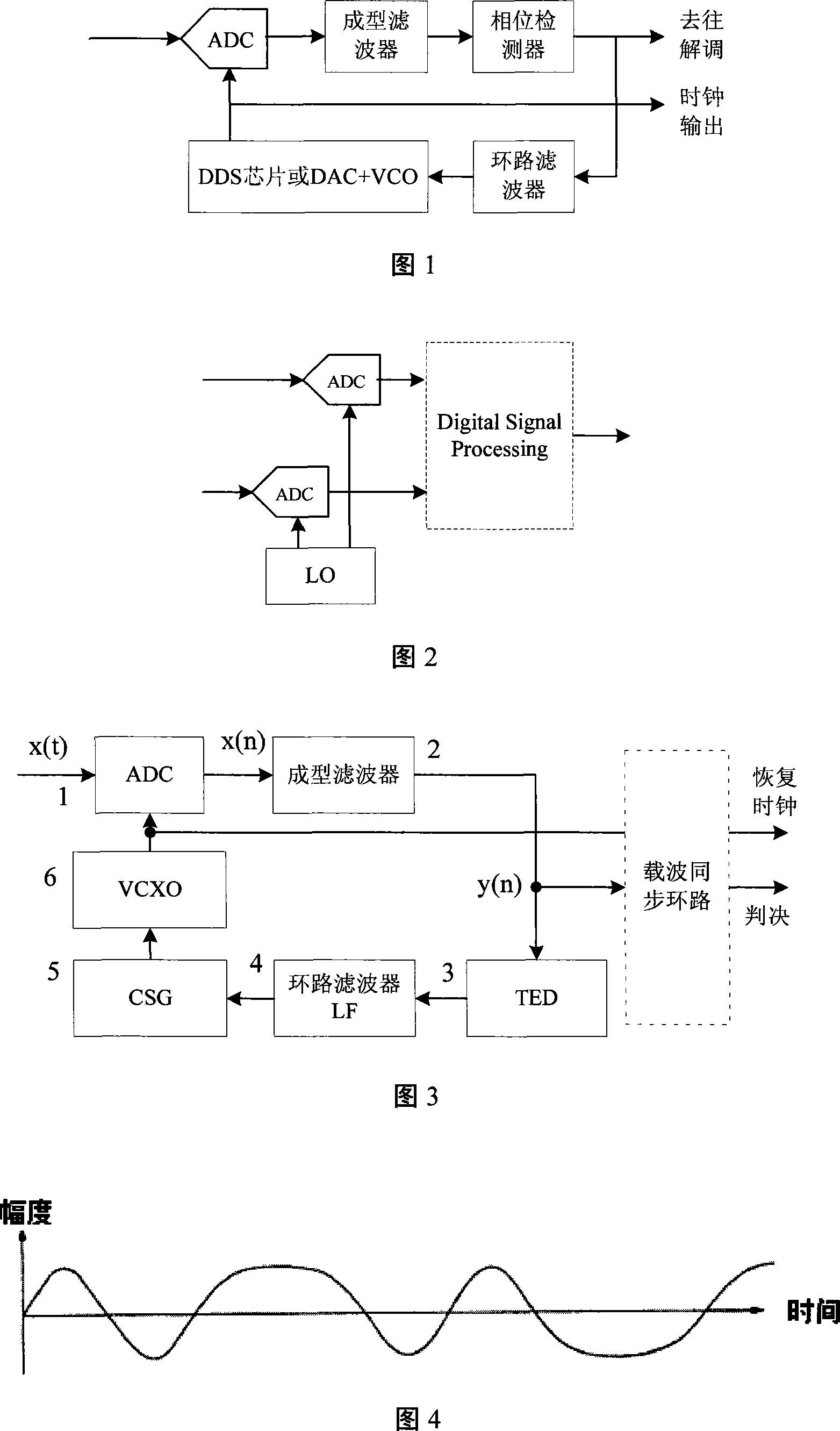

[0025] As shown in Fig. 3, the present invention is suitable for realization on FPGA or DSP+FPGA platform. If implemented by FPGA, except the two modules of ADC and VCXO in Figure 3, other modules are implemented in FPGA; if implemented by DSP+FPGA, the timing error detector TED in Figure 3 can be implemented in DSP, other Modules except ADC and VCXO are implemented in FPGA. The shaping filter adopts the root raised cosine filter (Root Raised Cosine Filter, RRCF); the voltage-controlled crystal oscillator VXCO adopts a general-purpose voltage-controlled crystal oscillator, which includes four pins: the input control signal pin, the power pin , ground pin and output clock signal pin.

[0026] As shown in Figure 3, the working process of the clock recovery loop is: (1) the root raised cosine filter (RootRaised Cosine Filter, RRCF) performs shaping filtering on the sampling signal of the ADC to restore the best sampling point; (2) timing The error detector (Timing Error Detecto...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More