Baud-rate CDR circuit and method for low power applications

A clock data recovery, circuit technology, applied in the direction of automatic power control, electrical components, digital transmission systems, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

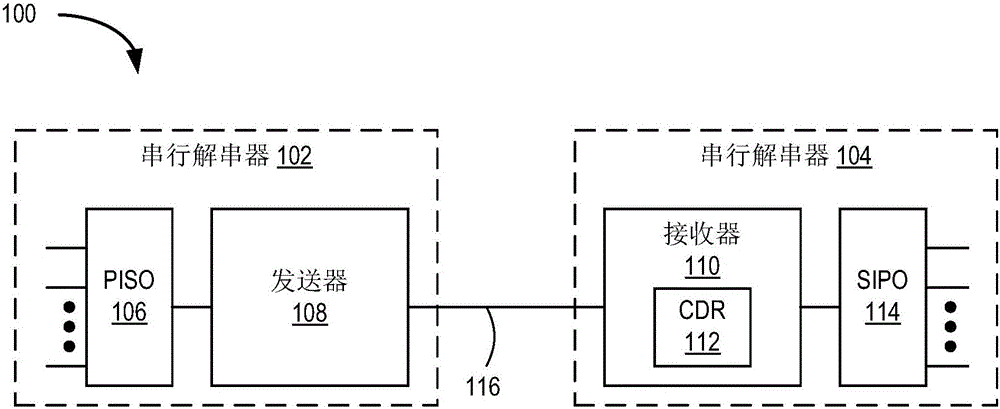

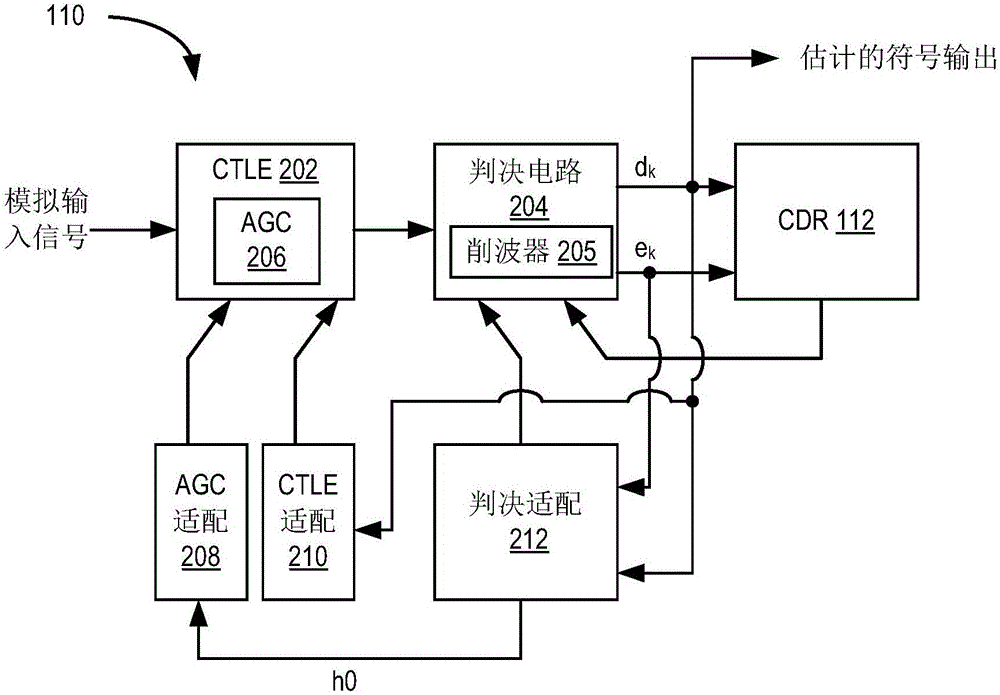

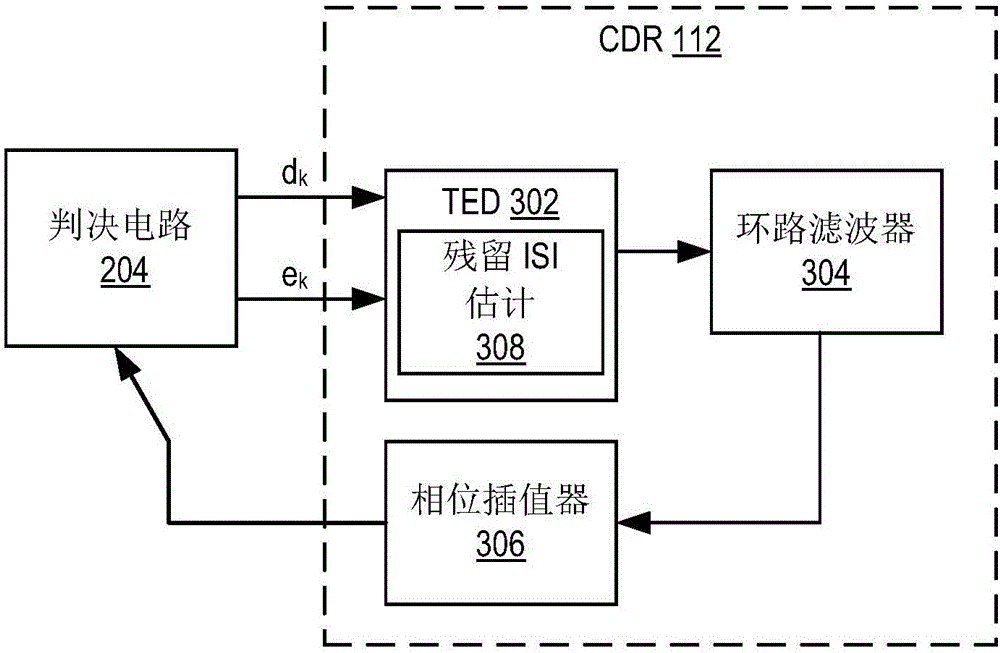

[0016] Various features are described below with respect to the accompanying drawings. It should be noted that the drawings may or may not be drawn to scale and that elements having similar structure or function are represented by like reference numerals throughout the drawings. It should be noted that the drawings are only intended to facilitate the description of the features. It is not intended as a detailed description or as a limitation of the scope of the claimed invention. Furthermore, an illustrated embodiment need not have all of the aspects or advantages illustrated. Aspects or advantages described in connection with a particular embodiment are not necessarily limited to that embodiment, and may be practiced in any other embodiment although not shown or described in detail in any other embodiment.

[0017] The techniques described here provide baud rate clock data recovery (CDR) for low power applications. The disclosed CDR circuit provides a robust CDR for use in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com